Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Detuils                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-10-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

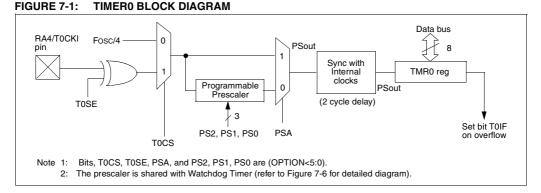

#### 7.0 TIMER0 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

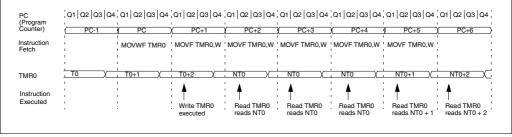

Timer mode is selected by clearing bit T0CS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 TMR0 Interrupt

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the TImer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

© 1997-2013 Microchip Technology Inc.

#### 8.1 <u>Timer1 Operation in Timer Mode</u>

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer mode is selected by clearing bit TMR1CS (T1CON<1>). In this mode, the input clock to the timer is Fosc/4. The synchronize control bit  $\overline{T1SYNC}$  (T1CON<2>) has no effect since the internal clock is always in sync.

#### 8.2 <u>Timer1 Operation in Synchronized</u> <u>Counter Mode</u>

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on T1OSI when enable bit T1OSCEN is set or pin with T1CKI when bit T1OSCEN is cleared.

| Note: | The T1OSI function is multiplexed to differ- |

|-------|----------------------------------------------|

|       | ent pins, depending on the device. See the   |

|       | pinout descriptions to see which pin has     |

|       | the T1OSI function.                          |

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if an external clock is present, since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

# 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to appropriate electrical specification section, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to applicable electrical specification section, parameters 40, 42, 45, 46, and 47.

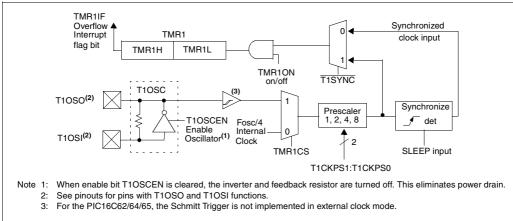

#### FIGURE 8-2: TIMER1 BLOCK DIAGRAM

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF   | CCP1CON     | ; | Turn CCP module off   |

|--------|-------------|---|-----------------------|

| MOVLW  | NEW_CAPT_PS | ; | Load the W reg with   |

|        |             | ; | the new prescaler     |

|        |             | ; | mode value and CCP ON |

| MOVWF  | CCP1CON     | ; | Load CCP1CON with     |

| ; this | value       |   |                       |

## 10.2 Compare Mode

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time interrupt flag bit CCP1IF is set.

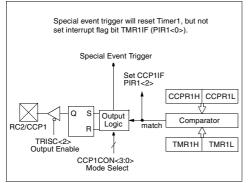

#### FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 10.2.1 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 10.2.2 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 10.2.3 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 and CCP2 resets the TMR1 register pair. This allows the CCPR1H:CCPR1L and CCPR2H:CCPR2L registers to effectively be 16-bit programmable period register(s) for Timer1.

For compatibility issues, the special event trigger output of CCP1 (<u>PIC16C72</u>) and CCP2 (all other <u>PIC16C7X</u> devices) also starts an A/D conversion.

Note: The "special event trigger" from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

#### 10.3 PWM Mode

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

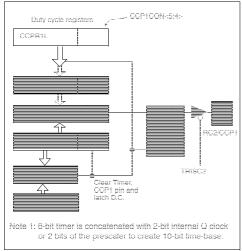

Figure 10-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 10.3.3.

#### FIGURE 10-4: SIMPLIFIED PWM BLOCK DIAGRAM

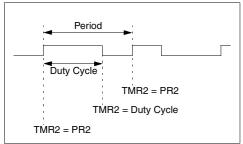

A PWM output (Figure 10-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 10-5: PWM OUTPUT

#### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM duty cycle is latched from CCPR1L into CCPR1H

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

| Note: | The Timer2 postscaler (see Section 9.1) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be forced to the low level.

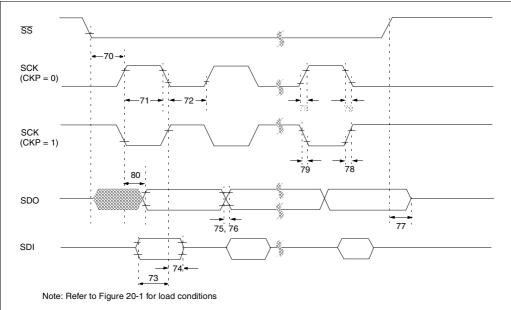

#### 11.2 <u>SPI Mode for PIC16C62/62A/R62/63/</u> R63/64/64A/R64/65/65A/R65

This section contains register definitions and operational characteristics of the SPI module for the PIC16C62, PIC16C62A, PIC16CR62, PIC16C63, PIC16CR63, PIC16C64A, PIC16CR64, PIC16CR64, PIC16C65, PIC16C65A, PIC16CR65.

## FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| U-0      | U-0                                                                                                                                                                                                                                                                    | R-0         | B-0      | B-0 | R-0 | B-0 | B-0 |                  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-----|-----|-----|-----|------------------|--|--|--|--|

| _        | _                                                                                                                                                                                                                                                                      | D/A         | P        | S   | R/W | UA  | BF  | R = Readable bit |  |  |  |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset                                                                                                                                                                           |             |          |     |     |     |     |                  |  |  |  |  |

| bit 7-6: | Unimpl                                                                                                                                                                                                                                                                 | emented     | Read as  | '0' |     |     |     |                  |  |  |  |  |

| bit 5:   | <ul> <li>5: D/Ā: Data/Address bit (l<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                       |             |          |     |     |     |     |                  |  |  |  |  |

| bit 4:   | <ul> <li>P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul> |             |          |     |     |     |     |                  |  |  |  |  |

| bit 3:   | <ul> <li>Start bit (l<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Start bit was not detected last</li> </ul> |             |          |     |     |     |     |                  |  |  |  |  |

| bit 2:   | <b>R/W</b> : Read/Write bit information ( $I^2C$ mode only)<br>This bit holds the R/W bit information following the last address match. This bit is valid from the address match to the next start bit, stop bit, or $\overline{ACK}$ bit.<br>1 = Read<br>0 = Write    |             |          |     |     |     |     |                  |  |  |  |  |

| bit 1:   | <b>UA</b> : Update Address (10-bit $I^2C$ mode only)<br>1 = Indicates that the user needs to update the address in the SSPADD register<br>0 = Address does not need to be updated                                                                                      |             |          |     |     |     |     |                  |  |  |  |  |

| bit 0:   | BF: Buf                                                                                                                                                                                                                                                                | fer Full St | atus bit |     |     |     |     |                  |  |  |  |  |

|          | <u>Beceive</u> (SPI and I <sup>2</sup> C modes)<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                                                   |             |          |     |     |     |     |                  |  |  |  |  |

|          | <u>Iransmit</u> (I <sup>2</sup> C mode only)<br>1 = Transmit in progress, SSPBUF is full<br>0 = Transmit complete, SSPBUF is empty                                                                                                                                     |             |          |     |     |     |     |                  |  |  |  |  |

## FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                      | R/W-0          | R/W-0        | R/W-0           | R/W-0       | R/W-0                        |                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|--------------|-----------------|-------------|------------------------------|---------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SSPEN                      | CKP            | SSPM3        | SSPM2           | SSPM1       | SSPM0                        | R = Readable bit                                                    |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             | bit0                         | W = Writable bit<br>U = Unimplemented bit, read                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | as '0'                                                              |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | - n =Value at POR reset                                             |

| bit 7:   | WCOL: W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rite Collisio              | on Detect      | bit          |                 |             |                              | <u>.</u>                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                | ritten while | e it is still t | ransmitting | the previo                   | us word                                                             |

|          | (must be c<br>0 = No col                                                                                                                                                                                                                                                                                                                                                                                                                                                         | leared in s                | oftware)       |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                | 1. 11        |                 |             |                              |                                                                     |

| bit 6:   | SSPOV: R                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            | erriow Dei     | IECT DIT     |                 |             |                              |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | الماريد اممريا |              |                 |             | والمراجع والمراجع            |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | evious data. In case of overflow,<br>e. The user must read the SSP- |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | 0              |              |                 | ,           |                              | mode the overflow bit is not set                                    |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | ption (and     | l transmiss  | sion) is init   | iated by w  | riting to the                | SSPBUF register.                                                    |

|          | 0 = No over                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |                |              |                 |             |                              |                                                                     |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = A byte<br>in transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              | us byte. SSPOV is a "don't care"                                    |

|          | 0 = No ove                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | r Ov mus       | t De cleate  | su in sonw      |             | er moue.                     |                                                                     |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vnchronou                  | s Serial F     | ort Enable   | e bit           |             |                              |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | ort and co     | nfigures S   | CK, SDO,        | and SDI a   | s serial por                 | t pins                                                              |

|          | 0 = Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es serial p                | ort and co     | onfigures th | nese pins       | as I/O port | pins                         |                                                                     |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = Enable<br>0 = Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              | ial port pins                                                       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                | •            | •               | •           | •                            | s input or output.                                                  |

| bit 4:   | CKP: Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             | <u>9</u>                     |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ,                          |                |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | k is a higł    | n level. Tra | nsmit hap       | pens on fa  | lling edge,                  | receive on rising edge.                                             |

|          | 0 = Idle sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ate for cloc               | k is a low     | level. Trar  | nsmit happ      | ens on ris  | ing edge, re                 | eceive on falling edge.                                             |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | SCK relea                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = Enable<br>0 = Holds                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | clock stra     | tch) (Llead  | to onsure       | data satu   | n tima)                      |                                                                     |

| hit 2 0. | SSPM3:S                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                | , ,          |                 |             | P ane)                       |                                                                     |

| DII 3-0. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                |                |              |                 | elect bits  |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                | ,              |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                | ,              |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                |                |              |                 | ontrol one  | blod                         |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI slave mo<br>PI slave mo |                |              |                 |             |                              | an be used as I/O pin.                                              |

|          | 0110 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 01000 = 00000000 | C slave mo                 | de, 7-bit a    | address      |                 |             |                              |                                                                     |

|          | $0111 = I^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C slave mo                 | de, 10-bit     | address      |                 |             |                              |                                                                     |

|          | $1011 =  ^{2}($                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C firmware                 | controlled     | d Master N   | lode (slav      | e idle)     |                              | b.ld                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             | interrupts e<br>t interrupts |                                                                     |

|          | 1111 - I (                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 Slave 110                |                | auuress V    | viui stait d    | na stop bli | interrupts                   | enabled                                                             |

# 14.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 14-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 14-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 14-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 14-2 lists the instructions recognized by the MPASM assembler.

Figure 14-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXX products, do not use the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

#### FIGURE 14-1: GENERAL FORMAT FOR INSTRUCTIONS

| RETLW             | Return v                                                                                                                                                            | vith Liter            | al in W                            |                                         | RETURN                                                                                            | Return fi                 | rom Sub          | routine          |                    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------|------------------|------------------|--------------------|

| Syntax:           | [ label ]                                                                                                                                                           | RETLW                 | k                                  |                                         | Syntax:                                                                                           | [ label ]                 | RETUR            | N                |                    |

| Operands:         | $0 \le k \le 2$                                                                                                                                                     | 55                    |                                    |                                         | Operands:                                                                                         | None                      |                  |                  |                    |

| Operation:        | $k \rightarrow (W);$                                                                                                                                                |                       |                                    |                                         | Operation:                                                                                        | $\text{TOS} \to \text{F}$ | ъС               |                  |                    |

|                   | $TOS \rightarrow F$                                                                                                                                                 | PC                    |                                    |                                         | Status Affected:                                                                                  | None                      |                  |                  |                    |

| Status Affected:  | None                                                                                                                                                                | -                     |                                    |                                         | Encoding:                                                                                         | 00                        | 0000             | 0000             | 1000               |

| Encoding:         | 11                                                                                                                                                                  | 01xx                  | kkkk                               | kkkk                                    | Description:                                                                                      | Return fro                | m subrout        | ine. The st      | ack is             |

| Description:      | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle |                       |                                    |                                         | POPed and the top of the stack (T is loaded into the program counter. is a two cycle instruction. |                           |                  |                  |                    |

|                   | instruction                                                                                                                                                         |                       | s is a two c                       | cycle                                   | Words:                                                                                            | 1                         |                  |                  |                    |

| Words:            | 1                                                                                                                                                                   |                       |                                    |                                         | Cycles:                                                                                           | 2                         |                  |                  |                    |

| Cycles:           | 2                                                                                                                                                                   |                       |                                    |                                         | Q Cycle Activity:                                                                                 | Q1                        | Q2               | Q3               | Q4                 |

| Q Cycle Activity: | Q1                                                                                                                                                                  | Q2                    | Q3                                 | Q4                                      | 1st Cycle                                                                                         | Decode                    | No-<br>Operation | No-<br>Operation | Pop from the Stack |

| 1st Cycle         | Decode                                                                                                                                                              | Read<br>literal 'k'   | No-<br>Operation                   | Write to<br>W, Pop<br>from the<br>Stack | 2nd Cycle                                                                                         | No-<br>Operation          | No-<br>Operation | No-<br>Operation | No-<br>Operation   |

| 2nd Cycle         | No-                                                                                                                                                                 | No-                   | No-                                | No-                                     | Example                                                                                           | RETURN                    |                  |                  |                    |

|                   | Operation                                                                                                                                                           | Operation             | Operation                          | Operation                               |                                                                                                   | After Inte                | •                |                  |                    |

| Example           | CALL TABL                                                                                                                                                           | ;offse                | tains tabl<br>t value<br>has table |                                         |                                                                                                   |                           | PC =             | TOS              |                    |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2<br>•                                                                                                                               | ;W = 0<br>;Begin<br>; |                                    |                                         |                                                                                                   |                           |                  |                  |                    |

|                   | RETLW kn                                                                                                                                                            |                       | of table                           |                                         |                                                                                                   |                           |                  |                  |                    |

|                   | Before In<br>After Inst                                                                                                                                             | truction              | 0x07<br>value of k8                | 3                                       |                                                                                                   |                           |                  |                  |                    |

#### 15.2 DC Characteristics: PIC16LC61-04 (Commercial, Industrial)

|              | Standard Operating Conditions (unless otherwise stated)          |                                                                                   |      |      |     |       |                                                                  |  |  |

|--------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|-----|-------|------------------------------------------------------------------|--|--|

| DC CHA       | RACTERISTICS                                                     | Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and |      |      |     |       |                                                                  |  |  |

|              |                                                                  |                                                                                   |      |      | 0°C | ≥ ≤   | $TA \le +70^{\circ}C$ for commercial                             |  |  |

| Param<br>No. | Characteristic                                                   | Sym                                                                               | Min  | Тур† | Max | Units | Conditions                                                       |  |  |

| D001         | Supply Voltage                                                   | Vdd                                                                               | 3.0  | -    | 6.0 | V     | XT, RC, and LP osc configuration                                 |  |  |

| D002*        | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr                                                                               | -    | 1.5  | -   | V     |                                                                  |  |  |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                                                                              | -    | Vss  | -   | V     | See section on Power-on Reset for details                        |  |  |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                                                                              | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details                        |  |  |

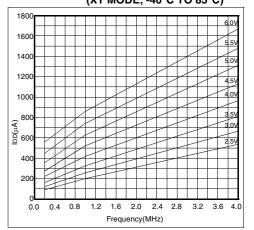

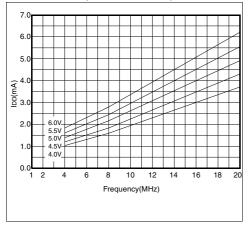

| D010         | Supply Current (Note 2)                                          | Idd                                                                               | -    | 1.4  | 2.5 | mA    | FOSC = 4 MHz, VDD = 3.0V (Note 4)                                |  |  |

| D010A        |                                                                  |                                                                                   | -    | 15   | 32  | μA    | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc configuration |  |  |

| D020         | Power-down Current                                               | IPD                                                                               | -    | 5    | 20  | μA    | VDD = 3.0V, WDT enabled, -40°C to +85°C                          |  |  |

| D021         | (Note 3)                                                         |                                                                                   | -    | 0.6  | 9   | μA    | VDD = 3.0V, WDT disabled, 0°C to +70°C                           |  |  |

| D021A        |                                                                  |                                                                                   | -    | 0.6  | 12  | μA    | VDD = 3.0V, WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$       |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

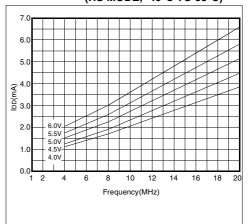

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.