Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-10-pq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**TABLE 3-3:** PIC16C64/64A/R64/65/65A/R65/67 PINOUT DESCRIPTION

| Pin Name                                      | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>MQFP<br>Pin# | Pin<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |  |  |

|-----------------------------------------------|-------------|--------------|----------------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC1/CLKIN                                    | 13          | 14           | 30                   | ı           | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |  |  |

| OSC2/CLKOUT                                   | 14          | 15           | 31                   | 0           | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the pin outputs CLK-OUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |

| MCLR/VPP                                      | 1           | 2            | 18                   | I/P         | ST                     | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                    |  |  |

|                                               |             |              |                      |             |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |  |  |

| RA0                                           | 2           | 3            | 19                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RA1                                           | 3           | 4            | 20                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RA2                                           | 4           | 5            | 21                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RA3                                           | 5           | 6            | 22                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RA4/T0CKI                                     | 6           | 7            | 23                   | I/O         | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                  |  |  |

| RA5/SS                                        | 7           | 8            | 24                   | I/O         | TTL                    | RA5 can also be the slave select for the synchronous serial port.                                                                                                                                        |  |  |

|                                               |             |              |                      |             |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |  |  |

| RB0/INT                                       | 33          | 36           | 8                    | I/O         | TTL/ST <sup>(4)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |  |  |

| RB1                                           | 34          | 37           | 9                    | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RB2                                           | 35          | 38           | 10                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RB3                                           | 36          | 39           | 11                   | I/O         | TTL                    |                                                                                                                                                                                                          |  |  |

| RB4                                           | 37          | 41           | 14                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |  |  |

| RB5                                           | 38          | 42           | 15                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |  |  |

| RB6                                           | 39          | 43           | 16                   | I/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |  |  |

| RB7                                           | 40          | 44           | 17                   | I/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |  |  |

|                                               |             |              |                      |             |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                      |  |  |

| RC0/T10SO <sup>(1)</sup> /T1CKI               | 15          | 16           | 32                   | I/O         | ST                     | RC0 can also be the Timer1 oscillator output <sup>(1)</sup> or Timer1 clock input.                                                                                                                       |  |  |

| RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> | 16          | 18           | 35                   | I/O         | ST                     | RC1 can also be the Timer1 oscillator input <sup>(1)</sup> or Capture2 input/Compare2 output/PWM2 output <sup>(2)</sup> .                                                                                |  |  |

| RC2/CCP1                                      | 17          | 19           | 36                   | I/O         | ST                     | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                     |  |  |

| RC3/SCK/SCL                                   | 18          | 20           | 37                   | I/O         | ST                     | RC3 can also be the synchronous serial clock input/out-<br>put for both SPI and I <sup>2</sup> C modes.                                                                                                  |  |  |

| RC4/SDI/SDA                                   | 23          | 25           | 42                   | I/O         | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                          |  |  |

| RC5/SDO                                       | 24          | 26           | 43                   | I/O         | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                             |  |  |

| RC6/TX/CK <sup>(2)</sup>                      | 25          | 27           | 44                   | I/O         | ST                     | RC6 can also be the USART Asynchronous Transmit <sup>(2)</sup> or Synchronous Clock <sup>(2)</sup> .                                                                                                     |  |  |

| RC7/RX/DT <sup>(2)</sup>                      | 26          | 29           | 1                    | I/O         | ST                     | RC7 can also be the USART Asynchronous Receive <sup>(2)</sup> or Synchronous Data <sup>(2)</sup> .                                                                                                       |  |  |

Legend: I = input O = output - = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: Pin functions T1OSO and T1OSI are reversed on the PIC16C64.

- 2: CCP2 and the USART are not available on the PIC16C64/64A/R64.

- 3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

- 4: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 5: This buffer is a Schmitt Trigger input when used in serial programming mode.

- 6: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

#### 4.2.2.5 PIR1 REGISTER

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

#### FIGURE 4-16: PIR1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 0Ch)

| R/   | /W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |                                       |

|------|------|-------|-----|-----|-------|--------|--------|--------|---------------------------------------|

| -    | _    | _     | _   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF | R = Readable bit                      |

| bit7 |      |       |     |     |       |        |        | bit0   | U = Unimplemented bit,<br>read as '0' |

|      |      | _     |     |     |       |        |        |        | - n = Value at POR reset              |

- bit 7-6: Reserved: Always maintain these bits clear.

- bit 5-4: Unimplemented: Read as '0'

- bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit

- 1 = The transmission/reception is complete (must be cleared in software)

- 0 = Waiting to transmit/receive

- bit 2: CCP1IF: CCP1 Interrupt Flag bit

#### Capture Mode

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

#### Compare Mode

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

#### **PWM Mode**

Unused in this mode

- bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflow occurred (must be cleared in software)

- 0 = No TMR1 register overflow occurred

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| U = Unimplemented bit, read as '0' - n = Value at POR reset  1.7-6: Reserved: Always maintain these bits clear.  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  1.4: TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  1.3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  1.2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1. TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                   | R/W-0    | R/W-0                                                                   | R-0                                                                              | R-0                                   | R/W-0                                 | R/W-0         | R/W-0         | R/W-0    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------|---------------|----------|--|--|

| U = Unimplemented bit, read as '0' - n = Value at POR reset  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  TXIF: USART transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred (must be cleared in software) 1 : TMR1F: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software) | _        | _                                                                       | RCIF                                                                             | TXIF                                  | SSPIF                                 | CCP1IF        | TMR2IF        | TMR1IF   |  |  |

| t 5: RCIF: USART Receive Interrupt Flag bit  1 = The USART receive buffer is full (cleared by reading RCREG)  0 = The USART receive buffer is empty  44: TXIF: USART Transmit Interrupt Flag bit  1 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is full  1 = The transmission/reception is complete (must be cleared in software)  0 = Waiting to transmit/receive  1 = CCP1IF: CCP1 Interrupt Flag bit  Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2IF: TMR2 to PR2 match occurred  0 = No TMR1 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 O: TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                             | oit7     |                                                                         |                                                                                  | bit0                                  | U = Unimplemented bit,<br>read as '0' |               |               |          |  |  |

| 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  14:  TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2:  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1:  TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: 1:  TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow loccurred (must be cleared in software)                                                                                                                                                                                                                                                                                                | bit 7-6: | Reserved:                                                               | Always ma                                                                        | intain thes                           | e bits clear.                         |               |               |          |  |  |

| 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  4: 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  4: 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 5:   | 1 = The US                                                              | ART receiv                                                                       | e buffer is                           | full (cleared                         | d by reading  | RCREG)        |          |  |  |

| 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2 : CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1 to: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 4:   | 1 = The US                                                              | ART transi                                                                       | nit buffer is                         | empty (cle                            | ared by writi | ng to TXRE    | G)       |  |  |

| Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 : TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 3:   | 1 = The tra                                                             | nsmission/i                                                                      | reception is                          |                                       |               | ared in softv | vare)    |  |  |

| 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred  t 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 2:   | Capture Mo 1 = A TMR 0 = No TMI Compare M 1 = A TMR 0 = No TMI PWM Mode | ode<br>1 register c<br>R1 register<br><u>lode</u><br>1 register c<br>R1 register | apture occ<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | ed (must be o | ,             | oftware) |  |  |

| 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1:   | 1 = TMR2 t                                                              | o PR2 mat                                                                        | ch occurre                            | d (must be                            |               | oftware)      |          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 0:   | 1 = TMR1 ı                                                              | egister ove                                                                      | rflow occu                            | rred (must l                          | oe cleared in | software)     |          |  |  |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

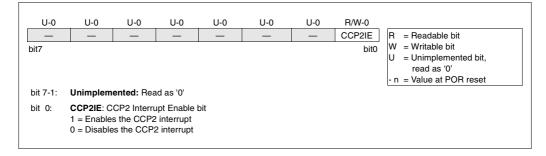

#### 4.2.2.6 PIE2 REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt enable bit.

# FIGURE 4-20: PIE2 REGISTER (ADDRESS 8Dh)

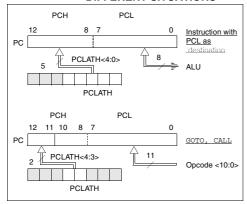

#### 4.3 PCL and PCLATH

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-24 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-24: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or a POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no status bits to indicate stack overflows or stack underflow conditions

Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address

## 4.4 Program Memory Paging

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PIC16C6X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C6X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

# PIC16C6X

NOTES:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must

## **EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)**

be followed even if the WDT is disabled.

Lines 2 and 3 do NOT have to be included if the final desired prescale value is other than 1:1. If 1:1 is final desired value, then a temporary prescale value is set in lines 2 and 3 and the final prescale value will be set in lines 10 and 11.

```

1) BSF

STATUS, RPO

MOVLW b'xx0x0xxx'

;Select clock source and prescale value of

3) MOVWF OPTION REG

;other than 1:1

STATUS, RPO

BCF

;Bank 0

5)

;Clear TMR0 and prescaler

CLRF

TMR0

BSF

STATUS, RP1

;Bank 1

7)

MOVLW b'xxxx1xxx'

;Select WDT, do not change prescale value

8) MOVWF OPTION REG

9) CLRWDT

;Clears WDT and prescaler

10) MOVLW b'xxxx1xxx'

;Select new prescale value and WDT

11) MOVWF OPTION REG

STATUS, RPO

:Bank 0

12) BCF

```

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

#### **EXAMPLE 7-2:** CHANGING PRESCALER (WDT→TIMER0)

```

CLRWDT ;Clear WDT and prescaler

BSF STATUS, RPO ;Bank 1

MOVLW b'xxxx0xxx';Select TMRO, new prescale value and clock source

MOVWF OPTION_REG ;

BCF STATUS, RPO ;Bank 0

```

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name   | Bit 7  | Bit 6               | Bit 5      | Bit 4       | Bit 3 | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|---------------------|------------|-------------|-------|---------|---------|-------|--------------------------|---------------------------|

| 01h, 101h             | TMR0   | Timer0 | module's r          | egister    |             |       |         |         |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE <sup>(1)</sup> | TOIE       | INTE        | RBIE  | TOIF    | INTF    | RBIF  | 0000 000x                | 0000 000u                 |

| 81h, 181h             | OPTION | RBPU   | INTEDG              | T0CS       | T0SE        | PSA   | PS2     | PS1     | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | _      | _                   | PORTA Data | Direction F | •     | 11 1111 | 11 1111 |       |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

Note 1: TRISA<5> and bit PEIE are not implemented on the PIC16C61, read as '0'.

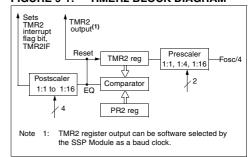

### 9.0 TIMER2 MODULE

#### **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

#### 9.2 Output of TMR2

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

#### U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 = Readable bit W = Writable bit hit7 U = Unimplemented bit, read as '0' - n = Value at POR reset bit 7: Unimplemented: Read as '0' TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits 0000 = 1:1 postscale 0001 = 1:2 postscale 1111 = 1:16 postscale bit 2: TMR2ON: Timer2 On bit 1 = Timer2 is on 0 = Timer2 is off bit 1-0: T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits 00 = 1:1 prescale 01 = 1:4 prescale 1x = 1:16 prescale

# 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT ter-

minals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- · Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|-------|-------|-----|-------|------|-------|

| CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

| bit7  |       |       |       |     |       |      | bit0  |

R = Readable bit

W = Writable bit

U = Unimplemented bit.

read as '0'

- n =Value at POR reset

bit 7: CSRC: Clock Source Select bit

Asynchronous mode

Don't care

Synchronous mode

- 1 = Master mode (Clock generated internally from BRG)

- 0 = Slave mode (Clock from external source)

bit 6: TX9: 9-bit Transmit Enable bit

1 = Selects 9-bit transmission

0 = Selects 8-bit transmission

bit 5: TXEN: Transmit Enable bit

1 = Transmit enabled

0 = Transmit disabled

Note: SREN/CREN overrides TXEN in SYNC mode.

bit 4: SYNC: USART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

bit 3: Unimplemented: Read as '0'

bit 2: BRGH: High Baud Rate Select bit

Asynchronous mode

1 = High speed

Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional infor-

mation or use the PIC16C66/67.

0 = Low speed

Synchronous mode Unused in this mode

bit 1: TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0: TX9D: 9th bit of transmit data. Can be parity bit.

# 13.0 SPECIAL FEATURES OF THE CPU

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- · Watchdog Timer (WDT)

- SLEEP mode

- · Code protection

- · ID locations

- · In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two

timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 13.1 Configuration Bits

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming

## FIGURE 13-1: CONFIGURATION WORD FOR PIC16C61

| — -<br>bit13 | -   -                                               | _                                   | _           | _       | _        | _        | _        | CP0    | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|--------------|-----------------------------------------------------|-------------------------------------|-------------|---------|----------|----------|----------|--------|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5:    | Unimple                                             | mented                              | Read        | as '1'  |          |          |          |        |       |      |       |               |                      |                 |

| bit 4:       | <b>CP0</b> : Code<br>1 = Code<br>0 = All me         | protecti                            | on off      |         | d, but ( | 00h - 3f | =h is wr | itable |       |      |       |               |                      |                 |

| bit 3:       | PWRTE:<br>1 = Powe<br>0 = Powe                      | r-up Tim                            | ner ena     | bled    | e bit    |          |          |        |       |      |       |               |                      |                 |

| bit 2:       | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT               | enabled                             | ĺ           | Enable  | e bit    |          |          |        |       |      |       |               |                      |                 |

| bit 1-0:     | FOSC1:F<br>11 = RC<br>10 = HS<br>01 = XT<br>00 = LP | oscillato<br>oscillato<br>oscillato | r<br>r<br>r | or Sele | ction b  | its      |          |        |       |      |       |               |                      |                 |

TABLE 13-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register |    |    |     |     |    | Appli | cab | le De | vices | 5  |     |     |    |    | Brown-out<br>Reset |     | MCLR Reset during:  – normal operation  – SLEEP  WDT Reset | Wake-up via<br>interrupt or<br>WDT Wake-up |

|----------|----|----|-----|-----|----|-------|-----|-------|-------|----|-----|-----|----|----|--------------------|-----|------------------------------------------------------------|--------------------------------------------|

| W        | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| INDF     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | N/A                |     | N/A                                                        | N/A                                        |

| TMR0     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| PCL      | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000h              |     | 0000h                                                      | PC + 1 <sup>(2)</sup>                      |

| STATUS   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0001 1xx           | кx  | 000q quuu(3)                                               | uuuq quuu(3)                               |

| FSR      | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| DODTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | x xxx              | кx  | u uuuu                                                     | u uuuu                                     |

| PORTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xx xxx             | кx  | uu uuuu                                                    | uu uuuu                                    |

| PORTB    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| PORTC    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| PORTD    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| PORTE    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xx                 | кx  | uuu                                                        | uuu                                        |

| PCLATH   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0 000              | 0.0 | 0 0000                                                     | u uuuu                                     |

| INTCON   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | ΣX  | 0000 000u                                                  | uuuu uuuu(1)                               |

| PIR1     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 000             | 0.0 | 00 0000                                                    | uu uuuu(1)                                 |

|          | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu(1)                               |

| PIR2     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 |                    | - 0 | 0                                                          | (2)                                        |

| TMR1L    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| TMR1H    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кх  | uuuu uuuu                                                  | uuuu uuuu                                  |

| T1CON    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 000             | 0.0 | uu uuuu                                                    | uu uuuu                                    |

| TMR2     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu                                  |

| T2CON    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | -000 000           | 0.0 | -000 0000                                                  | -uuu uuuu                                  |

| SSPBUF   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кх  | uuuu uuuu                                                  | uuuu uuuu                                  |

| SSPCON   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu                                  |

| CCPR1L   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| CCPR1H   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| CCP1CON  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 000             | 0.0 | 00 0000                                                    | uu uuuu                                    |

| RCSTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 -00           | хC  | 0000 -00x                                                  | uuuu -uuu                                  |

| TXREG    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu                                  |

| RCREG    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu                                  |

| CCPR2L   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| CCPR2H   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxx           | кx  | uuuu uuuu                                                  | uuuu uuuu                                  |

| CCP2CON  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000           | 0.0 | 0000 0000                                                  | uuuu uuuu                                  |

| OPTION   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 111           | 11  | 1111 1111                                                  | uuuu uuuu                                  |

| TRISA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1 111              | 11  | 1 1111                                                     | u uuuu                                     |

| .1110/1  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 11 111             | 11  | 11 1111                                                    | uu uuuu                                    |

| TRISB    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 111           | 11  | 1111 1111                                                  | uuuu uuuu                                  |

| TRISC    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 111           | 11  | 1111 1111                                                  | uuuu uuuu                                  |

Legend: u = unchanged, x = unknown, -= unimplemented bit read as '0', <math>q = value depends on condition.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

<sup>3:</sup> See Table 13-10 and Table 13-11 for reset value for specific conditions.

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

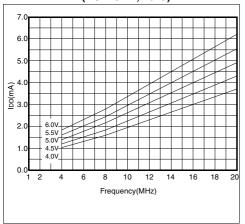

15.1 DC Characteristics: PIC16C61-04 (Commercial, Industrial, Extended) PIC16C61-20 (Commercial, Industrial, Extended)

|              |                                                                   | Standard Operating Conditions (unless otherwise stated) |      |      |     |       |                                                   |  |  |  |

|--------------|-------------------------------------------------------------------|---------------------------------------------------------|------|------|-----|-------|---------------------------------------------------|--|--|--|

| DC CHAR      |                                                                   | Operatir                                                |      | •    |     |       | ≤ Ta ≤ +125°C for extended,                       |  |  |  |

| DC CHARA     | ACTENISTICS                                                       |                                                         |      |      | -40 | )°C ≤ | ≤ Ta ≤ +85°C for industrial and                   |  |  |  |

|              |                                                                   |                                                         |      |      | 0°( | 2 ≤   | TA ≤ +70°C for commercial                         |  |  |  |

| Param<br>No. | Characteristic                                                    | Sym                                                     | Min  | Typ† | Max | Units | Conditions                                        |  |  |  |

| D001         | Supply Voltage                                                    | VDD                                                     | 4.0  | -    | 6.0 | V     | XT, RC and LP osc configuration                   |  |  |  |

| D001A        |                                                                   |                                                         | 4.5  | -    | 5.5 | V     | HS osc configuration                              |  |  |  |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                            | VDR                                                     | -    | 1.5  | -   | V     |                                                   |  |  |  |

| D003         | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                                                    | -    | Vss  | -   | V     | See section on Power-on Reset for details         |  |  |  |

| D004*        | VDD rise rate to ensure internal Power-on Reset signal            | SVDD                                                    | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details         |  |  |  |

| D010         | Supply Current (Note 2)                                           | IDD                                                     | -    | 1.8  | 3.3 | mA    | FOSC = 4 MHz, VDD = 5.5V (Note 4)                 |  |  |  |

| D013         |                                                                   |                                                         | -    | 13.5 | 30  | mA    | HS osc configuration<br>FOSC = 20 MHz, VDD = 5.5V |  |  |  |

| D020         | Power-down Current                                                | IPD                                                     | -    | 7    | 28  | μА    | VDD = 4.0V, WDT enabled, -40°C to +85°C           |  |  |  |

| D021         | (Note 3)                                                          |                                                         | -    | 1.0  | 14  | μΑ    | VDD = 4.0V, WDT disabled, -0°C to +70°C           |  |  |  |

| D021A        |                                                                   |                                                         | -    | 1.0  | 16  | μΑ    | VDD = 4.0V, WDT disabled, -40°C to +85°C          |  |  |  |

| D021B        |                                                                   |                                                         | -    | 1.0  | 20  | μΑ    | VDD = 4.0V, WDT disabled, -40°C to +125°C         |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\underline{\mathsf{OSC1}}$  = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

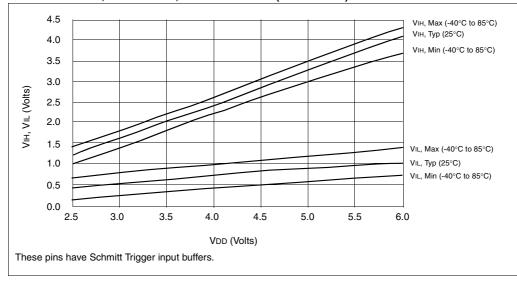

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

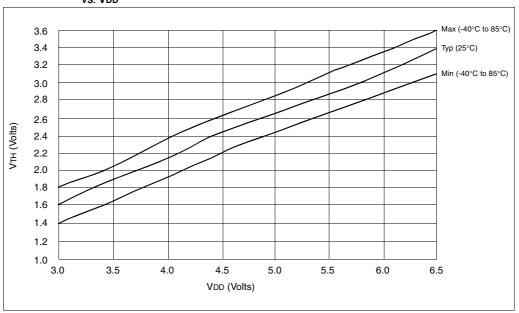

FIGURE 16-11: VTH (INPUT THRESHOLD VOLTAGE) OF OSC1 INPUT (IN XT, HS, AND LP MODES) vs. VDD

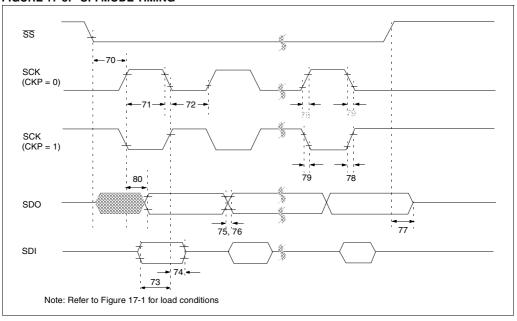

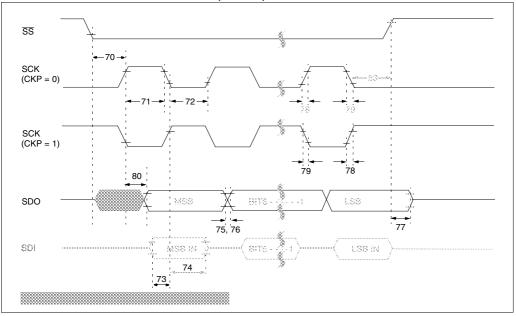

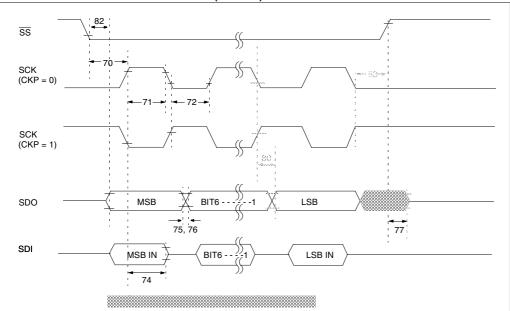

# FIGURE 17-8: SPI MODE TIMING

**TABLE 17-8: SPI MODE REQUIREMENTS**

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Typ† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                | _        | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)       | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

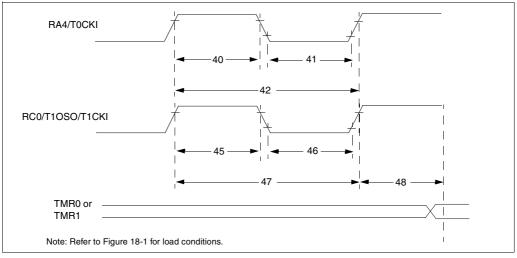

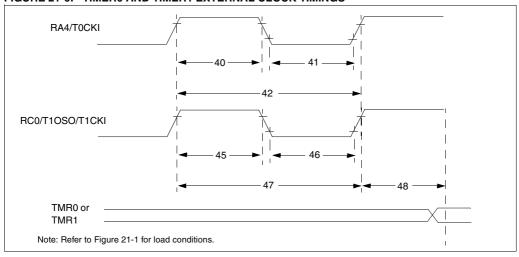

FIGURE 18-6: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 18-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                |                                   |                                | Min                                       | Typ† | Max   | Units | Conditions                         |

|--------------|----------|-----------------------------------------------|-----------------------------------|--------------------------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H     | T0CKI High Pulse V                            | Vidth                             | No Prescaler                   | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                                               |                                   | With Prescaler                 | 10                                        | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L     | T0CKI Low Pulse W                             | /idth                             | No Prescaler<br>With Prescaler | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                                               |                                   |                                | 10                                        | _    | _     | ns    | parameter 42                       |

| 42*          | Tt0P     | T0CKI Period                                  |                                   | No Prescaler<br>With Prescaler | Tcy + 40                                  | _    | _     | ns    |                                    |

|              |          |                                               |                                   |                                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H     | T1CKI High Time                               | Synchronous, F                    |                                | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                                               | Synchronous,                      | PIC16 <b>C</b> 6X              | 15                                        | _    | _     | ns    | parameter 47                       |

|              |          |                                               | Prescaler = 2,4,8                 | PIC16 <b>LC</b> 6X             | 25                                        | _    | _     | ns    |                                    |

|              |          |                                               | Asynchronous                      | PIC16 <b>C</b> 6X              | 30                                        | _    | _     | ns    |                                    |

|              |          |                                               |                                   | PIC16 <b>LC</b> 6X             | 50                                        | _    | _     | ns    |                                    |

| 46*          | Tt1L     | T1CKI Low Time                                | Synchronous, F                    |                                | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                                               | Synchronous,                      | PIC16 <b>C</b> 6X              | 15                                        | _    | _     | ns    | parameter 47                       |

|              |          |                                               | Prescaler = 2,4,8                 | PIC16 <b>LC</b> 6X             | 25                                        | -    | _     | ns    |                                    |

|              |          |                                               | Asynchronous                      | PIC16 <b>C</b> 6X              | 30                                        | _    | _     | ns    |                                    |

|              |          |                                               |                                   | PIC16 <b>LC</b> 6X             | 50                                        | _    | _     | ns    |                                    |

| 47*          | Tt1P     | T1CKI input period                            | Synchronous                       | PIC16 <b>C</b> 6X              | Greater of:<br>30 OR TCY + 40<br>N        | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                               |                                   | PIC16 <b>LC</b> 6X             | Greater of:<br>50 OR TCY + 40<br>N        |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                               | Asynchronous                      | PIC16 <b>C</b> 6X              | 60                                        | _    | _     | ns    |                                    |

|              |          |                                               |                                   | PIC16 <b>LC</b> 6X             | 100                                       | _    | _     | ns    |                                    |

|              | Ft1      | Timer1 oscillator inp                         |                                   |                                | DC                                        | _    | 200   | kHz   |                                    |

|              |          | ,                                             | r enabled by setting bit T1OSCEN) |                                |                                           |      |       |       |                                    |

| 48           | TCKEZtmr | Delay from external clock edge to timer incre |                                   | ner increment                  | 2Tosc                                     | -    | 7Tosc | _     |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for extended,  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for industrial and

0°C ≤ TA ≤ +70°C for commercial

Operating voltage VDD range as described in DC spec Section 20.1 and Section 20.2

|              |                                         | Section           | 011 20.2 |          |     |       |                                                                   |  |  |

|--------------|-----------------------------------------|-------------------|----------|----------|-----|-------|-------------------------------------------------------------------|--|--|

| Param<br>No. | Characteristic                          | Sym               | Min      | Typ<br>+ | Max | Units | Conditions                                                        |  |  |

|              | Output High Voltage                     |                   |          | '        |     |       |                                                                   |  |  |

| D090         | I/O ports (Note 3)                      | Vон               | VDD-0.7  | -        | -   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                      |  |  |

| D090A        |                                         |                   | VDD-0.7  | -        | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                     |  |  |

| D092         | OSC2/CLKOUT (RC osc config)             |                   | VDD-0.7  | -        | -   | V     | IOH = -1.3 mA, VDD = $4.5V$ , $-40^{\circ}$ C to $+85^{\circ}$ C  |  |  |

| D092A        |                                         |                   | VDD-0.7  | -        | -   | V     | IOH = -1.0 mA, VDD = $4.5V$ , $-40^{\circ}$ C to $+125^{\circ}$ C |  |  |

| D150*        | Open-Drain High Voltage                 | Vod               | -        | -        | 14  | V     | RA4 pin                                                           |  |  |

|              | Capacitive Loading Specs on Output Pins |                   |          |          |     |       |                                                                   |  |  |

| D100         | OSC2 pin                                | Cosc <sub>2</sub> | -        | -        | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |

| D101         | All I/O pins and OSC2 (in RC mode)      | Сю                | -        | -        | 50  | pF    |                                                                   |  |  |

| D102         | SCL, SDA in I <sup>2</sup> C mode       | Cb                | -        | -        | 400 | pF    |                                                                   |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

DC CHARACTERISTICS

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

- The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 21-6: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 21-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                              |                                      |                    | Min                                       | Typ† | Max | Units | Conditions                         |