Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-20-p |

TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64

| Address              | Name                                                      | Bit 7                                                    | Bit 6              | Bit 5          | Bit 4          | Bit 3        | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|-----------------------------------------------------------|----------------------------------------------------------|--------------------|----------------|----------------|--------------|-------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               | •                                                         | •                                                        | •                  |                |                | •            | •           | •             | •         | •                        | •                                              |

| 00h <sup>(1)</sup>   | INDF                                                      | Addressing                                               | this location      | uses conter    | nts of FSR to  | address data | a memory (n | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0                                                      | Timer0 mod                                               | dule's registe     | r              |                |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL                                                       | Program Co                                               | ounter's (PC)      | Least Signi    | ficant Byte    |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS                                                    | IRP <sup>(5)</sup>                                       | RP1 <sup>(5)</sup> | RP0            | TO             | PD           | Z           | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR                                                       | Indirect dat                                             | a memory ac        | Idress pointe  | er             |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA                                                     | _                                                        | _                  | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB                                                     | PORTB Da                                                 | ta Latch whe       | n written: PC  | ORTB pins wh   | nen read     |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC PORTC Data Latch when written: PORTC pins when read |                                                          |                    |                |                |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD                                                     | PORTD Data Latch when written: PORTD pins when read      |                    |                |                |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE                                                     | _                                                        | _                  | _              | _              | _            | RE2         | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH                                                    | Write Buffer for the upper 5 bits of the Program Counter |                    |                |                |              |             |               |           | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON                                                    | GIE                                                      | PEIE               | TOIE           | INTE           | RBIE         | TOIF        | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1                                                      | PSPIF                                                    | (6)                | -              | _              | SSPIF        | CCP1IF      | TMR2IF        | TMR1IF    | 00 0000                  | 00 0000                                        |

| 0Dh                  | _                                                         | Unimpleme                                                | nted               |                |                | •            |             |               |           | _                        | _                                              |

| 0Eh                  | TMR1L                                                     | Holding reg                                              | ister for the I    | _east Signific | ant Byte of t  | he 16-bit TM | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H                                                     | Holding reg                                              | ister for the I    | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON                                                     | _                                                        | _                  | T1CKPS1        | T1CKPS0        | T10SCEN      | T1SYNC      | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2                                                      | Timer2 mod                                               | dule's registe     | r              | •              |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON                                                     | _                                                        | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON      | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF                                                    | Synchronou                                               | us Serial Por      | t Receive Bu   | ffer/Transmit  | Register     |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON                                                    | WCOL                                                     | SSPOV              | SSPEN          | CKP            | SSPM3        | SSPM2       | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L Capture/Compare/PWM1 (LSB)                         |                                                          |                    |                |                |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H Capture/Compare/PWM1 (MSB)                         |                                                          |                    |                |                |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON                                                   | ON — — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0           |                    |                |                |              |             |               |           | 00 0000                  | 00 0000                                        |

| 18h-1Fh              | — Unimplemented                                           |                                                          |                    |                |                |              |             |               | •         | _                        | _                                              |

$\begin{tabular}{ll} Legend: & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented location read as '0'. \end{tabular}$

Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

- $\hbox{6:} \quad \hbox{PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear. } \\$

### PIC16C6X

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### FIGURE 4-12: PIE1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 8Ch)

| RW-0     | R/W-0                                     | U-0        | U-0          | R/W-0         | R/W-0  | R/W-0  | R/W-0  |                                                                              |

|----------|-------------------------------------------|------------|--------------|---------------|--------|--------|--------|------------------------------------------------------------------------------|

| _        | _                                         | _          | _            | SSPIE         | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                             |

| bit7     |                                           |            |              |               |        |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7-6: | Reserved:                                 | Always ma  | intain thes  | e bits clear. |        |        |        |                                                                              |

| bit 5-4: | Unimpleme                                 | ented: Rea | ad as '0'    |               |        |        |        |                                                                              |

| bit 3:   | SSPIE: Syn<br>1 = Enables<br>0 = Disables | the SSP i  |              |               |        |        |        |                                                                              |

| bit 2:   | CCP1IE: C0<br>1 = Enables<br>0 = Disables | the CCP1   | I interrupt  | bit           |        |        |        |                                                                              |

| bit 1:   | TMR2IE: TM<br>1 = Enables<br>0 = Disables | the TMR2   | 2 to PR2 m   |               |        |        |        |                                                                              |

| bit 0:   | TMR1IE: TM<br>1 = Enables<br>0 = Disables | the TMR1   | 1 overflow i | nterrupt      | t      |        |        |                                                                              |

**TABLE 5-11: PORTE FUNCTIONS**

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                                 |

|--------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Read control input in parallel slave port mode.  RD  1 = Not a read operation 0 = Read operation. The system reads the PORTD register (if chip selected)        |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Write control input in parallel slave port mode.  WR  1 = Not a write operation 0 = Write operation. The system writes to the PORTD register (if chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Chip select control input in parallel slave port mode.  CS  1 = Device is not selected 0 = Device is selected                                                   |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port (PSP) mode.

#### TABLE 5-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|---------------------------|-------|-------|--------------------------|---------------------------|

| 09h     | PORTE | _     | _     | _     | _       | _     | RE2                       | RE1   | RE0   | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE |       | PORTE Data Direction Bits |       | Bits  | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells not used by PORTE.

#### TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                        | Name   | Bit 7                      | Bit 6   | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | ,    | Valu<br>all o<br>res |      |

|--------------------------------|--------|----------------------------|---------|---------------------|---------------------|---------|--------|---------|---------|-------------------|------|----------------------|------|

| 0Bh,8Bh<br>10Bh,18Bh           | INTCON | GIE                        | PEIE    | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000                 | 000u |

| 0Ch                            | PIR1   | PSPIF <sup>(2)</sup>       | (3)     | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000                 | 0000 |

| 8Ch                            | PIE1   | PSPIE <sup>(2)</sup>       | (3)     | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000                 | 0000 |

| 11h                            | TMR2   | 2 Timer2 module's register |         |                     |                     |         |        |         |         | 0000              | 0000 | 0000                 | 0000 |

| 12h                            | T2CON  | _                          | TOUTPS3 | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000                 | 0000 |

| 92h PR2 Timer2 Period register |        |                            |         |                     |                     |         |        |         |         | 1111              | 1111 | 1111                 | 1111 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer2. Note 1: The USART is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

<sup>2:</sup> Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

<sup>3:</sup> PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### 11.4 I<sup>2</sup>C™ Overview

This section provides an overview of the Inter-Integrated Circuit (I<sup>2</sup>C) bus, with Section 11.5 discussing the operation of the SSP module in I<sup>2</sup>C mode.

The I<sup>2</sup>C bus is a two-wire serial interface developed by the Philips<sup>®</sup> Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. The enhanced specification (fast mode) is also supported. This device will communicate with both standard and fast mode devices if attached to the same bus. The clock will determine the data rate.

The I<sup>2</sup>C interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXX software. Table 11-3 defines some of the I<sup>2</sup>C bus terminology. For additional information on the I<sup>2</sup>C interface specification, refer to the Philips document "The I<sup>2</sup>C bus and how to use it." #939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- · Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the I<sup>2</sup>C bus is limited only by the maximum bus loading specification of 400 pF.

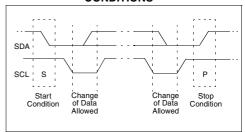

## 11.4.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. Figure 11-14 shows the START and STOP conditions. The master generates these conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

FIGURE 11-14: START AND STOP CONDITIONS

TABLE 11-3: I<sup>2</sup>C BUS TERMINOLOGY

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- · START condition

- · STOP condition

- · Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an  $\overline{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

TABLE 11-5: REGISTERS ASSOCIATED WITH I2C OPERATION

| Address                 | Name    | Bit 7                            | Bit 6              | Bit 5                    | Bit 4     | Bit 3      | Bit 2    | Bit 1  | Bit 0  | PC   | e on<br>DR,<br>DR | Value<br>other | on all<br>resets |

|-------------------------|---------|----------------------------------|--------------------|--------------------------|-----------|------------|----------|--------|--------|------|-------------------|----------------|------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                              | PEIE               | TOIE                     | INTE      | RBIE       | TOIF     | INTF   | RBIF   | 0000 | 000x              | 0000           | 000u             |

| 0Ch                     | PIR1    | PSPIF <sup>(1)</sup>             | (2)                | RCIF                     | TXIF      | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 | 0000              | 0000           | 0000             |

| 8Ch                     | PIE1    | PSPIE <sup>(1)</sup>             | (2)                | RCIE                     | TXIE      | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 | 0000              | 0000           | 0000             |

| 13h                     | SSPBUF  | Synchrono                        | us Serial          | Port Rece                | ive Buffe | r/Transmit | Register |        |        | xxxx | xxxx              | uuuu           | uuuu             |

| 93h                     | SSPADD  | Synchrono                        | us Serial          | Port (I <sup>2</sup> C ı | mode) Ad  | ldress Re  | gister   |        |        | 0000 | 0000              | 0000           | 0000             |

| 14h                     | SSPCON  | WCOL                             | SSPOV              | SSPEN                    | CKP       | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000              | 0000           | 0000             |

| 94h                     | SSPSTAT | SMP <sup>(3)</sup>               | CKE <sup>(3)</sup> | D/Ā                      | Р         | S          | R/W      | UA     | BF     | 0000 | 0000              | 0000           | 0000             |

| 87h                     | TRISC   | SC PORTC Data Direction register |                    |                          |           |            |          |        |        |      |                   | 1111           | 1111             |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.} \\ Shaded cells are not used by SSP module in SPI mode.}$

- Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

- 2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

- The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'.

#### FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0        | R/W-0                                                    | R/W-0                        | R/W-0          | U-0          | R-0           | R-0          | R-x          |        |                 |

|--------------|----------------------------------------------------------|------------------------------|----------------|--------------|---------------|--------------|--------------|--------|-----------------|

| SPEN<br>bit7 | RX9                                                      | SREN                         | CREN           |              | FERR          | OERR         | RX9D<br>bit0 |        |                 |

|              | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p | s RC7/RX/I<br>port enable    | DT and RC<br>d | 6/TX/CK p    | oins as seri  | al port pins | when bits    | TRIS   | C<7:6> are set) |

|              | RX9: 9-bit  <br>1 = Selects<br>0 = Selects               | 9-bit rece                   | otion          |              |               |              |              |        |                 |

| bit 5:       | SREN: Sin                                                | gle Receive                  | e Enable b     | it           |               |              |              |        |                 |

|              | Asynchrone<br>Don't care                                 | ous mode                     |                |              |               |              |              |        |                 |

|              | Synchrono<br>1 = Enable<br>0 = Disable<br>This bit is o  | s single red<br>es single re | ceive          | ı is comple  | ite.          |              |              |        |                 |

|              | Synchrono<br>Unused in                                   |                              | <u>slave</u>   |              |               |              |              |        |                 |

| bit 4:       | CREN: Cor                                                | ntinuous Re                  | eceive Ena     | ble bit      |               |              |              |        |                 |

|              | Asynchrone<br>1 = Enable<br>0 = Disable                  | s continuo                   |                |              |               |              |              |        |                 |

|              | Synchrono<br>1 = Enable<br>0 = Disable                   | s continuo                   |                | until enable | e bit CREN    | l is cleared | (CREN ove    | erride | es SREN)        |

| bit 3:       | Unimplem                                                 | ented: Rea                   | ad as '0'      |              |               |              |              |        |                 |

|              | FERR: Fraing<br>1 = Framing<br>0 = No fran               | g error (Ca                  |                | ed by reac   | ling RCRE     | G register a | and receive  | next   | valid byte)     |

|              | OERR: Over                                               |                              |                | nd hy clear  | ing bit CRI   | =NI)         |              |        |                 |

|              | 0 = No ove                                               | •                            | ii be cieaie   | o by olear   | ing bit Oi it | _14)         |              |        |                 |

#### 13.2 Oscillator Configurations

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 13.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power CrystalXT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

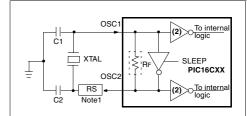

## 13.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

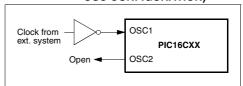

In LP, XT, or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 13-4). The PIC16CXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in LP, XT, or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 13-5).

# FIGURE 13-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 13-1, Table 13-3, Table 13-2 and Table 13-4 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- For the PIC16C61 the buffer is on the OSC2 pin, all other devices have the buffer on the OSC1 pin.

## FIGURE 13-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

TABLE 13-9: STATUS BITS AND THEIR SIGNIFICANCE FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |

| 0   | x   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

Legend: x = unknown, u = unchanged

TABLE 13-10: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C61/62/64/65

|                                    | Program Counter       | STATUS    | PCON <sup>(2)</sup> |

|------------------------------------|-----------------------|-----------|---------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0 -                 |

| MCLR reset during normal operation | 000h                  | 000u uuuu | u-                  |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | u-                  |

| WDT Reset                          | 000h                  | 0000 luuu | u-                  |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | u-                  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | u-                  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

2: The PCON register is not implemented on the PIC16C61.

TABLE 13-11: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

|                                    | Program Counter       | STATUS    | PCON |

|------------------------------------|-----------------------|-----------|------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0x   |

| MCLR reset during normal operation | 000h                  | 000u uuuu | uu   |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | uu   |

| WDT Reset                          | 000h                  | 0000 luuu | uu   |

| Brown-out Reset                    | 000h                  | 0001 1uuu | u0   |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | uu   |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | uu   |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

TABLE 13-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

| Register |    | Applicable Devices |     |     |    |     |    |     |     | \$ |     |     | Power-on Reset<br>Brown-out<br>Reset | MCLR Reset during:  - normal operation  - SLEEP WDT Reset | Wake-up via<br>interrupt or<br>WDT Wake-up |           |           |

|----------|----|--------------------|-----|-----|----|-----|----|-----|-----|----|-----|-----|--------------------------------------|-----------------------------------------------------------|--------------------------------------------|-----------|-----------|

| TRISD    | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 1111 1111                                  | 1111 1111 | uuuu uuuu |

| TRISE    | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0000 -111                                  | 0000 -111 | uuuu -uuu |

| PIE1     | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 00 0000                                    | 00 0000   | uu uuuu   |

|          | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0000 0000                                  | 0000 0000 | uuuu uuuu |

| PIE2     | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0                                          | 0         | u         |

| PCON     | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0u                                         | uu        | uu        |

| FCON     | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0-                                         | u-        | u-        |

| PR2      | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 1111 1111                                  | 1111 1111 | 1111 1111 |

| SSPADD   | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0000 0000                                  | 0000 0000 | uuuu uuuu |

| SSPSTAT  | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 00 0000                                    | 00 0000   | uu uuuu   |

| TXSTA    | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0000 -010                                  | 0000 -010 | uuuu -uuu |

| SPBRG    | 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66                                   | 67                                                        | 0000 0000                                  | 0000 0000 | uuuu uuuu |

$<sup>\</sup>label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

<sup>3:</sup> See Table 13-10 and Table 13-11 for reset value for specific conditions.

| BTFSS             | Bit Test                   | f, Skip if \$                                    | Set                       |                  |   | CALL              | Call Sub                              | routine                                               |                                         |                               |  |  |

|-------------------|----------------------------|--------------------------------------------------|---------------------------|------------------|---|-------------------|---------------------------------------|-------------------------------------------------------|-----------------------------------------|-------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] B         | ΓFSS f,b                                         |                           |                  |   | Syntax:           | [ label ]                             | CALL k                                                |                                         |                               |  |  |

| Operands:         | $0 \le f \le 12$           |                                                  |                           |                  |   | Operands:         | $0 \leq k \leq 2047$                  |                                                       |                                         |                               |  |  |

|                   | $0 \le b < 7$              |                                                  |                           |                  |   | Operation:        | (PC)+ 1-                              | $(PC)+1 \rightarrow TOS$ ,                            |                                         |                               |  |  |

| Operation:        | skip if (f<                | <b>) = 1</b>                                     |                           |                  |   | •                 | $k \rightarrow PC$                    | ,                                                     |                                         |                               |  |  |

| Status Affected:  | None                       |                                                  |                           |                  |   |                   | $(PCLATH<4:3>) \rightarrow PC<12:11>$ |                                                       |                                         |                               |  |  |

| Encoding:         | 01                         | 11bb                                             | bfff                      | ffff             |   | Status Affected:  | None                                  |                                                       |                                         |                               |  |  |

| Description:      |                            | register 'f' i                                   |                           | he next          | ı | Encoding:         | 10                                    | 0kkk                                                  | kkkk                                    | kkkk                          |  |  |

|                   | If bit 'b' is<br>discarded | n is execute '1', then the and a NOF haking this | e next instr<br>is execut | ed               |   | Description:      | (PC+1) is<br>eleven bit<br>into PC bi | outine. Firs<br>pushed or<br>immediate<br>its <10:0>. | to the stace<br>address is<br>The upper | k. The<br>s loaded<br>bits of |  |  |

| Words:            | 1                          |                                                  |                           |                  |   |                   |                                       | e loaded fr<br>ycle instruc                           |                                         | H. CALL                       |  |  |

| Cycles:           | 1(2)                       |                                                  |                           |                  |   | Words:            | 1                                     | ,                                                     |                                         |                               |  |  |

| Q Cycle Activity: | Q1                         | Q2                                               | Q3                        | Q4               |   | Cycles:           | 2                                     |                                                       |                                         |                               |  |  |

|                   | Decode                     | Read<br>register 'f'                             | Process<br>data           | No-<br>Operation |   | Q Cycle Activity: | Q1                                    | Q2                                                    | Q3                                      | Q4                            |  |  |

| If Skip:          | (2nd Cyc                   | ole)                                             |                           |                  |   | 1st Cycle         | Decode                                | Read<br>literal 'k'.                                  | Process<br>data                         | Write to<br>PC                |  |  |

| •                 | Q1                         | Q2                                               | Q3                        | Q4               | 1 |                   |                                       | Push PC<br>to Stack                                   | data                                    | 10                            |  |  |

|                   | No-<br>Operation           | No-<br>Operation                                 | No-<br>Operation          | No-<br>Operation |   | 2nd Cycle         | No-<br>Operation                      | No-<br>Operation                                      | No-<br>Operation                        | No-<br>Operation              |  |  |

| Example           | HERE<br>FALSE<br>TRUE      | BTFSC<br>GOTO<br>•                               | FLAG, 1<br>PROCESS        | _CODE            |   | Example           | HERE Before In                        | truction                                              | ddress HE                               |                               |  |  |

|                   |                            | struction                                        |                           |                  |   |                   |                                       |                                                       | ddress TH<br>ddress HE                  |                               |  |  |

|                   |                            |                                                  | address I                 | HERE             |   |                   |                                       | 103 = A                                               | uuitss HE                               | VE+T                          |  |  |

|                   | After Inst                 | truction<br>if FLAG<1:                           | > = 0.                    |                  |   |                   |                                       |                                                       |                                         |                               |  |  |

|                   |                            | PC =                                             | address F                 | ALSE             |   |                   |                                       |                                                       |                                         |                               |  |  |

|                   |                            | PC =                                             |                           | ALSE             |   |                   |                                       |                                                       |                                         |                               |  |  |

if FLAG<1> = 1, PC = address TRUE

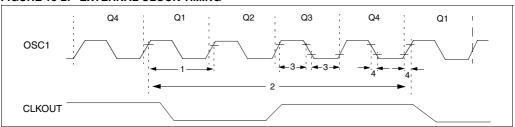

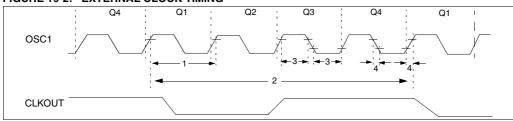

#### 15.5 <u>Timing Diagrams and Specifications</u>

FIGURE 15-2: EXTERNAL CLOCK TIMING

TABLE 15-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|---------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|               | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|               |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|               |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|               |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|               |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|               |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|               |       |                                  | 1   | _    | 4      | MHz   | HS osc mode (-04)  |

|               |       |                                  | 1   | _    | 20     | MHz   | HS osc mode (-20)  |

| 1             | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|               |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|               |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|               |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|               |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|               |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|               |       |                                  | 250 | _    | 1,000  | ns    | HS osc mode (-04)  |

|               |       |                                  | 50  | _    | 1,000  | ns    | HS osc mode (-20)  |

|               |       |                                  | 5   |      | _      | μS    | LP osc mode        |

| 2             | Tcy   | Instruction Cycle Time (Note 1)  | 1.0 | Tcy  | DC     | μS    | Tcy = 4/Fosc       |

| 3             | TosL, | External Clock in (OSC1) High or | 50  | _    | _      | ns    | XT oscillator      |

|               | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|               |       |                                  | 10  |      | _      | ns    | HS oscillator      |

| 4             | TosR, | External Clock in (OSC1) Rise or | 25  | _    | _      | ns    | XT oscillator      |

|               | TosF  | Fall Time                        | 50  |      | _      | ns    | LP oscillator      |

|               |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

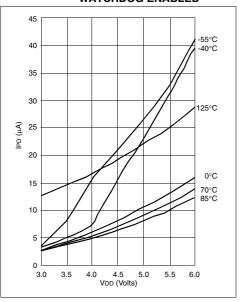

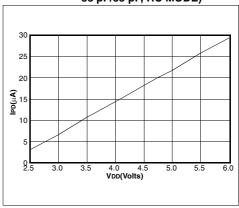

FIGURE 16-8: MAXIMUM IPD vs. VDD WATCHDOG ENABLED\*

\*IPD, with Watchdog Timer enabled, has two components: The leakage current which increases with higher temperature and the operating current of the Watchdog Timer logic which increases with lower temperature. At -40°C, the latter dominates explaining the apparently anomalous behavior.

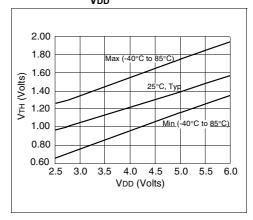

FIGURE 16-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs.

DC CHARACTERISTICS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

17.3 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial)

> PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial) PIC16LC62/64-04 (Commercial, Industrial)

> > Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C  $\leq$  TA  $\leq$  +85°C for industrial and

0°C

$\leq$  TA  $\leq$  +70°C for commercial

Operating voltage VDD range as described in DC spec Section 17.1

and Section 17.2

|       | and Section 17.2                   |       |         |     |         |       |                                                    |  |  |  |  |  |

|-------|------------------------------------|-------|---------|-----|---------|-------|----------------------------------------------------|--|--|--|--|--|

| Param | Characteristic                     | Sym   | Min     | Тур | Max     | Units | Conditions                                         |  |  |  |  |  |

| No.   |                                    |       |         | t   |         |       |                                                    |  |  |  |  |  |

|       | Input Low Voltage                  |       |         |     |         |       |                                                    |  |  |  |  |  |

|       | I/O ports                          | VIL   |         |     |         |       |                                                    |  |  |  |  |  |

| D030  | with TTL buffer                    |       | Vss     | -   | 0.15VDD | V     | For entire VDD range                               |  |  |  |  |  |

| D030A |                                    |       | Vss     | -   | V8.0    | V     | $4.5V \le V_{DD} \le 5.5V$                         |  |  |  |  |  |

| D031  | with Schmitt Trigger buffer        |       | Vss     | -   | 0.2Vdd  | V     |                                                    |  |  |  |  |  |

| D032  | MCLR, OSC1 (in RC mode)            |       | Vss     | -   | 0.2Vdd  | V     |                                                    |  |  |  |  |  |

| D033  | OSC1 (in XT, HS and LP)            |       | Vss     | -   | 0.3VDD  | V     | Note1                                              |  |  |  |  |  |

|       | Input High Voltage                 |       |         |     |         |       |                                                    |  |  |  |  |  |

|       | I/O ports                          | VIH   |         |     |         |       |                                                    |  |  |  |  |  |

| D040  | with TTL buffer                    |       | 2.0     | -   | VDD     | V     | $4.5V \le V_{DD} \le 5.5V$                         |  |  |  |  |  |

| D040A |                                    |       | 0.25VDD | -   | VDD     | V     | For entire VDD range                               |  |  |  |  |  |

|       |                                    |       | + 0.8V  |     |         |       |                                                    |  |  |  |  |  |

|       |                                    |       |         |     |         |       |                                                    |  |  |  |  |  |

| D041  | with Schmitt Trigger buffer        |       | 0.8VDD  | -   | VDD     |       | For entire VDD range                               |  |  |  |  |  |

| D042  | MCLR                               |       | 0.8VDD  | -   | VDD     | V     |                                                    |  |  |  |  |  |

| D042A | OSC1 (XT, HS and LP)               |       | 0.7VDD  | -   | VDD     | V     | Note1                                              |  |  |  |  |  |

| D043  | OSC1 (in RC mode)                  |       | 0.9VDD  | -   | VDD     | V     |                                                    |  |  |  |  |  |

| D070  | PORTB weak pull-up current         | IPURB | 50      | 200 | 400     | μΑ    | VDD = 5V, VPIN = VSS                               |  |  |  |  |  |

|       | Input Leakage Current (Notes 2, 3) |       |         |     |         |       |                                                    |  |  |  |  |  |

| D060  | I/O ports                          | II∟   | -       | -   | ±1      | μА    | $Vss \leq VPIN \leq VDD, \ Pin \ at \ hiimpedance$ |  |  |  |  |  |

| D061  | MCLR, RA4/T0CKI                    |       | -       | -   | ±5      | μΑ    | $Vss \le VPIN \le VDD$                             |  |  |  |  |  |

| D063  | OSC1                               |       | -       | -   | ±5      | μΑ    | $Vss \le VPIN \le VDD$ , XT, HS and                |  |  |  |  |  |

|       |                                    |       |         |     |         |       | LP osc configuration                               |  |  |  |  |  |

|       | Output Low Voltage                 |       |         |     |         |       |                                                    |  |  |  |  |  |

| D080  | I/O ports                          | VOL   | -       | -   | 0.6     | V     | IOL = 8.5  mA, VDD = 4.5V,                         |  |  |  |  |  |

|       |                                    |       |         |     |         |       | -40°C to +85°C                                     |  |  |  |  |  |

| D083  | OSC2/CLKOUT (RC osc config)        |       | -       | -   | 0.6     | V     | IOL = 1.6  mA, VDD = 4.5V,                         |  |  |  |  |  |

|       |                                    |       |         |     |         |       | -40°C to +85°C                                     |  |  |  |  |  |

|       | Output High Voltage                |       |         |     |         |       |                                                    |  |  |  |  |  |

| D090  | I/O ports (Note 3)                 | Vон   | VDD-0.7 | -   | -       | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C       |  |  |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)        |       | VDD-0.7 | -   | -       | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +85°C       |  |  |  |  |  |

| D150* | Open-Drain High Voltage            | Vod   | -       | -   | 14      | V     | RA4 pin                                            |  |  |  |  |  |

| l     |                                    |       | I .     |     |         |       | •                                                  |  |  |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

#### 19.5 Timing Diagrams and Specifications

FIGURE 19-2: EXTERNAL CLOCK TIMING

TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2                | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 50  | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  | _   |      | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

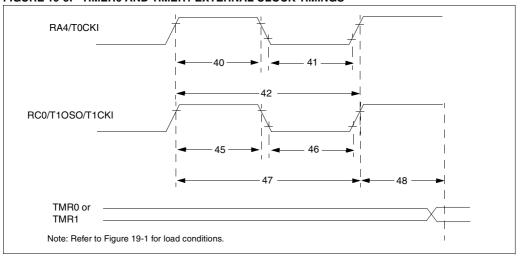

FIGURE 19-5: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 19-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                              | Characteristic    |                    |                                    | Typ† | Max   | Units    | Conditions                         |

|--------------|-------|---------------------------------------------|-------------------|--------------------|------------------------------------|------|-------|----------|------------------------------------|

| 40*          | Tt0H  | T0CKI High Pulse V                          | Vidth             | No Prescaler       | 0.5Tcy + 20                        |      |       | ns       | Must also meet                     |

| 40           | 11011 | Tooki riigiri uise v                        | Vidiri            | With Prescaler     | 10                                 |      |       |          | parameter 42                       |

| 41*          | TtOL  |                                             |                   | No Prescaler       | 0.5Tcy + 20                        | _    | _     | ns<br>ns | Must also meet                     |

| 41           | TIOL  | TOCKI LOW Fulse W                           | /Idili            | With Prescaler     | 10                                 |      |       | ns       | parameter 42                       |

| 42*          | Tt0P  | T0CKI Period                                |                   | No Prescaler       | Tcy + 40                           | H    |       | ns       | paramotor 12                       |

|              | 1.0.  |                                             |                   | With Prescaler     |                                    | _    | _     | ns       | N = prescale value                 |

|              |       |                                             |                   | With Freedomen     | 20 or Tcy + 40                     |      |       | 110      | (2, 4,, 256)                       |

|              |       |                                             |                   |                    | N                                  |      |       |          | , , , ,                            |

| 45*          | Tt1H  | T1CKI High Time                             | Synchronous, P    | rescaler = 1       | 0.5Tcy + 20                        | _    | _     | ns       | Must also meet                     |

|              |       |                                             | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _    | _     | ns       | parameter 47                       |

|              |       |                                             | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _    | _     | ns       |                                    |

|              |       |                                             | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _    | _     | ns       |                                    |

|              |       |                                             |                   | PIC16 <b>LC</b> 6X | 50                                 | _    | _     | ns       |                                    |

| 46*          | Tt1L  | T1CKI Low Time                              | Synchronous, P    | rescaler = 1       | 0.5TCY + 20                        | _    | _     | ns       | Must also meet                     |

|              |       |                                             | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _    | _     | ns       | parameter 47                       |

|              |       |                                             | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _    | _     | ns       |                                    |

|              |       |                                             | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _    | _     | ns       |                                    |

|              |       |                                             |                   | PIC16 <b>LC</b> 6X | 50                                 | _    | _     | ns       |                                    |

| 47*          | Tt1P  | T1CKI input period                          | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N | _    | _     | ns       | N = prescale value<br>(1, 2, 4, 8) |

|              |       |                                             |                   | PIC16 <b>LC</b> 6X | Greater of:<br>50 OR TCY + 40<br>N |      |       |          | N = prescale value<br>(1, 2, 4, 8) |

|              |       |                                             | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                 | _    | _     | ns       |                                    |

|              |       |                                             |                   | PIC16 <b>LC</b> 6X | 100                                | _    | _     | ns       |                                    |

|              | Ft1   | Timer1 oscillator inp                       |                   |                    | DC                                 | _    | 200   | kHz      |                                    |

|              |       | (oscillator enabled by setting bit T1OSCEN) |                   |                    |                                    |      |       |          |                                    |

| 48           |       | Delay from external                         |                   |                    | 2Tosc                              | _    | 7Tosc | _        |                                    |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

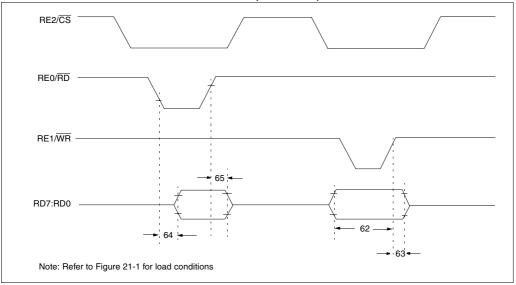

FIGURE 21-8: PARALLEL SLAVE PORT TIMING (PIC16CR65)

TABLE 21-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16CR65)

| Parameter No. | Sym      | Characteristic                        |                                            |    | Typ† | Max | Units | Conditions |

|---------------|----------|---------------------------------------|--------------------------------------------|----|------|-----|-------|------------|

| 62*           | TdtV2wrH | Data in valid before WR↑ or CS↑ (setu | ta in valid before WR↑ or CS↑ (setup time) |    |      | _   | ns    |            |

| 63*           | TwrH2dtI | WR↑ or CS↑ to data–in invalid (hold   | PIC16 <b>CR</b> 65                         | 20 | _    | _   | ns    |            |

|               |          | time)                                 | PIC16LCR65                                 | 35 | _    | _   | ns    |            |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid         | S√ to data–out valid                       |    | _    | 80  | ns    |            |

| 65*           | TrdH2dtl | RD↑ or CS↑ to data–out invalid        |                                            | 10 | _    | 30  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

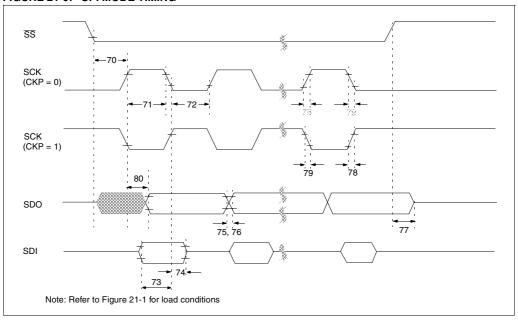

#### FIGURE 21-9: SPI MODE TIMING

**TABLE 21-8: SPI MODE REQUIREMENTS**

| Parameter No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|---------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71*           | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72*           | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75*           | TdoR                  | SDO data output rise time                | l        | 10   | 25  | ns    |            |

| 76*           | TdoF                  | SDO data output fall time                | l        | 10   | 25  | ns    |            |

| 77*           | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78*           | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79*           | TscF                  | SCK output fall time (master mode)       |          | 10   | 25  | ns    |            |

| 80*           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

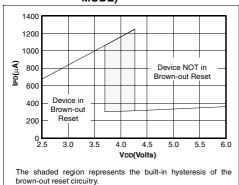

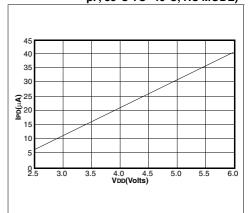

FIGURE 23-8: TYPICAL IPD vs. VDD BROWN-OUT DETECT ENABLED (RC MODE)

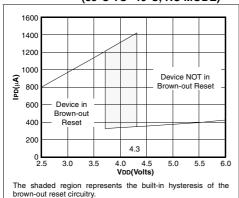

FIGURE 23-9: MAXIMUM IPD vs. VDD BROWN-OUT DETECT ENABLED (85°C TO -40°C, RC MODE)

FIGURE 23-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)