Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

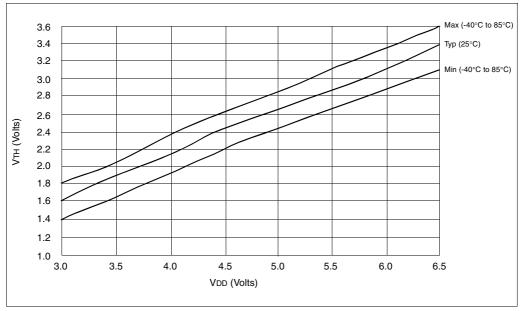

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-20i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16CXX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C61** device has 36 bytes of RAM and 13 I/O pins. In addition a timer/counter is available.

The **PIC16C62/62A/R62** devices have 128 bytes of RAM and 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI<sup>TM</sup>) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus.

The **PIC16C63/R63** devices have 192 bytes of RAM, while the **PIC16C66** has 368 bytes. All three devices have 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit ( $I^2C$ ) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also know as a Serial Communications Interface or SCI.

The **PIC16C64/64A/R64** devices have 128 bytes of RAM and 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. An 8-bit Parallel Slave Port is also provided.

The **PIC16C65/65A/R65** devices have 192 bytes of RAM, while the **PIC16C67** has 368 bytes. All four devices have 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmit-

ter (USART) is also known as a Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is also provided.

The PIC16C6X device family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers a power saving mode. The user can wake the chip from SLEEP through several external and internal interrupts, and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C6X family fits perfectly in applications ranging from high-speed automotive and appliance control to low-power remote sensors, keyboards and telecom processors. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use, and I/O flexibility make the PIC16C6X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions, and co-processor applications).

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16CXX family of devices (Appendix B).

## 1.2 Development Support

PIC16C6X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 15.0 for more details about Microchip's development tools.

## 4.0 MEMORY ORGANIZATION

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

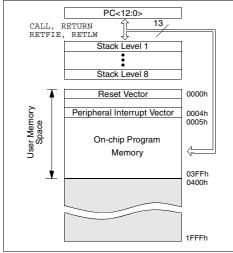

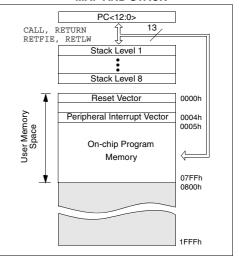

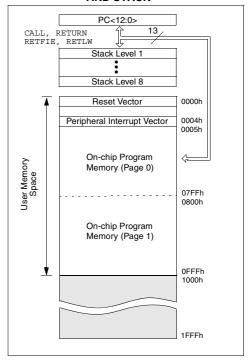

### 4.1 Program Memory Organization

The PIC16C6X family has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C61  | 1K x 14           | 0000h-03FFh   |

| PIC16C62  | 2K x 14           | 0000h-07FFh   |

| PIC16C62A | 2K x 14           | 0000h-07FFh   |

| PIC16CR62 | 2K x 14           | 0000h-07FFh   |

| PIC16C63  | 4K x 14           | 0000h-0FFFh   |

| PIC16CR63 | 4K x 14           | 0000h-0FFFh   |

| PIC16C64  | 2K x 14           | 0000h-07FFh   |

| PIC16C64A | 2K x 14           | 0000h-07FFh   |

| PIC16CR64 | 2K x 14           | 0000h-07FFh   |

| PIC16C65  | 4K x 14           | 0000h-0FFFh   |

| PIC16C65A | 4K x 14           | 0000h-0FFFh   |

| PIC16CR65 | 4K x 14           | 0000h-0FFFh   |

| PIC16C66  | 8K x 14           | 0000h-1FFFh   |

| PIC16C67  | 8K x 14           | 0000h-1FFFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 4-1: PIC16C61 PROGRAM MEMORY MAP AND STACK

### FIGURE 4-2: PIC16C62/62A/R62/64/64A/ R64 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-3: PIC16C63/R63/65/65A/R65 PROGRAM MEMORY MAP AND STACK

| Address              | Name    | Bit 7                      | Bit 6              | Bit 5          | Bit 4          | Bit 3         | Bit 2           | Bit 1        | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------------|--------------------|----------------|----------------|---------------|-----------------|--------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                            |                    |                |                |               |                 |              |           |                          | ·                                              |

| 00h <sup>(1)</sup>   | INDF    | Addressing                 | this location      | uses conter    | ts of FSR to   | address data  | a memory (n     | ot a physica | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod                 | lule's registe     | r              |                |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co                 | ounter's (PC)      | Least Signif   | icant Byte     |               |                 |              |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>         | RP1 <sup>(5)</sup> | RP0            | TO             | PD            | Z               | DC           | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data              | a memory ad        | dress pointe   | r              |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | -                          | _                  | PORTA Dat      | a Latch wher   | n written: PO | RTA pins wh     | en read      |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat                  | ta Latch whe       | n written: PC  | ORTB pins wi   | nen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da                   | ta Latch whe       | n written: PC  | ORTC pins w    | hen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat                  | ta Latch whe       | n written: PC  | ORTD pins w    | hen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                            | —                  | _              | _              | —             | RE2             | RE1          | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  |                            | _                  | _              | Write Buffer   | for the uppe  | r 5 bits of the | e Program C  | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                        | PEIE               | TOIE           | INTE           | RBIE          | TOIF            | INTF         | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF                      | (6)                | _              | 1              | SSPIF         | CCP1IF          | TMR2IF       | TMR1IF    | 00 0000                  | 00 0000                                        |

| 0Dh                  | _       | Unimpleme                  | nted               |                |                |               |                 |              |           | —                        | _                                              |

| 0Eh                  | TMR1L   | Holding reg                | ister for the L    | east Signific  | ant Byte of t  | he 16-bit TM  | R1 register     |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg                | ister for the M    | /lost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | -                          | _                  | T1CKPS1        | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS       | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod                 | lule's registe     | r              |                |               |                 |              |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   |                            | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1      | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou                 | us Serial Port     | Receive Bu     | ffer/Transmit  | Register      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                       | SSPOV              | SSPEN          | СКР            | SSPM3         | SSPM2           | SSPM1        | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Compare/PWM1 (LSB) |                    |                |                |               |                 | xxxx xxxx    | uuuu uuuu |                          |                                                |

| 16h                  | CCPR1H  | Capture/Compare/PWM1 (MSB) |                    |                |                |               | uuuu uuuu       |              |           |                          |                                                |

| 17h                  | CCP1CON | —                          | —                  | CCP1X          | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1       | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h-1Fh              | _       | Unimpleme                  | nted               |                |                |               |                 |              |           | _                        |                                                |

### TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

## 9.0 TIMER2 MODULE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

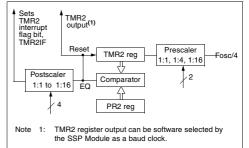

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

### 9.1 Timer2 Prescaler and Postscaler

### Applicable Devices

## 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

### 9.2 Output of TMR2

## Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

## FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

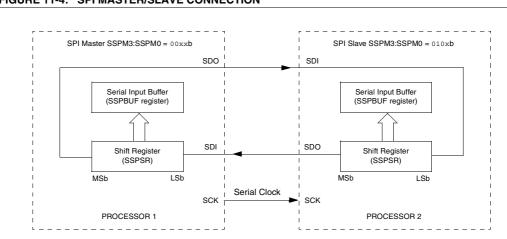

To enable the serial port, SSP enable bit SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear enable bit SSPEN, re-initialize SSPCON register, and then set enable bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if implemented)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

## FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the software protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5 and Figure 11-6 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

Γ

## FIGURE 11-8: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)(PIC16C66/67)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                               | R/W-0                                                                                                                                      | R/W-0                                                                                                 | R/W-0                                                                                         | R/W-0                                              | R/W-0                   |                                                                                                                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                     | SSPEN                                                                                                                               | CKP                                                                                                                                        | SSPM3                                                                                                 | SSPM2                                                                                         | SSPM1                                              | SSPM0                   | R = Readable bit<br>W = Writable bit                                                                             |

| oit7     |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                     |                                                                                                                                            |                                                                                                       |                                                                                               |                                                    | bit0                    | U = Unimplemented bit, rea<br>as '0'<br>- n =Value at POR reset                                                  |

| bit 7:   | WCOL: W<br>1 = The SS<br>(must be c<br>0 = No col                                                                                                                                                                                                                                                                                                                                                         | SPBUF reg                                                                                                                           | gister is wi                                                                                                                               |                                                                                                       | e it is still ti                                                                              | ransmitting                                        | g the previo            | us word                                                                                                          |

| bit 6:   | SSPOV: R                                                                                                                                                                                                                                                                                                                                                                                                  | eceive Ov                                                                                                                           | erflow Indi                                                                                                                                | cator bit                                                                                             |                                                                                               |                                                    |                         |                                                                                                                  |

|          | the data in<br>if only tran                                                                                                                                                                                                                                                                                                                                                                               | byte is rece<br>SSPSR is<br>smitting da<br>tion (and t                                                                              | lost. Over<br>ata, to avo                                                                                                                  | flow can c<br>bid setting                                                                             | only occur<br>overflow.                                                                       | in slave m<br>n master                             | ode. The us             | revious data. In case of overflo<br>er must read the SSPBUF, eve<br>verflow bit is not set since eac<br>egister. |

|          | $\frac{\ln l^2 C \mod}{1 = A \text{ byte}}$<br>in transmit<br>0 = No over                                                                                                                                                                                                                                                                                                                                 | is received<br>mode. SS                                                                                                             |                                                                                                                                            |                                                                                                       |                                                                                               |                                                    |                         | us byte. SSPOV is a "don't car                                                                                   |

| oit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                  | ynchronou                                                                                                                           | is Serial P                                                                                                                                | ort Enable                                                                                            | bit                                                                                           |                                                    |                         |                                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                           | es serial po                                                                                                                        |                                                                                                                                            |                                                                                                       |                                                                                               |                                                    | is serial por<br>t pins | t pins                                                                                                           |

|          | <ul> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li><u>In I<sup>2</sup>C mode</u></li> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li>In both modes, when enabled, these pins must be properly configured as input or output.</li> </ul> |                                                                                                                                     |                                                                                                                                            |                                                                                                       |                                                                                               |                                                    |                         |                                                                                                                  |

| bit 4:   | <b>CKP</b> : Cloc<br>In SPI mod<br>1 = Idle sta<br>0 = Idle sta<br>In $I^2C$ mod<br>SCK relea<br>1 = Enable<br>0 = Holds                                                                                                                                                                                                                                                                                  | <u>de</u><br>ate for cloc<br>ate for cloc<br><u>de</u><br>se control<br>e clock                                                     | k is a high<br>k is a low                                                                                                                  | level                                                                                                 | to ensure                                                                                     | data setu                                          | p time)                 |                                                                                                                  |

| bit 3-0: | $0110 =  ^{2}(0)$ $0111 =  ^{2}(0)$ $1011 =  ^{2}(0)$ $1110 =  ^{2}(0)$                                                                                                                                                                                                                                                                                                                                   | PI master r<br>PI master r<br>PI master r<br>PI master r<br>PI slave mo<br>CI slave mo<br>CI slave mo<br>CI slave mo<br>CI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock<br>ode, clock<br>de, 7-bit a<br>de, 10-bit<br>controllec<br>de, 7-bit a | k = Fosc/.<br>k = Fosc/.<br>k = Fosc/.<br>k = TMR2<br>= SCK pir address address I master m address wi | 4<br>64<br>output/2<br>a. <u>SS</u> pin c<br>a. <u>SS</u> pin c<br>node (slave<br>th start an | ontrol ena<br>ontrol disa<br>e idle)<br>d stop bit |                         |                                                                                                                  |

### 13.8 Power-down Mode (SLEEP)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, status bit  $\overline{PD}$  (STATUS<3>) is cleared, status bit  $\overline{TO}$  (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, and disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC).

#### 13.8.1 WAKE-UP FROM SLEEP

The device can wake from SLEEP through one of the following events:

- 1. External reset input on MCLR/VPP pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or some peripheral interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. USART TX or RX (synchronous slave mode).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the subset of the new provide the instruction after the subset (on address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 13.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### Instruction Descriptions 14.1

| Add Lite                                                                                                                | ral and                                                                                                                                                                             | w                                                      |                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ <i>label</i> ] ADDLW k                                                                                                |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| $0 \le k \le 255$                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| (W) + k –                                                                                                               | → (W)                                                                                                                                                                               |                                                        |                                                                                                                                                                                                                                                |

| C, DC, Z                                                                                                                |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| 11                                                                                                                      | 111x                                                                                                                                                                                | kkkk                                                   | kkkk                                                                                                                                                                                                                                           |

| The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| 1                                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| 1                                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                |

| Q1                                                                                                                      | Q2                                                                                                                                                                                  | Q3                                                     | Q4                                                                                                                                                                                                                                             |

| Decode                                                                                                                  | Read<br>literal 'k'                                                                                                                                                                 | Process<br>data                                        | Write to<br>W                                                                                                                                                                                                                                  |

| After Inst                                                                                                              | W =<br>ruction                                                                                                                                                                      | 0x10<br>0x25                                           |                                                                                                                                                                                                                                                |

|                                                                                                                         | [ <i>label</i> ] Al<br>$0 \le k \le 2\xi$<br>(W) + k -<br>C, DC, Z<br>11<br>The conte<br>added to the<br>result is pl<br>1<br>1<br>Q1<br>Decode<br>ADDLW<br>Before In<br>After Inst | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$ | $0 \le k \le 255$ (W) + k → (W) C, DC, Z $11  111x  kkkk$ The contents of the W register added to the eight bit literal 'k' result is placed in the W regist 1 1 2 2 2 2 2 3 2 2 2 3 2 2 3 2 3 2 3 3 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |

| ANDLW             | AND Lite                                  | eral with                | W               |               |  |

|-------------------|-------------------------------------------|--------------------------|-----------------|---------------|--|

| Syntax:           | [ <i>label</i> ] A                        | [ <i>label</i> ] ANDLW k |                 |               |  |

| Operands:         | $0 \le k \le 25$                          | 55                       |                 |               |  |

| Operation:        | (W) .AND                                  | D. (k) $\rightarrow$ (   | W)              |               |  |

| Status Affected:  | Z                                         |                          |                 |               |  |

| Encoding:         | 11                                        | 1001                     | kkkk            | kkkk          |  |

| Description:      | The conter<br>AND'ed wird<br>result is pl | th the eig               | ht bit literal  | 'k'. The      |  |

| Words:            | 1                                         |                          |                 |               |  |

| Cycles:           | 1                                         |                          |                 |               |  |

| Q Cycle Activity: | Q1                                        | Q2                       | Q3              | Q4            |  |

|                   | Decode                                    | Read<br>literal "k"      | Process<br>data | Write to<br>W |  |

| Example           | ANDLW                                     | 0x5F                     |                 |               |  |

|                   | Before In                                 | struction                |                 |               |  |

|                   | After Inst                                |                          | 0xA3            |               |  |

|                   |                                           | W =                      | 0x03            |               |  |

| ADDWF             | Add W and f                                                                                                                                                               |                         |                 |                         |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------------|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                                        | DDWF                    | f,d             |                         |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |                         |                 |                         |  |

| Operation:        | (W) + (f) $\rightarrow$ (destination)                                                                                                                                     |                         |                 |                         |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                  |                         |                 |                         |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff                    |  |

| Description:      | Add the contents of the W register with<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |                         |                 |                         |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                         |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                         |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4                      |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to<br>destination |  |

| Evennle           | ADDUE                                                                                                                                                                     | BOD                     | <u>.</u>        |                         |  |

| Example           | ADDWF                                                                                                                                                                     |                         | 0               |                         |  |

|                   | Before In                                                                                                                                                                 | structior               | ו<br>0x17       |                         |  |

|                   | W = 0x17<br>FSR = 0xC2                                                                                                                                                    |                         |                 |                         |  |

|                   | After Inst                                                                                                                                                                |                         |                 |                         |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                         |  |

| ANDWF             | AND W v                                                        | vith f                    |                 |                      |

|-------------------|----------------------------------------------------------------|---------------------------|-----------------|----------------------|

| Syntax:           | [ <i>label</i> ] Al                                            | NDWF                      | f,d             |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                         |                 |                      |

| Operation:        | (W) .AND                                                       | 0. (f) $\rightarrow$ (e   | destinatio      | on)                  |

| Status Affected:  | Z                                                              |                           |                 |                      |

| Encoding:         | 0.0                                                            | 0101                      | dfff            | ffff                 |

| Description:      | AND the W<br>is 0 the res<br>ter. If 'd' is<br>register 'f'.   | sult is stor<br>1 the res | red in the      | W regis-             |

| Words:            | 1                                                              |                           |                 |                      |

| Cycles:           | 1                                                              |                           |                 |                      |

| Q Cycle Activity: | Q1                                                             | Q2                        | Q3              | Q4                   |

|                   | Decode                                                         | Read<br>register<br>'f'   | Process<br>data | Write to destination |

| Example           | ANDWF                                                          | FSR,                      | 1               |                      |

|                   | Before In                                                      |                           |                 |                      |

|                   |                                                                | W =<br>FSR =              | 0x17<br>0xC2    |                      |

|                   | After Inst                                                     |                           | 0102            |                      |

|                   |                                                                | W =                       | 0x17            |                      |

|                   |                                                                | FSR =                     | 0x02            |                      |

| NOP               | No Operation |                  |                  |                  |  |

|-------------------|--------------|------------------|------------------|------------------|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |

| Operands:         | None         |                  |                  |                  |  |

| Operation:        | No opera     | ition            |                  |                  |  |

| Status Affected:  | None         |                  |                  |                  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |

| Description:      | No operat    | ion.             |                  |                  |  |

| Words:            | 1            |                  |                  |                  |  |

| Cycles:           | 1            |                  |                  |                  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |

|                   | Decode       | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |

| Example           | NOP          |                  |                  |                  |  |

| RETFIE                       | Return from Interrupt                                                                                                         |                               |                                              |                       |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|-----------------------|--|

| Syntax:                      | [ label ]                                                                                                                     | RETFIE                        |                                              |                       |  |

| Operands:                    | None                                                                                                                          |                               |                                              |                       |  |

| Operation:                   | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                       |                               |                                              |                       |  |

| Status Affected:             | None                                                                                                                          |                               |                                              |                       |  |

| Encoding:                    | 00                                                                                                                            | 0000                          | 0000                                         | 1001                  |  |

|                              | PC. Interrupts are enabled by setting<br>Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |                               |                                              |                       |  |

|                              | Global Inte<br>(INTCON<                                                                                                       | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |  |

| Words:                       | Global Inte<br>(INTCON<                                                                                                       | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |  |

| Words:<br>Cycles:            | Global Inte<br>(INTCON<<br>instruction                                                                                        | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |  |

|                              | Global Inte<br>(INTCON<<br>instruction                                                                                        | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |  |

| Cycles:                      | Global Inte<br>(INTCON<<br>instruction<br>1<br>2                                                                              | errupt Ena<br>(7>). This      | ble bit, GIE<br>is a two cy                  | E<br>cle              |  |

| Cycles:<br>Q Cycle Activity: | Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1                                                                        | Q2<br>No-                     | ble bit, GIE<br>is a two cy<br>Q3<br>Set the | cle<br>Q4<br>Pop from |  |

After Interrupt PC = TOS GIE = 1

| OPTION                            | Load Option Register                                                                                                                                                                                                                                    |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                           | [label] OPTION                                                                                                                                                                                                                                          |  |  |  |

| Operands:                         | None                                                                                                                                                                                                                                                    |  |  |  |

| Operation:                        | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                |  |  |  |

| Status Affected:                  | None                                                                                                                                                                                                                                                    |  |  |  |

| Encoding:                         | 00 0000 0110 0010                                                                                                                                                                                                                                       |  |  |  |

| Description:<br>Words:<br>Cycles: | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it.<br>1 |  |  |  |

| Example                           | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                      |  |  |  |

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

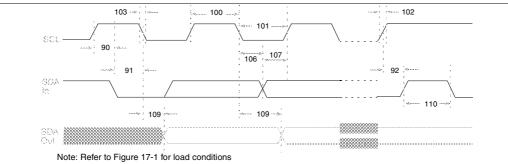

## FIGURE 17-10: I<sup>2</sup>C BUS DATA TIMING

### TABLE 17-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Тнідн   | Clock high time        | 100 kHz mode | 4.0        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     |      |       |                                                  |

| 102              | TR      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        |      | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | —          | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

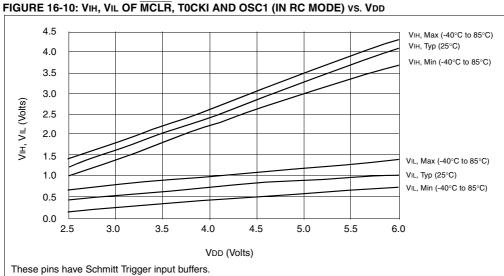

## 20.0 ELECTRICAL CHARACTERISTICS FOR PIC16C63/65A

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                              | 55°C to +125°C             |

|-------------------------------------------------------------------------------------------------------------|----------------------------|

| Storage temperature                                                                                         | 65°C to +150°C             |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                          | 0.3V to (VDD + 0.3V)       |

| Voltage on VDD with respect to VSS                                                                          | 0.3V to +7.5V              |

| Voltage on MCLR with respect to Vss (Note 2)                                                                |                            |

| Voltage on RA4 with respect to Vss                                                                          | 0V to +14V                 |

| Total power dissipation (Note 1)                                                                            | 1.0W                       |

| Maximum current out of Vss pin                                                                              |                            |

| Maximum current into VDD pin                                                                                | 250 mA                     |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                     |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ±20 mA                     |

| Maximum output current sunk by any I/O pin                                                                  |                            |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                      |

| Maximum current sunk by PORTA, PORTB, and PORTE (Note 3) (combined)                                         | 200 mA                     |

| Maximum current sourced by PORTA, PORTB, and PORTE (Note 3) (combined)                                      | 200 mA                     |

| Maximum current sunk by PORTC and PORTD (Note 3) (combined)                                                 | 200 mA                     |

| Maximum current sourced by PORTC and PORTD (Note 3) (combined)                                              | 200 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | ′он) x Iон} + ∑(Vol x Iol) |

- Note 2: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE not available on the PIC16C63.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 20-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C63-04<br>PIC16C65A-04                                                                                 | PIC16C63-10<br>PIC16C65A-10                                                                 | PIC16C63-20<br>PIC16C65A-20                                                                 | PIC16LC63-04<br>PIC16LC65A-04                                                                           | JW Devices                                                                                              |  |