Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64at-04i-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

г

### FIGURE 4-19: PIR1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 0Ch)

| R/W-0         | R/W-0                                                                                                                                                                                   | R-0                                                                                                                                                              | R-0                                    | R/W-0                                 | R/W-0                                | R/W-0       | R/W-0          |                                                                                                                                                |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|--------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PSPIF<br>bit7 | —                                                                                                                                                                                       | RCIF                                                                                                                                                             | TXIF                                   | SSPIF                                 | CCP1IF                               | TMR2IF      | TMR1IF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |

| bit 7:        | <b>PSPIF:</b> Parallel Slave Port Interrupt Flag bit<br>1 = A read or a write operation has taken place (must be cleared in software)<br>0 = No read or write operation has taken place |                                                                                                                                                                  |                                        |                                       |                                      |             |                |                                                                                                                                                |  |  |

| bit 6:        | Reserved:                                                                                                                                                                               | Always ma                                                                                                                                                        | intain this I                          | bit clear.                            |                                      |             |                |                                                                                                                                                |  |  |

| bit 5:        | <b>RCIF:</b> USA<br>1 = The US<br>0 = The US                                                                                                                                            | SART receiv                                                                                                                                                      | /e buffer is                           | full (cleared                         | d by reading                         | RCREG)      |                |                                                                                                                                                |  |  |

| bit 4:        | <b>TXIF:</b> USA<br>1 = The US<br>0 = The US                                                                                                                                            | SART trans                                                                                                                                                       | nit buffer is                          | empty (cle                            | eared by writ                        | ing to TXRE | EG)            |                                                                                                                                                |  |  |

| bit 3:        | 1 = The tra                                                                                                                                                                             | SSPIF: Synchronous Serial Port Interrupt Flag bit<br>1 = The transmission/reception is complete (must be cleared in software)<br>0 = Waiting to transmit/receive |                                        |                                       |                                      |             |                |                                                                                                                                                |  |  |

| bit 2:        | 0 = No TMI<br>Compare M                                                                                                                                                                 | ode<br>1 register c<br>R1 register<br><u>Aode</u><br>1 register c<br>R1 register<br><u>e</u>                                                                     | apture occi<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | be cleared i<br>ed (must be o<br>red | ,           | oftware)       |                                                                                                                                                |  |  |

| bit 1:        | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TMI                                                                                                                                           | to PR2 mat                                                                                                                                                       | ch occurred                            | d (must be                            | bit<br>cleared in so                 | ftware)     |                |                                                                                                                                                |  |  |

| bit 0:        | TMR1IF: TMR1 Overflow Interrupt Flag bit         1 = TMR1 register overflow occurred (must be cleared in software)         0 = No TMR1 register overflow occurred                       |                                                                                                                                                                  |                                        |                                       |                                      |             |                |                                                                                                                                                |  |  |

| global        |                                                                                                                                                                                         | GIE (INTC                                                                                                                                                        |                                        |                                       |                                      |             |                | corresponding enable bit or the<br>rupt flag bits are clear prior to                                                                           |  |  |

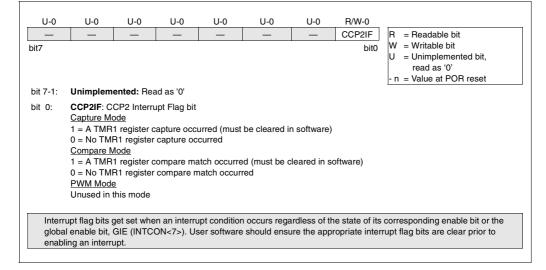

#### 4.2.2.7 PIR2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 4-21: PIR2 REGISTER (ADDRESS 0Dh)

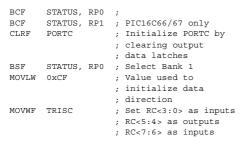

### 5.3 PORTC and TRISC Register

### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

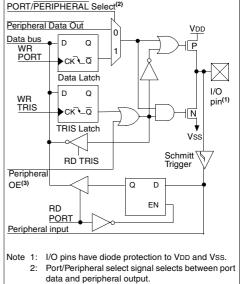

PORTC is an 8-bit wide bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### EXAMPLE 5-3: INITIALIZING PORTC

### FIGURE 5-6: PORTC BLOCK DIAGRAM

3: Peripheral OE (output enable) is only activated if peripheral select is active.

### TABLE 5-5: PORTC FUNCTIONS FOR PIC16C62/64

| Name            | Bit# | Buffer Type | Function                                                                    |

|-----------------|------|-------------|-----------------------------------------------------------------------------|

| RC0/T1OSI/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator input or Timer1 clock input      |

| RC1/T1OSO       | bit1 | ST          | Input/output port pin or Timer1 oscillator output                           |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).      |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                |

| RC6             | bit6 | ST          | Input/output port pin                                                       |

| RC7             | bit7 | ST          | Input/output port pin                                                       |

Legend: ST = Schmitt Trigger input

## TABLE 5-6:PORTC FUNCTIONS FOR PIC16C62A/R62/64A/R64

| Name            | Bit# | Buffer Type | Function                                                                              |

|-----------------|------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input               |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                      |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture input/Compare output/PWM1 output                     |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 |             | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                          |

| RC6             | bit6 | ST          | Input/output port pin                                                                 |

| RC7             | bit7 | ST          | Input/output port pin                                                                 |

Legend: ST = Schmitt Trigger input

### TABLE 5-7: PORTC FUNCTIONS FOR PIC16C63/R63/65/65A/R65/66/67

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input                        |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                    |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit, or USART Syn-<br>chronous Clock          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive, or USART Syn-<br>chronous Data            |

Legend: ST = Schmitt Trigger input

### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6      | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|------------|-------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6        | RC5         | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC D | Data Direc | tion Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

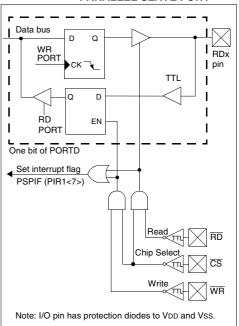

## 5.7 Parallel Slave Port

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD operates as an 8-bit wide parallel slave port (microprocessor port) when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input (RE0/ $\overline{\text{RD}}$ ) and  $\overline{\text{WR}}$  control input pin (RE1/ $\overline{\text{WR}}$ ).

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$  lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

### FIGURE 5-11: PORTD AND PORTE AS A PARALLEL SLAVE PORT

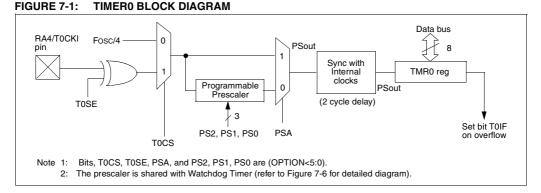

#### 7.0 TIMER0 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

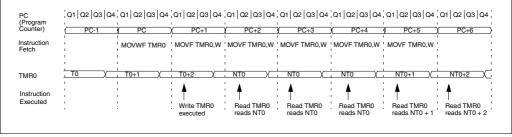

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing bit T0CS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 TMR0 Interrupt

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the TImer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

© 1997-2013 Microchip Technology Inc.

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                 | Name    | Bit 7                | Bit 6                         | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|-------------------------|---------|----------------------|-------------------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                          | TOIE                   | INTE       | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                     | PIR1    | PSPIF <sup>(1)</sup> | (2)                           | RCIF                   | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                     | PIE1    | PSPIE <sup>(1)</sup> | (2)                           | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                     | SSPBUF  | Synchrono            | us Serial                     | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                     | SSPADD  | Synchrono            | us Serial                     | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                     | SSPCON  | WCOL                 | SSPOV                         | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                     | SSPSTAT | SMP <sup>(3)</sup>   | CKE <sup>(3)</sup>            | D/A                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                     | TRISC   | PORTC Da             | PORTC Data Direction register |                        |            |            |          |        |        | 1111 1111               | 1111 1111                 |

### TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

3: The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'. NOTES:

-

| COMF                                                                                    | Complement f                                                                                                                                                                                                                                                                                                                                                                                       | DECFSZ            | Decrement f, Skip if 0                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                 | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                                                                                                                          | Syntax:           | [label] DECFSZ f,d                                                                                                                                                                                                                                                 |

| Operands:                                                                               | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                        | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                    |

| Operation:                                                                              | $(\bar{f}) \rightarrow (destination)$                                                                                                                                                                                                                                                                                                                                                              | Operation:        | (f) - 1 $\rightarrow$ (destination);                                                                                                                                                                                                                               |

| Status Affected:                                                                        | Z                                                                                                                                                                                                                                                                                                                                                                                                  |                   | skip if result = 0                                                                                                                                                                                                                                                 |

| Encoding:                                                                               | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                  | Status Affected:  | None                                                                                                                                                                                                                                                               |

| Description:                                                                            | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in                                                                                                                                                                                                                                                                                                            | Encoding:         | 00 1011 dfff ffff                                                                                                                                                                                                                                                  |

| Words:<br>Cycles:                                                                       | W. If 'd' is 1 the result is stored back in<br>register 'f'.<br>1                                                                                                                                                                                                                                                                                                                                  | Description:      | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is |

| Q Cycle Activity:                                                                       | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                        |                   | executed instead making it a 2TCY instruc-<br>tion.                                                                                                                                                                                                                |

| , ,                                                                                     | Decode Read Process Write to                                                                                                                                                                                                                                                                                                                                                                       | Words:            | 1                                                                                                                                                                                                                                                                  |

|                                                                                         | register data destination                                                                                                                                                                                                                                                                                                                                                                          | Cycles:           | 1(2)                                                                                                                                                                                                                                                               |

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                    | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                        |

| Example                                                                                 | COMF REG1, 0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                 | , ,               | Decode Read Process Write to register 'f' data destination                                                                                                                                                                                                         |

|                                                                                         | $\begin{array}{rcl} REG1 &=& 0x13\\ After Instruction & \\ REG1 &=& 0x13\\ W &=& 0xEC \end{array}$                                                                                                                                                                                                                                                                                                 | lf Skip:          | Q1         Q2         Q3         Q4           No-<br>Operation         Operation         Operation         Operation                                                                                                                                               |

| DECF                                                                                    | Decrement f                                                                                                                                                                                                                                                                                                                                                                                        |                   |                                                                                                                                                                                                                                                                    |

| Syntax:                                                                                 | [ <i>label</i> ] DECF f,d                                                                                                                                                                                                                                                                                                                                                                          | Example           | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                    |

| Operands:                                                                               | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                  |                   | CONTINUE •                                                                                                                                                                                                                                                         |

|                                                                                         | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                          |                   | •                                                                                                                                                                                                                                                                  |

| Operation:                                                                              | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                               |                   | •<br>Before Instruction                                                                                                                                                                                                                                            |

| Operation:<br>Status Affected:                                                          |                                                                                                                                                                                                                                                                                                                                                                                                    |                   | •<br>Before Instruction<br>PC = address HERE                                                                                                                                                                                                                       |

| •                                                                                       | (f) - 1 $\rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                                                |                   | PC = address HERE<br>After Instruction                                                                                                                                                                                                                             |

| Status Affected:                                                                        | (f) - 1 → (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is                                                                                                                                                                                                                                                      |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE                                                                                                                                                                    |

| Status Affected:<br>Encoding:                                                           | (f) - 1 → (destination)<br>Z<br>00 0011 dfff ffff                                                                                                                                                                                                                                                                                                                                                  |                   | $\begin{array}{rcl} PC &=& address {}_{HERE}\\ \textbf{After Instruction}\\ & CNT &=& CNT-1\\ & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                            |

| Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | (f) - 1 $\rightarrow$ (destination)<br>Z<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                                                                                                                                                                                                               |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE                                                                                                                                                                    |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | (f) - 1 $\rightarrow$ (destination)<br>Z<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                                                                                                                                                                                                               |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1                                                                                                                                                                                |                   | $\begin{array}{rcl} PC &=& address \mbox{ HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \mbox{ continue} \\ \mbox{if CNT} &\neq& 0, \\ \end{array}$                                                               |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination                                                                                                             |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $ \begin{array}{c c} (f) - 1 \rightarrow (destination) \\ \hline Z \\ \hline 00 & 0011 & dfff & ffff \\ \hline Decrement register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. \\ 1 & & \\ 1 & & \\ Q1 & Q2 & Q3 & Q4 \\ \hline \hline Decode & Read & Process & Write to destination \\ \hline & & \\ f'' & & \\ \end{array} $ |                   | $\begin{array}{rcl} PC &=& address {}_{HERE}\\ \textbf{After Instruction}\\ & CNT &=& CNT-1\\ & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                            |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00  0011  dfff  ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>2<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01                                                       |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 → (destination)<br>Z<br>00 0011 dfff fff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>register data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01<br>Z = 0                                                     |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00  0011  dfff  ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>2<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01                                                       |                   | $\begin{array}{rcl} PC &=& address \mbox{ HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \mbox{ continue} \\ \mbox{if CNT} &\neq& 0, \\ \end{array}$                                                               |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 15.1 DC Characteristics: PIC16C61-04 (Commercial, Industrial, Extended) PIC16C61-20 (Commercial, Industrial, Extended)

|              |                                                                   | Standa                                                                                | rd Opei | rating | Condi | tions (ı | unless otherwise stated)                                       |  |  |  |

|--------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------|--------|-------|----------|----------------------------------------------------------------|--|--|--|

|              | ACTERISTICS                                                       | $Operating \ temperature  -40^{\circ}C  \leq TA \leq +125^{\circ}C \ for \ extended,$ |         |        |       |          |                                                                |  |  |  |

| DC CHAR      | ACTERISTICS                                                       | -40°C $\leq$ TA $\leq$ +85°C for industrial and                                       |         |        |       |          |                                                                |  |  |  |

|              |                                                                   |                                                                                       |         |        | 0°0   | C ≤      | $TA \leq +70^{\circ}C$ for commercial                          |  |  |  |

| Param<br>No. | Characteristic                                                    | Sym                                                                                   | Min     | Тур†   | Max   | Units    | Conditions                                                     |  |  |  |

| D001         | Supply Voltage                                                    | Vdd                                                                                   | 4.0     | -      | 6.0   | V        | XT, RC and LP osc configuration                                |  |  |  |

| D001A        |                                                                   |                                                                                       | 4.5     | -      | 5.5   | V        | HS osc configuration                                           |  |  |  |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                                                                                   | -       | 1.5    | -     | V        |                                                                |  |  |  |

| D003         | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                                                                                  | -       | Vss    | -     | V        | See section on Power-on Reset for details                      |  |  |  |

| D004*        | VDD rise rate to ensure<br>internal Power-on<br>Reset signal      | SVDD                                                                                  | 0.05    | -      | -     | V/ms     | See section on Power-on Reset for details                      |  |  |  |

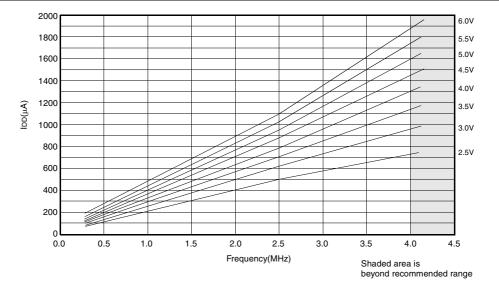

| D010         | Supply Current (Note 2)                                           | IDD                                                                                   | -       | 1.8    | 3.3   | mA       | Fosc = 4 MHz, VDD = 5.5V (Note 4)                              |  |  |  |

| D013         |                                                                   |                                                                                       | -       | 13.5   | 30    | mA       | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V              |  |  |  |

| D020         | Power-down Current                                                | IPD                                                                                   | -       | 7      | 28    | μA       | VDD = 4.0V, WDT enabled, -40°C to +85°C                        |  |  |  |

| D021         | (Note 3)                                                          |                                                                                       | -       | 1.0    | 14    | μA       | VDD = 4.0V, WDT disabled, -0°C to +70°C                        |  |  |  |

| D021A        |                                                                   |                                                                                       | -       | 1.0    | 16    | μA       | VDD = 4.0V, WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$     |  |  |  |

| D021B        |                                                                   |                                                                                       | -       | 1.0    | 20    | μA       | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

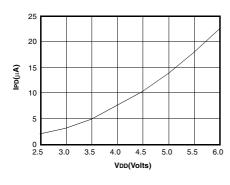

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

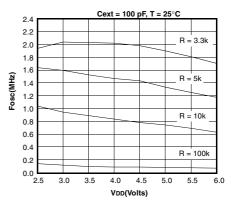

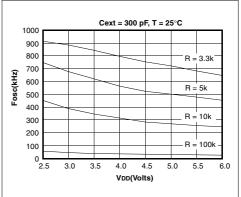

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# 15.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp             | S                              |                   | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|------------------------|--------------------------------|-------------------|-----------|----------------------------------------|

| 2. TppS                |                                |                   | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                      |                                |                   |           |                                        |

| F                      | Frequency                      |                   | т         | Time                                   |

| Lowercas               | e letters (pp) and their meani | ngs:              |           |                                        |

| рр                     |                                |                   |           |                                        |

| сс                     | CCP1                           |                   | OSC       | OSC1                                   |

| ck                     | CLKOUT                         |                   | rd        | RD                                     |

| CS                     | CS                             |                   | rw        | RD or WR                               |

| di                     | SDI                            |                   | SC        | SCK                                    |

| do                     | SDO                            |                   | SS        | SS                                     |

| dt                     | Data in                        |                   | t0        | TOCKI                                  |

| io                     | I/O port                       |                   | t1        | T1CKI                                  |

| mc                     | MCLR                           |                   | wr        | WR                                     |

|                        | e letters and their meanings:  |                   | 1         |                                        |

| S                      |                                |                   |           |                                        |

| F                      | Fall                           |                   | Р         | Period                                 |

| Н                      | High                           |                   | R         | Rise                                   |

| I                      | Invalid (Hi-impedance)         |                   | V         | Valid                                  |

| L                      | Low                            |                   | Z         | Hi-impedance                           |

| I <sup>2</sup> C only  |                                |                   |           |                                        |

| AA                     | output access                  |                   | High      | High                                   |

| BUF                    | Bus free                       |                   | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> | C specifications only)         |                   |           |                                        |

| CC                     |                                |                   |           |                                        |

| HD                     | Hold                           |                   | SU        | Setup                                  |

| ST                     |                                |                   |           |                                        |

| DAT                    | DATA input hold                |                   | STO       | STOP condition                         |

| STA                    | START condition                |                   |           |                                        |

| FIGURE 15              | -1: LOAD CONDITIONS            | FOR DEVICE        | TIMING SP | PECIFICATIONS                          |

|                        | Load condition 1               |                   |           | Load condition 2                       |

|                        | Load condition 1               |                   |           | Load condition 2                       |

|                        | VD                             | D/2               |           |                                        |

|                        | (                              |                   |           |                                        |

|                        | <                              | ⊧<br>≥ RL         |           |                                        |

|                        | <                              | > '``             |           |                                        |

|                        |                                |                   |           |                                        |

|                        | Pin =                          | CL                |           |                                        |

|                        | FIII .                         | 7                 | Г         | - III                                  |

|                        | Vs                             | SS                |           | Vss                                    |

|                        | $RL = 464\Omega$               |                   |           |                                        |

|                        |                                | all pins except C |           | ІТ                                     |

|                        |                                | OSC2 output       |           |                                        |

|                        | - 1                            |                   |           |                                        |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

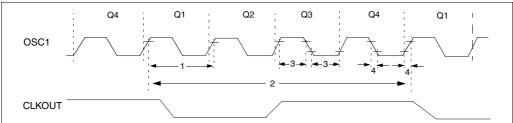

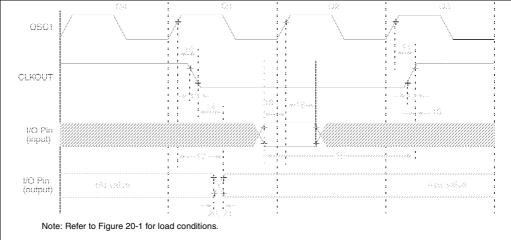

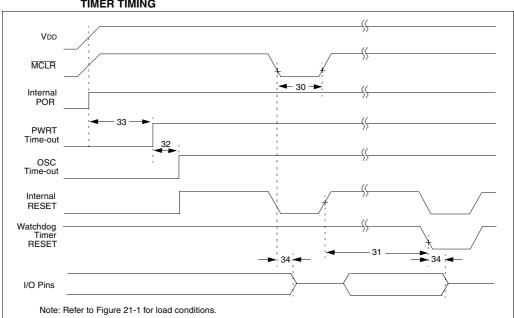

# 15.5 <u>Timing Diagrams and Specifications</u>

### FIGURE 15-2: EXTERNAL CLOCK TIMING

## TABLE 15-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 1   | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | 1   | _    | 20     | MHz   | HS osc mode (-20)  |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | —      | μs    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 1,000  | ns    | HS osc mode (-04)  |

|                  |       |                                  | 50  | _    | 1,000  | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 1.0 | Тсү  | DC     | μs    | TCY = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 50  | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | —      | μs    | LP oscillator      |

|                  |       |                                  | 10  | _    | —      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | 25  | _    | _      | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | 50  | _    | —      | ns    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 18.1 DC Characteristics: PIC16C62A/R62/64A/R64-04 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-10 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-20 (Commercial, Industrial, Extended)

| DC CHA        |                                                                  | <b>Standar</b><br>Operatir |            |            | ə -40      | )°C ≤  | unless otherwise stated)<br>$TA \le +125^{\circ}C$ for extended,                   |

|---------------|------------------------------------------------------------------|----------------------------|------------|------------|------------|--------|------------------------------------------------------------------------------------|

|               |                                                                  |                            |            |            | -4(<br>0°( |        | $\leq$ TA $\leq$ +85°C for industrial and<br>$\leq$ TA $\leq$ +70°C for commercial |

| Param<br>No.  | Characteristic                                                   | Sym                        | Min        | Тур†       | Max        | Units  | Conditions                                                                         |

| D001<br>D001A | Supply Voltage                                                   | Vdd                        | 4.0<br>4.5 | -          | 6.0<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                            |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | Vdr                        | -          | 1.5        | -          | V      |                                                                                    |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                       | -          | Vss        | -          | V      | See section on Power-on Reset for details                                          |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                       | 0.05       | -          | -          | V/ms   | See section on Power-on Reset for details                                          |

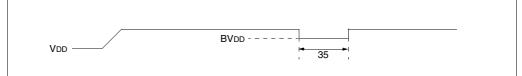

| D005          | Brown-out Reset Voltage                                          | Bvdd                       | 3.7        | 4.0        | 4.3        | V      | BODEN bit in configuration word enabled                                            |

|               |                                                                  |                            | 3.7        | 4.0        | 4.4        | v      | Extended Range Only                                                                |

| D010          | Supply Current (Note 2, 5)                                       | Idd                        | -          | 2.7        | 5          | mA     | XT, RC, osc configuration Fosc = 4 MHz,<br>VDD = 5.5V (Note 4)                     |

| D013          |                                                                  |                            | -          | 10         | 20         | mA     | HS osc configuration FOSC = 20 MHz,<br>VDD = 5.5V                                  |

| D015*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor              | -          | 350        | 425        | μA     | BOR enabled, VDD = 5.0V                                                            |

| D020          | Power-down Current (Note                                         | IPD                        | -          | 10.5       | 42         | μA     | VDD = 4.0V, WDT enabled, -40°C to +85°C                                            |

| D021          | 3, 5)                                                            |                            | -          | 1.5        | 16         | μA     | VDD = 4.0V, WDT disabled, $-0^{\circ}C$ to $+70^{\circ}C$                          |

| D021A         |                                                                  |                            | -          | 1.5<br>2.5 | 19         | μA     | $V_{DD} = 4.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$                   |

| D021B         |                                                                  |                            | -          | 2.5        | 19         | μA     | VDD = 4.0V, WDT disabled, -40°C to +125°C                                          |

| D023*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor              | -          | 350        | 425        | μA     | BOR enabled, VDD = 5.0V                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

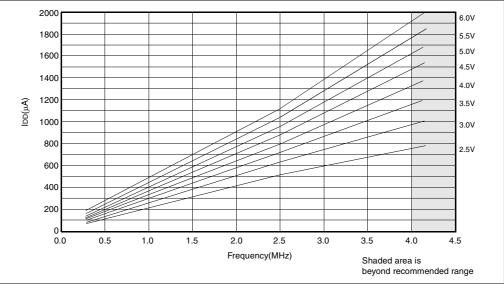

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 19.1 DC Characteristics: PIC16C65-04 (Commercial, Industrial) PIC16C65-10 (Commercial, Industrial) PIC16C65-20 (Commercial, Industrial)

| Standard Operating Conditions (unless otherwise stated) |                                                                                                           |      |            |                    |                   |                |                                                                                                                                                                                                                                                               |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------------|--------------------|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC CHA                                                  | <b>DC CHARACTERISTICS</b> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and |      |            |                    |                   |                |                                                                                                                                                                                                                                                               |

|                                                         |                                                                                                           |      |            |                    | 0°0               | C ≤            | $\leq$ TA $\leq$ +70°C for commercial                                                                                                                                                                                                                         |

| Param<br>No.                                            | Characteristic                                                                                            | Sym  | Min        | Тур†               | Max               | Units          | Conditions                                                                                                                                                                                                                                                    |

| D001<br>D001A                                           | Supply Voltage                                                                                            | Vdd  | 4.0<br>4.5 | -                  | 6.0<br>5.5        | v<br>v         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                       |