Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                             |

| Data Converters            | - ·                                                                      |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

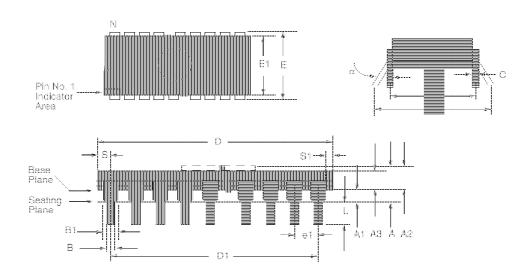

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c65a-04-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7                | Bit 6                                                                       | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------|-----------------------------------------------------------------------------|---------------|----------------|---------------|-------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                      |                                                                             |               |                |               |             |               |           |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing           | this location                                                               | uses conter   | ts of FSR to   | address data  | a memory (n | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod           | lule's registe                                                              | r             |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)                                                               | Least Signi   | ficant Byte    |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP                  | RP1                                                                         | RP0           | TO             | PD            | Z           | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat         | ndirect data memory address pointer                                         |               |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | _                    | _                                                                           | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da             | ta Latch whe                                                                | n written: PC | ORTB pins wi   | nen read      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | ta Latch whe                                                                | n written: PO | ORTC pins w    | hen read      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da             | ORTD Data Latch when written: PORTD pins when read                          |               |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | —                    | —                                                                           | —             | —              | —             | RE2         | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                    | — — Write Buffer for the upper 5 bits of the Program Counter                |               |                |               |             |               |           | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE                                                                        | TOIE          | INTE           | RBIE          | T0IF        | INTF          | RBIF      | 0000 000x                | 0000 0000                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(6)</sup> | (4)                                                                         | RCIF          | TXIF           | SSPIF         | CCP1IF      | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | —                    | —                                                                           |               |                | —             | —           | —             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg          | Holding register for the Least Significant Byte of the 16-bit TMR1 register |               |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg          | ister for the I                                                             | Most Signific | ant Byte of th | ne 16-bit TMF | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                    | _                                                                           | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod           | lule's registe                                                              | r             |                |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | —                    | TOUTPS3                                                                     | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON      | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou           | us Serial Por                                                               | t Receive Bu  | ffer/Transmit  | Register      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                                       | SSPEN         | СКР            | SSPM3         | SSPM2       | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWM                                                                   | 1 (LSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWM                                                                   | 1 (MSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                    | —                                                                           | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2      | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9                                                                         | SREN          | CREN           | _             | FERR        | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra            | nsmit Data F                                                                | legister      |                |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re             | ceive Data R                                                                | egister       |                |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co           | mpare/PWM                                                                   | 2 (LSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co           | mpare/PWM                                                                   | 2 (MSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                    | —                                                                           | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2      | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | -       | Unimpleme            | nted                                                                        |               |                |               |             |               |           | —                        | —                                              |

### TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

### 4.2.2.2 OPTION REGISTER

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB. Note: To achieve a 1:1 prescaler assignment for TMR0 register, assign the prescaler to the Watchdog Timer.

#### R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU INTEDG TOCS T0SE PSA PS2 PS1 PS0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7: RBPU: PORTB Pull-up Enable bit 1 = PORTB pull-ups are disabled 0 = PORTB pull-ups are enabled by individual port latch values INTEDG: Interrupt Edge Select bit bit 6: 1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin bit 5: TOCS: TMR0 Clock Source Select bit 1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) TOSE: TMR0 Source Edge Select bit bit 4. 1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin PSA: Prescaler Assignment bit bit 3: 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0: PS2:PS0: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 000 1:1 1:2 001 1:2 1 · 4 1:4 010 1:8 1:8 011 1:16 100 1:32 1:16 1:32 101 1:64 1:64 110 1:128 1:128 111 1:256

### FIGURE 4-10: OPTION REGISTER (ADDRESS 81h, 181h)

|                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |             |            |                      | -         |        |                                                                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|------------|----------------------|-----------|--------|-------------------------------------------------------------------------|--|--|--|

| R/W-0                                                                                                                                                                                   | B/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                      | U-0         | B/W-0      | R/W-0                | B/W-0     | R/W-0  |                                                                         |  |  |  |

| PSPIF                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |             | SSPIF      | CCP1IF               | TMR2IF    | TMR1IF | R = Readable bit                                                        |  |  |  |

| bit7                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |             |            |                      |           | bit0   |                                                                         |  |  |  |

| bit 7: PSPIF: Parallel Slave Port Interrupt Flag bit<br>1 = A read or a write operation has taken place (must be cleared in software)<br>0 = No read or write operation has taken place |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |             |            |                      |           |        |                                                                         |  |  |  |

| bit 6:                                                                                                                                                                                  | Reserved: Always maintain this bit clear.                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |             |            |                      |           |        |                                                                         |  |  |  |

| bit 5-4:                                                                                                                                                                                | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |             |            |                      |           |        |                                                                         |  |  |  |

| bit 3:                                                                                                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          |             |            |                      |           |        |                                                                         |  |  |  |

| bit 2:                                                                                                                                                                                  | <ul> <li>bit 2: CCP1IF: CCP1 Interrupt Flag bit</li> <li>Capture Mode         <ol> <li>A TMR1 register capture occurred (must be cleared in software)</li> <li>No TMR1 register capture occurred</li> <li>Compare Mode                 <ol> <li>A TMR1 register compare match occurred (must be cleared in software)</li> <li>No TMR1 register compare match occurred (must be cleared in software)</li> <li>No TMR1 register compare match occurred</li></ol></li></ol></li></ul> |                                          |             |            |                      |           |        |                                                                         |  |  |  |

| bit 1:                                                                                                                                                                                  | 1 = TMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MR2 to PR<br>to PR2 mat<br>R2 to PR2     | ch occurre  | d (must be | bit<br>cleared in so | ftware)   |        |                                                                         |  |  |  |

| bit 0:                                                                                                                                                                                  | 1 = TMR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MR1 Overf<br>register ove<br>R1 register | erflow occu |            | be cleared in        | software) |        |                                                                         |  |  |  |

| global                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GIE (INTC                                |             |            |                      |           |        | s corresponding enable bit or the<br>rrupt flag bits are clear prior to |  |  |  |

### FIGURE 4-18: PIR1 REGISTER FOR PIC16C64/64A/R64 (ADDRESS 0Ch)

| Addr                 | Name    | Bit 7                           | Bit 6                    | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|----------------------|---------|---------------------------------|--------------------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                             | PEIE                     | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000<br>000x             | 0000<br>000u                    |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup>            | (3)                      | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000                     | 0000                            |

| 0Dh <sup>(4)</sup>   | PIR2    | —                               | _                        | _                   | _                   | _       | _      | _       | CCP2IF  |                          | <br>0                           |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup>            | (3)                      | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000                     | 0000                            |

| 8Dh <sup>(4)</sup>   | PIE2    | —                               | _                        | -                   | _                   | -       | _      | -       | CCP2IE  |                          | <br>0                           |

| 87h                  | TRISC   | C PORTC Data Direction register |                          |                     |                     |         |        |         |         |                          | 1111<br>1111                    |

| 11h                  | TMR2    | Timer2 m                        | Timer2 module's register |                     |                     |         |        |         |         |                          | 0000                            |

| 92h                  | PR2     | Timer2 m                        | iodule's Per             | iod register        |                     |         |        |         |         | 1111<br>1111             | 1111<br>1111                    |

| 12h                  | T2CON   | —                               | TOUTPS3                  | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000<br>0000             | -000<br>0000                    |

| 15h                  | CCPR1L  | Capture/0                       | Compare/P                | VM1 (LSB)           | 1                   |         |        |         |         | xxxx<br>xxxx             | uuuu<br>uuuu                    |

| 16h                  | CCPR1H  | Capture/0                       | Compare/P                | VM1 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 17h                  | CCP1CON | —                               | —                        | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00<br>0000               | 00<br>0000                      |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/0                       | Compare/P                | VM2 (LSB)           | 1                   |         | 1      |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/0                       | Compare/P\               | VM2 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Dh <sup>(4)</sup>   | CCP2CON | -                               | —                        | CCP2X               | CCP2Y               | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00<br>0000               | 00<br>0000                      |

### TABLE 10-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend:

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode.

Note

1:

These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

### 11.2 <u>SPI Mode for PIC16C62/62A/R62/63/</u> R63/64/64A/R64/65/65A/R65

This section contains register definitions and operational characteristics of the SPI module for the PIC16C62, PIC16C62A, PIC16CR62, PIC16C63, PIC16CR63, PIC16C64A, PIC16CR64, PIC16CR64, PIC16C65, PIC16C65A, PIC16CR65.

### FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| U-0                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                           | R-0                           | B-0        | B-0                                                     | R-0           | B-0          | B-0          |                                                                                      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|---------------------------------------------------------|---------------|--------------|--------------|--------------------------------------------------------------------------------------|--|--|

| _                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                             | D/A                           | P          | S                                                       | R/W           | UA           | BF           | R = Readable bit                                                                     |  |  |

| bit7                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                               |                               | 1          |                                                         |               | <u>I</u>     | bit0         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |

| bit 7-6:                                                                                                                                                                                                                             | Unimpl                                                                                                                                                                                                                                                                        | emented                       | Read as    | '0'                                                     |               |              |              |                                                                                      |  |  |

| <ul> <li>bit 5: D/Ā: Data/Address bit (I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul> |                                                                                                                                                                                                                                                                               |                               |            |                                                         |               |              |              |                                                                                      |  |  |

| bit 4:                                                                                                                                                                                                                               | <ul> <li>bit 4: P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul> |                               |            |                                                         |               |              |              |                                                                                      |  |  |

| bit 3:                                                                                                                                                                                                                               | <ul> <li>S: Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Start bit was not detected last</li> </ul>     |                               |            |                                                         |               |              |              |                                                                                      |  |  |

| bit 2:                                                                                                                                                                                                                               | This bit                                                                                                                                                                                                                                                                      | holds the<br>o the next<br>ad | R/W bit i  | ation (I <sup>2</sup> C r<br>nformation<br>stop bit, or | following the | e last addre | ess match. T | his bit is valid from the address                                                    |  |  |

| bit 1:                                                                                                                                                                                                                               | 1 = Indi                                                                                                                                                                                                                                                                      | cates that                    | the user   | it I <sup>2</sup> C mode<br>needs to up<br>to be upda   | odate the add | dress in the | SSPADD re    | egister                                                                              |  |  |

| bit 0:                                                                                                                                                                                                                               | BF: Buf                                                                                                                                                                                                                                                                       | fer Full St                   | atus bit   |                                                         |               |              |              |                                                                                      |  |  |

|                                                                                                                                                                                                                                      | 1 = Rec                                                                                                                                                                                                                                                                       |                               | olete, SSF | es)<br>PBUF is full<br>SSPBUF is                        |               |              |              |                                                                                      |  |  |

|                                                                                                                                                                                                                                      | 1 = Trar                                                                                                                                                                                                                                                                      |                               | ogress, S  | SPBUF is f<br>PBUF is err                               |               |              |              |                                                                                      |  |  |

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and  $\overline{SS}$  could be used as general purpose outputs by clearing their corresponding TRIS register bits.

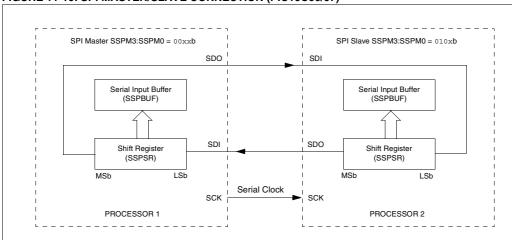

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

### FIGURE 11-10: SPI MASTER/SLAVE CONNECTION (PIC16C66/67)

### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                           | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|---------------------------------|----------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>            | (2)      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                            | RX9      | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra                       | ansmit R | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>            | (2)      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                            | TX9      | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | RG Baud Rate Generator Register |          |         |       |       |        |        |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### Value on Value on Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. all other BOR Resets PSPIF<sup>(1)</sup> 0Ch PIR1 RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000 (2) 18h RCSTA SPEN RX9 SREN CREN FFRR OFBB 0000 -00x 0000 -00x RX9D 0000 0000 0000 0000 1Ah RCREG USART Receive Register PSPIE<sup>(1)</sup> CCP1IE 0000 0000 0000 0000 8Ch PIE1 RCIE TXIE SSPIE TMR2IE TMR1IE (2) 0000 -010 0000 -010 98h TXSTA CSRC BRGH TRMT TX9D TX9 TXEN SYNC \_ 0000 0000 0000 0000 SPBRG 99h Baud Rate Generator Register

### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

### 13.5 Interrupts

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The PIC16C6X family has up to 11 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or global enable bit, GIE.            |

Global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enable interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flag bits are contained in the INTCON register.

The peripheral interrupt flag bits are contained in special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2 and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, bit GIE is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

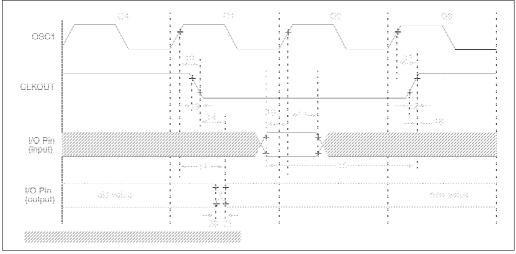

For external interrupt events, such as the RB0/INT pin or RB port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 13-19). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C61/62/64/65, if an interrupt occurs while the Global Interrupt Enable bit, GIE is being cleared, bit GIE may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

- 4. Perform the following to ensure that interrupts are globally disabled.

| LOOP | BCF II           | NTCON,GIE | ;Disable Global    |  |  |  |  |

|------|------------------|-----------|--------------------|--|--|--|--|

|      |                  |           | ;Interrupt bit     |  |  |  |  |

|      | BTFSC INTCON,GIE |           | ;Global Interrupt  |  |  |  |  |

|      |                  |           | ;Disabled?         |  |  |  |  |

|      | GOTO             | LOOP      | ;NO, try again     |  |  |  |  |

|      | :                |           | ;Yes, continue     |  |  |  |  |

|      |                  |           | ;with program flow |  |  |  |  |

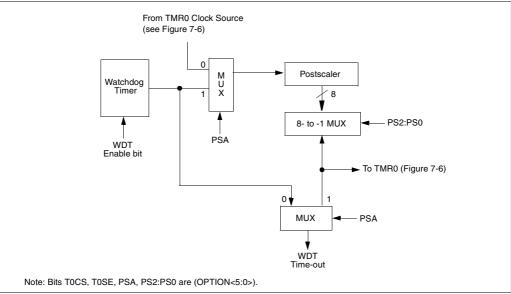

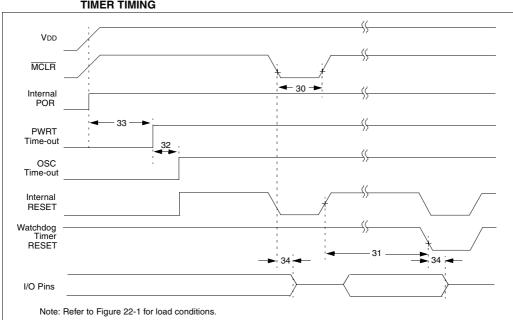

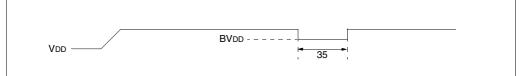

### 13.7 <u>Watchdog Timer (WDT)</u>

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device reset. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (WDT Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 13.1).

### 13.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be

### FIGURE 13-20: WATCHDOG TIMER BLOCK DIAGRAM

assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

13.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

### FIGURE 13-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 13-1, Figure 13-2, and Figure 13-3 for details of these bits for the specific device.

#### Instruction Descriptions 14.1

| Add Lite                                                                                                                | ral and                                                                                                                                                                             | w                                                      |                                                                                                                                                                                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [ <i>label</i> ] A                                                                                                      | DDLW                                                                                                                                                                                | k                                                      |                                                                                                                                                                                                        |  |  |  |  |

| $0 \le k \le 255$                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| $(W) + k \rightarrow (W)$                                                                                               |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| C, DC, Z                                                                                                                |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| 11                                                                                                                      | 111x                                                                                                                                                                                | kkkk                                                   | kkkk                                                                                                                                                                                                   |  |  |  |  |

| The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| 1                                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| 1                                                                                                                       |                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                        |  |  |  |  |

| Q1                                                                                                                      | Q2                                                                                                                                                                                  | Q3                                                     | Q4                                                                                                                                                                                                     |  |  |  |  |

| Decode                                                                                                                  | Read<br>literal 'k'                                                                                                                                                                 | Process<br>data                                        | Write to<br>W                                                                                                                                                                                          |  |  |  |  |

| After Inst                                                                                                              | W =<br>ruction                                                                                                                                                                      | 0x10<br>0x25                                           |                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                         | [ <i>label</i> ] Al<br>$0 \le k \le 2\xi$<br>(W) + k -<br>C, DC, Z<br>11<br>The conte<br>added to the<br>result is pl<br>1<br>1<br>Q1<br>Decode<br>ADDLW<br>Before In<br>After Inst | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$ | $0 \le k \le 255$ (W) + k → (W) C, DC, Z $11  111x  kkkk$ The contents of the W register added to the eight bit literal 'k' result is placed in the W register 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 3 2 2 2 2 |  |  |  |  |

| ANDLW             | AND Lite                                                                                                            | eral with                | W               |               |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|---------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                  | [ <i>label</i> ] ANDLW k |                 |               |  |  |  |  |

| Operands:         | $0 \le k \le 25$                                                                                                    | $0 \le k \le 255$        |                 |               |  |  |  |  |

| Operation:        | (W) .AND                                                                                                            | D. (k) $\rightarrow$ (   | W)              |               |  |  |  |  |

| Status Affected:  | Z                                                                                                                   |                          |                 |               |  |  |  |  |

| Encoding:         | 11                                                                                                                  | 1001                     | kkkk            | kkkk          |  |  |  |  |

| Description:      | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                          |                 |               |  |  |  |  |

| Words:            | 1                                                                                                                   |                          |                 |               |  |  |  |  |

| Cycles:           | 1                                                                                                                   |                          |                 |               |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                  | Q2                       | Q3              | Q4            |  |  |  |  |

|                   | Decode                                                                                                              | Read<br>literal "k"      | Process<br>data | Write to<br>W |  |  |  |  |

| Example           | ANDLW                                                                                                               | 0x5F                     |                 |               |  |  |  |  |

|                   | Before In                                                                                                           | struction                |                 |               |  |  |  |  |

|                   | After Inst                                                                                                          |                          | 0xA3            |               |  |  |  |  |

|                   |                                                                                                                     | W =                      | 0x03            |               |  |  |  |  |

| ADDWF             | Add W a                                                                                                                                                          | nd f                    |                 |                         |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                               | DDWF                    | f,d             |                         |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                |                         |                 |                         |  |  |  |  |

| Operation:        | (W) + (f) $\rightarrow$ (destination)                                                                                                                            |                         |                 |                         |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                         |                         |                 |                         |  |  |  |  |

| Encoding:         | 00                                                                                                                                                               | 0111                    | dfff            | ffff                    |  |  |  |  |

| Description:      | Add the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |                         |                 |                         |  |  |  |  |

| Words:            | 1                                                                                                                                                                |                         |                 |                         |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                |                         |                 |                         |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                               | Q2                      | Q3              | Q4                      |  |  |  |  |

|                   | Decode                                                                                                                                                           | Read<br>register<br>'f' | Process<br>data | Write to<br>destination |  |  |  |  |

| Evennle           | ADDUE                                                                                                                                                            | BOD                     | <u>.</u>        |                         |  |  |  |  |

| Example           | ADDWF                                                                                                                                                            |                         | 0               |                         |  |  |  |  |

|                   | Before In                                                                                                                                                        | structior               | ו<br>0x17       |                         |  |  |  |  |

|                   | FSR = 0xC2                                                                                                                                                       |                         |                 |                         |  |  |  |  |

|                   | After Inst                                                                                                                                                       |                         |                 |                         |  |  |  |  |

|                   |                                                                                                                                                                  | W =<br>FSR =            | 0xD9<br>0xC2    |                         |  |  |  |  |

| ANDWF             | AND W v                                                        | vith f                    |                 |                      |

|-------------------|----------------------------------------------------------------|---------------------------|-----------------|----------------------|

| Syntax:           | [ <i>label</i> ] Al                                            | NDWF                      | f,d             |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                         |                 |                      |

| Operation:        | (W) .AND                                                       | 0. (f) $\rightarrow$ (e   | destinatio      | on)                  |

| Status Affected:  | Z                                                              |                           |                 |                      |

| Encoding:         | 0.0                                                            | 0101                      | dfff            | ffff                 |

| Description:      | AND the W<br>is 0 the res<br>ter. If 'd' is<br>register 'f'.   | sult is stor<br>1 the res | red in the      | W regis-             |

| Words:            | 1                                                              |                           |                 |                      |

| Cycles:           | 1                                                              |                           |                 |                      |

| Q Cycle Activity: | Q1                                                             | Q2                        | Q3              | Q4                   |

|                   | Decode                                                         | Read<br>register<br>'f'   | Process<br>data | Write to destination |

| Example           | ANDWF                                                          | FSR,                      | 1               |                      |

|                   | Before In                                                      |                           |                 |                      |

|                   |                                                                | W =<br>FSR =              | 0x17<br>0xC2    |                      |

|                   | After Inst                                                     |                           | 0102            |                      |

|                   |                                                                | W =                       | 0x17            |                      |

|                   |                                                                | FSR =                     | 0x02            |                      |

| <b>Applicable Devices</b> | 61 | 60 | 601 | Deo | 60 | Dec | 61 | 611 | DGA | 65 | 65A | Dee | 66 | 67 |

|---------------------------|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| Applicable Devices        | 01 | 02 | 02A | n02 | 03 | n03 | 04 | 04A | n04 | 05 | 05A | H00 | 00 | 07 |

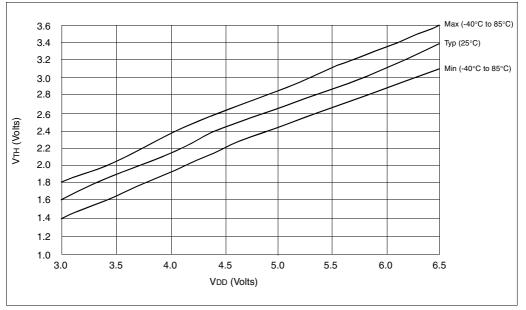

|       |                                    | Standa        | rd Operat  | ing Co |           |          | ss otherwise stated)                                |  |  |

|-------|------------------------------------|---------------|------------|--------|-----------|----------|-----------------------------------------------------|--|--|

|       |                                    | Operatir      | ng temper  | ature  | -40°C     | S ≤ TA   | $\Delta \leq +125^{\circ}C$ for extended,           |  |  |

|       | RACTERISTICS                       |               |            |        | -40°C     | ≤ T/     | $\Delta \leq +85^{\circ}$ C for industrial and      |  |  |

|       | ARACIERISTICS                      |               |            |        | 0°C       | ≤ T⁄     | $A \leq +70^{\circ}C$ for commercial                |  |  |

|       |                                    | Operatir      | ng voltage | VDD r  | ange as c | describe | ed in DC spec Section 15.1 and                      |  |  |

|       |                                    | Section 15.2. |            |        |           |          |                                                     |  |  |

| Param | Characteristic                     | Sym           | Min        | Typ†   | Max       | Units    | Conditions                                          |  |  |

| No.   |                                    |               |            |        |           |          |                                                     |  |  |

|       | Output High Voltage                |               |            |        |           |          |                                                     |  |  |

| D090  | I/O ports (Note 3)                 | Voh           | VDD-0.7    | -      | -         | v        | IOH = -3.0 mA,                                      |  |  |

|       |                                    |               |            |        |           | -        | $VDD = 4.5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |  |  |

| D090A |                                    |               | VDD-0.7    | -      | -         | v        | IOH = -2.5 mA,                                      |  |  |

|       |                                    |               |            |        |           |          | VDD = 4.5V, -40°C to +125°C                         |  |  |

| D092  | OSC2/CLKOUT (RC osc config)        |               | VDD-0.7    | -      | -         | V        | IOH = -1.3 mA,                                      |  |  |

|       |                                    |               |            |        |           |          | VDD = 4.5V, -40°C to +85°C                          |  |  |

| D092A |                                    |               | VDD-0.7    | -      | -         | V        | IOH = -1.0 mA,                                      |  |  |

|       |                                    |               |            |        |           |          | VDD = 4.5V, -40°C to +125°C                         |  |  |

| D150* | Open-Drain High Voltage            | Vod           | -          | -      | 14        | V        | RA4 pin                                             |  |  |

|       | Capacitive Loading Specs on        |               |            |        |           |          |                                                     |  |  |

|       | Output Pins                        |               |            |        |           |          |                                                     |  |  |

| D100  | OSC2 pin                           | Cosc2         |            |        | 15        | pF       | In XT, HS and LP modes when                         |  |  |

|       |                                    |               |            |        |           |          | external clock is used to drive                     |  |  |

|       |                                    |               |            |        |           |          | OSC1.                                               |  |  |

| D101  | All I/O pins and OSC2 (in RC mode) | Cio           |            |        | 50        | pF       |                                                     |  |  |

The parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.