Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c65a-04i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

-

| Address              | Name    | Bit 7                | Bit 6                                                        | Bit 5          | Bit 4          | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------|--------------------------------------------------------------|----------------|----------------|---------------|-------------|---------|---------|--------------------------|------------------------------------------------|

| Bank 0               |         |                      |                                                              |                |                |               |             |         |         |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing           | this location                                                | register)      | 0000 0000      | 0000 0000     |             |         |         |                          |                                                |

| 01h                  | TMR0    | Timer0 mod           | lule's registe                                               |                | xxxx xxxx      | uuuu uuuu     |             |         |         |                          |                                                |

| 02h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)                                                | Least Signi    | ficant Byte    |               |             |         |         | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP                  | RP1                                                          | RP0            | TO             | PD            | Z           | DC      | С       | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat         | a memory ac                                                  | Idress pointe  | ər             |               |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | _                    | _                                                            | PORTA Dat      | a Latch wher   | n written: PO | RTA pins wh | en read |         | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da             | ta Latch whe                                                 | n written: PC  | ORTB pins wi   | nen read      |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | ta Latch whe                                                 | n written: PO  | ORTC pins w    | hen read      |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da             | ta Latch whe                                                 | n written: PO  | ORTD pins w    | hen read      |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | —                    | —                                                            | —              | —              | —             | RE2         | RE1     | RE0     | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                    | — — Write Buffer for the upper 5 bits of the Program Counter |                |                |               |             |         |         |                          |                                                |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE                                                         | TOIE           | INTE           | RBIE          | T0IF        | INTF    | RBIF    | 0000 000x                | 0000 0000                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(6)</sup> | (4)                                                          | RCIF           | TXIF           | SSPIF         | CCP1IF      | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | —                    | —                                                            |                |                | —             | —           | —       | CCP2IF  | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg          | ister for the I                                              | _east Signific | cant Byte of t | he 16-bit TM  | R1 register |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg          | ister for the I                                              | Most Signific  | ant Byte of th | ne 16-bit TMF | R1 register |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                    | _                                                            | T1CKPS1        | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS  | TMR10N  | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod           | lule's registe                                               | r              |                |               |             |         |         | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | —                    | TOUTPS3                                                      | TOUTPS2        | TOUTPS1        | TOUTPS0       | TMR2ON      | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou           | us Serial Por                                                | t Receive Bu   | ffer/Transmit  | Register      |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                        | SSPEN          | СКР            | SSPM3         | SSPM2       | SSPM1   | SSPM0   | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWM                                                    | 1 (LSB)        |                |               |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWM                                                    | 1 (MSB)        |                |               |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                    | —                                                            | CCP1X          | CCP1Y          | CCP1M3        | CCP1M2      | CCP1M1  | CCP1M0  | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9                                                          | SREN           | CREN           | _             | FERR        | OERR    | RX9D    | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra            | nsmit Data F                                                 | legister       |                |               |             |         |         | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re             | ceive Data R                                                 | egister        |                |               |             |         |         | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co           | mpare/PWM                                                    | 2 (LSB)        |                |               |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co           | mpare/PWM                                                    | 2 (MSB)        |                |               |             |         |         | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                    | —                                                            | CCP2X          | CCP2Y          | CCP2M3        | CCP2M2      | CCP2M1  | CCP2M0  | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | -       | Unimpleme            | nted                                                         |                |                |               |             |         |         | —                        | —                                              |

# TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

## 5.3 PORTC and TRISC Register

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTC is an 8-bit wide bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

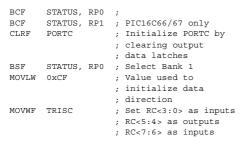

#### EXAMPLE 5-3: INITIALIZING PORTC

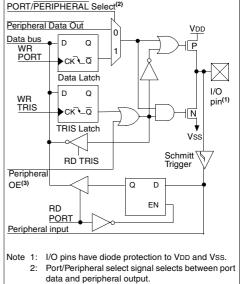

## FIGURE 5-6: PORTC BLOCK DIAGRAM

3: Peripheral OE (output enable) is only activated if peripheral select is active.

## TABLE 5-5: PORTC FUNCTIONS FOR PIC16C62/64

| Name            | Bit# | Buffer Type | Function                                                                    |

|-----------------|------|-------------|-----------------------------------------------------------------------------|

| RC0/T1OSI/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator input or Timer1 clock input      |

| RC1/T1OSO       | bit1 | ST          | Input/output port pin or Timer1 oscillator output                           |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).      |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                |

| RC6             | bit6 | ST          | Input/output port pin                                                       |

| RC7             | bit7 | ST          | Input/output port pin                                                       |

Legend: ST = Schmitt Trigger input

## TABLE 5-6: PORTC FUNCTIONS FOR PIC16C62A/R62/64A/R64

| Name            | Bit# | Buffer Type | Function                                                                              |

|-----------------|------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input               |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                      |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture input/Compare output/PWM1 output                     |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 |             | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                          |

| RC6             | bit6 | ST          | Input/output port pin                                                                 |

| RC7             | bit7 | ST          | Input/output port pin                                                                 |

Legend: ST = Schmitt Trigger input

## TABLE 5-7: PORTC FUNCTIONS FOR PIC16C63/R63/65/65A/R65/66/67

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input                        |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                    |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit, or USART Syn-<br>chronous Clock          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive, or USART Syn-<br>chronous Data            |

Legend: ST = Schmitt Trigger input

## TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7                         | Bit 6                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------------------------------|---------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7                           | RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC Data Direction Register |                                 |       |       |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

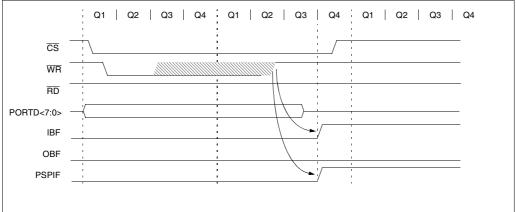

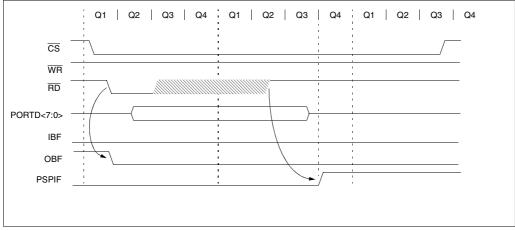

## FIGURE 5-12: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### TABLE 5-13: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name  | Bit 7 | Bit 6 | Bit 5               | Bit 4               | Bit 3 Bit 2 Bit 1 Bit 0 |          | Value on:<br>POR,<br>BOR | Value on all other resets |           |           |

|---------|-------|-------|-------|---------------------|---------------------|-------------------------|----------|--------------------------|---------------------------|-----------|-----------|

| 08h     | PORTD | PSP7  | PSP6  | PSP5                | PSP4                | PSP3                    | PSP2     | PSP1                     | PSP0                      | xxxx xxxx | uuuu uuuu |

| 09h     | PORTE | _     |       |                     | _                   | _                       | RE2      | RE1                      | RE0                       | xxx       | uuu       |

| 89h     | TRISE | IBF   | OBF   | IBOV                | PSPMODE             | _                       | PORTE Da | ata Directior            | n Bits                    | 0000 -111 | 0000 -111 |

| 0Ch     | PIR1  | PSPIF | (1)   | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF                   | CCP1IF   | TMR2IF                   | TRM1IF                    | 0000 0000 | 0000 0000 |

| 8Ch     | PIE1  | PSPIE | (1)   | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE                   | CCP1IE   | TMR2IE                   | TMR1IE                    | 0000 0000 | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by the PSP.

Note 1: These bits are reserved, always maintain these bits clear.

2: These bits are implemented on the PIC16C65/65A/R65/67 only.

# 6.0 OVERVIEW OF TIMER MODULES

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

All PIC16C6X devices have three timer modules except for the PIC16C61, which has one timer module. Each module can generate an interrupt to indicate that an event has occurred (i.e., timer overflow). Each of these modules are detailed in the following sections. The timer modules are:

- Timer0 module (Section 7.0)

- Timer1 module (Section 8.0)

- Timer2 module (Section 9.0)

#### 6.1 <u>Timer0 Overview</u>

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. TMR0 can increment at the following rates: 1:1 when the prescaler is assigned to Watchdog Timer, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

## 6.2 <u>Timer1 Overview</u>

| Ap | plicable Devices |

|----|------------------|

|    |                  |

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

TImer1 also has a prescaler option which allows TMR1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. TMR1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit capture or 16-bit compare and must be synchronized to the device.

#### 6.3 <u>Timer2 Overview</u>

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a programmable prescaler and a programmable postscaler, as well as an 8-bit Period Register (PR2). Timer2 can be used with the CCP module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, and 1:16.

The postscaler allows TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

#### 6.4 <u>CCP Overview</u>

| e Devices |

|-----------|

|           |

|           |

|           |

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The CCP module(s) can operate in one of three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs, an interrupt can be generated and the output pin CCPx can be forced to a given state (High or Low) and Timer1 can be reset. This depends on control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

### 11.2 <u>SPI Mode for PIC16C62/62A/R62/63/</u> R63/64/64A/R64/65/65A/R65

This section contains register definitions and operational characteristics of the SPI module for the PIC16C62, PIC16C62A, PIC16CR62, PIC16C63, PIC16CR63, PIC16C64A, PIC16CR64, PIC16CR64, PIC16C65, PIC16C65A, PIC16CR65.

## FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| U-0      | U-0                                                                                                                                                                                                                                                                    | R-0                           | B-0        | B-0                                                     | R-0                                 | B-0          | B-0          |                                                                                      |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|---------------------------------------------------------|-------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------|--|--|--|

| _        | _                                                                                                                                                                                                                                                                      | D/A                           | P          | S                                                       | R/W                                 | UA           | BF           | R = Readable bit                                                                     |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                        |                               | 1          |                                                         |                                     | <u>I</u>     | bit0         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7-6: | Unimpl                                                                                                                                                                                                                                                                 | emented                       | Read as    | '0'                                                     |                                     |              |              |                                                                                      |  |  |  |

| bit 5:   | 1 = Indi                                                                                                                                                                                                                                                               | cates that                    | the last b | ,                                                       | )<br>d or transmit<br>d or transmit |              |              |                                                                                      |  |  |  |

| bit 4:   | <ul> <li>P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul> |                               |            |                                                         |                                     |              |              |                                                                                      |  |  |  |

| bit 3:   | <ul> <li>Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Start bit was not detected last</li> </ul> |                               |            |                                                         |                                     |              |              |                                                                                      |  |  |  |

| bit 2:   | This bit                                                                                                                                                                                                                                                               | holds the<br>o the next<br>ad | R/W bit i  | ation (I <sup>2</sup> C r<br>nformation<br>stop bit, or | following the                       | e last addre | ess match. T | his bit is valid from the address                                                    |  |  |  |

| bit 1:   | 1 = Indi                                                                                                                                                                                                                                                               | cates that                    | the user   | it I <sup>2</sup> C mode<br>needs to up<br>to be upda   | odate the add                       | dress in the | SSPADD re    | egister                                                                              |  |  |  |

| bit 0:   | BF: Buf                                                                                                                                                                                                                                                                | fer Full St                   | atus bit   |                                                         |                                     |              |              |                                                                                      |  |  |  |

|          | 1 = Rec                                                                                                                                                                                                                                                                |                               | olete, SSF | es)<br>PBUF is full<br>SSPBUF is                        |                                     |              |              |                                                                                      |  |  |  |

|          | 1 = Trar                                                                                                                                                                                                                                                               |                               | ogress, S  | SPBUF is f<br>PBUF is err                               |                                     |              |              |                                                                                      |  |  |  |

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and  $\overline{SS}$  could be used as general purpose outputs by clearing their corresponding TRIS register bits.

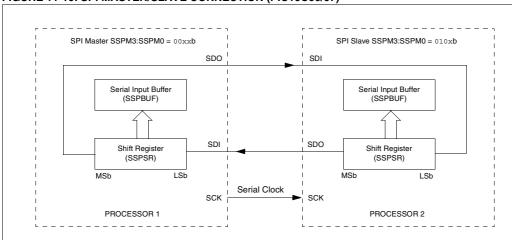

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

#### FIGURE 11-10: SPI MASTER/SLAVE CONNECTION (PIC16C66/67)

Г

# FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                | R/W-0                       | R/W-0          | U-0         | R-0          | R-0          | R-x         |                    |                                                                                                                               |

|--------|----------------------------------------------------------------------|-----------------------------|----------------|-------------|--------------|--------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                  | SREN                        | CREN           | —           | FERR         | OERR         | RX9D        | R                  | = Readable bit                                                                                                                |

| bit7   |                                                                      |                             |                |             |              |              | bitO        | W<br>U<br>- n<br>x | <ul> <li>Writable bit</li> <li>Unimplemented</li> <li>bit, read as '0'</li> <li>Value at POR rese</li> <li>unknown</li> </ul> |

| bit 7: | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p             | s RC7/RX/l                  | DT and RC<br>d | 6/TX/CK     | pins as seri | al port pins | s when bits | TRIS               | C<7:6> are set)                                                                                                               |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion          |             |              |              |             |                    |                                                                                                                               |

| bit 5: | SREN: Sing                                                           | gle Receiv                  | e Enable bi    | t           |              |              |             |                    |                                                                                                                               |

|        | Asynchrone<br>Don't care                                             | ous mode                    |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{Synchronof}{1 = Enables}$ $0 = Disables$ This bit is c        | s single ree<br>s single re | ceive<br>ceive | is comple   | ete.         |              |             |                    |                                                                                                                               |

|        | Synchrono<br>Unused in t                                             |                             | <u>slave</u>   |             |              |              |             |                    |                                                                                                                               |

| bit 4: | CREN: Cor                                                            | ntinuous R                  | eceive Ena     | ble bit     |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Asynchrono}}{1 = \text{Enable}}$ $0 = \text{Disable}$   | s continuo                  |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Synchronor}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                | until enabl | le bit CREN  | l is cleared | (CREN ov    | erride             | s SREN)                                                                                                                       |

| bit 3: | Unimplem                                                             | ented: Rea                  | ad as '0'      |             |              |              |             |                    |                                                                                                                               |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                | ed by rea   | ding RCRE    | G register   | and receive | e next             | valid byte)                                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                | d by clea   | ring bit CRI | EN)          |             |                    |                                                                                                                               |

| bit 0: | <b>RX9D</b> : 9th                                                    |                             |                |             |              |              |             |                    |                                                                                                                               |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7                | Bit 6     | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|-----------|---------|-----------|-----------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)       | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9       | SREN    | CREN      |           | FERR   | OERR   | RX9D   | 0000 -00x               | x00- 0000                       |

| 19h     | TXREG | USART Tra            | ansmit Re | egister |           |           |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)       | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN    | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Generat   |         | 0000 0000 | 0000 0000 |        |        |        |                         |                                 |

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

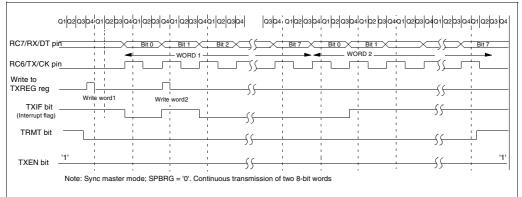

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

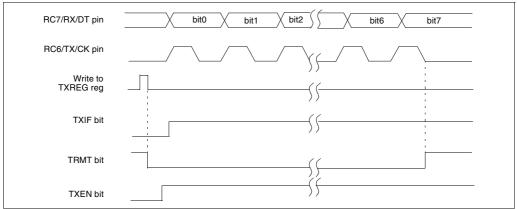

### FIGURE 12-13: SYNCHRONOUS TRANSMISSION THROUGH TXEN

# TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic, Description<br>Operands |        | Description                  | Cycles                             | 14-Bit Opcode |      |      |          | Status | Notes |  |

|-----------------------------------|--------|------------------------------|------------------------------------|---------------|------|------|----------|--------|-------|--|

|                                   |        |                              | MSb                                |               |      | LSb  | Affected |        |       |  |

| BYTE-ORIE                         | NTED   | FILE REGISTER OPERATIONS     |                                    |               |      |      |          |        |       |  |

| ADDWF                             | f, d   | Add W and f                  | 1                                  | 00            | 0111 | dfff | ffff     | C,DC,Z | 1,2   |  |

| ANDWF                             | f, d   | AND W with f                 | 1                                  | 00            | 0101 | dfff | ffff     | Z      | 1,2   |  |

| CLRF                              | f      | Clear f                      | 1                                  | 00            | 0001 | lfff | ffff     | Z      | 2     |  |

| CLRW                              | -      | Clear W                      | 1                                  | 00            | 0001 | 0xxx | xxxx     | Z      |       |  |

| COMF                              | f, d   | Complement f                 | 1                                  | 00            | 1001 | dfff | ffff     | Z      | 1,2   |  |

| DECF                              | f, d   | Decrement f                  | 1                                  | 00            | 0011 | dfff | ffff     | Z      | 1,2   |  |

| DECFSZ                            | f, d   | Decrement f, Skip if 0       | 1(2)                               | 00            | 1011 | dfff | ffff     |        | 1,2,3 |  |

| INCF                              | f, d   | Increment f                  | 1                                  | 00            | 1010 | dfff | ffff     | Z      | 1,2   |  |

| INCFSZ                            | f, d   | Increment f, Skip if 0       | 1(2)                               | 00            | 1111 | dfff | ffff     |        | 1,2,3 |  |

| IORWF                             | f, d   | Inclusive OR W with f        | 1                                  | 00            | 0100 | dfff | ffff     | Z      | 1,2   |  |

| MOVF                              | f, d   | Move f                       | 1                                  | 00            | 1000 | dfff | ffff     | Z      | 1,2   |  |

| MOVWF                             | f      | Move W to f                  | 1                                  | 00            | 0000 | lfff | ffff     |        |       |  |

| NOP                               | -      | No Operation                 | 1                                  | 00            | 0000 | 0xx0 | 0000     |        |       |  |

| RLF                               | f, d   | Rotate Left f through Carry  | 1                                  | 00            | 1101 | dfff | ffff     | С      | 1,2   |  |

| RRF                               | f, d   | Rotate Right f through Carry | 1                                  | 00            | 1100 | dfff | ffff     | С      | 1,2   |  |

| SUBWF                             | f, d   | Subtract W from f            | 1                                  | 00            | 0010 | dfff | ffff     | C,DC,Z | 1,2   |  |

| SWAPF                             | f, d   | Swap nibbles in f            | 1                                  | 00            | 1110 | dfff | ffff     |        | 1,2   |  |

| XORWF                             | f, d   | Exclusive OR W with f        | 1                                  | 00            | 0110 | dfff | ffff     | Z      | 1,2   |  |

| BIT-ORIENT                        | ED FIL | E REGISTER OPERATIONS        |                                    |               |      |      |          |        |       |  |

| BCF                               | f, b   | Bit Clear f                  | 1                                  | 01            | 00bb | bfff | ffff     |        | 1,2   |  |

| BSF                               | f, b   | Bit Set f                    | 1                                  | 01            | 01bb | bfff | ffff     |        | 1,2   |  |

| BTFSC                             | f, b   | Bit Test f, Skip if Clear    | 1 (2)                              | 01            | 10bb | bfff | ffff     |        | 3     |  |

| BTFSS                             | f, b   | Bit Test f, Skip if Set      | 1 (2)                              | 01            | 11bb | bfff | ffff     |        | 3     |  |

| LITERAL A                         | ND CO  | NTROL OPERATIONS             |                                    |               |      |      |          |        |       |  |

| ADDLW                             | k      | Add literal and W            | 1                                  | 11            | 111x | kkkk | kkkk     | C,DC,Z |       |  |

| ANDLW                             | k      | AND literal with W           | 1                                  | 11            | 1001 | kkkk | kkkk     | Z      |       |  |

| CALL                              | k      | Call subroutine              | 2                                  | 10            | 0kkk | kkkk | kkkk     |        |       |  |

| CLRWDT                            | -      | Clear Watchdog Timer         | 1                                  | 00            | 0000 | 0110 | 0100     | TO,PD  |       |  |

| GOTO                              | k      | Go to address                | 2                                  | 10            | 1kkk | kkkk | kkkk     |        |       |  |

| IORLW                             | k      | Inclusive OR literal with W  | 1                                  | 11            | 1000 | kkkk | kkkk     | Z      |       |  |

| MOVLW                             | k      | Move literal to W            | 1                                  | 11            | 00xx | kkkk | kkkk     | c l    |       |  |

| RETFIE                            | -      | Return from interrupt        | 2                                  | 00            | 0000 | 0000 | 1001     |        |       |  |

| RETLW                             | k      | Return with literal in W     | Return with literal in W 2 11 01xx |               | 01xx | kkkk | kkkk     |        |       |  |

| RETURN                            | -      | Return from Subroutine       | 2                                  | 00            | 0000 | 0000 | 1000     |        |       |  |

| SLEEP                             | -      | Go into standby mode         | 1                                  | 00            | 0000 | 0110 | 0011     | TO,PD  |       |  |

| SUBLW                             | k      | Subtract W from literal      | 1                                  | 11            | 110x | kkkk | kkkk     | C,DC,Z |       |  |

|                                   |        | Exclusive OR literal with W  |                                    |               |      |      |          |        |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| SUBWF             | Subtract                                                                   | W from f                     |                                   |                      |  |  |

|-------------------|----------------------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|--|--|

| Syntax:           | [ label ]                                                                  | SUBWF                        | f,d                               |                      |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$ | ,                            |                                   |                      |  |  |

| Operation:        | (f) - (W) $\rightarrow$ (destination)                                      |                              |                                   |                      |  |  |

| Status Affected:  | C, DC, Z                                                                   |                              |                                   |                      |  |  |

| Encoding:         | 00                                                                         | 0010                         | dfff                              | ffff                 |  |  |

| Description:      | Subtract (2'<br>ister from re<br>stored in the<br>result is sto            | egister 'f'. l<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the        |  |  |

| Words:            | 1                                                                          |                              |                                   |                      |  |  |

| Cycles:           | 1                                                                          |                              |                                   |                      |  |  |

| Q Cycle Activity: | Q1                                                                         | Q2                           | Q3                                | Q4                   |  |  |

|                   | Decode                                                                     | Read<br>register 'f'         | Process<br>data                   | Write to destination |  |  |

| Example 1:        | SUBWF                                                                      | REG1,1                       |                                   |                      |  |  |

|                   | Before Ins                                                                 | truction                     |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 3                                 |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |  |  |

|                   | Z                                                                          | =                            | ?                                 |                      |  |  |

|                   | After Instru                                                               | uction                       |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 1                                 |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | nositive             |  |  |

|                   | z                                                                          | =                            | 0                                 | poolavo              |  |  |

| Example 2:        | Before Ins                                                                 | truction                     |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 2                                 |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |  |  |

|                   | Z                                                                          | =                            | ?                                 |                      |  |  |

|                   | After Instru                                                               | uction                       |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 0                                 |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | 7010                 |  |  |

|                   | z                                                                          | =                            | 1                                 | 2010                 |  |  |

| Example 3:        | Before Ins                                                                 | truction                     |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 1                                 |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |  |  |

|                   | z                                                                          | =                            | ?                                 |                      |  |  |

|                   | After Instru                                                               | uction                       |                                   |                      |  |  |

|                   | REG1                                                                       | =                            | 0xFF                              |                      |  |  |

|                   | W<br>C                                                                     | =                            | 2<br>0; result is                 | negative             |  |  |

|                   | z                                                                          | =                            | 0                                 | guivo                |  |  |

|                   |                                                                            |                              |                                   |                      |  |  |

| SWAPF             | Swap Ni                                                                                                                                                               | bbles in             | f               |                      |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [label]                                                                                                                                                               | SWAPF 1              | ,d              |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                        | 27                   |                 |                      |  |  |  |

| Operation:        | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                               |                      |                 |                      |  |  |  |

| Status Affected:  | None                                                                                                                                                                  |                      |                 |                      |  |  |  |

| Encoding:         | 0 0                                                                                                                                                                   | 1110                 | dfff            | ffff                 |  |  |  |

| Description:      | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |                      |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                     |                      |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                     |                      |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                    | Q2                   | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                | Read<br>register 'f' | Process<br>data | Write to destination |  |  |  |

| Example           | SWAPF                                                                                                                                                                 | REG,                 | 0               |                      |  |  |  |

|                   | Before In                                                                                                                                                             | struction            |                 |                      |  |  |  |

|                   |                                                                                                                                                                       | REG1                 | = 0xA           | 45                   |  |  |  |

|                   | After Inst                                                                                                                                                            | ruction              |                 |                      |  |  |  |

|                   |                                                                                                                                                                       | REG1<br>W            | = 0xA<br>= 0x5  | .0                   |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |           |         |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------|--|--|--|

| Syntax:          | [label]                                                                                                                                                                             | TRIS      | f       |      |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                   |           |         |      |  |  |  |

| Operation:       | $(W) \rightarrow TI$                                                                                                                                                                | RIS regis | ster f; |      |  |  |  |

| Status Affected: | None                                                                                                                                                                                |           |         |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                  | 0000      | 0110    | Offf |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |           |         |      |  |  |  |

| Words:           | 1                                                                                                                                                                                   |           |         |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |           |         |      |  |  |  |

| Example          |                                                                                                                                                                                     |           |         |      |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |           |         |      |  |  |  |

|                  | <u>.</u>                                                                                                                                                                            |           |         |      |  |  |  |

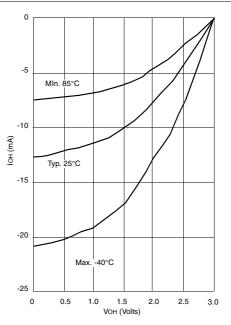

Data based on matrix samples. See first page of this section for details.

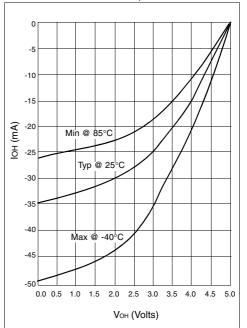

FIGURE 16-20: IOH VS. VOH, VDD = 5V

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 17.1 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial) PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial)

| DC CHAR               |                                                                   | <b>Standaı</b><br>Operatir |             | •                  |                | )°C ≤          | unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------|----------------------------|-------------|--------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                    | Sym                        | Min         | Тур†               | Max            | Units          | Conditions                                                                                                                                                                                                                                                                        |

| D001<br>D001A         | Supply Voltage                                                    | Vdd                        | 4.0<br>4.5  | -                  | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                           |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                        | -           | 1.5                | -              | V              |                                                                                                                                                                                                                                                                                   |

| D003                  | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                       | -           | Vss                | -              | V              | See section on Power-on Reset for details                                                                                                                                                                                                                                         |

| D004*                 | VDD rise rate to ensure<br>internal Power-on<br>Reset signal      | SVDD                       | 0.05        | -                  | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                                                                                                         |

| D010                  | Supply Current<br>(Note 2, 5)                                     | IDD                        | -           | 2.7                | 5.0            | mA             | XT, RC, osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                    |

| D013                  |                                                                   |                            | -           | 13.5               | 30             | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                 |

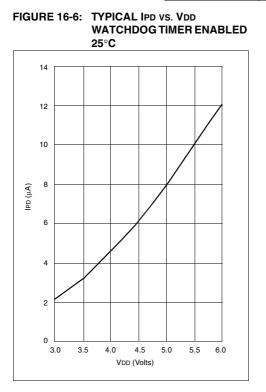

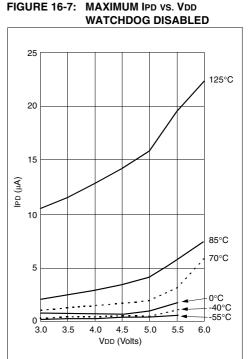

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3, 5)                                 | IPD                        | -<br>-<br>- | 10.5<br>1.5<br>1.5 | 42<br>21<br>24 | μΑ<br>μΑ<br>μΑ | $ \begin{array}{l} V{}_{DD}=4.0V, WDT \mbox{ enabled}, -40^{\circ}{C} \mbox{ to } +85^{\circ}{C} \\ V{}_{DD}=4.0V, WDT \mbox{ disabled}, -0^{\circ}{C} \mbox{ to } +70^{\circ}{C} \\ V{}_{DD}=4.0V, WDT \mbox{ disabled}, -40^{\circ}{C} \mbox{ to } +85^{\circ}{C} \end{array} $ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSs.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

# PIC16C6X

19.3

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### DC Characteristics: PIC16C65-04 (Commercial, Industrial) PIC16C65-10 (Commercial, Industrial) PIC16C65-20 (Commercial, Industrial) PIC16LC65-04 (Commercial, Industrial)

|              |                                       |                                                                                                                                        | <b>rd Operati</b><br>ng tempera | •        | -40°C   | ;` ≤ T, | ss otherwise stated)<br>A ≤ +85°C for industrial and                                                                               |  |  |

|--------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DC CHA       | RACTERISTICS                          | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial Operating voltage VDD range as described in DC spec Section 19.1 at Section 19.2 |                                 |          |         |         |                                                                                                                                    |  |  |

| Param<br>No. | Characteristic                        | Sym                                                                                                                                    | Min                             | Тур<br>† | Мах     | Units   | Conditions                                                                                                                         |  |  |

|              | Input Low Voltage                     |                                                                                                                                        |                                 |          |         |         |                                                                                                                                    |  |  |

|              | I/O ports                             | VIL                                                                                                                                    |                                 |          |         |         |                                                                                                                                    |  |  |

| D030         | with TTL buffer                       |                                                                                                                                        | Vss                             | -        | 0.15Vdd | V       | For entire VDD range                                                                                                               |  |  |

| D030A        |                                       |                                                                                                                                        | Vss                             | -        | 0.8V    | V       | $4.5V \leq V \text{DD} \leq 5.5V$                                                                                                  |  |  |

| D031         | with Schmitt Trigger buffer           |                                                                                                                                        | Vss                             | -        | 0.2Vdd  | V       |                                                                                                                                    |  |  |

| D032         | MCLR, OSC1 (in RC mode)               |                                                                                                                                        | Vss                             | -        | 0.2Vdd  | V       |                                                                                                                                    |  |  |

| D033         | OSC1 (in XT, HS and LP)               |                                                                                                                                        | Vss                             | -        | 0.3Vdd  | V       | Note1                                                                                                                              |  |  |