Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c65a-10-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64

| Address              | Name    | Bit 7              | Bit 6              | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|----------------|----------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                    |                |                |              |                 |               | •         |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter    | nts of FSR to  | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r              |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signi    | ficant Byte    |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | С              | 0001 1xxx      | 000q quuu    |                 |               |           |                          |                                                |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac        | Idress pointe  | er             |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | _                  | _                  | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe       | n written: PC  | ORTB pins wh   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe       | n written: PO  | ORTC pins w    | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Da           | ta Latch whe       | n written: PO  | ORTD pins w    | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   | _                  | _                  | _              | _              | _            | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                  | -              | Write Buffer   | for the uppe | r 5 bits of the | Program C     | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE           | INTE           | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                | -              | _              | SSPIF        | CCP1IF          | TMR2IF        | TMR1IF    | 00 0000                  | 00 0000                                        |

| 0Dh                  | _       | Unimpleme          | nted               |                |                |              |                 |               |           | _                        | _                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the I    | _east Signific | ant Byte of t  | he 16-bit TM | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the I    | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | _                  | _                  | T1CKPS1        | T1CKPS0        | T10SCEN      | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r              | •              | •            |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                  | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | ıs Serial Por      |                | xxxx xxxx      | uuuu uuuu    |                 |               |           |                          |                                                |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN          | CKP            | SSPM3        | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                  | _                  | CCP1X          | CCP1Y          | CCP1M3       | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h-1Fh              | _       | - Unimplemented -  |                    |                |                |              |                 |               |           |                          | _                                              |

$\begin{tabular}{ll} Legend: & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented location read as '0'. \end{tabular}$

Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

- $\hbox{6:} \quad \hbox{PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear. } \\$

## FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| U = Unimplemented bit, read as '0' - n = Value at POR reset  1.7-6: Reserved: Always maintain these bits clear.  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  1.4: TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  1.3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  1.2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1. TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                   | R/W-0    | R/W-0                                                                   | R-0                                                                              | R-0                                   | R/W-0                                 | R/W-0         | R/W-0         | R/W-0    |                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------|---------------|----------|------------------------------------|

| U = Unimplemented bit, read as '0' - n = Value at POR reset  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  TXIF: USART transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred (must be cleared in software) 1 : TMR1F: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software) | _        | _                                                                       | RCIF                                                                             | TXIF                                  | SSPIF                                 | CCP1IF        | TMR2IF        | TMR1IF   |                                    |

| t 5: RCIF: USART Receive Interrupt Flag bit  1 = The USART receive buffer is full (cleared by reading RCREG)  0 = The USART receive buffer is empty  44: TXIF: USART Transmit Interrupt Flag bit  1 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is full  1 = The transmission/reception is complete (must be cleared in software)  0 = Waiting to transmit/receive  1 = CCP1IF: CCP1 Interrupt Flag bit  Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2IF: TMR2 to PR2 match occurred  0 = No TMR1 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 O: TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                             | oit7     |                                                                         |                                                                                  |                                       |                                       |               |               | bit0     | U = Unimplemented bit, read as '0' |

| 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  14:  TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2:  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1:  TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: 1:  TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow loccurred (must be cleared in software)                                                                                                                                                                                                                                                                                                | bit 7-6: | Reserved:                                                               | Always ma                                                                        | intain thes                           | e bits clear.                         |               |               |          |                                    |

| 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  4: 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  4: 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 5:   | 1 = The US                                                              | ART receiv                                                                       | e buffer is                           | full (cleared                         | d by reading  | RCREG)        |          |                                    |

| 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2 : CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1 to: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 4:   | 1 = The US                                                              | ART transi                                                                       | nit buffer is                         | empty (cle                            | ared by writi | ng to TXRE    | G)       |                                    |

| Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 : TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 3:   | 1 = The tra                                                             | nsmission/i                                                                      | reception is                          |                                       |               | ared in softv | vare)    |                                    |

| 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred  t 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 2:   | Capture Mo 1 = A TMR 0 = No TMI Compare M 1 = A TMR 0 = No TMI PWM Mode | ode<br>1 register c<br>R1 register<br><u>lode</u><br>1 register c<br>R1 register | apture occ<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | ed (must be o | ,             | oftware) |                                    |

| 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1:   | 1 = TMR2 t                                                              | o PR2 mat                                                                        | ch occurre                            | d (must be                            |               | oftware)      |          |                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 0:   | 1 = TMR1 ı                                                              | egister ove                                                                      | rflow occu                            | rred (must l                          | oe cleared in | software)     |          |                                    |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

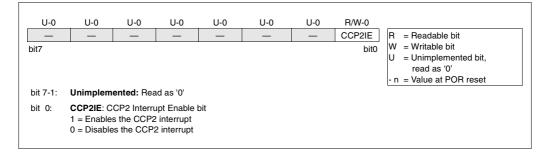

#### 4.2.2.6 PIE2 REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt enable bit.

## FIGURE 4-20: PIE2 REGISTER (ADDRESS 8Dh)

#### 4.2.2.8 PCON REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control register (PCON) contains a flag bit to allow differentiation between a Power-on Reset to an external MCLR reset or WDT reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN

bit in the Configuration word).

#### FIGURE 4-22: PCON REGISTER FOR PIC16C62/64/65 (ADDRESS 8Eh)

R/W-0 R/W-q U-0 U-0 U-0 U-0 U-0 U-0 **POR** = Readable bit W = Writable bit bit7 hit0 = Unimplemented bit, read as '0' n = Value at POR reset = value depends on conditions Unimplemented: Read as '0' hit 7-2. bit 1: POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) bit 0: Reserved This bit should be set upon a Power-on Reset by user software and maintained as set. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.

## FIGURE 4-23: PCON REGISTER FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 (ADDRESS 8Eh)

| U-0      | U-0                                         | U-0         | U-0         | U-0        | U-0            | R/W-0       | R/W-q       |                                                                                                              |

|----------|---------------------------------------------|-------------|-------------|------------|----------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------|

| _        | _                                           | _           | _           | -          | _              | POR         | BOR         | R = Readable bit                                                                                             |

| bit7     |                                             |             |             |            |                |             | bit0        | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset q = value depends on conditions |

| bit 7-2: | Unimplem                                    | ented: Rea  | ıd as '0'   |            |                |             |             |                                                                                                              |

| bit 1:   | <b>POR</b> : Power 1 = No Power 0 = A Power | ver-on Rese | et occurred | must be se | in software    | after a Pow | er-on Reset | occurs)                                                                                                      |

| bit 0:   | BOR: Brow<br>1 = No Bro<br>0 = A Brow       | wn-out Res  | et occurred | i          | et in software | after a Bro | wn-out Rese | et occurs)                                                                                                   |

## TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | AUD FOSC = 20 MHz SPBRG |            |                    | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |  |

|-------------|-------------------------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|--|

| RATE<br>(K) | KBAUD                   | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |  |

| 0.3         | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |  |

| 1.2         | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |  |

| 2.4         | NA                      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |  |

| 9.6         | NA                      | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |  |

| 19.2        | 19.53                   | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |  |

| 76.8        | 76.92                   | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |  |

| 96          | 96.15                   | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |  |

| 300         | 294.1                   | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |  |

| 500         | 500                     | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |  |

| HIGH        | 5000                    | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |  |

| LOW         | 19.53                   | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |  |

|                     | Fosc = | 5.0688 MI  | Нz                          | 4 MHz  |            |                             | 3.579545 | MHz        |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

## TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 | 0 MHz      | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | 1.221    | +1.73      | 255                | 1.202  | +0.16      | 207                | 1.202  | +0.16      | 129                | 1.203     | +0.23      | 92                 |

| 2.4         | 2.404    | +0.16      | 129                | 2.404  | +0.16      | 103                | 2.404  | +0.16      | 64                 | 2.380     | -0.83      | 46                 |

| 9.6         | 9.469    | -1.36      | 32                 | 9.615  | +0.16      | 25                 | 9.766  | +1.73      | 15                 | 9.322     | -2.90      | 11                 |

| 19.2        | 19.53    | +1.73      | 15                 | 19.23  | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64     | -2.90      | 5                  |

| 76.8        | 78.13    | +1.73      | 3                  | 83.33  | +8.51      | 2                  | 78.13  | +1.73      | 1                  | NA        | -          | -                  |

| 96          | 104.2    | +8.51      | 2                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 300         | 312.5    | +4.17      | 0                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 500         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| HIGH        | 312.5    | -          | 0                  | 250    | -          | 0                  | 156.3  | -          | 0                  | 111.9     | -          | 0                  |

| LOW         | 1.221    | -          | 255                | 0.977  | -          | 255                | 0.6104 | -          | 255                | 0.437     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

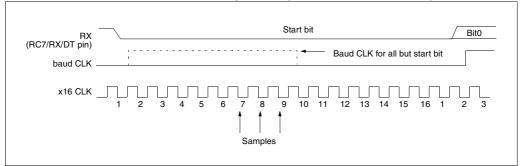

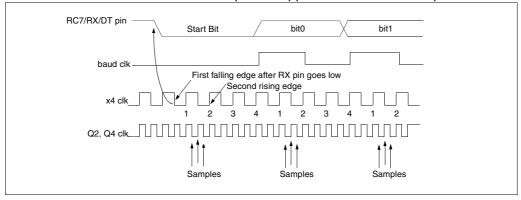

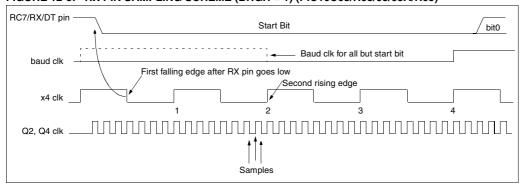

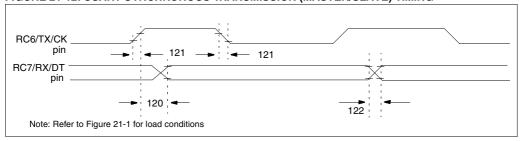

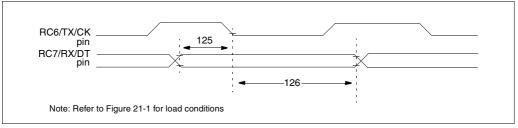

#### 12.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is

set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

FIGURE 12-3: RX PIN SAMPLING SCHEME (BRGH = 0) PIC16C63/R63/65/65A/R65)

FIGURE 12-4: RX PIN SAMPLING SCHEME (BRGH = 1) (PIC16C63/R63/65/65A/R65)

FIGURE 12-5: RX PIN SAMPLING SCHEME (BRGH = 1) (PIC16C63/R63/65/65A/R65)

Steps to follow when setting up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, then set bit BRGH. (Section 12.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit TXIE.

- If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Load data to the TXREG register (starts transmission).

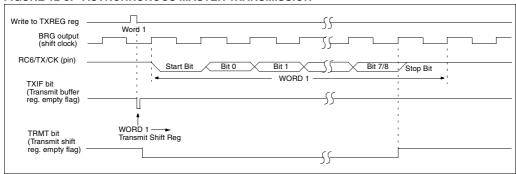

#### FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

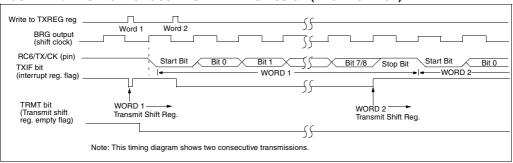

#### FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)                          | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9                          | SREN    | CREN  | -     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra            | ansmit R                     | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)                          | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9                          | TXEN    | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |                         | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

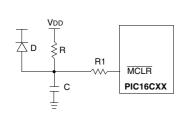

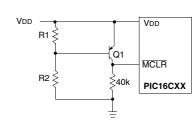

### FIGURE 13-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the devices electrical specifications.

- R1 = 100Ω to 1 kΩ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrostatic Overstress (EOS).

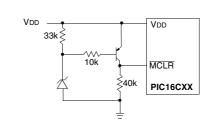

## FIGURE 13-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

## FIGURE 13-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

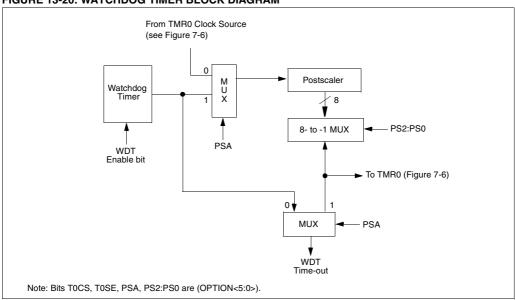

#### 13.7 Watchdog Timer (WDT)

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device reset. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (WDT Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 13.1).

#### 13.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be

assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition

The TO bit in the STATUS register will be cleared upon a WDT time-out.

#### 13.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 13-20: WATCHDOG TIMER BLOCK DIAGRAM

### FIGURE 13-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 13-1, Figure 13-2, and Figure 13-3 for details of these bits for the specific device.

## PIC16C6X

**CLRF** Clear f Syntax: [label] CLRF Operands:  $0 \le f \le 127$ Operation:  $00h \rightarrow (f)$  $1 \rightarrow Z$ Status Affected: Ζ Encoding: 00 0001 1fff ffff The contents of register 'f' are cleared Description: and the Z bit is set. Words: 1

Cycles: 1

Q Cycle Activity: Q1 Q2 Q3 Q4 Write Decode Read Process register 'f' data register 'f

Example CLRF FLAG REG

Before Instruction

FLAG\_REG 0x5A After Instruction

> FLAG\_REG 0x00 Z 1

**CLRW** Clear W Syntax: [label] CLRW Operands: None Operation:  $00h \rightarrow (W)$  $1 \rightarrow Z$ Status Affected: Z 0.0 0001 0xxx **Encoding:** xxxx Description: W register is cleared. Zero bit (Z) is Words: 1 Cycles: Q2 Q4 Q Cycle Activity: Q1 Q3 Decode Process Write to No-Operation data Example CLRW Before Instruction W 0x5A After Instruction W 0x00 Z 1

**CLRWDT** Clear Watchdog Timer Syntax: [label] CLRWDT Operands: None  $00h \rightarrow WDT$ Operation:  $0 \rightarrow WDT$  prescaler,  $1 \rightarrow \overline{10}$  $1 \rightarrow \overline{PD}$ TO, PD Status Affected: Encoding: 00 0000 0110 0100 Description: CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are Words: 1 Cycles: Q Cycle Activity: Q1 Q2 Q3 Q4 Decode No-Process Clear Operation WDT data Counter CLRWDT Example Before Instruction

After Instruction

TO  $\overline{PD}$

WDT counter =

WDT counter =

WDT prescaler=

0x00

0

SLEEP Syntax:

[ label ] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

$0 \rightarrow WDT$  prescaler,

$1 \rightarrow \overline{10}$  $0 \rightarrow \overline{PD}$

TO, PD Status Affected:

Encoding:

0000 0110 0011

Description: The power-down status bit, PD is

cleared. Time-out status bit,  $\overline{\text{TO}}$  is set. Watchdog Timer and its pres-

caler are cleared.

The processor is put into SLEEP mode with the oscillator stopped. See

Section 13.8 for more details.

Words:

Cycles:

Q Cycle Activity: Q1 Q2 Q3 Q4

Decode No-No-Go to Operation Operation Sleep

Example: SLEEP **SUBLW** Subtract W from Literal

Syntax: [ label ] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$

C. DC. Z Status Affected:

Encoding: 110x kkkk kkkk

The W register is subtracted (2's comple-Description: ment method) from the eight bit literal 'k'.

The result is placed in the W register.

Words:

Cycles:

Q1 Q2 Q4 Q Cycle Activity: Q3 Decode Read Process Write to W

Example 1: SUBLW 0x02

Before Instruction

W С ? ?

literal 'k'

After Instruction

W

С 1; result is positive

data

Ζ

Example 2: Before Instruction

> 2 W С ? =

Z

After Instruction

W

С 1; result is zero

z

Example 3: Before Instruction

> W 3 С ? = ?

After Instruction

W 0xFF

С 0; result is negative

z

# PIC16C6X

| XORLW                        | Exclusive OR Literal with W                                                                                       | XORWF                          | Exclusive OR W with f                                                                                                                                                     |

|------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                      | [ <i>label</i> ] XORLW k                                                                                          | Syntax:                        | [label] XORWF f,d                                                                                                                                                         |

| Operands:                    | $0 \le k \le 255$                                                                                                 | Operands:                      | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        |

| Operation: Status Affected:  | (W) .XOR. $k \rightarrow (W)$                                                                                     | Operation:<br>Status Affected: | (W) .XOR. (f) $\rightarrow$ (destination) Z                                                                                                                               |

| Encoding:                    | 11 1010 kkkk kkkk                                                                                                 | Encoding:                      | 00 0110 dfff ffff                                                                                                                                                         |

| Description:                 | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. | Description:                   | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |

| Words:                       | 1                                                                                                                 | Words:                         | 1                                                                                                                                                                         |

| Cycles:<br>Q Cycle Activity: | 1<br>Q1 Q2 Q3 Q4                                                                                                  | Cycles:<br>Q Cycle Activity:   | 1<br>Q1 Q2 Q3 Q4                                                                                                                                                          |

|                              | Decode Read Process Write to literal 'k' data W                                                                   | Q Gyolo / lollvilly.           | Decode Read Process Write to register data destination                                                                                                                    |

| Example:                     | XORLW 0xAF                                                                                                        |                                | T                                                                                                                                                                         |

|                              | Before Instruction                                                                                                | Example                        | XORWF REG 1                                                                                                                                                               |

|                              | W = 0xB5                                                                                                          |                                | Before Instruction                                                                                                                                                        |

|                              | After Instruction $W = 0x1A$                                                                                      |                                | REG = 0xAF  W = 0xB5                                                                                                                                                      |

|                              | - 0////                                                                                                           |                                | After Instruction                                                                                                                                                         |

|                              |                                                                                                                   |                                | $ \begin{array}{rcl} REG & = & 0x1A \\ W & = & 0xB5 \end{array} $                                                                                                         |

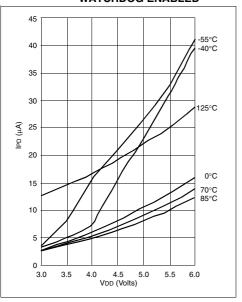

FIGURE 16-8: MAXIMUM IPD vs. VDD WATCHDOG ENABLED\*

\*IPD, with Watchdog Timer enabled, has two components: The leakage current which increases with higher temperature and the operating current of the Watchdog Timer logic which increases with lower temperature. At -40°C, the latter dominates explaining the apparently anomalous behavior.

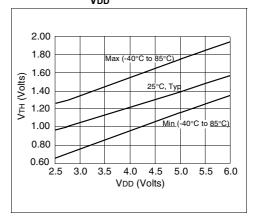

FIGURE 16-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs.

### 17.2 DC Characteristics: PIC16LC62/64-04 (Commercial, Industrial)

| DC CHA       | RACTERISTICS                                                      | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C}$ $\leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C}$ $\leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial |      |      |      |       |                                                                 |  |  |

|--------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------|--|--|

| Param<br>No. | Characteristic                                                    | Sym                                                                                                                                                                                                                                            | Min  | Тур† | Max  | Units | Conditions                                                      |  |  |

| D001         | Supply Voltage                                                    | VDD                                                                                                                                                                                                                                            | 3.0  | -    | 6.0  | V     | LP, XT, RC osc configuration (DC - 4 MHz)                       |  |  |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                            | VDR                                                                                                                                                                                                                                            | -    | 1.5  | -    | V     |                                                                 |  |  |

| D003         | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                                                                                                                                                                                                                                           | -    | Vss  | -    | V     | See section on Power-on Reset for details                       |  |  |

| D004*        | VDD rise rate to ensure internal Power-on Reset signal            | SVDD                                                                                                                                                                                                                                           | 0.05 | -    | -    | V/ms  | See section on Power-on Reset for details                       |  |  |

| D010         | Supply Current (Note 2, 5)                                        | IDD                                                                                                                                                                                                                                            | -    | 2.0  | 3.8  | mA    | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 3.0V (Note 4)   |  |  |

| D010A        |                                                                   |                                                                                                                                                                                                                                                | -    | 22.5 | 48   | μΑ    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |  |  |

| D020         | Power-down Current                                                | IPD                                                                                                                                                                                                                                            | -    | 7.5  | 30   | μΑ    | VDD = 3.0V, WDT enabled, -40°C to +85°C                         |  |  |

| D021         | (Note 3, 5)                                                       |                                                                                                                                                                                                                                                | -    | 0.9  | 13.5 | μΑ    | VDD = 3.0V, WDT disabled, 0°C to +70°C                          |  |  |

| D021A        |                                                                   |                                                                                                                                                                                                                                                | -    | 0.9  | 18   | μΑ    | VDD = 3.0V, WDT disabled, -40°C to +85°C                        |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

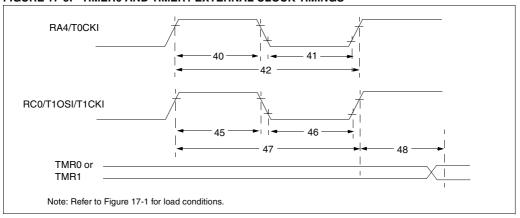

FIGURE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic         |                   |                    | Min                                | Typ† | Max   | Units | Conditions                         |  |

|--------------|-----------|------------------------|-------------------|--------------------|------------------------------------|------|-------|-------|------------------------------------|--|

|              |           |                        |                   | L                  |                                    |      |       |       |                                    |  |

| 40* Tt0H     |           | T0CKI High Pulse Width |                   | No Prescaler       | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |           |                        |                   | With Prescaler     | 10                                 | l —  | _     | ns    | parameter 42                       |  |

| 41*          | Tt0L      | TOCKI Low Pulse Width  |                   | No Prescaler       | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |           |                        |                   | With Prescaler     | 10                                 | _    | _     | ns    | parameter 42                       |  |

| 42*          | Tt0P      | T0CKI Period           |                   | No Prescaler       | Tcy + 40                           | _    | _     | ns    |                                    |  |

|              |           |                        |                   | With Prescaler     |                                    | _    | _     | ns    | N = prescale value                 |  |

|              |           |                        |                   |                    | 20 or TCY + 40                     |      |       |       | (2, 4,, 256)                       |  |

|              |           |                        |                   |                    | N                                  |      |       |       |                                    |  |

| 45*          | Tt1H      | T1CKI High Time        | Synchronous, P    |                    | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |           |                        | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _    | _     | ns    | parameter 47                       |  |

|              |           |                        | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _    | _     | ns    |                                    |  |

|              |           |                        | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _    | _     | ns    |                                    |  |

|              |           |                        |                   | PIC16 <b>LC</b> 6X | 50                                 | _    | _     | ns    |                                    |  |

| 46*          | Tt1L      | t1L T1CKI Low Time     | Synchronous, P    | rescaler = 1       | 0.5TCY + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |           |                        | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _    | _     | ns    | parameter 47                       |  |

|              |           |                        | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _    |       | ns    |                                    |  |

|              |           |                        | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _    | _     | ns    |                                    |  |

|              |           |                        |                   | PIC16 <b>LC</b> 6X | 50                                 | _    | -     | ns    |                                    |  |

| 47*          | Tt1P      | T1CKI input period     | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                        |                   | PIC16 <b>LC</b> 6X | Greater of:<br>50 OR TCY + 40<br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                        | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                 | _    | _     | ns    |                                    |  |

|              |           |                        |                   | PIC16 <b>LC</b> 6X | 100                                | _    | _     | ns    |                                    |  |

|              | Ft1       | Timer1 oscillator inp  |                   |                    | DC                                 | _    | 200   | kHz   |                                    |  |

|              |           | (oscillator enabled b  | , ,               |                    |                                    |      |       |       |                                    |  |

| 48           | TCKEZtmr1 | Delay from external    | •                 |                    | 2Tosc                              | _    | 7Tosc | -     |                                    |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

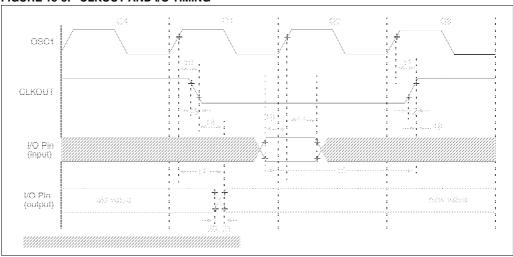

## FIGURE 18-3: CLKOUT AND I/O TIMING

TABLE 18-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameters | Sym      | Characteristic                                                           |                                               | Min        | Typ† | Max         | Units | Conditions |

|------------|----------|--------------------------------------------------------------------------|-----------------------------------------------|------------|------|-------------|-------|------------|

| 10*        | TosH2ckL | OSC1↑ to CLKOUT↓                                                         | OSC1↑ to CLKOUT↓                              |            | 75   | 200         | ns    | Note 1     |

| 11*        | TosH2ckH | OSC1↑ to CLKOUT↑                                                         |                                               | _          | 75   | 200         | ns    | Note 1     |

| 12*        | TckR     | CLKOUT rise time                                                         |                                               | _          | 35   | 100         | ns    | Note 1     |

| 13*        | TckF     | CLKOUT fall time                                                         |                                               | _          | 35   | 100         | ns    | Note 1     |

| 14*        | TckL2ioV | CLKOUT ↓ to Port out valid                                               |                                               | _          |      | 0.5Tcy + 20 | ns    | Note 1     |

| 15*        | TioV2ckH | Port in valid before CLKOUT ↑                                            |                                               | Tosc + 200 |      | _           | ns    | Note 1     |

| 16*        | TckH2ioI | Port in hold after CLKOUT ↑                                              |                                               | 0          | _    | _           | ns    | Note 1     |

| 17*        | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid                                       |                                               | _          | 50   | 150         | ns    |            |

| 18*        | TosH2ioI | ol OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | PIC16 <b>C</b> 62A/<br>R62/64A/R64            | 100        | _    | _           | ns    |            |

|            |          |                                                                          | PIC16 <b>LC</b> 62A/<br>R62/64A/R64           | 200        |      | _           | ns    |            |