Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Batalla                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c65a-20-pq |

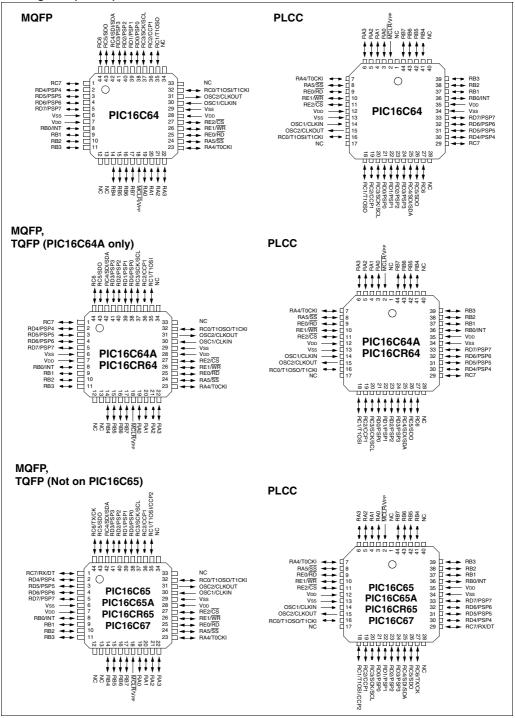

### Pin Diagrams (Cont.'d)

**TABLE 3-2:** PIC16C62/62A/R62/63/R63/66 PINOUT DESCRIPTION

| Pin Name                                      | Pin#   | Pin Type | Buffer<br>Type         | Description                                                                                                                                                                                             |

|-----------------------------------------------|--------|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

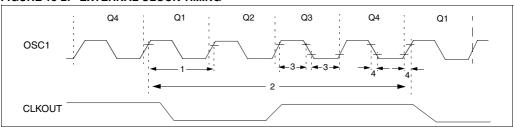

| OSC1/CLKIN                                    | 9      | I        | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                   |

| OSC2/CLKOUT                                   | 10     | 0        | ı                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP                                      | 1      | I/P      | ST                     | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                   |

|                                               |        |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                     |

| RA0                                           | 2      | I/O      | TTL                    |                                                                                                                                                                                                         |

| RA1                                           | 3      | I/O      | TTL                    |                                                                                                                                                                                                         |

| RA2                                           | 4      | I/O      | TTL                    |                                                                                                                                                                                                         |

| RA3                                           | 5      | I/O      | TTL                    |                                                                                                                                                                                                         |

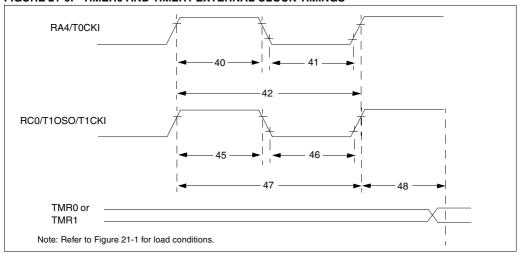

| RA4/T0CKI                                     | 6      | I/O      | ST                     | RA4 can also be the clock input to the Timer0 timer/counter.<br>Output is open drain type.                                                                                                              |

| RA5/SS                                        | 7      | I/O      | TTL                    | RA5 can also be the slave select for the synchronous serial port.                                                                                                                                       |

|                                               |        |          |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                           |

| RB0/INT                                       | 21     | I/O      | TTL/ST(4)              | RB0 can also be the external interrupt pin.                                                                                                                                                             |

| RB1                                           | 22     | I/O      | TTL                    |                                                                                                                                                                                                         |

| RB2                                           | 23     | I/O      | TTL                    |                                                                                                                                                                                                         |

| RB3                                           | 24     | I/O      | TTL                    |                                                                                                                                                                                                         |

| RB4                                           | 25     | I/O      | TTL                    | Interrupt on change pin.                                                                                                                                                                                |

| RB5                                           | 26     | I/O      | TTL                    | Interrupt on change pin.                                                                                                                                                                                |

| RB6                                           | 27     | I/O      | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                      |

| RB7                                           | 28     | I/O      | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                       |

|                                               |        |          |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                     |

| RC0/T1OSO <sup>(1)</sup> /T1CKI               | 11     | I/O      | ST                     | RC0 can also be the Timer1 oscillator output <sup>(1)</sup> or Timer1 clock input.                                                                                                                      |

| RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> | 12     | I/O      | ST                     | RC1 can also be the Timer1 oscillator input <sup>(1)</sup> or Capture2 input/Compare2 output/PWM2 output <sup>(2)</sup> .                                                                               |

| RC2/CCP1                                      | 13     | I/O      | ST                     | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                    |

| RC3/SCK/SCL                                   | 14     | I/O      | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                      |

| RC4/SDI/SDA                                   | 15     | I/O      | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                         |

| RC5/SDO                                       | 16     | I/O      | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                            |

| RC6/TX/CK <sup>(2)</sup>                      | 17     | I/O      | ST                     | RC6 can also be the USART Asynchronous Transmit <sup>(2)</sup> or Synchronous Clock <sup>(2)</sup> .                                                                                                    |

| RC7/RX/DT <sup>(2)</sup>                      | 18     | I/O      | ST                     | RC7 can also be the USART Asynchronous Receive <sup>(2)</sup> or Synchronous Data <sup>(2)</sup> .                                                                                                      |

| Vss                                           | 8,19   | Р        | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                |

| VDD                                           | 20     | Р        | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                 |

| Legend: I = input O =                         | output | l/       | O = input/outpu        |                                                                                                                                                                                                         |

— = Not used

I/O = input/output TTL = TTL input

P = power ST = Schmitt Trigger input

Note 1: Pin functions T10SO and T10SI are reversed on the PIC16C62.

- 2: The USART and CCP2 are not available on the PIC16C62/62A/R62.

- 3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

- 4: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 5: This buffer is a Schmitt Trigger input when used in serial programming mode.

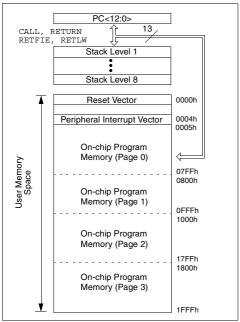

FIGURE 4-4: PIC16C66/67 PROGRAM MEMORY MAP AND STACK

### 4.2 <u>Data Memory Organization</u>

| Αp | pli | cable | e Dev | /ice | es  |    |     |     |    |     |     |    |    |

|----|-----|-------|-------|------|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62  | 62A   | R62   | 63   | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

$= 00 \rightarrow Bank0$

$= 01 \rightarrow Bank1$

=  $10 \rightarrow Bank2$

= 11 → Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTERS

These registers are accessed either directly or indirectly through the File Select Register (FSR) (Section 4.5).

For the PIC16C61, general purpose register locations 8Ch-AFh of Bank 1 are not physically implemented. These locations are mapped into 0Ch-2Fh of Bank 0.

FIGURE 4-5: PIC16C61 REGISTER FILE MAP

| File Address | S                              | File                               | e Address |

|--------------|--------------------------------|------------------------------------|-----------|

| 00h          | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>                | 80h       |

| 01h          | TMR0                           | OPTION                             | 81h       |

| 02h          | PCL                            | PCL                                | 82h       |

| 03h          | STATUS                         | STATUS                             | 83h       |

| 04h          | FSR                            | FSR                                | 84h       |

| 05h          | PORTA                          | TRISA                              | 85h       |

| 06h          | PORTB                          | TRISB                              | 86h       |

| 07h          |                                |                                    | 87h       |

| 08h          |                                |                                    | 88h       |

| 09h          |                                |                                    | 89h       |

| 0Ah          | PCLATH                         | PCLATH                             | 8Ah       |

| 0Bh          | INTCON                         | INTCON                             | 8Bh       |

| 0Ch          |                                |                                    | 8Ch       |

|              | General<br>Purpose<br>Register | Mapped<br>in Bank 0 <sup>(2)</sup> |           |

| 2Fh          |                                |                                    | AFh       |

| 30h          |                                |                                    | B0h       |

|              | (                              |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

|              |                                |                                    |           |

| 7Fh          |                                |                                    | FFh       |

|              | Bank 0                         | Bank 1                             | _         |

| Note 1       | emented data memo              | gister.                            |           |

These locations are unimplemented in Bank 1. Any access to these locations will access the corresponding Bank 0 register.

TABLE 4-2: SPECIAL FUNCTION REGISTERS FOR THE PIC16C62/62A/R62 (Cont.'d)

| Address              | Name    | Bit 7                  | Bit 6                                                            | Bit 5         | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|------------------------|------------------------------------------------------------------|---------------|----------------|--------------|-----------------|---------------|--------------------|--------------------------|------------------------------------------------|

| Bank 1               |         |                        |                                                                  |               |                |              |                 |               |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing             | this location                                                    | uses conter   | nts of FSR to  | address data | a memory (n     | ot a physical | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU                   | INTEDG                                                           | T0CS          | T0SE           | PSA          | PS2             | PS1           | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co             | ounter's (PC)                                                    | Least Sigr    | nificant Byte  |              |                 |               |                    | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>     | RP1 <sup>(5)</sup>                                               | RP0           | TO             | PD           | Z               | DC            | С                  | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect dat           | a memory ac                                                      | Idress pointe | er             | 1            |                 |               | 1                  | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                      | _                                                                | PORTA Dat     | ta Direction R | egister      |                 |               |                    | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Da               | ta Direction F                                                   | Register      |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da               | ta Direction F                                                   | Register      |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

| 89h                  | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                      | _                                                                | _             | Write Buffer   | for the uppe | r 5 bits of the | Program C     | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                    | PEIE                                                             | TOIE          | INTE           | RBIE         | TOIF            | INTF          | RBIF               | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | (6)                    | (6)                                                              | _             | _              | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE             | 00 0000                  | 00 0000                                        |

| 8Dh                  | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

| 8Eh                  | PCON    | _                      | _                                                                | _             | _              | _            | _               | POR           | BOR <sup>(4)</sup> | qq                       | uu                                             |

| 8Fh                  | _       | Unimpleme              | nted                                                             |               |                |              | •               |               |                    | _                        | _                                              |

| 90h                  | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

| 91h                  | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

| 92h                  | PR2     | Timer2 Period Register |                                                                  |               |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou             | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |               |                |              |                 |               |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | _                      | _                                                                | D/Ā           | Р              | S            | R/W             | UA            | BF                 | 00 0000                  | 00 0000                                        |

| 95h-9Fh              | _       | Unimpleme              | nted                                                             |               |                |              |                 |               |                    | _                        | _                                              |

|                      |         |                        |                                                                  |               |                |              |                 |               |                    |                          |                                                |

$\begin{tabular}{ll} Legend: & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented location read as '0'. \\ & Shaded locations are unimplemented, read as '0'. \\ \end{tabular}$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C62, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

- 6: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63 (Cont.'d)

| Address              | Name    | Bit 7              | Bit 6                                                    | Bit 5                     | Bit 4         | Bit 3        | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|----------------------------------------------------------|---------------------------|---------------|--------------|-------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 1               |         |                    |                                                          |                           |               |              |             |               |           |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location                                            | uses conter               | nts of FSR to | address data | a memory (n | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU               | INTEDG                                                   | T0CS                      | TOSE          | PSA          | PS2         | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                                            | Least Sigr                | nificant Byte |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                       | RP0                       | TO            | PD           | Z           | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ac                                              | dress pointe              | er            |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                  | _                                                        | PORTA Dat                 | a Direction R | egister      |             |               |           | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat          | ta Direction F                                           | Register                  |               |              |             |               |           | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da           | ta Direction F                                           | Register                  |               |              |             |               |           | 1111 1111                | 1111 1111                                      |

| 88h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 89h                  | _       | Unimpleme          | nted                                                     |                           |               | _            | _           |               |           |                          |                                                |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                  | Write Buffer for the upper 5 bits of the Program Counter |                           |               |              |             |               |           |                          | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                                     | TOIE                      | INTE          | RBIE         | TOIF        | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | (5)                | (5)                                                      | RCIE                      | TXIE          | SSPIE        | CCP1IE      | TMR2IE        | TMR1IE    | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                  | _                                                        | _                         | _             | _            | _           | _             | CCP2IE    | 0                        | 0                                              |

| 8Eh                  | PCON    | _                  | _                                                        | _                         | _             | _            | _           | POR           | BOR       | qq                       | uu                                             |

| 8Fh                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 90h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 91h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 92h                  | PR2     | Timer2 Peri        | iod Register                                             |                           |               |              |             |               |           | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou         | us Serial Port                                           | t (I <sup>2</sup> C mode) | Address Reg   | gister       |             |               |           | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | _                  | _                                                        | D/Ā                       | Р             | S            | R/W         | UA            | BF        | 00 0000                  | 00 0000                                        |

| 95h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 96h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 97h                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 98h <sup>(2)</sup>   | TXSTA   | CSRC               | TX9                                                      | TXEN                      | SYNC          | _            | BRGH        | TRMT          | TX9D      | 0000 -010                | 0000 -010                                      |

| 99h <sup>(2)</sup>   | SPBRG   | Baud Rate          | Generator Re                                             | egister                   |               |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 9Ah                  | _       | Unimpleme          | nted                                                     |                           |               | _            | _           |               |           |                          |                                                |

| 9Bh                  | _       | Unimpleme          | nted                                                     |                           |               | _            | _           |               |           |                          |                                                |

| 9Ch                  | _       | Unimpleme          | nimplemented                                             |                           |               |              |             |               |           |                          | _                                              |

| 9Dh                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | _                        | _                                              |

| 9Eh                  | _       | Unimpleme          | nimplemented                                             |                           |               |              |             |               |           |                          | _                                              |

| 9Fh                  | _       | Unimpleme          | nted                                                     |                           |               |              |             |               |           | -                        | _                                              |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value depends on condition}, \ \textbf{-} = \textbf{unimplemented location read as '0'}.$

Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

- 5: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C63/R63, always maintain these bits clear.

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

## FIGURE 4-12: PIE1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 8Ch)

| RW-0     | R/W-0                                     | U-0        | U-0          | R/W-0         | R/W-0     | R/W-0  | R/W-0  |                                                                              |

|----------|-------------------------------------------|------------|--------------|---------------|-----------|--------|--------|------------------------------------------------------------------------------|

| _        | _                                         | _          | _            | SSPIE         | CCP1IE    | TMR2IE | TMR1IE | R = Readable bit                                                             |

| bit7     |                                           |            |              |               |           |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7-6: | Reserved:                                 | Always ma  | intain thes  | e bits clear. |           |        |        |                                                                              |

| bit 5-4: | Unimpleme                                 | ented: Rea | ad as '0'    |               |           |        |        |                                                                              |

| bit 3:   | SSPIE: Syn<br>1 = Enables<br>0 = Disables | the SSP i  | interrupt    | Interrupt Er  | nable bit |        |        |                                                                              |

| bit 2:   | CCP1IE: C0<br>1 = Enables<br>0 = Disables | the CCP1   | I interrupt  | bit           |           |        |        |                                                                              |

| bit 1:   | TMR2IE: TM<br>1 = Enables<br>0 = Disables | the TMR2   | 2 to PR2 m   | atch interru  | ot        |        |        |                                                                              |

| bit 0:   | TMR1IE: TM<br>1 = Enables<br>0 = Disables | the TMR1   | 1 overflow i | nterrupt      | t         |        |        |                                                                              |

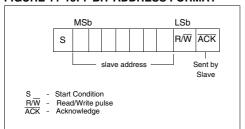

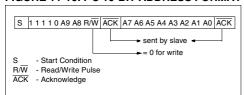

#### 11.4.2 ADDRESSING I2C DEVICES

There are two address formats. The simplest is the 7-bit address format with a  $R\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

#### FIGURE 11-16: I2C 10-BIT ADDRESS FORMAT

#### 11.4.3 TRANSFER ACKNOWLEDGE

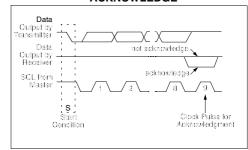

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

# FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

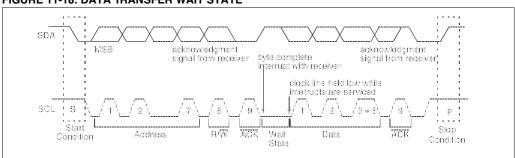

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 11-18: DATA TRANSFER WAIT STATE

## TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Нz                          | 4 MHz  |            |                             | 3.579545 | MHz        |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

# TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 | 0 MHz      | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | 1.221    | +1.73      | 255                | 1.202  | +0.16      | 207                | 1.202  | +0.16      | 129                | 1.203     | +0.23      | 92                 |

| 2.4         | 2.404    | +0.16      | 129                | 2.404  | +0.16      | 103                | 2.404  | +0.16      | 64                 | 2.380     | -0.83      | 46                 |

| 9.6         | 9.469    | -1.36      | 32                 | 9.615  | +0.16      | 25                 | 9.766  | +1.73      | 15                 | 9.322     | -2.90      | 11                 |

| 19.2        | 19.53    | +1.73      | 15                 | 19.23  | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64     | -2.90      | 5                  |

| 76.8        | 78.13    | +1.73      | 3                  | 83.33  | +8.51      | 2                  | 78.13  | +1.73      | 1                  | NA        | -          | -                  |

| 96          | 104.2    | +8.51      | 2                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 300         | 312.5    | +4.17      | 0                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 500         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| HIGH        | 312.5    | -          | 0                  | 250    | -          | 0                  | 156.3  | -          | 0                  | 111.9     | -          | 0                  |

| LOW         | 1.221    | -          | 255                | 0.977  | -          | 255                | 0.6104 | -          | 255                | 0.437     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

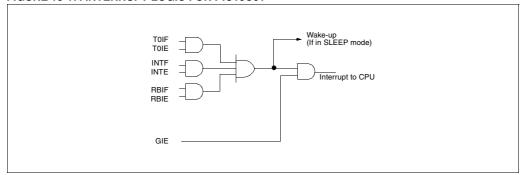

## FIGURE 13-17: INTERRUPT LOGIC FOR PIC16C61

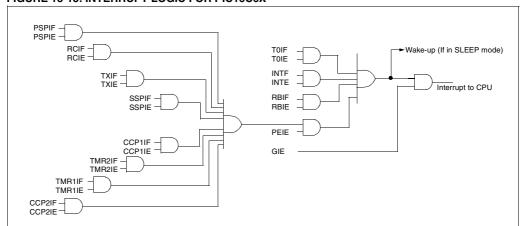

#### FIGURE 13-18: INTERRUPT LOGIC FOR PIC16C6X

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|-------|--------|--------|--------|--------|

| PIC16C62  | Yes  | Yes  | Yes  |       | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C62A | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16CR62 | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C63  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR63 | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64A | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C65  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C65A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR65 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C66  | Yes  | Yes  | Yes  |       | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C67  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

#### 13.6 Context Saving During Interrupts

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 13-1 stores and restores the STATUS and W registers. Example 13-2 stores and restores the STATUS, W, and PCLATH registers (Devices with paged program memory). For all PIC16C6X devices with greater than 1K of program memory (all devices except PIC16C61), the register, W\_TEMP, must be

defined in banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1. 0x120 in bank 2. and 0x1A0 in bank 3).

#### The examples:

- a) Stores the W register

- b) Stores the STATUS register in bank 0

- c) Stores PCLATH

- d) Executes ISR code

- e) Restores PCLATH

- f) Restores STATUS register (and bank select bit)

- g) Restores W register

#### **EXAMPLE 13-1: SAVING STATUS AND W REGISTERS IN RAM (PIC16C61)**

```

MOVWF

W TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

MOVWE

STATUS TEMP

; Save status to bank zero STATUS TEMP register

: (ISR)

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP, F

;Swap W TEMP

;Swap W TEMP into W

SWAPF

W TEMP, W

```

# EXAMPLE 13-2: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM (ALL OTHER PIC16C6X DEVICES)

```

;Copy W to TEMP register, could be bank one or zero

MOVWF

W TEMP

SWAPF

STATUS, W

;Swap status to be saved into W

CLRF

STATUS

;bank 0, regardless of current bank, Clears IRP, RP1, RP0

MOVWF

STATUS TEMP

; Save status to bank zero STATUS TEMP register

PCLATH, W

MOVE

;Only required if using pages 1, 2 and/or 3

;Save PCLATH into W

PCLATH TEMP

MOVWF

CLRF

PCLATH

; Page zero, regardless of current page

BCF

STATUS, IRP

;Return to Bank 0

FSR, W

;Copy FSR to W

MOVWF

FSR TEMP

;Copy FSR from W to FSR TEMP

· (TSR)

MOVF

PCLATH TEMP, W

;Restore PCLATH

MOVWF

PCLATH

; Move W into PCLATH

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

: (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP,F

;Swap W TEMP

W_TEMP,W

SWAPF

;Swap W TEMP into W

```

| BCF               | Bit Clear                        | r f           |                   |                       | BTFSC            | Bit Test,                        | Skip if Cl                  | lear              |                  |

|-------------------|----------------------------------|---------------|-------------------|-----------------------|------------------|----------------------------------|-----------------------------|-------------------|------------------|

| Syntax:           | [label] B0                       | CF f,b        |                   |                       | Syntax:          | [label] B1                       | FSC f,b                     |                   |                  |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$ |               |                   |                       | Operands:        | $0 \le f \le 12$ $0 \le b \le 7$ |                             |                   |                  |

| Operation:        | $0 \rightarrow (f < b$           | >)            |                   |                       | Operation:       | skip if (f<                      | b>) = 0                     |                   |                  |

| Status Affected:  | None                             |               |                   |                       | Status Affected: | None                             |                             |                   |                  |

| Encoding:         | 01                               | 00bb          | bfff              | ffff                  | Encoding:        | 01                               | 10bb                        | bfff              | ffff             |

| Description:      | Bit 'b' in re                    | egister 'f' i | s cleared.        | <u> </u>              | Description:     |                                  | register 'f' is             |                   | ne next          |

| Words:            | 1                                |               |                   |                       |                  |                                  | is execute<br>register 'f', |                   | the next         |

| Cycles:           | 1                                |               |                   |                       |                  | instruction                      | is discarde                 | ed, and a N       | IOP is           |

| Q Cycle Activity: | Q1                               | Q2            | Q3                | Q4                    |                  | executed instruction             | nstead, ma                  | king this a       | 2Tcy             |

|                   | Decode                           | Read register | Process<br>data   | Write<br>register 'f' | Words:           | 1                                |                             |                   |                  |

|                   |                                  | 'f'           |                   |                       | Cycles:          | 1(2)                             |                             |                   |                  |

| Example           | cample BCF FLAG REG, 7           |               | Q Cycle Activity: | Q1                    | Q2               | Q3                               | Q4                          |                   |                  |

| •                 | Before In                        | struction     | 1                 |                       |                  | Decode                           | Read<br>register 'f'        | Process<br>data   | No-<br>Operation |

|                   | After Inst                       | _             | EG = 0xC7         | 7                     | If Skip:         | (2nd Cyc                         | ele)                        |                   |                  |

|                   |                                  | FLAG_R        | EG = 0x47         |                       | ·                | Q1                               | Q2                          | Q3                | Q4               |

|                   |                                  |               |                   |                       |                  | No-<br>Operation                 | No-<br>Operation            | No-<br>Operation  | No-<br>Operation |

|                   |                                  |               |                   |                       | Example          | HERE<br>FALSE<br>TRUE            | BTFSC<br>GOTO<br>•          | FLAG,1<br>PROCESS | _CODE            |

|                   |                                  |               |                   |                       |                  | Before In                        | struction                   |                   |                  |

| BSF               | Bit Set f                            |                         |                 |                       |  |  |

|-------------------|--------------------------------------|-------------------------|-----------------|-----------------------|--|--|

| Syntax:           | [label] BS                           | SF f,b                  |                 |                       |  |  |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$ |                         |                 |                       |  |  |

| Operation:        | $1 \rightarrow (f < b)$              | >)                      |                 |                       |  |  |

| Status Affected:  | None                                 |                         |                 |                       |  |  |

| Encoding:         | 01                                   | 01bb                    | bfff            | ffff                  |  |  |

| Description:      | Bit 'b' in re                        | gister 'f' is           | s set.          |                       |  |  |

| Words:            | 1                                    |                         |                 |                       |  |  |

| Cycles:           | 1                                    |                         |                 |                       |  |  |

| Q Cycle Activity: | Q1                                   | Q2                      | Q3              | Q4                    |  |  |

|                   | Decode                               | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |

|                   |                                      |                         |                 |                       |  |  |

BSF FLAG\_REG, Before Instruction  $FLAG_REG = 0x0A$

After Instruction FLAG\_REG = 0x8A

Example

PC = address HERE

address TRUE

if FLAG<1>=0, PC =

if FLAG<1>=1, PC = address FALSE

After Instruction

NOP No Operation Syntax: [label] NOP Operands: None Operation: No operation Status Affected: None Encoding: 0000 0xx00000 Description: No operation. Words: Cycles: 1 Q3 Q4 Q Cycle Activity: Q1 Q2 Decode No-No-No-Operation Operation Operation

NOP

| RETFIE            | Return from Interrupt                                                                                                                                                                              |                  |                    |                    |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                          | RETFIE           |                    |                    |  |  |  |  |

| Operands:         | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |

| Operation:        | $\begin{array}{c} TOS \to P \\ 1 \to GIE \end{array}$                                                                                                                                              | PC,              |                    |                    |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |

| Encoding:         | 0.0                                                                                                                                                                                                | 0000             | 0000               | 1001               |  |  |  |  |

| Description:      | Return from Interrupt. Stack is POPed and Top of Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a two cycle instruction. |                  |                    |                    |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                 | Q2               | Q3                 | Q4                 |  |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                             | No-<br>Operation | Set the<br>GIE bit | Pop from the Stack |  |  |  |  |

| 2nd Cycle         | No-<br>Operation                                                                                                                                                                                   | No-<br>Operation | No-<br>Operation   | No-<br>Operation   |  |  |  |  |

OPTION

Load Option Register

Syntax:

[ label ] OPTION

Operands:

None

Operation:  $(W) \rightarrow OPTION$

Status Affected: None

Encoding:

Description:

Example

The contents of the W register are loaded in the OPTION register. This instruction is supported for code compatibility with PIC16C5X products. Since OPTION is a readable/writable register, the user can directly address it.

0110

0010

0000

Words: 1

Cycles: 1

Example

To maintain upward compatibility with future PIC16CXX products, do not use this instruction.

After Interrupt

PC = TOS GIE = 1

| RLF               | Rotate Left f the                                                                                           | rough Ca                    | rry                  | RRF               | Rotate F                       | Right f th                                                  | rough C                                                                  | arry                  |

|-------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|-------------------|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|

| Syntax:           | [ label ] RLF                                                                                               | f,d                         |                      | Syntax:           | [ label ]                      | RRF f,                                                      | d                                                                        |                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                             |                             |                      | Operands:         | $0 \le f \le 12$ $d \in [0,1]$ |                                                             |                                                                          |                       |

| Operation:        | See description                                                                                             | below                       |                      | Operation:        | See des                        | cription b                                                  | elow                                                                     |                       |

| Status Affected:  | С                                                                                                           |                             |                      | Status Affected:  | С                              |                                                             |                                                                          |                       |

| Encoding:         | 00 1101                                                                                                     | dfff                        | ffff                 | Encoding:         | 0.0                            | 1100                                                        | dfff                                                                     | ffff                  |

| Description:      | The contents of re one bit to the left ti Flag. If 'd' is 0 the W register. If 'd' is back in register 'f'. | nrough the<br>result is pla | Carry<br>ced in the  | Description:      | one bit to<br>Flag. If 'd'     | the right t<br>is 0 the re<br>r. If 'd' is 1<br>gister 'f'. | ister 'f' are<br>hrough the<br>esult is pla-<br>the result<br>Register f | e Carry<br>ced in the |

| Words:            | 1                                                                                                           |                             |                      | Words:            | 1                              |                                                             |                                                                          |                       |

| Cycles:           | 1                                                                                                           |                             |                      | Cycles:           | 1                              |                                                             |                                                                          |                       |

| Q Cycle Activity: | Q1 Q2                                                                                                       | Q3                          | Q4                   | Q Cycle Activity: | Q1                             | Q2                                                          | Q3                                                                       | Q4                    |

|                   | Decode Read<br>register<br>'f'                                                                              | Process<br>data             | Write to destination |                   | Decode                         | Read<br>register<br>'f'                                     | Process<br>data                                                          | Write to destination  |

| Example           | RLF R                                                                                                       | EG1,0                       |                      | Example           | RRF                            |                                                             | REG1,0                                                                   |                       |

|                   | Before Instruction                                                                                          | n                           |                      |                   | Before Ir                      | struction                                                   | 1                                                                        |                       |

|                   | REG1<br>C                                                                                                   | = 111<br>= 0                | 0 0110               |                   |                                | REG1                                                        |                                                                          | 0 0110                |