Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-04-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.1 STATUS REGISTER

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The STATUS register, shown in Figure 4-9, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                        | R-1                                        | R-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-x                                                               | R/W-x                         | R/W-x        |                                                                                     |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|--------------|-------------------------------------------------------------------------------------|--|--|--|

| IRP      | RP1                                                                                                                                                                                                                                                          | RP0                                          | TO                                         | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Z                                                                   | DC                            | С            | R = Readable bit                                                                    |  |  |  |

| bit7     |                                                                                                                                                                                                                                                              |                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                               | bit0         | W = Writable bit<br>- n = Value at POR reset<br>x = unknown                         |  |  |  |

| bit 7:   | IRP: Regls<br>1 = Bank 2<br>0 = Bank 0                                                                                                                                                                                                                       | , 3 (100h - 1                                | 1FFh)                                      | ed for indire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ect addressir                                                       | ng)                           |              |                                                                                     |  |  |  |

| bit 6-5: | <ul> <li>RP1:RP0: Register Bank Select bits (used for direct addressing)</li> <li>11 = Bank 3 (180h - 1FFh)</li> <li>10 = Bank 2 (100h - 17Fh)</li> <li>01 = Bank 1 (80h - FFh)</li> <li>00 = Bank 0 (00h - 7Fh)</li> <li>Each bank is 128 bytes.</li> </ul> |                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                               |              |                                                                                     |  |  |  |

| bit 4:   | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                              |                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                               |              |                                                                                     |  |  |  |

| bit 3:   | <b>PD</b> : Power-<br>1 = After po<br>0 = By exec                                                                                                                                                                                                            | ower-up or                                   |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tion                                                                |                               |              |                                                                                     |  |  |  |

| bit 2:   | <b>Z</b> : Zero bit<br>1 = The res $0 = The res$                                                                                                                                                                                                             |                                              |                                            | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tion is zero<br>tion is not ze                                      | ero                           |              |                                                                                     |  |  |  |

| bit 1:   | DC: Digit carry/borrow bit (for ADDUW, ADDLW, SUBLW, and SUBWF instructions) (For borrow the polarity is reversed).<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result        |                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                               |              |                                                                                     |  |  |  |

| bit 0:   | 1 = A carry<br>0 = No carr<br>Note: a sub                                                                                                                                                                                                                    | -out from th<br>y-out from<br>otraction is o | the most sig<br>the most si<br>executed by | nificant bit of gnificant bit of gnifica | of the result of<br>t of the result<br>tof the result<br>two's comp | occurred<br>t<br>lement of th | ne second op | orrow the polarity is reversed).<br>perand.<br>ow order bit of the source register. |  |  |  |

#### FIGURE 4-9: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

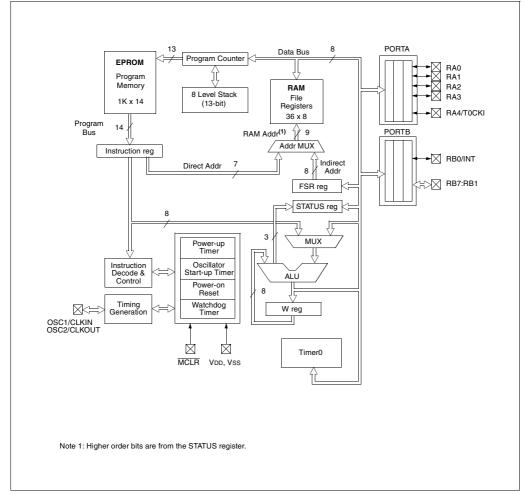

#### 4.2.2.6 PIE2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt enable bit.

#### FIGURE 4-20: PIE2 REGISTER (ADDRESS 8Dh)

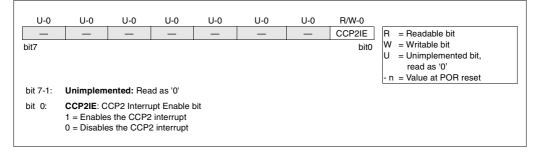

#### 4.2.2.8 PCON REGISTER

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

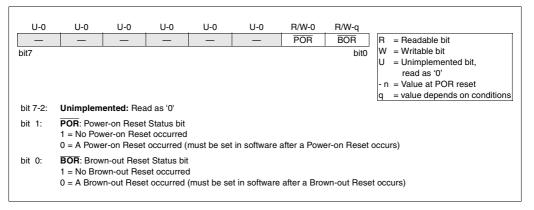

The Power Control register (PCON) contains a flag bit to allow differentiation between a Power-on Reset to an external MCLR reset or WDT reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Poweron Reset condition.

#### Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### FIGURE 4-22: PCON REGISTER FOR PIC16C62/64/65 (ADDRESS 8Eh)

#### FIGURE 4-23: PCON REGISTER FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 (ADDRESS 8Eh)

### 10.0 CAPTURE/COMPARE/PWM (CCP) MODULE(s)

#### Applicable Devices

| 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP1 |

|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|------|

| 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP2 |

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM master/slave duty cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP modules(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### CCP1 module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the *Embedded Control Handbook*, "Using the CCP Modules" (AN594).

#### TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

#### EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 78.125 kHz, Fosc = 20 MHz TMR2 prescale = 1

$1/78.125 \text{ kHz} = [(PR2) + 1] \cdot 4 \cdot 1/20 \text{ MHz} \cdot 1$   $12.8 \ \mu s = [(PR2) + 1] \cdot 4 \cdot 50 \text{ ns} \cdot 1$ PR2 = 63

Find the maximum resolution of the duty cycle that can be used with a 78.125 kHz frequency and 20 MHz oscillator:

| 1/78.125 kHz | = $2^{\text{PWM RESOLUTION}} \cdot 1/20 \text{ MHz} \cdot 1$  |

|--------------|---------------------------------------------------------------|

| 12.8 µs      | = $2^{\text{PWM RESOLUTION}} \bullet 50 \text{ ns} \bullet 1$ |

| 256          | $= 2^{\text{PWM RESOLUTION}}$                                 |

| log(256)     | = (PWM Resolution) • $log(2)$                                 |

| 8.0          | = PWM Resolution                                              |

|              |                                                               |

At most, an 8-bit resolution duty cycle can be obtained from a 78.125 kHz frequency and a 20 MHz oscillator, i.e.,  $0 \leq$  CCPR1L:CCP1CON<5:4>  $\leq$  255. Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-3 lists example PWM frequencies and resolutions for Fosc = 20 MHz. The TMR2 prescaler and PR2 values are also shown.

10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 10-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz 4.88 kHz 19 |      | 19.53 kHz | 19.53 kHz 78.12 kHz |      | 208.3 kHz |  |

|----------------------------|----------------------|------|-----------|---------------------|------|-----------|--|

| Timer Prescaler (1, 4, 16) | 16                   | 4    | 1         | 1                   | 1    | 1         |  |

| PR2 Value                  | 0xFF                 | 0xFF | 0xFF      | 0x3F                | 0x1F | 0x17      |  |

| Maximum Resolution (bits)  | 10                   | 10   | 10        | 8                   | 7    | 5.5       |  |

#### TABLE 10-4: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Add                  | Name    | Bit 7                | Bit 6                      | Bit 5               | Bit 4               | Bit 3                    | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|----------------------|---------|----------------------|----------------------------|---------------------|---------------------|--------------------------|------------|------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                       | TOIE                | INTE                | RBIE                     | T0IF       | INTF       | RBIF   |      |                    | 0000  |                       |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup> | (3)                        | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF                    | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 0Dh <sup>(4)</sup>   | PIR2    | —                    | _                          | _                   | _                   | -                        | -          | -          | CCP2IF |      | 0                  |       | 0                     |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup> | (3)                        | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE                    | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 8Dh <sup>(4)</sup>   | PIE2    | —                    | _                          | _                   | _                   |                          | —          |            | CCP2IE |      | 0                  |       | 0                     |

| 87h                  | TRISC   | PORTC D              | ata Direc                  | ction registe       | er                  |                          |            |            |        | 1111 | 1111               | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding re           | egister for                | the Least           | Significant         | Byte of the              | 16-bit TMF | R1 registe | r      | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding re           | egister for                | the Most S          | Significant I       | Byte of the <sup>·</sup> | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h                  | T1CON   | _                    | _                          | T1CKPS1             | T1CKPS0             | T1OSCEN                  | T1SYNC     | TMR1CS     | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/C            | Compare/                   | PWM1 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture/C            | Compare/                   | PWM1 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                  | CCP1CON | —                    | _                          | CCP1X               | CCP1Y               | CCP1M3                   | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00    | 0000                  |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/C            | Capture/Compare/PWM2 (LSB) |                     |                     |                          |            |            |        |      |                    | uuuu  | uuuu                  |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/C            | Compare/                   | PWM2 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh <sup>(4)</sup>   | CCP2CON | —                    | _                          | CCP2X               | CCP2Y               | CCP2M3                   | CCP2M2     | CCP2M1     | CCP2M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

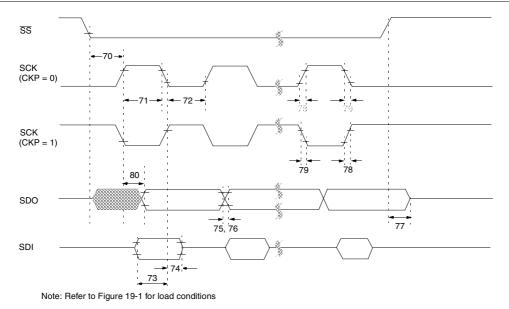

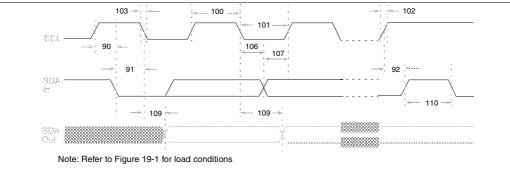

#### 11.3 SPI Mode for PIC16C66/67

This section contains register definitions and operational characterisitics of the SPI module on the PIC16C66 and PIC16C67 only.

#### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C66/67)

| R/W-0  | R/W-0                                                                                                                                                                                                                         | R-0                                                      | R-0                                          | R-0                                                                                 | R-0                                            | R-0          | R-0          |                                                                                      |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------|--|--|--|

| SMP    | CKE                                                                                                                                                                                                                           | D/A                                                      | Р                                            | S                                                                                   | R/W                                            | UA           | BF           | R = Readable bit                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                               |                                                          |                                              |                                                                                     |                                                |              | bit0         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7: | <u>SPI Mas</u><br>1 = Inpu<br>0 = Inpu<br><u>SPI Slav</u>                                                                                                                                                                     | <u>ster Mod</u><br>it data sa<br>it data sa<br>ve Mode   | ampled at e<br>ampled at r                   | end of data<br>niddle of da                                                         | output time<br>ata output tir<br>ed in slave m |              |              |                                                                                      |  |  |  |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$                                                                                                                                                              | <u>)</u><br>a transm<br>a transm<br><u>1</u><br>a transm | itted on ris<br>itted on fal<br>itted on fal | ct (Figure <sup>-</sup><br>ing edge of<br>ling edge o<br>ling edge o<br>ing edge of | f SCK<br>f SCK                                 | e 11-12, an  | d Figure 11- | 13)                                                                                  |  |  |  |

| bit 5: | <ul> <li>D/Ā: Data/Āddress bit (I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul> |                                                          |                                              |                                                                                     |                                                |              |              |                                                                                      |  |  |  |

| bit 4: | detected<br>1 = India                                                                                                                                                                                                         | d last, SS<br>cates tha                                  | SPEN is cle                                  | eared)<br>t has been                                                                | cleared whe<br>detected las                    |              |              | isabled, or when the Start bit is<br>T)                                              |  |  |  |

| bit 3: | detected<br>1 = India                                                                                                                                                                                                         | d last, SS<br>cates tha                                  | SPEN is cle                                  | eared)<br>t has been                                                                | cleared whe                                    |              |              | lisabled, or when the Stop bit is                                                    |  |  |  |

| bit 2: | This bit                                                                                                                                                                                                                      | holds th<br>match to<br>d                                | ne R/W bit                                   |                                                                                     |                                                |              | Iress match  | . This bit is only valid from the                                                    |  |  |  |

| bit 1: | 1 = India                                                                                                                                                                                                                     | cates that                                               | at the user                                  | it I <sup>2</sup> C mode<br>needs to up<br>I to be upda                             | pdate the ad                                   | dress in the | e SSPADD r   | egister                                                                              |  |  |  |

| bit 0: | BF: Buff                                                                                                                                                                                                                      | fer Full S                                               | status bit                                   |                                                                                     |                                                |              |              |                                                                                      |  |  |  |

|        | 1 = Rec<br>0 = Rec                                                                                                                                                                                                            | eive com<br>eive not                                     | complete,                                    | es)<br>PBUF is full<br>SSPBUF is                                                    |                                                |              |              |                                                                                      |  |  |  |

|        | 1 = Tran                                                                                                                                                                                                                      | ismit in p                                               |                                              | SPBUF is f<br>PBUF is en                                                            |                                                |              |              |                                                                                      |  |  |  |

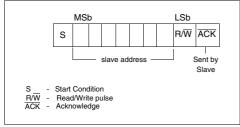

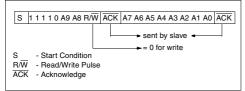

#### 11.4.2 ADDRESSING I<sup>2</sup>C DEVICES

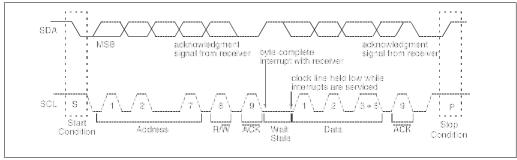

There are two address formats. The simplest is the 7-bit address format with a R/W bit (Figure 11-15). The more complex is the 10-bit address with a R/W bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

#### FIGURE 11-16: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

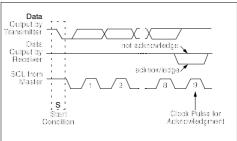

#### 11.4.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

#### FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 11-18: DATA TRANSFER WAIT STATE

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

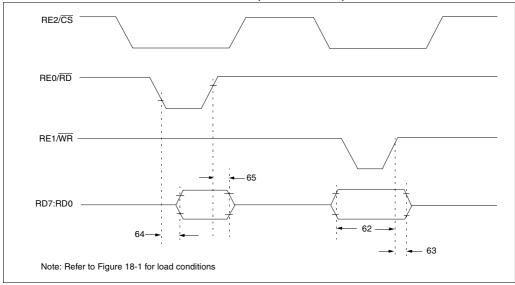

#### FIGURE 18-8: PARALLEL SLAVE PORT TIMING (PIC16C64A/R64)

#### TABLE 18-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C64A/R64)

| Parameter<br>No. | Sym      | Characteristic                                                                    | Min                     | Тур† | Max | Units | Conditions |                        |

|------------------|----------|-----------------------------------------------------------------------------------|-------------------------|------|-----|-------|------------|------------------------|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (set      | 20                      | —    | _   | ns    |            |                        |

|                  |          |                                                                                   |                         |      | _   | -     | ns         | Extended<br>Range Only |

| 63*              | TwrH2dtl | $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data–in invalid (hold | PIC16 <b>C</b> 64A/R64  | 20   | —   | —     | ns         |                        |

|                  |          | time)                                                                             | PIC16 <b>LC</b> 64A.R64 | 35   | _   | —     | ns         |                        |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid         |                         | I    | _   | 80    | ns         |                        |

|                  |          |                                                                                   |                         |      | _   | 90    | ns         | Extended<br>Range Only |

| 65*              | TrdH2dtI | $\overline{\text{RD}}$ for $\overline{\text{CS}}$ to data-out invalid             |                         | 10   | _   | 30    | ns         |                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

NOTES:

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 19.1 DC Characteristics: PIC16C65-04 (Commercial, Industrial) PIC16C65-10 (Commercial, Industrial) PIC16C65-20 (Commercial, Industrial)

|                       | Standard Operating Conditions (unless otherwise stated)          |                                                                                                                           |                                       |                    |                   |                |                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DC CHA                | ARACTERISTICS                                                    | Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and<br>0°C $<$ TA $\leq$ +70°C for commercial |                                       |                    |                   |                |                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                       |                                                                  |                                                                                                                           | $\leq$ TA $\leq$ +70°C for commercial |                    |                   |                |                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Param<br>No.          | Characteristic                                                   | Sym                                                                                                                       | Min                                   | Тур†               | Max               | Units          | Conditions                                                                                                                                                                                                                                                    |  |  |  |  |  |

| D001<br>D001A         | Supply Voltage                                                   | Vdd                                                                                                                       | 4.0<br>4.5                            | -                  | 6.0<br>5.5        | v<br>v         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                       |  |  |  |  |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr                                                                                                                       | -                                     | 1.5                | -                 | V              |                                                                                                                                                                                                                                                               |  |  |  |  |  |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                                                                                                                      | -                                     | Vss                | -                 | V              | See section on Power-on Reset for details                                                                                                                                                                                                                     |  |  |  |  |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                                                                                                                      | 0.05                                  | -                  | -                 | V/ms           | See section on Power-on Reset for details                                                                                                                                                                                                                     |  |  |  |  |  |

| D010                  | Supply Current (Note 2, 5)                                       | IDD                                                                                                                       | -                                     | 2.7                | 5                 | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                 |  |  |  |  |  |

| D013                  |                                                                  |                                                                                                                           | -                                     | 13.5               | 30                | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                             |  |  |  |  |  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3, 5)                                | IPD                                                                                                                       |                                       | 10.5<br>1.5<br>1.5 | 800<br>800<br>800 | μΑ<br>μΑ<br>μΑ | $\label{eq:VDD} \begin{array}{l} VDD=4.0V, WDT \mbox{ enabled}, -40^\circ C \mbox{ to } +85^\circ C \\ VDD=4.0V, WDT \mbox{ disabled}, -0^\circ C \mbox{ to } +70^\circ C \\ VDD=4.0V, WDT \mbox{ disabled}, -40^\circ C \mbox{ to } +85^\circ C \end{array}$ |  |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

19.3

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### DC Characteristics: PIC16C65-04 (Commercial, Industrial) PIC16C65-10 (Commercial, Industrial) PIC16C65-20 (Commercial, Industrial) PIC16LC65-04 (Commercial, Industrial)

|              |                                       |                                                                                                                                         | <b>rd Operati</b><br>ng tempera | •        | -40°C   | ;` ≤ T, | ss otherwise stated)<br>A ≤ +85°C for industrial and                                                                                                     |  |  |  |  |  |

|--------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DC CHA       | RACTERISTICS                          | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial Operating voltage VDD range as described in DC spec Section 19.1 and Section 19.2 |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

| Param<br>No. | Characteristic                        | Sym                                                                                                                                     | Min                             | Тур<br>† | Мах     | Units   | Conditions                                                                                                                                               |  |  |  |  |  |

|              | Input Low Voltage                     |                                                                                                                                         |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

|              | I/O ports                             | VIL                                                                                                                                     |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

| D030         | with TTL buffer                       |                                                                                                                                         | Vss                             | -        | 0.15Vdd | V       | For entire VDD range                                                                                                                                     |  |  |  |  |  |

| D030A        |                                       |                                                                                                                                         | Vss                             | -        | 0.8V    | V       | $4.5V \leq V \text{DD} \leq 5.5V$                                                                                                                        |  |  |  |  |  |

| D031         | with Schmitt Trigger buffer           |                                                                                                                                         | Vss                             | -        | 0.2Vdd  | V       |                                                                                                                                                          |  |  |  |  |  |

| D032         | MCLR, OSC1 (in RC mode)               |                                                                                                                                         | Vss                             | -        | 0.2Vdd  | V       |                                                                                                                                                          |  |  |  |  |  |

| D033         | OSC1 (in XT, HS and LP)               |                                                                                                                                         | Vss                             | -        | 0.3Vdd  | V       | Note1                                                                                                                                                    |  |  |  |  |  |

|              | Input High Voltage                    |                                                                                                                                         |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

|              | I/O ports                             | Vін                                                                                                                                     |                                 | -        |         |         |                                                                                                                                                          |  |  |  |  |  |

| D040         | with TTL buffer                       |                                                                                                                                         | 2.0                             | -        | Vdd     | V       | $4.5V \leq V \text{DD} \leq 5.5V$                                                                                                                        |  |  |  |  |  |

| D040A        |                                       |                                                                                                                                         | 0.25VDD+<br>0.8V                | -        | VDD     | V       | For entire VDD range                                                                                                                                     |  |  |  |  |  |

| D041         | with Schmitt Trigger buffer           |                                                                                                                                         | 0.8VDD                          | -        | Vdd     |         | For entire VDD range                                                                                                                                     |  |  |  |  |  |

| D042         | MCLR                                  |                                                                                                                                         | 0.8VDD                          | -        | Vdd     | V       |                                                                                                                                                          |  |  |  |  |  |

| D042A        | OSC1 (XT, HS and LP)                  |                                                                                                                                         | 0.7 VDD                         | -        | Vdd     | V       | Note1                                                                                                                                                    |  |  |  |  |  |

| D043         | OSC1 (in RC mode)                     |                                                                                                                                         | 0.9Vdd                          | -        | Vdd     | V       |                                                                                                                                                          |  |  |  |  |  |

| D070         | PORTB weak pull-up current            | <b>I</b> PURB                                                                                                                           | 50                              | 250      | 400     | μA      | VDD = 5V, VPIN = VSS                                                                                                                                     |  |  |  |  |  |

|              | Input Leakage Current<br>(Notes 2, 3) |                                                                                                                                         |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

| D060         | I/O ports                             | lı∟                                                                                                                                     | -                               | -        | ±1      | μA      | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance                                                                                                      |  |  |  |  |  |

| D061         | MCLR, RA4/T0CKI                       |                                                                                                                                         | -                               | -        | ±5      | μA      | $V_{SS} \leq V_{PIN} \leq V_{DD}$                                                                                                                        |  |  |  |  |  |

| D063         | OSC1                                  |                                                                                                                                         | -                               | -        | ±5      | μΑ      | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \ &X{\sf T}, \ &H{\sf S}, \ and \\ &L{\sf P} \ osc \ configuration \end{split}$ |  |  |  |  |  |

| 1            | Output Low Voltage                    |                                                                                                                                         | 1                               |          |         |         |                                                                                                                                                          |  |  |  |  |  |

| D080         | I/O ports                             | Vol                                                                                                                                     | -                               | -        | 0.6     | V       | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                                              |  |  |  |  |  |

| D083         | OSC2/CLKOUT (RC osc config)           |                                                                                                                                         | -                               | -        | 0.6     | V       | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                                              |  |  |  |  |  |

|              | Output High Voltage                   |                                                                                                                                         |                                 |          |         |         |                                                                                                                                                          |  |  |  |  |  |

| D090         | I/O ports (Note 3)                    | Vон                                                                                                                                     | VDD-0.7                         | -        | -       | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                                                             |  |  |  |  |  |

| D092         | OSC2/CLKOUT (RC osc config)           |                                                                                                                                         | VDD-0.7                         | -        | -       | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                                                             |  |  |  |  |  |

| D150*        | Open-Drain High Voltage               | VOD                                                                                                                                     | -                               | -        | 14      | V       | RA4 pin                                                                                                                                                  |  |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 19.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats: