Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-04-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

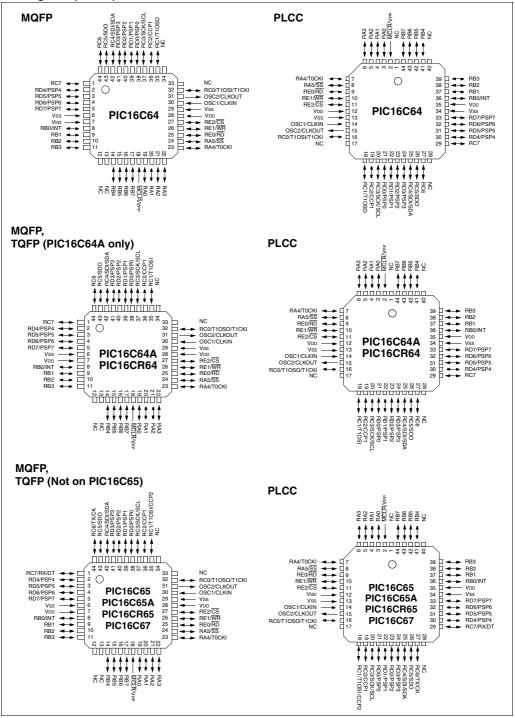

#### Pin Diagrams (Cont.'d)

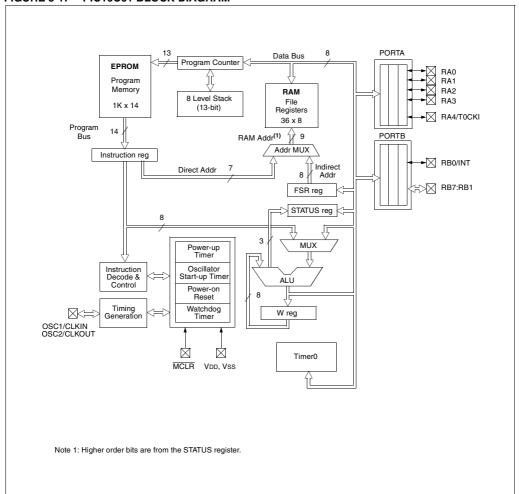

FIGURE 3-1: PIC16C61 BLOCK DIAGRAM

### FIGURE 4-15: PIE1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 8Ch)

| R/W-0  | R/W-0                                   | R/W-0       | R/W-0        | R/W-0        | R/W-0        | R/W-0  | R/W-0  | T                                                                            |

|--------|-----------------------------------------|-------------|--------------|--------------|--------------|--------|--------|------------------------------------------------------------------------------|

| PSPIE  | _                                       | RCIE        | TXIE         | SSPIE        | CCP1IE       | TMR2IE | TMR1IE | R = Readable bit                                                             |

| it7    |                                         |             |              |              |              |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| oit 7: | PSPIE: Par<br>1 = Enable<br>0 = Disable | s the PSP i | ead/write i  | nterrupt     | upt Enable b | it     |        |                                                                              |

| bit 6: | Reserved:                               | Always ma   | intain this  | oit clear.   |              |        |        |                                                                              |

| bit 5: | RCIE: USA<br>1 = Enable<br>0 = Disable  | s the USAF  | RT receive i | nterrupt     |              |        |        |                                                                              |

| bit 4: | TXIE: USA<br>1 = Enable<br>0 = Disable  | s the USAF  | RT transmit  | interrupt    |              |        |        |                                                                              |

| bit 3: | SSPIE: Syr<br>1 = Enable<br>0 = Disable | s the SSP i | nterrupt     | Interrupt Er | nable bit    |        |        |                                                                              |

| bit 2: | CCP1IE: C<br>1 = Enable<br>0 = Disable  | s the CCP1  | interrupt    | bit          |              |        |        |                                                                              |

| bit 1: | TMR2IE: T<br>1 = Enable:<br>0 = Disable | s the TMR2  | to PR2 m     | atch interru | pt           |        |        |                                                                              |

| bit 0: | TMR1IE: T<br>1 = Enable:<br>0 = Disable | s the TMR1  | overflow i   | nterrupt     | t            |        |        |                                                                              |

#### 4.2.2.5 PIR1 REGISTER

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

#### FIGURE 4-16: PIR1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 0Ch)

| R/   | /W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |                                       |

|------|------|-------|-----|-----|-------|--------|--------|--------|---------------------------------------|

| -    | _    | _     | _   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF | R = Readable bit                      |

| bit7 |      |       |     |     |       |        |        | bit0   | U = Unimplemented bit,<br>read as '0' |

|      |      | _     |     |     |       |        |        |        | - n = Value at POR reset              |

- bit 7-6: Reserved: Always maintain these bits clear.

- bit 5-4: Unimplemented: Read as '0'

- bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit

- 1 = The transmission/reception is complete (must be cleared in software)

- 0 = Waiting to transmit/receive

- bit 2: CCP1IF: CCP1 Interrupt Flag bit

#### Capture Mode

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

#### Compare Mode

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

#### **PWM Mode**

Unused in this mode

- bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflow occurred (must be cleared in software)

- 0 = No TMR1 register overflow occurred

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 4.3 PCL and PCLATH

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

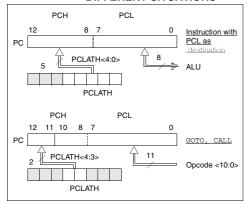

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-24 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-24: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or a POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no status bits to indicate stack overflows or stack underflow conditions

Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address

#### 4.4 Program Memory Paging

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PIC16C6X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C6X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

NOTES:

TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                    |

|------------|------|-------------|-----------------------------------------------------------------------------|

| RA0        | bit0 | TTL         | Input/output                                                                |

| RA1        | bit1 | TTL         | Input/output                                                                |

| RA2        | bit2 | TTL         | Input/output                                                                |

| RA3        | bit3 | TTL         | Input/output                                                                |

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0. Output is open drain type. |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

#### TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5              | Bit 4                                        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|--------------------|----------------------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | _     | _     | RA5 <sup>(1)</sup> | RA4                                          | RA3   | RA2   | RA1   | RA0   | xx xxxx                  | uu uuuu                   |

| 85h     | TRISA | _     | _     | PORTA Data         | PORTA Data Direction Register <sup>(1)</sup> |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

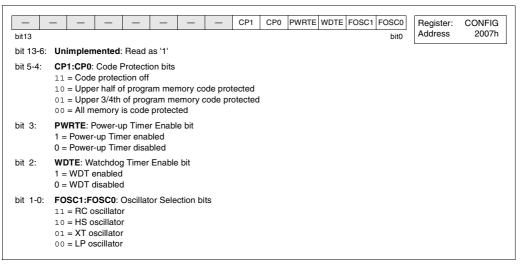

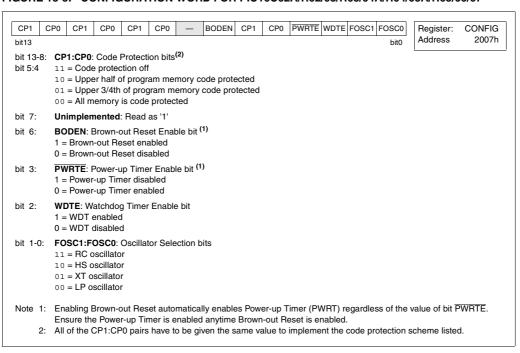

#### FIGURE 13-2: CONFIGURATION WORD FOR PIC16C62/64/65

#### FIGURE 13-3: CONFIGURATION WORD FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

TABLE 13-9: STATUS BITS AND THEIR SIGNIFICANCE FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |

| 0   | x   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

Legend: x = unknown, u = unchanged

TABLE 13-10: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C61/62/64/65

|                                    | Program Counter       | STATUS    | PCON <sup>(2)</sup> |

|------------------------------------|-----------------------|-----------|---------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0 -                 |

| MCLR reset during normal operation | 000h                  | 000u uuuu | u-                  |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | u-                  |

| WDT Reset                          | 000h                  | 0000 luuu | u-                  |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | u-                  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | u-                  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

2: The PCON register is not implemented on the PIC16C61.

TABLE 13-11: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

|                                    | Program Counter       | STATUS    | PCON |

|------------------------------------|-----------------------|-----------|------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0x   |

| MCLR reset during normal operation | 000h                  | 000u uuuu | uu   |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | uu   |

| WDT Reset                          | 000h                  | 0000 luuu | uu   |

| Brown-out Reset                    | 000h                  | 0001 1uuu | u0   |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | uu   |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | uu   |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

#### 13.6 Context Saving During Interrupts

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 13-1 stores and restores the STATUS and W registers. Example 13-2 stores and restores the STATUS, W, and PCLATH registers (Devices with paged program memory). For all PIC16C6X devices with greater than 1K of program memory (all devices except PIC16C61), the register, W\_TEMP, must be

defined in banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1. 0x120 in bank 2. and 0x1A0 in bank 3).

#### The examples:

- a) Stores the W register

- b) Stores the STATUS register in bank 0

- c) Stores PCLATH

- d) Executes ISR code

- e) Restores PCLATH

- f) Restores STATUS register (and bank select bit)

- g) Restores W register

#### **EXAMPLE 13-1: SAVING STATUS AND W REGISTERS IN RAM (PIC16C61)**

```

MOVWF

W TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

MOVWE

STATUS TEMP

; Save status to bank zero STATUS TEMP register

: (ISR)

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP, F

;Swap W TEMP

;Swap W TEMP into W

SWAPF

W TEMP, W

```

### EXAMPLE 13-2: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM (ALL OTHER PIC16C6X DEVICES)

```

;Copy W to TEMP register, could be bank one or zero

MOVWF

W TEMP

SWAPF

STATUS, W

;Swap status to be saved into W

CLRF

STATUS

;bank 0, regardless of current bank, Clears IRP, RP1, RP0

MOVWF

STATUS TEMP

; Save status to bank zero STATUS TEMP register

PCLATH, W

MOVE

;Only required if using pages 1, 2 and/or 3

;Save PCLATH into W

PCLATH TEMP

MOVWF

CLRF

PCLATH

; Page zero, regardless of current page

BCF

STATUS, IRP

;Return to Bank 0

FSR, W

;Copy FSR to W

MOVWF

FSR TEMP

;Copy FSR from W to FSR TEMP

· (TSR)

MOVF

PCLATH TEMP, W

;Restore PCLATH

MOVWF

PCLATH

; Move W into PCLATH

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

: (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP,F

;Swap W TEMP

W_TEMP,W

SWAPF

;Swap W TEMP into W

```

| IORWF             | Inclusive                                                   | OR W                         | with f           |                      |

|-------------------|-------------------------------------------------------------|------------------------------|------------------|----------------------|

| Syntax:           | [ label ]                                                   | IORWF                        | f,d              |                      |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                              | 27                           |                  |                      |

| Operation:        | (W) .OR.                                                    | $(f) \rightarrow (de$        | estination       | 1)                   |

| Status Affected:  | Z                                                           |                              |                  |                      |

| Encoding:         | 0.0                                                         | 0100                         | dfff             | ffff                 |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg | is 0 the re<br>: If 'd' is 1 | sult is plac     | ced in the           |

| Words:            | 1                                                           |                              |                  |                      |

| Cycles:           | 1                                                           |                              |                  |                      |

| Q Cycle Activity: | Q1                                                          | Q2                           | Q3               | Q4                   |

|                   | Decode                                                      | Read<br>register<br>'f'      | Process<br>data  | Write to destination |

| Example           | IORWF                                                       |                              | RESULT,          | 0                    |

|                   | Before In                                                   |                              |                  |                      |

|                   |                                                             | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |

|                   | After Inst                                                  | • •                          | _ 0.891          |                      |

|                   |                                                             | RESULT                       | = 0x13           | 3                    |

0x93

| MOVLW             | Move Lit        | eral to V           | V                            |               |

|-------------------|-----------------|---------------------|------------------------------|---------------|

| Syntax:           | [ label ]       | MOVLW               | / k                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                              |               |

| Operation:        | $k\to(W)$       |                     |                              |               |

| Status Affected:  | None            |                     |                              |               |

| Encoding:         | 11              | 00xx                | kkkk                         | kkkk          |

| Description:      |                 |                     | k' is loaded<br>ares will as |               |

| Words:            | 1               |                     |                              |               |

| Cycles:           | 1               |                     |                              |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                           | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data              | Write to<br>W |

| Example           | MOVLW           | 0x5A                |                              |               |

|                   | After Inst      |                     |                              |               |

|                   |                 | W =                 | 0x5A                         |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

| MOVF              | Move f                                                                                                                                                                                                                                                  |                         |                 |                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                               | MOVF                    | f,d             |                      |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                      |                         |                 |                      |  |  |  |

| Operation:        | $(f) \rightarrow (destination)$                                                                                                                                                                                                                         |                         |                 |                      |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                      | 1000                    | dfff            | ffff                 |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |                         |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                      | Q2                      | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                  | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |

| Example           | MOVF                                                                                                                                                                                                                                                    | FSR,                    | 0               |                      |  |  |  |

|                   | After Instruction W = value in FSR register                                                                                                                                                                                                             |                         |                 |                      |  |  |  |

Z = 1

| MOVWF             | Move W                                    | to f                    |                 |                       |  |

|-------------------|-------------------------------------------|-------------------------|-----------------|-----------------------|--|

| Syntax:           | [ label ]                                 | MOVWI                   | F f             |                       |  |

| Operands:         | $0 \le f \le 12$                          | .7                      |                 |                       |  |

| Operation:        | $(W) \rightarrow (f)$                     |                         |                 |                       |  |

| Status Affected:  | None                                      |                         |                 |                       |  |

| Encoding:         | 00                                        | 0000                    | 1fff            | ffff                  |  |

| Description:      | Move data                                 | from W r                | egister to      | register              |  |

| Words:            | 1                                         |                         |                 |                       |  |

| Cycles:           | 1                                         |                         |                 |                       |  |

| Q Cycle Activity: | Q1                                        | Q2                      | Q3              | Q4                    |  |

|                   | Decode                                    | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |

| Example           | MOVWF                                     | OPTIC                   | ON_REG          |                       |  |

|                   | Before Instruction OPTION = 0xFF W = 0x4F |                         |                 |                       |  |

|                   | After Inst                                | ruction<br>OPTION       | = 0x4F          | =                     |  |

W = 0x4F

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 15.0 ELECTRICAL CHARACTERISTICS FOR PIC16C61

#### Absolute Maximum Ratings †

| - ·                                                                |                      |

|--------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                     | 55°C to +125°C       |

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | -0.3V to +7.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +14V           |

| Voltage on RA4 pin with respect to Vss                             | 0V to +14V           |

| Total power dissipation (Note 1)                                   | 800 mW               |

| Maximum current out of VSs pin                                     | 150 mA               |

| Maximum current into VDD pin                                       | 100 mA               |

| Input clamp current, IIK (VI < 0 or VI > VDD)                      | ± 20 mA              |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                     | ± 20 mA              |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 20 mA                |

| Maximum current sunk by PORTA                                      | 80 mA                |

| Maximum current sourced by PORTA                                   | 50 mA                |

| Maximum current sunk by PORTB                                      | 150 mA               |

| Maximum current sourced by PORTB                                   | 100 mA               |

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD - \( \subseteq \text{IDD} - \subseteq \text{IOH} \) + \( \subseteq \text{(VDD-VOH)} \) x IOH} + \( \subseteq \text{(VOI x IOL)} \)

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 15-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C61-04                | PIC16C61-20              | PIC16LC61-04               | JW Devices                 |

|-----|----------------------------|--------------------------|----------------------------|----------------------------|

| RC  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| XT  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| HS  | VDD: 4.5V to 5.5V          | VDD: 4.5V to 5.5V        |                            | VDD: 4.5V to 5.5V          |

|     | IDD: 13.5 mA typ. at 5.5V  | IDD: 30 mA max. at 5.5V  | Not recommended for use in | IDD: 30 mA max. at 5.5V    |

|     | IPD: 1.0 μA typ. at 4.5V   | IPD: 1.0 μA typ. at 4.5V | HS mode                    | IPD: 1.0 μA typ. at 4.5V   |

|     | Freq: 4 MHz max.           | Freq: 20 MHz max.        |                            | Freq: 20 MHz max.          |

| LP  | VDD: 4.0V to 6.0V          |                          | VDD: 3.0V to 6.0V          | VDD: 3.0V to 6.0V          |

|     | IDD: 15 μA typ. at 32 kHz, | Not recommended for      | IDD: 32 μA max. at 32 kHz, | IDD: 32 μA max. at 32 kHz, |

|     | 4.0V                       | use in LP mode           | 3.0V                       | 3.0V                       |

|     | IPD: 0.6 μA typ. at 4.0V   | use iii LP mode          | IPD: 9 μA max. at 3.0V     | IPD: 9 μA max. at 3.0V     |

|     | Freq: 200 kHz max.         |                          | Freq: 200 kHz max.         | Freq: 200 kHz max.         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

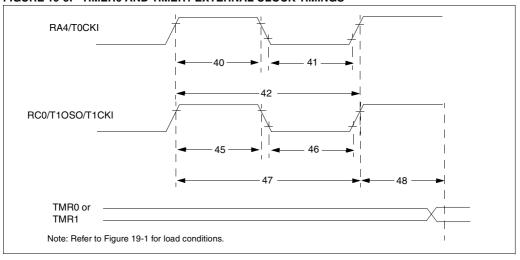

FIGURE 19-5: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 19-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym   | Characteristic        |                                             |                             | Min                                | Typ† | Max   | Units    | Conditions                         |

|--------------|-------|-----------------------|---------------------------------------------|-----------------------------|------------------------------------|------|-------|----------|------------------------------------|

| 40*          | Tt0H  | T0CKI High Pulse V    | Vidth                                       | No Prescaler                | 0.5Tcy + 20                        |      |       | ns       | Must also meet                     |

| 40           | 11011 | Tooki riigiri uise v  |                                             |                             | 10                                 |      |       |          | parameter 42                       |

| 41*          | TtOL  | T0CKI Low Pulse W     | lidth                                       | With Prescaler No Prescaler | 0.5Tcy + 20                        | _    | _     | ns<br>ns | Must also meet                     |

| 41           | TIOL  | TOCKI LOW Fulse W     | /Idili                                      | With Prescaler              | 10                                 |      |       | ns       | parameter 42                       |

| 42*          | Tt0P  | T0CKI Period          |                                             | No Prescaler                | Tcy + 40                           | H    |       | ns       | paramotor 12                       |

|              |       |                       |                                             | With Prescaler              |                                    | _    | _     | ns       | N = prescale value                 |

|              |       |                       |                                             | With Freedomen              | 20 or Tcy + 40                     |      |       | 110      | (2, 4,, 256)                       |

|              |       |                       |                                             |                             | N                                  |      |       |          | , , , ,                            |

| 45*          | Tt1H  | T1CKI High Time       | Synchronous, P                              | rescaler = 1                | 0.5Tcy + 20                        | _    | _     | ns       | Must also meet                     |

|              |       |                       | Synchronous,                                | PIC16 <b>C</b> 6X           | 15                                 | _    | _     | ns       | parameter 47                       |

|              |       |                       | Prescaler = 2,4,8                           | PIC16 <b>LC</b> 6X          | 25                                 | _    | _     | ns       |                                    |

|              |       |                       | Asynchronous                                | PIC16 <b>C</b> 6X           | 30                                 | _    | _     | ns       |                                    |

|              |       |                       |                                             | PIC16 <b>LC</b> 6X          | 50                                 | _    | _     | ns       |                                    |

| 46*          | Tt1L  | T1CKI Low Time        | Synchronous, P                              | rescaler = 1                | 0.5TCY + 20                        | _    | _     | ns       | Must also meet                     |

|              |       |                       | Synchronous,                                | PIC16 <b>C</b> 6X           | 15                                 | _    | _     | ns       | parameter 47                       |

|              |       |                       | Prescaler = 2,4,8                           | PIC16 <b>LC</b> 6X          | 25                                 | _    | _     | ns       |                                    |

|              |       |                       | Asynchronous                                | PIC16 <b>C</b> 6X           | 30                                 | _    | _     | ns       |                                    |

|              |       |                       |                                             | PIC16 <b>LC</b> 6X          | 50                                 | _    | _     | ns       |                                    |

| 47*          | Tt1P  | T1CKI input period    | Synchronous                                 | PIC16 <b>C</b> 6X           | Greater of:<br>30 OR TCY + 40<br>N | _    | _     | ns       | N = prescale value<br>(1, 2, 4, 8) |

|              |       |                       |                                             | PIC16 <b>LC</b> 6X          | Greater of:<br>50 OR TCY + 40<br>N |      |       |          | N = prescale value<br>(1, 2, 4, 8) |

|              |       |                       | Asynchronous                                | PIC16 <b>C</b> 6X           | 60                                 | _    | _     | ns       |                                    |

|              |       |                       |                                             | PIC16 <b>LC</b> 6X          | 100                                | _    | _     | ns       |                                    |

|              | Ft1   | Timer1 oscillator inp |                                             |                             | DC                                 | _    | 200   | kHz      |                                    |

|              |       |                       | (oscillator enabled by setting bit T1OSCEN) |                             |                                    |      |       |          |                                    |

| 48           |       | Delay from external   |                                             |                             | 2Tosc                              | _    | 7Tosc | _        |                                    |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

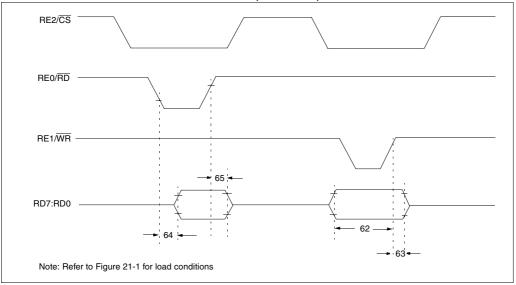

FIGURE 21-8: PARALLEL SLAVE PORT TIMING (PIC16CR65)

TABLE 21-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16CR65)

| Parameter No. | Sym      | Characteristic                               |                    | Min | Typ† | Max | Units | Conditions |

|---------------|----------|----------------------------------------------|--------------------|-----|------|-----|-------|------------|

| 62*           | TdtV2wrH | Data in valid before WR↑ or CS↑ (setup time) |                    | 20  | _    | _   | ns    |            |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data–in invalid (hold          | PIC16 <b>CR</b> 65 | 20  | _    | _   | ns    |            |

|               |          | time)                                        | PIC16LCR65         | 35  | _    | _   | ns    |            |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid                |                    | _   | _    | 80  | ns    |            |

| 65*           | TrdH2dtl | RD↑ or CS↑ to data–out invalid               |                    | 10  | _    | 30  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

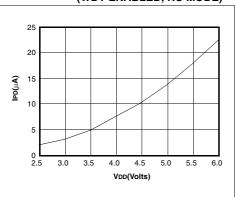

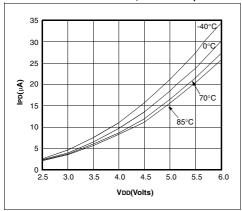

FIGURE 23-3: TYPICAL IPD vs. VDD @ 25°C (WDT ENABLED, RC MODE)

FIGURE 23-4: MAXIMUM IPD vs. VDD (WDT ENABLED, RC MODE)

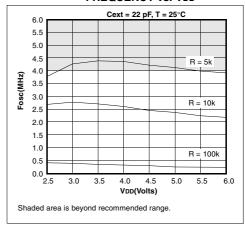

FIGURE 23-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

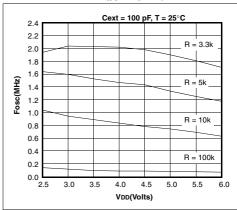

FIGURE 23-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

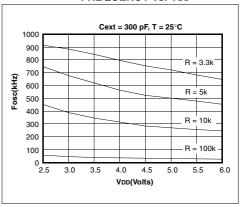

FIGURE 23-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

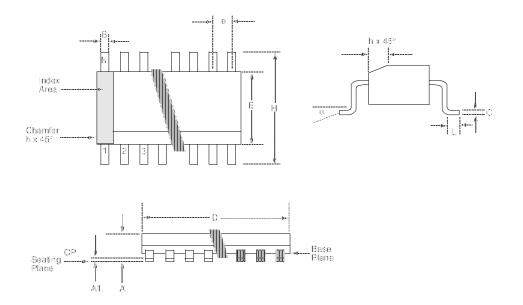

#### 24.5 28-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Plastic SOIC (SO) |             |         |       |        |         |  |  |  |

|--------|----------------------------------|-------------|---------|-------|--------|---------|--|--|--|

|        |                                  | Millimeters |         |       | Inches |         |  |  |  |

| Symbol | Min                              | Max         | Notes   | Min   | Max    | Notes   |  |  |  |

| α      | 0°                               | 8°          |         | 0°    | 8°     |         |  |  |  |

| Α      | 2.362                            | 2.642       |         | 0.093 | 0.104  |         |  |  |  |

| A1     | 0.101                            | 0.300       |         | 0.004 | 0.012  |         |  |  |  |

| В      | 0.355                            | 0.483       |         | 0.014 | 0.019  |         |  |  |  |

| С      | 0.241                            | 0.318       |         | 0.009 | 0.013  |         |  |  |  |

| D      | 17.703                           | 18.085      |         | 0.697 | 0.712  |         |  |  |  |

| E      | 7.416                            | 7.595       |         | 0.292 | 0.299  |         |  |  |  |

| е      | 1.270                            | 1.270       | Typical | 0.050 | 0.050  | Typical |  |  |  |

| Н      | 10.007                           | 10.643      |         | 0.394 | 0.419  |         |  |  |  |

| h      | 0.381                            | 0.762       |         | 0.015 | 0.030  |         |  |  |  |

| L      | 0.406                            | 1.143       |         | 0.016 | 0.045  |         |  |  |  |

| N      | 28                               | 28          |         | 28    | 28     |         |  |  |  |

| CP     | _                                | 0.102       |         | _     | 0.004  |         |  |  |  |

#### F.3 PIC16C15X Family of Devices

|             |                                      | PIC16C154                           | PIC16CR154                          | PIC16C156                           | PIC16CR156                          | PIC16C158                           | PIC16CR158                          |

|-------------|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  |

|             | EPROM Program Memory (x12 words)     | 512                                 | _                                   | 1K                                  | _                                   | 2K                                  | _                                   |

| Memory      | ROM Program Memory (x12 words)       | _                                   | 512                                 | _                                   | 1K                                  | _                                   | 2K                                  |

|             | RAM Data Memory (bytes)              | 25                                  | 25                                  | 25                                  | 25                                  | 73                                  | 73                                  |

| Peripherals | Timer Module(s)                      | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | I/O Pins                             | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  |

|             | Voltage Range (Volts)                | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             |

| Features    | Number of Instructions               | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

|             | Packages                             | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

#### F.4 PIC16C5X Family of Devices

|             |                                      | PIC16C52            | PIC16C54                            | PIC16C54A                           | PIC16CR54A                          | PIC16C55                     | PIC16C56                            |

|-------------|--------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 4                   | 20                                  | 20                                  | 20                                  | 20                           | 20                                  |

|             | EPROM Program Memory (x12 words)     | 384                 | 512                                 | 512                                 | _                                   | 512                          | 1K                                  |

| Memory      | ROM Program Memory<br>(x12 words)    | _                   | _                                   | _                                   | 512                                 | _                            | _                                   |

|             | RAM Data Memory (bytes)              | 25                  | 25                                  | 25                                  | 25                                  | 24                           | 25                                  |

| Peripherals | Timer Module(s)                      | TMR0                | TMR0                                | TMR0                                | TMR0                                | TMR0                         | TMR0                                |

|             | I/O Pins                             | 12                  | 12                                  | 12                                  | 12                                  | 20                           | 12                                  |

|             | Voltage Range (Volts)                | 2.5-6.25            | 2.5-6.25                            | 2.0-6.25                            | 2.0-6.25                            | 2.5-6.25                     | 2.5-6.25                            |

| Features    | Number of Instructions               | 33                  | 33                                  | 33                                  | 33                                  | 33                           | 33                                  |

| reatures    | Packages                             | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC,<br>SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

|             |                                      | PIC16C57                     | PIC16CR57B                | PIC16C58A                        | PIC16CR58A                       |

|-------------|--------------------------------------|------------------------------|---------------------------|----------------------------------|----------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                           | 20                        | 20                               | 20                               |

|             | EPROM Program Memory (x12 words)     | 2K                           | _                         | 2K                               | _                                |

| Memory      | ROM Program Memory (x12 words)       | _                            | 2K                        | _                                | 2K                               |

|             | RAM Data Memory (bytes)              | 72                           | 72                        | 73                               | 73                               |

| Peripherals | Timer Module(s)                      | TMR0                         | TMR0                      | TMR0                             | TMR0                             |

|             | I/O Pins                             | 20                           | 20                        | 12                               | 12                               |

|             | Voltage Range (Volts)                | 2.5-6.25                     | 2.5-6.25                  | 2.0-6.25                         | 2.5-6.25                         |

| Features    | Number of Instructions               | 33                           | 33                        | 33                               | 33                               |

|             | Packages                             | 28-pin DIP,<br>SOIC,<br>SSOP | 28-pin DIP, SOIC,<br>SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer (except PIC16C52), selectable code protect and high I/O current capability.

#### SPI Master/Slave Connection...... 87 INDEX Numerics Timer0 ...... 65 9-bit Receive Enable bit, RX9......106 Timer1 ...... 72 9th bit of received data, RX9D.......106 Timer2 ...... 75 USART Receive ...... 114 USART Transmit ...... 112 Α Watchdog Timer ...... 140 Absolute Maximum Ratings.......163, 183, 199, 215, 231, 247, 263 BOR ...... 47. 131 ACK.......96, 100, 101 BRGH ...... 105 ALU ......9 AN552 (Implementing Wake-up on Key Stroke) ....... 53 Buffer Full Status bit, BF...... 84, 89 AN556 (Implementing a Table Read) ......48 AN594 (Using the CCP Modules) ......77 C Capture Baud Rate Formula......107 Block Diagram ...... 78 **Baud Rates** Pin Configuration ...... 78 Asynchronous Mode ......108 Prescaler ...... 79 Error, Calculating ...... 107 RX Pin Sampling, Timing Diagrams......110, 111 Capture Interrupt ...... 78 Sampling......110 Capture/Compare/PWM (CCP) Synchronous Mode......108 Capture Mode...... 78 Capture Mode Block Diagram ...... 78 **Block Diagrams** CCP1......77 Capture Mode Operation ......78 CCP2......77 Compare Mode Block Diagram ...... 79 Overview...... 63 External Parallel Resonant Crystal Circuit .................. 127 PWM Block Diagram ...... 80 External Series Resonant Crystal Circuit.......127 I<sup>2</sup>C Mode......99 PWM, Example Frequencies/Resolutions ...... 81 In-circuit Programming Connections......142 Parallel Slave Port, PORTD-PORTE ......61 PIC16C62 11 PIC16C63 ...... 12 CCP1 Interrupt Flag bit, CCP1IF......41 PIC16C64 ......11 CCP1 Mode Select bits......78 PIC16C64A ......11 CCP1CON......24, 26, 28, 30, 32, 34 CCP1IE 38 CCP1IF.......41 PIC16C66 13 CCP1M3:CCM1M0......78 CCP1X:CCP1Y.......78 PIC16CR62......11 CCP2 Interrupt Enable bit, CCP2IE......45 PIC16CR63......12 CCP2 Interrupt Flag bit, CCP2IF.......46 PIC16CR64......11 CCP2 Mode Select bits......78 PIC16CR65......12 CCP2CON ...... 24, 26, 28, 30, 32, 34 CCP2IE......45 PORTD (I/O Mode) .......57 PORTE (I/O Mode) ......58 PWM ...... 80 CCP2X:CCP2Y......78 RA3:RA0 pins ......51 CCPR1H......24, 26, 28, 30, 32, 34 RA4/T0CKI pin ......51 CCPR1L ...... 24, 26, 28, 30, 32, 34 RA5 pin ......51 CCPR2L ...... 24, 26, 28, 30, 32, 34 CKE ...... 89 RC Oscillator Mode......127

CKP ...... 85, 90

| LIST OF       | EQUATION AND EXAMPLES                                                 | Figure 4-15:  | PIE1 Register for PIC16C65/65A/R65/67 (Address 8Ch) | 40   |

|---------------|-----------------------------------------------------------------------|---------------|-----------------------------------------------------|------|

| Example 3-1:  | Instruction Pipeline Flow18                                           | Figure 4-16:  | PIR1 Register for PIC16C62/62A/R62                  | . 40 |

|               | Call of a Subroutine in Page 1                                        |               | (Address 0Ch)                                       | . 41 |

|               | from Page 049                                                         | Figure 4-17:  | PIR1 Register for PIC16C63/R63/66                   |      |

| Example 4-2:  | Indirect Addressing49                                                 |               | Address 0Ch)                                        | . 42 |

| Example 5-1:  | Initializing PORTA51                                                  | Figure 4-18:  | PIR1 Register for PIC16C64/64A/R64                  |      |

| Example 5-2:  | Initializing PORTB53                                                  |               | (Address 0Ch)                                       | . 43 |

| Example 5-3:  | Initializing PORTC55                                                  | Figure 4-19:  | PIR1 Register for PIC16C65/65A/R65/67               |      |

| Example 5-4:  | Read-Modify-Write Instructions on an                                  |               | (Address 0Ch)                                       |      |

|               | I/O Port60                                                            | Figure 4-20:  | PIE2 Register (Address 8Dh)                         |      |

|               | Changing Prescaler (Timer0→WDT)69                                     | Figure 4-21:  | PIR2 Register (Address 0Dh)                         | . 46 |

|               | Changing Prescaler (WDT→Timer0)69                                     | Figure 4-22:  | PCON Register for PIC16C62/64/65                    |      |

| Example 8-1:  | Reading a 16-bit                                                      | Figure 4 00   | (Address 8Eh)                                       | . 47 |

| F             | Free-running Timer                                                    | Figure 4-23:  | PCON Register for PIC16C62A/R62/63/                 |      |

| Example 10-1: | Changing Between                                                      |               | R63/64A/R64/65A/R65/66/67<br>(Address 8Eh)          | 17   |

| Evample 10 2  | Capture Prescalers79  PWM Period and Duty                             | Figure 4-24:  | Loading of PC in Different Situations               |      |

| Example 10-2. | Cycle Calculation81                                                   | Figure 4-25:  | Direct/Indirect Addressing                          |      |

| Evample 11-1: | Loading the SSPBUF                                                    | Figure 5-1:   | Block Diagram of the                                | . 40 |

| Lxample 11-1. | (SSPSR) Register86                                                    | rigaro o r.   | RA3:RA0 Pins and the RA5 Pin                        | 51   |

| Example 11-2  | Loading the SSPBUF                                                    | Figure 5-2:   | Block Diagram of the RA4/T0CKI Pin                  |      |

| Example 11 E. | (SSPSR) Register (PIC16C66/67)91                                      | Figure 5-3:   | Block Diagram of the                                |      |

| Example 12-1: | Calculating Baud Rate Error107                                        | 3             | RB7:RB4 Pins for PIC16C61/62/64/65                  | . 53 |

|               | Saving Status and W                                                   | Figure 5-4:   | Block Diagram of the                                |      |

|               | Registers in RAM139                                                   | · ·           | RB7:RB4 Pins for PIC16C62A/63/R63/                  |      |

| Example 13-2: | Saving Status, W, and                                                 |               | 64A/65A/R65/66/67                                   | . 54 |

| •             | PCLATH Registers in RAM                                               | Figure 5-5:   | Block Diagram of the                                |      |

|               | (All other PIC16C6X devices)139                                       |               | RB3:RB0 Pins                                        | . 54 |

|               |                                                                       | Figure 5-6:   | PORTC Block Diagram                                 | . 55 |

|               |                                                                       | Figure 5-7:   | PORTD Block Diagram                                 |      |

| LIST OF       | FIGURES                                                               |               | (In I/O Port Mode)                                  | . 57 |

|               |                                                                       | Figure 5-8:   | PORTE Block Diagram                                 |      |

| Figure 3-1:   | PIC16C61 Block Diagram10                                              | F: 50         | (In I/O Port Mode)                                  |      |

| Figure 3-2:   | PIC16C62/62A/R62/64/64A/R64                                           | Figure 5-9:   | TRISE Register (Address 89h)                        |      |

| Fig 0. 0.     | Block Diagram11                                                       | Figure 5-10:  | Successive I/O Operation                            | . 60 |

| Figure 3-3:   | PIC16C63/R63/65/65A/R65                                               | Figure 5-11:  | PORTD and PORTE as a Parallel                       | 61   |

| Figure 3-4:   | Block Diagram                                                         | Figure 5-12:  | Slave Port Parallel Slave Port Write Waveforms      |      |

| Figure 3-4:   | Clock/Instruction Cycle18                                             | Figure 5-12:  | Parallel Slave Port Read Waveforms                  |      |

| Figure 4-1:   | PIC16C61 Program Memory Map                                           | Figure 7-1:   | Timer0 Block Diagram                                |      |

| 94.0          | and Stack19                                                           | Figure 7-2:   | Timer0 Timing: Internal Clock/No                    |      |

| Figure 4-2:   | PIC16C62/62A/R62/64/64A/                                              | ga. 0 /       | Prescaler                                           | . 65 |

|               | R64 Program Memory Map and Stack 19                                   | Figure 7-3:   | Timer0 Timing: Internal                             |      |

| Figure 4-3:   | PIC16C63/R63/65/65A/R65 Program                                       | 3             | Clock/Prescale 1:2                                  | . 66 |

| •             | Memory Map and Stack19                                                | Figure 7-4:   | TMR0 Interrupt Timing                               |      |

| Figure 4-4:   | PIC16C66/67 Program Memory                                            | Figure 7-5:   | Timer0 Timing With External Clock                   | . 67 |

|               | Map and Stack20                                                       | Figure 7-6:   | Block Diagram of the Timer0/WDT                     |      |

| Figure 4-5:   | PIC16C61 Register File Map20                                          |               | Prescaler                                           | . 68 |

| Figure 4-6:   | PIC16C62/62A/R62/64/64A/                                              | Figure 8-1:   | T1CON: Timer1 Control Register                      |      |

|               | R64 Register File Map21                                               |               | (Address 10h)                                       |      |

| Figure 4-7:   | PIC16C63/R63/65/65A/R65                                               | Figure 8-2:   | Timer1 Block Diagram                                |      |

|               | Register File Map21                                                   | Figure 9-1:   | Timer2 Block Diagram                                | . 75 |

| Figure 4-8:   | PIC16C66/67 Data Memory Map22                                         | Figure 9-2:   | T2CON: Timer2 Control Register                      |      |

| Figure 4-9:   | STATUS Register                                                       | E' 10.1       | (Address 12h)                                       | . /5 |

| E' 4.40       | (Address 03h, 83h, 103h, 183h)                                        | Figure 10-1:  | CCP1CON Register (Address 17h) /                    | 70   |

| Figure 4-10:  | OPTION Register                                                       | Fig 10.0.     | CCP2CON Register (Address 1Dh)                      | . /8 |

| Ciaura 4 11.  | (Address 81h, 181h)                                                   | Figure 10-2:  | Capture Mode Operation                              | 70   |

| Figure 4-11:  | INTCON Register (Address ORb. 8Rb. 10Rb.18Rb) 37                      | Figure 10 2   | Block Diagram                                       | . 78 |

| Figure 4-12:  | (Address 0Bh, 8Bh, 10Bh 18Bh)37<br>PIE1 Register for PIC16C62/62A/R62 | Figure 10-3:  | Compare Mode Operation Block Diagram                | 70   |

| 1 19u16 4-12. | (Address 8Ch)38                                                       | Figure 10-4:  | Simplified PWM Block Diagram                        |      |

| Figure 4-13:  | PIE1 Register for PIC16C63/R63/66                                     | Figure 10-4.  | PWM Output                                          |      |

| guic 4-10.    | (Address 8Ch)39                                                       | Figure 10-5.  | SSPSTAT: Sync Serial Port Status                    | . 50 |

| Figure 4-14:  | PIE1 Register for PIC16C64/64A/R64                                    | riguio i i i. | Register (Address 94h)                              | . 84 |

| J             | (Address 8Ch)39                                                       |               | - 3 (                                               |      |

| Table 23-5:  | Timer0 and Timer1 External                  |       |

|--------------|---------------------------------------------|-------|

|              | Clock Requirements                          | 272   |

| Table 23-6:  | Capture/Compare/PWM                         |       |

|              | Requirements (CCP1 and CCP2)                | 273   |

| Table 23-7:  | Parallel Slave Port Requirements (PIC16 274 | 6C67) |

| Table 23-8:  | SPI Mode Requirements                       | 277   |

| Table 23-9:  | I <sup>2</sup> C Bus Start/Stop Bits        |       |

|              | Requirements                                | 278   |

| Table 23-10: | I <sup>2</sup> C Bus Data Requirements      | 279   |

| Table 23-11: | USART Synchronous Transmission              |       |

|              | Requirements                                | 280   |

| Table 23-12: | USART Synchronous Receive                   |       |

|              | Requirements                                | 280   |

| Table 24-1:  | RC Oscillator Frequencies                   | 287   |

| Table 24-2:  | Capacitor Selection for Crystal             |       |

|              | Oscillators                                 | 288   |

| Table E-1:   | Pin Compatible Devices                      | 315   |

|              |                                             |       |