#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

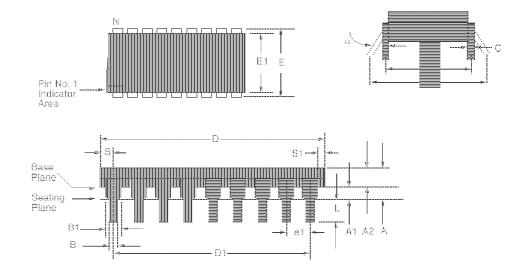

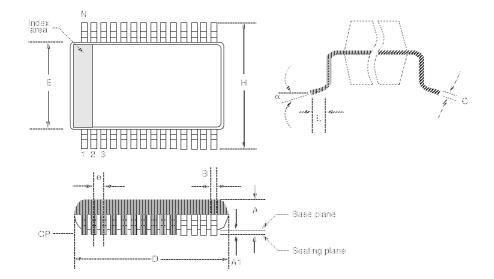

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-04i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | DIP<br>Pin#     | SOIC<br>Pin#      | Pin Type | Buffer<br>Type                   | Description                                                                                                                                                                                                   |

|-------------------|-----------------|-------------------|----------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 16              | 16                | I        | ST/CMOS(1)                       | Oscillator crystal input/external clock source input.                                                                                                                                                         |

| OSC2/CLKOUT       | 15              | 15                | 0        | _                                | Oscillator crystal output. Connects to crystal or resonator in crystal<br>oscillator mode. In RC mode, the pin outputs CLKOUT which has<br>1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP          | 4               | 4                 | I/P      | ST                               | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                         |

|                   |                 |                   |          |                                  | PORTA is a bi-directional I/O port.                                                                                                                                                                           |

| RA0               | 17              | 17                | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA1               | 18              | 18                | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA2               | 1               | 1                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA3               | 2               | 2                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA4/T0CKI         | 3               | 3                 | I/O      | ST                               | RA4 can also be the clock input to the Timer0 timer/counter.<br>Output is open drain type.                                                                                                                    |

|                   |                 |                   |          |                                  | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT           | 6               | 6                 | I/O      | TTL/ST <sup>(2)</sup>            | RB0 can also be the external interrupt pin.                                                                                                                                                                   |

| RB1               | 7               | 7                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB2               | 8               | 8                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB3               | 9               | 9                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB4               | 10              | 10                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                      |

| RB5               | 11              | 11                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                      |

| RB6               | 12              | 12                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming clock.                                                                                                                                                            |

| RB7               | 13              | 13                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming data.                                                                                                                                                             |

| Vss               | 5               | 5                 | Р        | -                                | Ground reference for logic and I/O pins.                                                                                                                                                                      |

| Vdd               | 14              | 14                | Р        | _                                | Positive supply for logic and I/O pins.                                                                                                                                                                       |

| Legend: I = input | 0 = ou<br>— = N | utput<br>lot used |          | ) = input/outpu<br>L = TTL input |                                                                                                                                                                                                               |

#### **PIC16C61 PINOUT DESCRIPTION TABLE 3-1:**

Note

1:

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

2:

This buffer is a Schmitt Trigger input when configured as the external interrupt.

Configured as the external interrup

3: This buffer is a Schmitt Trigger input when used in serial programming mode.

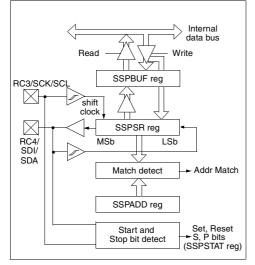

## 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in  $I^2C$  mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

#### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

Г

## FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                | R/W-0                       | R/W-0          | U-0         | R-0          | R-0          | R-x         |                    |                                                                                                                               |

|--------|----------------------------------------------------------------------|-----------------------------|----------------|-------------|--------------|--------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                  | SREN                        | CREN           | —           | FERR         | OERR         | RX9D        | R                  | = Readable bit                                                                                                                |

| bit7   |                                                                      |                             |                |             |              |              | bitO        | W<br>U<br>- n<br>x | <ul> <li>Writable bit</li> <li>Unimplemented</li> <li>bit, read as '0'</li> <li>Value at POR rese</li> <li>unknown</li> </ul> |

| bit 7: | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p             | s RC7/RX/l                  | DT and RC<br>d | 6/TX/CK     | pins as seri | al port pins | s when bits | TRIS               | C<7:6> are set)                                                                                                               |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion          |             |              |              |             |                    |                                                                                                                               |

| bit 5: | SREN: Sing                                                           | gle Receiv                  | e Enable bi    | t           |              |              |             |                    |                                                                                                                               |

|        | Asynchrone<br>Don't care                                             | ous mode                    |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{Synchronof}{1 = Enables}$ $0 = Disables$ This bit is c        | s single ree<br>s single re | ceive<br>ceive | is comple   | ete.         |              |             |                    |                                                                                                                               |

|        | Synchrono<br>Unused in t                                             |                             | <u>slave</u>   |             |              |              |             |                    |                                                                                                                               |

| bit 4: | CREN: Cor                                                            | ntinuous R                  | eceive Ena     | ble bit     |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Asynchrono}}{1 = \text{Enable}}$ $0 = \text{Disable}$   | s continuo                  |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Synchronor}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                | until enabl | le bit CREN  | l is cleared | (CREN ov    | erride             | s SREN)                                                                                                                       |

| bit 3: | Unimplem                                                             | ented: Rea                  | ad as '0'      |             |              |              |             |                    |                                                                                                                               |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                | ed by rea   | ding RCRE    | G register   | and receive | e next             | valid byte)                                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                | d by clea   | ring bit CRI | EN)          |             |                    |                                                                                                                               |

| bit 0: | <b>RX9D</b> : 9th                                                    |                             |                |             |              |              |             |                    |                                                                                                                               |

#### 13.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First a PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode, with the PWRT disabled, there will be no time-out at all. Figure 13-11, Figure 13-12, and Figure 13-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if the  $\overline{\text{MCLR}}/\text{VPP}$  pin is kept low long enough, the time-outs will expire. Then bringing the  $\overline{\text{MCLR}}/\text{VPP}$  pin high will begin execution immediately (Figure 13-14). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 13-10 and Table 13-11 show the reset conditions for some special function registers, while Table 13-12 shows the reset conditions for all the registers.

## 13.4.6 POWER CONTROL/STATUS REGISTER (PCON)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C62/64/65.

Bit0 is BOR (Brown-out Reset Status bit). BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR cleared, indicating that a brown-out has occurred. The BOR status bit is a "Don't Care" and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 13-5: TIME-OUT IN VARIOUS SITUATIONS, PIC16C61/62/64/65

| Oscillator Configuration | Power            | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

#### TABLE 13-6: TIME-OUT IN VARIOUS SITUATIONS, PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

| Oscillator Configuration | Power            | ·up       | Brown-out        | Wake up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Conliguration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024 Tosc    |  |

| RC                       | 72 ms            | _         | 72 ms            | —            |  |

#### TABLE 13-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C61

| TO | PD |                                                         |

|----|----|---------------------------------------------------------|

| 1  | 1  | Power-on Reset or MCLR reset during normal operation    |

| 0  | 1  | WDT Reset                                               |

| 0  | 0  | WDT Wake-up                                             |

| 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 13-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C62/64/65

| POR | то | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |

| 0   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |

| 1   | 0  | 1  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR reset during normal operation                      |

| 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

Legend: x = unknown, u = unchanged

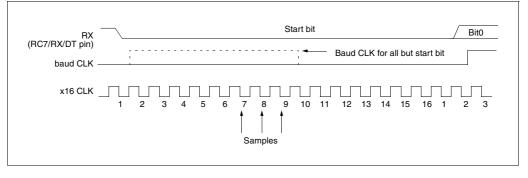

#### 13.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if edge select bit INTEDG (OPTION<6>) is set, or falling, if bit INTEDG is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP, if enable bit INTE was set prior to going into SLEEP. The status of global enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 13.8 for details on SLEEP mode.

#### 13.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0).

#### 13.5.3 PORTB INTERRUPT ON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 5.2).

Note: For the PIC16C61/62/64/65, if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then flag bit RBIF may not get set.

#### FIGURE 13-19: INT PIN INTERRUPT TIMING

| RLF               | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | Decode Read register 'f' Vite to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | Decode Read register data Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example           | RRF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -           After Instruction         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td></td> <td>Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -&lt;</td> |                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -< |

| SUBWF             | Subtract                                                        | W from f                     |                                   |                      |

|-------------------|-----------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|

| Syntax:           | [ label ]                                                       | SUBWF                        | f,d                               |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ | ,                            |                                   |                      |

| Operation:        | (f) - (W) $\rightarrow$                                         | (destina                     | tion)                             |                      |

| Status Affected:  | C, DC, Z                                                        |                              |                                   |                      |

| Encoding:         | 00                                                              | 0010                         | dfff                              | ffff                 |

| Description:      | Subtract (2'<br>ister from re<br>stored in the<br>result is sto | egister 'f'. l<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the        |

| Words:            | 1                                                               |                              |                                   |                      |

| Cycles:           | 1                                                               |                              |                                   |                      |

| Q Cycle Activity: | Q1                                                              | Q2                           | Q3                                | Q4                   |

|                   | Decode                                                          | Read<br>register 'f'         | Process<br>data                   | Write to destination |

| Example 1:        | SUBWF                                                           | reg1,1                       |                                   |                      |

|                   | Before Ins                                                      | truction                     |                                   |                      |

|                   | REG1                                                            | =                            | 3                                 |                      |

|                   | W<br>C                                                          | =                            | 2<br>?                            |                      |

|                   | Z                                                               | =                            | ?                                 |                      |

|                   | After Instru                                                    | uction                       |                                   |                      |

|                   | REG1                                                            | =                            | 1                                 |                      |

|                   | W<br>C                                                          | =                            | 2<br>1; result is                 | nositive             |

|                   | z                                                               | =                            | 0                                 | poolavo              |

| Example 2:        | Before Ins                                                      | truction                     |                                   |                      |

|                   | REG1                                                            | =                            | 2                                 |                      |

|                   | W<br>C                                                          | =                            | 2<br>?                            |                      |

|                   | Z                                                               | =                            | ?                                 |                      |

|                   | After Instru                                                    | uction                       |                                   |                      |

|                   | REG1                                                            | =                            | 0                                 |                      |

|                   | W<br>C                                                          | =                            | 2<br>1; result is                 | 7010                 |

|                   | z                                                               | =                            | 1                                 | 2010                 |

| Example 3:        | Before Ins                                                      | truction                     |                                   |                      |

|                   | REG1                                                            | =                            | 1                                 |                      |

|                   | W<br>C                                                          | =                            | 2<br>?                            |                      |

|                   | z                                                               | =                            | ?                                 |                      |

|                   | After Instru                                                    | uction                       |                                   |                      |

|                   | REG1                                                            | =                            | 0xFF                              |                      |

|                   | W<br>C                                                          | =                            | 2<br>0; result is                 | negative             |

|                   | z                                                               | =                            | 0                                 | guivo                |

|                   |                                                                 |                              |                                   |                      |

| SWAPF             | Swap Ni                           | bbles in                                                | f                             |                      |

|-------------------|-----------------------------------|---------------------------------------------------------|-------------------------------|----------------------|

| Syntax:           | [label]                           | SWAPF 1                                                 | ,d                            |                      |

| Operands:         | $0 \le f \le 12$<br>$d \in [0,1]$ | 27                                                      |                               |                      |

| Operation:        | · · ·                             | ightarrow (destin $ ightarrow$ (destin                  |                               |                      |

| Status Affected:  | None                              |                                                         |                               |                      |

| Encoding:         | 0 0                               | 1110                                                    | dfff                          | ffff                 |

| Description:      | 'f' are excl<br>placed in '       | r and lower<br>nanged. If<br>W register.<br>in register | 'd' is 0 the<br>If 'd' is 1 t | e result is          |