#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-10i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7              | Bit 6                           | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|---------------------------------|----------------|----------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               | 1       | 1                  | 1                               | I              |                | I            | 1               | 1             | 1         | 1                        | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location                   | uses conter    | its of FSR to  | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | dule's registe                  | r              |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                   | Least Signif   | icant Byte     |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>              | RP0            | TO             | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac                     | Idress pointe  | er             | 1            |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | —                  | —                               | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe                    | n written: PC  | ORTB pins wh   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe                    | n written: PC  | ORTC pins wi   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | _       | Unimpleme          | nted                            |                |                |              |                 |               |           | —                        | _                                              |

| 09h                  | —       | Unimpleme          | nted                            |                |                |              |                 |               |           | —                        | —                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                               | _              | Write Buffer   | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                            | TOIE           | INTE           | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | (5)                | (5)                             | RCIF           | TXIF           | SSPIF        | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | _                  | _                               | _              | _              | _            | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the I                 | _east Signific | ant Byte of t  | ne 16-bit TM | R1 register     |               | 1         | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the I                 | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                  | —                               | T1CKPS1        | T1CKPS0        | T1OSCEN      | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | dule's registe                  | r              |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                  | TOUTPS3                         | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | us Serial Por                   | t Receive Bu   | ffer/Transmit  | Register     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV                           | SSPEN          | CKP            | SSPM3        | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM                       | 1 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM                       | 1 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                  | _                               | CCP1X          | CCP1Y          | CCP1M3       | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                             | SREN           | CREN           | —            | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra          | nsmit Data F                    | legister       |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re           | USART Receive Data Register 000 |                |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM                       | 2 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM                       | 2 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                               | CCP2X          | CCP2Y          | CCP2M3       | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted                            |                |                |              |                 |               |           | _                        | _                                              |

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

5: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C63/R63, always maintain these bits clear.

| TABLE                | 4-6:    | SPECIA               |                              | TION RE                   | GISTERS        | S FOR T      | HE PIC1          | 6C66/67        | (Cont.'c  | I)                       |                                                |

|----------------------|---------|----------------------|------------------------------|---------------------------|----------------|--------------|------------------|----------------|-----------|--------------------------|------------------------------------------------|

| Address              | Name    | Bit 7                | Bit 6                        | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1          | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

| Bank 1               |         |                      |                              |                           |                |              |                  |                |           |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing           | this location                | uses conte                | nts of FSR to  | address dat  | a memory (n      | ot a physical  | register) | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU                 | INTEDG                       | TOCS                      | T0SE           | PSA          | PS2              | PS1            | PS0       | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)                | Least Sig                 | nificant Byte  |              |                  |                |           | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP                  | RP1                          | RP0                       | TO             | PD           | Z                | DC             | С         | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data        | a memory ad                  | dress point               | er             |              |                  |                | 1         | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                    | _                            | PORTA Da                  | ta Direction R | legister     |                  |                |           | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat            | ta Direction I               | Register                  |                |              |                  |                |           | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Dat            | ta Direction                 | Register                  |                |              |                  |                |           | 1111 1111                | 1111 1111                                      |

| 88h <sup>(5)</sup>   | TRISD   | PORTD Dat            | ta Direction                 | Register                  |                |              |                  |                |           | 1111 1111                | 1111 1111                                      |

| 89h <sup>(5)</sup>   | TRISE   | IBF                  | OBF                          | IBOV                      | PSPMODE        | _            | PORTE Da         | ta Direction I | Bits      | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                    | —                            | —                         | Write Buffer   | for the uppe | er 5 bits of the | e Program C    | ounter    | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE                         | TOIE                      | INTE           | RBIE         | TOIF             | INTF           | RBIF      | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | PSPIE <sup>(6)</sup> | (4)                          | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE         | TMR1IE    | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                    | _                            | _                         | _              | —            | _                | _              | CCP2IE    | 0                        | 0                                              |

| 8Eh                  | PCON    | —                    | —                            | —                         | -              | _            | _                | POR            | BOR       | dd                       | uu                                             |

| 8Fh                  | -       | Unimpleme            | nted                         |                           |                |              | •                |                |           | -                        | _                                              |

| 90h                  |         | Unimpleme            | nted                         |                           |                |              |                  |                |           | _                        | _                                              |

| 91h                  | -       | Unimpleme            | nted                         |                           |                |              |                  |                |           | -                        | —                                              |

| 92h                  | PR2     | Timer2 Peri          | od Register                  |                           |                |              |                  |                |           | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou           | us Serial Por                | t (I <sup>2</sup> C mode) | Address Reg    | gister       |                  |                |           | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | SMP                  | CKE                          | D/A                       | Р              | S            | R/W              | UA             | BF        | 0000 0000                | 0000 0000                                      |

| 95h                  | -       | Unimpleme            | nted                         |                           |                |              |                  |                |           | _                        | —                                              |

| 96h                  | -       | Unimpleme            | nted                         |                           |                |              |                  |                |           | _                        | —                                              |

| 97h                  | -       | Unimpleme            | nted                         |                           |                |              |                  |                |           | _                        | —                                              |

| 98h                  | TXSTA   | CSRC                 | TX9                          | TXEN                      | SYNC           | —            | BRGH             | TRMT           | TX9D      | 0000 -010                | 0000 -010                                      |

| 99h                  | SPBRG   | Baud Rate            | Baud Rate Generator Register |                           |                |              |                  |                |           |                          | 0000 0000                                      |

| 9Ah                  | -       | Unimpleme            | Unimplemented                |                           |                |              |                  |                |           | _                        | _                                              |

| 9Bh                  | _       | Unimpleme            | Unimplemented                |                           |                |              |                  |                |           |                          | —                                              |

| 9Ch                  | _       | Unimpleme            | nted                         |                           |                |              |                  |                |           | —                        | _                                              |

| 9Dh                  | —       | Unimpleme            | Unimplemented                |                           |                |              |                  |                |           |                          | —                                              |

| 9Eh                  | _       | Unimpleme            | nimplemented — —             |                           |                |              |                  |                |           |                          |                                                |

| 9Fh                  | -       | Unimpleme            | nted                         |                           |                |              |                  |                |           | -                        | -                                              |

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

## TABLE 5-6: PORTC FUNCTIONS FOR PIC16C62A/R62/64A/R64

| Name            | Bit# | Buffer Type | Function                                                                              |

|-----------------|------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input               |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                      |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture input/Compare output/PWM1 output                     |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 |             | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                          |

| RC6             | bit6 | ST          | Input/output port pin                                                                 |

| RC7             | bit7 | ST          | Input/output port pin                                                                 |

Legend: ST = Schmitt Trigger input

### TABLE 5-7: PORTC FUNCTIONS FOR PIC16C63/R63/65/65A/R65/66/67

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1 clock input                        |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                    |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit, or USART Syn-<br>chronous Clock          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive, or USART Syn-<br>chronous Data            |

Legend: ST = Schmitt Trigger input

### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|---------------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6                                         | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC D | ORTC Data Direction Register 1111 1111 1111 |       |       |       |       |       |       | 1111 1111                |                           |

Legend: x = unknown, u = unchanged.

## 6.0 OVERVIEW OF TIMER MODULES

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

All PIC16C6X devices have three timer modules except for the PIC16C61, which has one timer module. Each module can generate an interrupt to indicate that an event has occurred (i.e., timer overflow). Each of these modules are detailed in the following sections. The timer modules are:

- Timer0 module (Section 7.0)

- Timer1 module (Section 8.0)

- Timer2 module (Section 9.0)

#### 6.1 <u>Timer0 Overview</u>

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

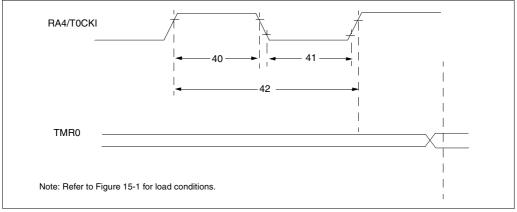

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. TMR0 can increment at the following rates: 1:1 when the prescaler is assigned to Watchdog Timer, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 6.2 <u>Timer1 Overview</u>

| Ap | plicable Devices |

|----|------------------|

|    |                  |

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

TImer1 also has a prescaler option which allows TMR1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. TMR1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit capture or 16-bit compare and must be synchronized to the device.

#### 6.3 <u>Timer2 Overview</u>

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a programmable prescaler and a programmable postscaler, as well as an 8-bit Period Register (PR2). Timer2 can be used with the CCP module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, and 1:16.

The postscaler allows TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

#### 6.4 <u>CCP Overview</u>

| e Devices |

|-----------|

|           |

|           |

|           |

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The CCP module(s) can operate in one of three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs, an interrupt can be generated and the output pin CCPx can be forced to a given state (High or Low) and Timer1 can be reset. This depends on control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

## 8.0 TIMER1 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

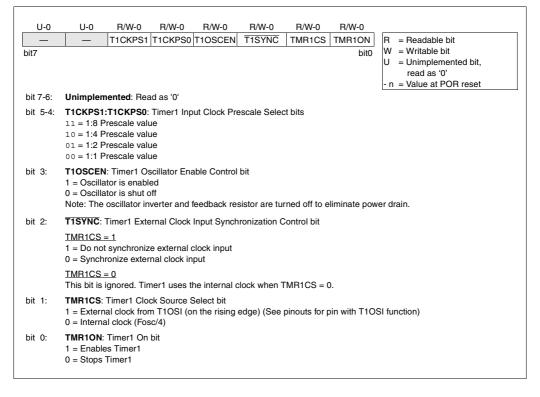

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

## 14.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 14-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 14-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 14-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 14-2 lists the instructions recognized by the MPASM assembler.

Figure 14-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXX products, do not use the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

#### FIGURE 14-1: GENERAL FORMAT FOR INSTRUCTIONS

| BTFSS             | Bit Test f                                                                                                                                                  | , Skip if S               | Set                       |                  | _         | CALL                    | Call Sub                               | routine                                              |                                        |                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------------------|-----------|-------------------------|----------------------------------------|------------------------------------------------------|----------------------------------------|-------------------------------|

| Syntax:           | [ <i>label</i> ] BTFSS f,b                                                                                                                                  |                           |                           |                  | Syntax:   | [ <i>label</i> ] CALL k |                                        |                                                      |                                        |                               |

| Operands:         | $0 \le f \le 127$                                                                                                                                           |                           |                           |                  | Operands: | 0 ≤ k ≤ 2047            |                                        |                                                      |                                        |                               |

| _                 | 0 ≤ b < 7                                                                                                                                                   |                           |                           |                  |           | Operation:              | (PC)+ 1-                               | ,                                                    |                                        |                               |

| Operation:        | skip if (f <l< td=""><td>b&gt;) = 1</td><td></td><td></td><td></td><td></td><td><math>k \rightarrow PC &lt;</math></td><td>,</td><td></td><td>44.</td></l<> | b>) = 1                   |                           |                  |           |                         | $k \rightarrow PC <$                   | ,                                                    |                                        | 44.                           |

| Status Affected:  | None                                                                                                                                                        |                           | 1                         |                  | 7         | o                       | (PCLATH                                | 1<4:3>) -                                            | > PG<12:                               | 11>                           |

| Encoding:         | 01                                                                                                                                                          | 11bb                      | bfff                      | ffff             |           | Status Affected:        | None                                   | 1                                                    |                                        | ·                             |

| Description:      | If bit 'b' in r<br>instruction                                                                                                                              |                           |                           | ne next          |           | Encoding:               | 10                                     | 0kkk                                                 | kkkk                                   | kkkk                          |

|                   | If bit 'b' is '<br>discarded<br>instead, m                                                                                                                  | 1', then the<br>and a NOF | e next instr<br>s execute | əd               |           | Description:            | (PC+1) is<br>eleven bit<br>into PC bit | putine. Firs<br>pushed on<br>immediate<br>ts <10:0>. | to the stac<br>address is<br>The upper | k. The<br>s loaded<br>bits of |

| Words:            | 1                                                                                                                                                           |                           |                           |                  |           |                         | the PC are<br>is a two cy              |                                                      |                                        | H. CALL                       |

| Cycles:           | 1(2)                                                                                                                                                        |                           |                           |                  |           | Words:                  | 1                                      |                                                      |                                        |                               |

| Q Cycle Activity: | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | -         | Cycles:                 | 2                                      |                                                      |                                        |                               |

|                   | Decode                                                                                                                                                      | Read<br>register 'f'      | Process<br>data           | No-<br>Operation |           | Q Cycle Activity:       | Q1                                     | Q2                                                   | Q3                                     | Q4                            |

| If Skip:          | (2nd Cyc                                                                                                                                                    | le)                       |                           |                  |           | 1st Cycle               | Decode                                 | Read<br>literal 'k',                                 | Process<br>data                        | Write to<br>PC                |

| ·                 | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | 7         |                         |                                        | Push PC<br>to Stack                                  | uulu                                   | 10                            |

|                   | No-<br>Operation                                                                                                                                            | No-<br>Operation          | No-<br>Operation          | No-<br>Operation |           | 2nd Cycle               | No-<br>Operation                       | No-<br>Operation                                     | No-<br>Operation                       | No-<br>Operation              |

| Example           | HERE<br>FALSE                                                                                                                                               | BTFSC<br>GOTO             | FLAG,1<br>PROCESS         | CODE             |           | Example                 | HERE                                   | CALL                                                 | THERE                                  |                               |

|                   | TRUE                                                                                                                                                        | •                         |                           |                  |           |                         |                                        | PC = A                                               | ddress HE                              | RE                            |

|                   |                                                                                                                                                             | •                         |                           |                  |           |                         | After Inst                             | truction<br>PC = A                                   | ddroce TTU                             | סמס                           |

|                   | Before In:                                                                                                                                                  |                           | address I                 | TEDE             |           |                         |                                        | TOS = A                                              |                                        |                               |

|                   | After Inst                                                                                                                                                  |                           | address r                 | IERE             |           |                         |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             | f FLAG<1:                 | - /                       |                  |           |                         |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             | PC =<br>if FLAG<1;        | address Fi                | ALSE             |           |                         |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             |                           | > = 1,<br>address TI      | RUE              |           |                         |                                        |                                                      |                                        |                               |

| [ label ]                         | IORWF                                                                                                                                             | f,d                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $0 \le f \le 12$<br>$d \in [0,1]$ | 7                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (W) .OR.                          | $(f) \rightarrow (de)$                                                                                                                            | estination                                                                                                                                                                                                                                                                                                      | )                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Z                                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 00                                | 0100                                                                                                                                              | dfff                                                                                                                                                                                                                                                                                                            | ffff                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ter 'f'. If 'd'<br>W register     | is 0 the re<br>. If 'd' is 1                                                                                                                      | sult is place                                                                                                                                                                                                                                                                                                   | ed in the                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1                                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1                                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Q1                                | Q2                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                              | Q4                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Decode                            | Read<br>register<br>'f'                                                                                                                           | Process<br>data                                                                                                                                                                                                                                                                                                 | Write to destination                                                                                                                                                                                                                                                                                                                                                                                                       |

| IORWF                             |                                                                                                                                                   | RESULT,                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                   |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   | ••                                                                                                                                                | - 0,91                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                   |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   | ••                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   | $0 \le f \le 12$ $d \in [0,1]$ (W) .OR. $Z$ $00$ Inclusive C ter 'f. If 'd' W register back in reg $1$ $1$ $Q1$ Decode IORWF Before In After Inst | $0 \le f \le 127$ $d \in [0,1]$ (W) .OR. (f) $\rightarrow$ (de<br>Z<br>00 0100<br>Inclusive OR the W<br>ter 'f'. If 'd' is 0 the re<br>W register. If 'd' is 1<br>back in register 'f'.<br>1<br>1<br>Q1 Q2<br>Decode Read<br>register<br>'f'<br>IORWF<br>Before Instruction<br>RESULT<br>W<br>After Instruction | $0 \le f \le 127$ $d \in [0,1]$ (W) .OR. (f) $\rightarrow$ (destination<br>Z $00  0100  dfff$ Inclusive OR the W register w<br>ter 'f'. If 'd' is 0 the result is plac<br>W register. If 'd' is 1 the result back in register 'f'. 1 $\frac{Q1}{Q2}  Q3$ Decode $\frac{Read}{register}  \frac{Process}{data}$ IORWF RESULT, Before Instruction<br>RESULT = 0x13<br>W = 0x91 After Instruction<br>RESULT = 0x13<br>W = 0x93 |

| MOVLW             | Move Literal to W                                                                          |

|-------------------|--------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:         | $0 \leq k \leq 255$                                                                        |

| Operation:        | $k \rightarrow (W)$                                                                        |

| Status Affected:  | None                                                                                       |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| Words:            | 1                                                                                          |

| Cycles:           | 1                                                                                          |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |

|                   | Decode Read Process Write to literal 'k' data W                                            |

| Example           | MOVLW 0x5A                                                                                 |

|                   | After Instruction<br>W = 0x5A                                                              |

-

| MOVF              | Move f                                                                                                                                                                                                                                                  |   |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|--|

| Syntax:           | [label] MOVF f,d                                                                                                                                                                                                                                        | _ |  |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                       |   |  |  |  |  |  |  |  |

| Operation:        | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                         |   |  |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                       |   |  |  |  |  |  |  |  |

| Encoding:         | 00 1000 dfff ffff                                                                                                                                                                                                                                       |   |  |  |  |  |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |   |  |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                       |   |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                       |   |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                             |   |  |  |  |  |  |  |  |

|                   | Decode Read register data Vrite to destinatio                                                                                                                                                                                                           | n |  |  |  |  |  |  |  |

| Example           | MOVF FSR, 0                                                                                                                                                                                                                                             |   |  |  |  |  |  |  |  |

|                   | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                 |   |  |  |  |  |  |  |  |

| MOVWF             | Move W            | to f                    |                  |                       |

|-------------------|-------------------|-------------------------|------------------|-----------------------|

| Syntax:           | [ label ]         | MOVW                    | F f              |                       |

| Operands:         | $0 \le f \le 12$  | .7                      |                  |                       |

| Operation:        | $(W) \to (f)$     |                         |                  |                       |

| Status Affected:  | None              |                         |                  |                       |

| Encoding:         | 00                | 0000                    | lfff             | ffff                  |

| Description:      | Move data<br>'f'. | from W r                | egister to       | register              |

| Words:            | 1                 |                         |                  |                       |

| Cycles:           | 1                 |                         |                  |                       |

| Q Cycle Activity: | Q1                | Q2                      | Q3               | Q4                    |

|                   | Decode            | Read<br>register<br>'f' | Process<br>data  | Write<br>register 'f' |

| Example           | MOVWF             | OPTIC                   | DN_REG           |                       |

|                   | Before In         | struction               |                  | _                     |

|                   |                   | W                       | = 0x+r<br>= 0x4F |                       |

|                   | After Inst        |                         |                  |                       |

|                   |                   | OPTION                  |                  |                       |

|                   |                   | W                       | = 0x4F           | -                     |

| <b>Applicable Devices</b> | 61 | 60 | 601 | Deo | 62 | Dec | 61 | 611 | DGA | 65 | 6EA | Dee | 66 | 67 |

|---------------------------|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| Applicable Devices        | 01 | 02 | 02A | n02 | 03 | n03 | 04 | 04A | n04 | 05 | 05A | H00 | 00 | 07 |

|       |                                    | Standa   | rd Operat  | ing Co |           |                                           | ss otherwise stated)                                |

|-------|------------------------------------|----------|------------|--------|-----------|-------------------------------------------|-----------------------------------------------------|

|       |                                    | Operatir | ature      | -40°C  | ≤ TA      | $\Delta \leq +125^{\circ}C$ for extended, |                                                     |

|       | RACTERISTICS                       |          |            |        | -40°C     | ≤ T⁄                                      | $\sim \pm +85^{\circ}$ C for industrial and         |

|       | ARACIERISTICS                      |          |            |        | 0°C       | ≤ TA                                      | $\Delta \leq +70^{\circ}$ C for commercial          |

|       |                                    | Operatir | ng voltage | VDD r  | ange as c | describe                                  | ed in DC spec Section 15.1 and                      |

|       |                                    | Section  | 15.2.      |        |           |                                           |                                                     |

| Param | Characteristic                     | Sym      | Min        | Typ†   | Max       | Units                                     | Conditions                                          |

| No.   |                                    |          |            |        |           |                                           |                                                     |

|       | Output High Voltage                |          |            |        |           |                                           |                                                     |

| D090  | I/O ports (Note 3)                 | Voh      | VDD-0.7    | -      | -         | v                                         | Iон = -3.0 mA,                                      |