Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-20i-so |

### 4.2.2.5 PIR1 REGISTER

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

### FIGURE 4-16: PIR1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 0Ch)

| R/   | /W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |                                       |

|------|------|-------|-----|-----|-------|--------|--------|--------|---------------------------------------|

| -    | _    | _     | _   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF | R = Readable bit                      |

| bit7 |      |       |     |     |       |        |        | bit0   | U = Unimplemented bit,<br>read as '0' |

|      |      | _     |     |     |       |        |        |        | - n = Value at POR reset              |

- bit 7-6: Reserved: Always maintain these bits clear.

- bit 5-4: Unimplemented: Read as '0'

- bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit

- 1 = The transmission/reception is complete (must be cleared in software)

- 0 = Waiting to transmit/receive

- bit 2: CCP1IF: CCP1 Interrupt Flag bit

### Capture Mode

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

### Compare Mode

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

### **PWM Mode**

Unused in this mode

- bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflow occurred (must be cleared in software)

- 0 = No TMR1 register overflow occurred

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### 4.2.2.8 PCON REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control register (PCON) contains a flag bit to allow differentiation between a Power-on Reset to an external MCLR reset or WDT reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN

bit in the Configuration word).

### FIGURE 4-22: PCON REGISTER FOR PIC16C62/64/65 (ADDRESS 8Eh)

R/W-0 R/W-q U-0 U-0 U-0 U-0 U-0 U-0 POR = Readable bit W = Writable bit bit7 hit0 = Unimplemented bit, read as '0' n = Value at POR reset = value depends on conditions Unimplemented: Read as '0' hit 7-2. bit 1: POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) bit 0: Reserved This bit should be set upon a Power-on Reset by user software and maintained as set. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.

# FIGURE 4-23: PCON REGISTER FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 (ADDRESS 8Eh)

| U-0      | U-0                                         | U-0         | U-0         | U-0        | U-0            | R/W-0       | R/W-q       |                                                                                                              |

|----------|---------------------------------------------|-------------|-------------|------------|----------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------|

| _        | _                                           | _           | _           | -          | _              | POR         | BOR         | R = Readable bit                                                                                             |

| bit7     |                                             |             |             |            |                |             | bit0        | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset q = value depends on conditions |

| bit 7-2: | Unimplem                                    | ented: Rea  | ıd as '0'   |            |                |             |             |                                                                                                              |

| bit 1:   | <b>POR</b> : Power 1 = No Power 0 = A Power | ver-on Rese | et occurred | must be se | in software    | after a Pow | er-on Reset | occurs)                                                                                                      |

| bit 0:   | BOR: Brow<br>1 = No Bro<br>0 = A Brow       | wn-out Res  | et occurred | i          | et in software | after a Bro | wn-out Rese | et occurs)                                                                                                   |

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that the PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

## EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

```

ORG 0x500

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

BCF PCLATH,4 ;Only on >4K devices

CALL SUB1_P1 ;Call subroutine in

;;page 1 (800h-FFFh)

;

ORG 0x900

SUB1_P1: ;called subroutine

;;page 1 (800h-FFFh)

;

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

```

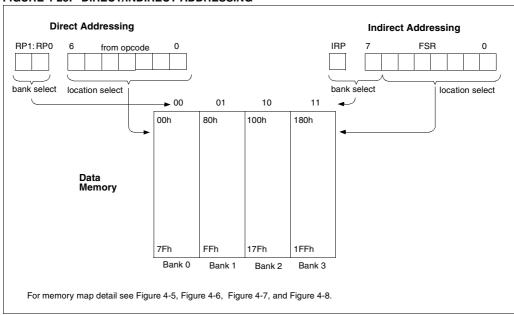

## 4.5 Indirect Addressing, INDF and FSR Registers

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-25.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

### **EXAMPLE 4-2: INDIRECT ADDRESSING**

```

movlw 0x20

;initialize pointer

movwf FSR

; to RAM

NEXT

clrf

INDF

;clear INDF register

FSR,F

incf

;inc pointer

btfss FSR,4

;all done?

;NO, clear next

goto NEXT

CONTINUE

;YES, continue

```

### FIGURE 4-25: DIRECT/INDIRECT ADDRESSING

NOTES:

### **5.0 I/O PORTS**

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Some pins for these I/O ports are multiplexed with an alternate function(s) for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

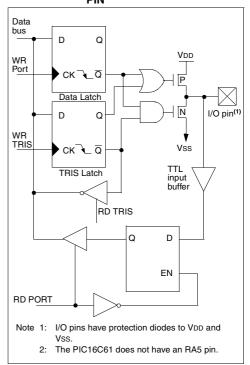

### 5.1 PORTA and TRISA Register

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

All devices have a 6-bit wide PORTA, except for the PIC16C61 which has a 5-bit wide PORTA.

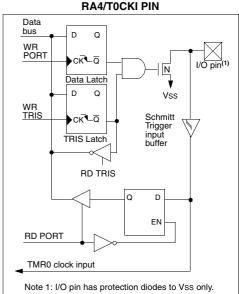

Pin RA4/T0CKI is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a bit in the TRISA register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch

Pin RA4 is multiplexed with Timer0 module clock input to become the RA4/T0CKI pin.

### **EXAMPLE 5-1: INITIALIZING PORTA**

```

BCF

STATUS, RP0

BCF

STATUS, RP1 ; PIC16C66/67 only

; Initialize PORTA by

CLRE

PORTA

: clearing output

; data latches

BSF

STATUS, RPO ; Select Bank 1

; Value used to

MOVLW

0xCF

: initialize data

: direction

MOVWF TRISA

; Set RA<3:0> as inputs

; RA<5:4> as outputs

; TRISA<7:6> are always

; read as '0'.

```

# FIGURE 5-1: BLOCK DIAGRAM OF THE RA3:RA0 PINS AND THE RA5 PIN

## FIGURE 5-2: BLOCK DIAGRAM OF THE

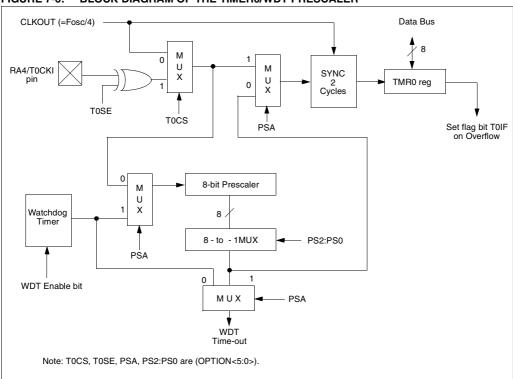

### 7.3 Prescaler

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF TMR0, MOVWF TMR0, BSF TMR0,bitx) will clear the prescaler count. When assigned to the Watchdog Timer, a CLRWDT instruction will clear the Watchdog Timer and the prescaler count. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

FIGURE 7-6: BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER

TABLE 10-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Addr                 | Name    | Bit 7                | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|----------------------|---------|----------------------|----------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                  | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000<br>000x             | 0000<br>000u                    |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup> | (3)            | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000                     | 0000                            |

| 0Dh <sup>(4)</sup>   | PIR2    | _                    | _              | CCP2IF              | 0                   | 0       |        |         |         |                          |                                 |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup> | (3)            | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000                     | 0000                            |

| 8Dh <sup>(4)</sup>   | PIE2    | _                    | _              | -                   | _                   | _       | _      | -       | CCP2IE  | 0                        | 0                               |

| 87h                  | TRISC   | PORTC I              | Data Direction | on register         |                     |         | ı      |         |         | 1111<br>1111             | 1111<br>1111                    |

| 11h                  | TMR2    | Timer2 m             | odule's reg    | ister               |                     |         |        |         |         | 0000                     | 0000                            |

| 92h                  | PR2     | Timer2 m             | odule's Per    | iod register        |                     |         |        |         |         | 1111<br>1111             | 1111<br>1111                    |

| 12h                  | T2CON   | _                    | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000<br>0000             | -000<br>0000                    |

| 15h                  | CCPR1L  | Capture/0            | Compare/P\     | WM1 (LSB)           |                     | ı       | l      |         |         | xxxx                     | uuuu<br>uuuu                    |

| 16h                  | CCPR1H  | Capture/0            | Compare/P\     | WM1 (MSB            | )                   |         |        |         |         | xxxx                     | uuuu<br>uuuu                    |

| 17h                  | CCP1CON | _                    | _              | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00<br>0000               | 00<br>0000                      |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/0            | Compare/P\     | WM2 (LSB)           | I                   | I       | I      |         |         | xxxx                     | uuuu<br>uuuu                    |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/0            | Compare/P\     | WM2 (MSB            | )                   |         |        |         |         | xxxx                     | uuuu<br>uuuu                    |

| 1Dh <sup>(4)</sup>   | CCP2CON | _                    | _              | CCP2X               | CCP2Y               | ССР2М3  | CCP2M2 | CCP2M1  | ССР2М0  | 00<br>0000               | 00<br>0000                      |

$\begin{tabular}{ll} Legend: & x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode. \\ \end{tabular}$

Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

<sup>2:</sup> Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

<sup>3:</sup> The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

<sup>4:</sup> These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD<br>RATE<br>(K) | FOSC = 2 | % ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH<br>KBAUD | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|----------|---------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|------------------|-----------------|-----------------------------|

| 9.6                 | 9.615    | +0.16   | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520            | -0.83           | 46                          |

| 19.2                | 19.230   | +0.16   | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454           | +1.32           | 22                          |

| 38.4                | 37.878   | -1.36   | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286           | -2.90           | 11                          |

| 57.6                | 56.818   | -1.36   | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930           | -2.90           | 7                           |

| 115.2               | 113.636  | -1.36   | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860          | -2.90           | 3                           |

| 250                 | 250      | 0       | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA               | -               | -                           |

| 625                 | 625      | 0       | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA               | -               | -                           |

| 1250                | 1250     | 0       | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA               | -               | -                           |

| BAUD        | Fosc = 5 | 5.068 MHz  | SPBRG              | 4 MHz  |            | SPBRG              | 3.579 MI | Ηz         | SPBRG              | 1 MHz  |            | SPBRG              | 32.768 I | kHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) |

| 9.6         | 9.6      | 0          | 32                 | NA     | -          | -                  | 9.727    | +1.32      | 22                 | 8.928  | -6.99      | 6                  | NA       | -          | -                  |

| 19.2        | 18.645   | -2.94      | 16                 | 1.202  | +0.17      | 207                | 18.643   | -2.90      | 11                 | 20.833 | +8.51      | 2                  | NA       | -          | -                  |

| 38.4        | 39.6     | +3.12      | 7                  | 2.403  | +0.13      | 103                | 37.286   | -2.90      | 5                  | 31.25  | -18.61     | 1                  | NA       | -          | -                  |

| 57.6        | 52.8     | -8.33      | 5                  | 9.615  | +0.16      | 25                 | 55.930   | -2.90      | 3                  | 62.5   | +8.51      | 0                  | NA       | -          | -                  |

| 115.2       | 105.6    | -8.33      | 2                  | 19.231 | +0.16      | 12                 | 111.860  | -2.90      | 1                  | NA     | -          | -                  | NA       | -          | -                  |

| 250         | NA       | -          | -                  | NA     | -          | -                  | 223.721  | -10.51     | 0                  | NA     | -          | -                  | NA       | -          | -                  |

| 625         | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  |

| 1250        | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  |

**Note:** For the PIC16C63/R63/656A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

| RLF               | Rotate Left f the                                                                                           | rough Ca                    | rry                  | RRF               | Rotate F                       | Right f th                                                  | rough C                                                                  | arry                  |

|-------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|-------------------|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|

| Syntax:           | [ label ] RLF                                                                                               | f,d                         |                      | Syntax:           | [ label ]                      | RRF f,                                                      | d                                                                        |                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                             |                             |                      | Operands:         | $0 \le f \le 12$ $d \in [0,1]$ |                                                             |                                                                          |                       |

| Operation:        | See description                                                                                             | below                       |                      | Operation:        | See des                        | cription b                                                  | elow                                                                     |                       |

| Status Affected:  | С                                                                                                           |                             |                      | Status Affected:  | С                              |                                                             |                                                                          |                       |

| Encoding:         | 00 1101                                                                                                     | dfff                        | ffff                 | Encoding:         | 0.0                            | 1100                                                        | dfff                                                                     | ffff                  |

| Description:      | The contents of re one bit to the left ti Flag. If 'd' is 0 the W register. If 'd' is back in register 'f'. | nrough the<br>result is pla | Carry<br>ced in the  | Description:      | one bit to<br>Flag. If 'd'     | the right t<br>is 0 the re<br>r. If 'd' is 1<br>gister 'f'. | ister 'f' are<br>hrough the<br>esult is pla-<br>the result<br>Register f | e Carry<br>ced in the |

| Words:            | 1                                                                                                           |                             |                      | Words:            | 1                              |                                                             |                                                                          |                       |

| Cycles:           | 1                                                                                                           |                             |                      | Cycles:           | 1                              |                                                             |                                                                          |                       |

| Q Cycle Activity: | Q1 Q2                                                                                                       | Q3                          | Q4                   | Q Cycle Activity: | Q1                             | Q2                                                          | Q3                                                                       | Q4                    |

|                   | Decode Read<br>register<br>'f'                                                                              | Process<br>data             | Write to destination |                   | Decode                         | Read<br>register<br>'f'                                     | Process<br>data                                                          | Write to destination  |

| Example           | RLF R                                                                                                       | EG1,0                       |                      | Example           | RRF                            |                                                             | REG1,0                                                                   |                       |

|                   | Before Instruction                                                                                          | n                           |                      |                   | Before Ir                      | struction                                                   | 1                                                                        |                       |

|                   | REG1<br>C                                                                                                   | = 111<br>= 0                | 0 0110               |                   |                                | REG1                                                        |                                                                          | 0 0110                |

|                   | After Instruction                                                                                           | = 0                         |                      |                   | After Ins                      | C                                                           | = 0                                                                      |                       |

|                   | REG1                                                                                                        | = 111                       | 0 0110               |                   | 7 (113)                        | REG1                                                        | = 111                                                                    | 0 0110                |

|                   | W                                                                                                           | = 110                       | 0 1100               |                   |                                | W                                                           | = 011                                                                    | 1 0011                |

|                   | С                                                                                                           | = 1                         |                      |                   |                                | С                                                           | = 0                                                                      |                       |

### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$  for extended,

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

0°C ≤ IA ≤ +/0°C for commercial

Operating voltage VDD range as described in DC spec Section 15.1 and Section 15.2.

|              | Oction 10.2.                               |       |         |      |     |       |                                                                   |  |  |  |  |  |  |

|--------------|--------------------------------------------|-------|---------|------|-----|-------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Param<br>No. | Characteristic                             | Sym   | Min     | Тур† | Max | Units | Conditions                                                        |  |  |  |  |  |  |

|              | Output High Voltage                        |       |         |      |     |       |                                                                   |  |  |  |  |  |  |

| D090         | I/O ports (Note 3)                         | Vон   | VDD-0.7 | -    | -   | V     | IOH = -3.0 mA,<br>VDD = 4.5V, -40°C to +85°C                      |  |  |  |  |  |  |

| D090A        |                                            |       | VDD-0.7 | -    | -   | V     | IOH = -2.5 mA,<br>VDD = 4.5V, -40°C to +125°C                     |  |  |  |  |  |  |

| D092         | OSC2/CLKOUT (RC osc config)                |       | VDD-0.7 | -    | -   | V     | IOH = -1.3 mA,<br>VDD = 4.5V, -40°C to +85°C                      |  |  |  |  |  |  |

| D092A        |                                            |       | VDD-0.7 | -    | -   | V     | IOH = -1.0 mA,<br>VDD = 4.5V, -40°C to +125°C                     |  |  |  |  |  |  |

| D150*        | Open-Drain High Voltage                    | Vod   | -       | -    | 14  | V     | RA4 pin                                                           |  |  |  |  |  |  |

|              | Capacitive Loading Specs on<br>Output Pins |       |         |      |     |       |                                                                   |  |  |  |  |  |  |

| D100         | OSC2 pin                                   | Cosc2 |         |      | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |  |  |

| D101         | All I/O pins and OSC2 (in RC mode)         | Cio   |         |      | 50  | pF    |                                                                   |  |  |  |  |  |  |

\* The parameters are characterized but not tested.

DC CHARACTERISTICS

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

- The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

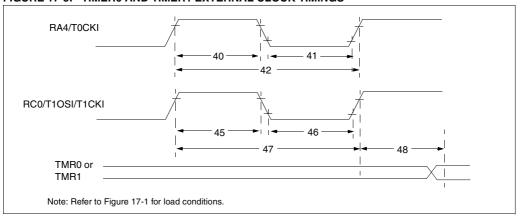

FIGURE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic        |                   |                    | Min                                       | Typ† | Max   | Units | Conditions                         |

|--------------|------|-----------------------|-------------------|--------------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H | T0CKI High Pulse V    | Vidth             | No Prescaler       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |      |                       |                   | With Prescaler     | 10                                        | _    | _     | ns    | parameter 42                       |

| 41*          | TtOL | T0CKI Low Pulse W     | /idth             | No Prescaler       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |      |                       |                   | With Prescaler     | 10                                        | _    | _     | ns    | parameter 42                       |

| 42*          | Tt0P | T0CKI Period          |                   | No Prescaler       | Tcy + 40                                  | _    | _     | ns    |                                    |

|              |      |                       |                   | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H | T1CKI High Time       | Synchronous, F    |                    | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |      |                       | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _    | _     | ns    | parameter 47                       |

|              |      |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _    | _     | ns    |                                    |

|              |      |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _    | _     | ns    |                                    |

|              |      |                       |                   | PIC16 <b>LC</b> 6X | 50                                        | _    | _     | ns    |                                    |

| 46*          | Tt1L | T1CKI Low Time        | Synchronous, F    |                    | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |      |                       | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _    | _     | ns    | parameter 47                       |

|              |      |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _    | _     | ns    |                                    |

|              |      |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _    | _     | ns    |                                    |

|              |      |                       |                   | PIC16 <b>LC</b> 6X | 50                                        | _    | _     | ns    |                                    |

| 47*          | Tt1P | T1CKI input period    | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N        | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |      |                       |                   | PIC16 <b>LC</b> 6X | Greater of:<br>50 OR TCY + 40<br>N        |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |      |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                        | _    | _     | ns    |                                    |

|              |      |                       |                   | PIC16 <b>LC</b> 6X | 100                                       | -    | _     | ns    |                                    |

|              | Ft1  | Timer1 oscillator inp |                   |                    | DC                                        | -    | 200   | kHz   |                                    |

|              |      | (oscillator enabled b |                   |                    |                                           |      |       |       |                                    |

| 48<br>* T    |      | 1 Delay from external |                   |                    | 2Tosc                                     | _    | 7Tosc | _     |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

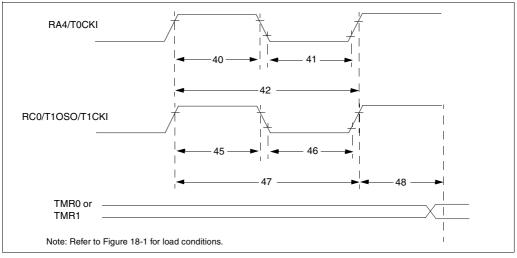

FIGURE 18-6: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 18-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym      | Characteristic        |                   |                                       | Min                                       | Typ† | Max   | Units | Conditions                         |

|--------------|----------|-----------------------|-------------------|---------------------------------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H     | T0CKI High Pulse V    | Vidth             | No Prescaler                          | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                       |                   | With Prescaler                        | 10                                        | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L     | T0CKI Low Pulse W     | /idth             | No Prescaler                          | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                       |                   | With Prescaler                        | 10                                        | _    | _     | ns    | parameter 42                       |

| 42*          | Tt0P     | T0CKI Period          |                   | No Prescaler<br>With Prescaler        | Tcy + 40                                  | _    | _     | ns    |                                    |

|              |          |                       |                   |                                       | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H     | T1CKI High Time       | Synchronous, F    |                                       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                       | Synchronous,      | PIC16 <b>C</b> 6X                     | 15                                        | _    | _     | ns    | parameter 47                       |

|              |          |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X                    | 25                                        | _    | _     | ns    |                                    |

|              |          |                       | Asynchronous      | PIC16 <b>C</b> 6X                     | 30                                        | _    | _     | ns    |                                    |

|              |          |                       |                   | PIC16 <b>LC</b> 6X                    | 50                                        | _    | _     | ns    |                                    |

| 46*          | Tt1L     | T1CKI Low Time        | Synchronous, F    |                                       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |          |                       | Synchronous,      | PIC16 <b>C</b> 6X                     | 15                                        | _    | _     | ns    | parameter 47                       |

|              |          |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X                    | 25                                        | -    | _     | ns    |                                    |

|              |          |                       | Asynchronous      | PIC16 <b>C</b> 6X                     | 30                                        | _    | _     | ns    |                                    |

|              |          |                       |                   | PIC16 <b>LC</b> 6X                    | 50                                        | _    | _     | ns    |                                    |

| 47*          | Tt1P     | T1CKI input period    | Synchronous       | PIC16 <b>C</b> 6X                     | Greater of:<br>30 OR TCY + 40<br>N        | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                       |                   | PIC16 <b>LC</b> 6X                    | Greater of:<br>50 OR TCY + 40<br>N        |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                       | Asynchronous      | PIC16 <b>C</b> 6X                     | 60                                        | _    | _     | ns    |                                    |

|              |          |                       |                   | PIC16 <b>LC</b> 6X                    | 100                                       | _    | _     | ns    |                                    |

|              | Ft1      | Timer1 oscillator inp |                   |                                       | DC                                        | _    | 200   | kHz   |                                    |

|              |          | (oscillator enabled b |                   | · · · · · · · · · · · · · · · · · · · |                                           |      |       |       |                                    |

| 48           | TCKEZtmr | Delay from external   | clock edge to tir | ner increment                         | 2Tosc                                     | -    | 7Tosc | _     |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

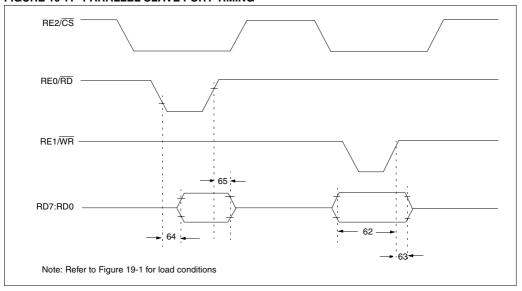

FIGURE 19-7: PARALLEL SLAVE PORT TIMING

TABLE 19-7: PARALLEL SLAVE PORT REQUIREMENTS

| Parameter No. | Sym      | Characteristic                         |                                            | Min | Typ† | Max | Units | Conditions |

|---------------|----------|----------------------------------------|--------------------------------------------|-----|------|-----|-------|------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS↑ (setup | ta in valid before WR↑ or CS↑ (setup time) |     | _    | _   | ns    |            |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data–in invalid (hold    | PIC16 <b>C</b> 65                          | 20  | _    | _   | ns    |            |

|               |          | time)                                  | PIC16 <b>LC</b> 65                         | 35  | _    | _   | ns    |            |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid          | •                                          | _   | _    | 80  | ns    |            |

| 65            | TrdH2dtl | RD↑ or CS↑ to data–out invalid         | ↑ or CS↑ to data-out invalid               |     | _    | 30  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

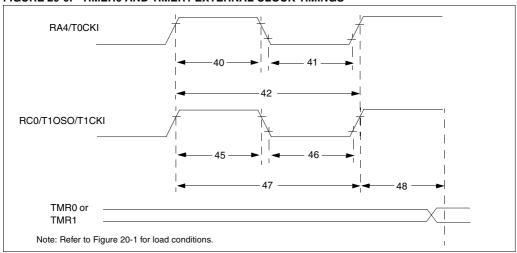

FIGURE 20-6: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 20-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                 |                   |                    | Min                                       | Typ† | Max   | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|-------------------|--------------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse V                             | Vidth             | No Prescaler       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |           |                                                |                   | With Prescaler     | 10                                        | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth             | No Prescaler       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |           |                                                |                   | With Prescaler     | 10                                        | _    | _     | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                   | No Prescaler       | Tcy + 40                                  | _    | _     | ns    |                                    |

|              |           |                                                |                   | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, F    | rescaler = 1       | 0.5Tcy + 20                               | _    | _     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _    | _     | ns    | parameter 47                       |

|              |           |                                                | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _    | _     | ns    |                                    |

|              |           |                                                | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _    | _     | ns    |                                    |

|              |           |                                                |                   | PIC16 <b>LC</b> 6X | 50                                        | _    | _     | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, F    | rescaler = 1       | 0.5TCY + 20                               | _    | _     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _    | _     | ns    | parameter 47                       |

|              |           |                                                | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _    | _     | ns    |                                    |

|              |           |                                                | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _    | _     | ns    |                                    |

|              |           |                                                |                   | PIC16 <b>LC</b> 6X | 50                                        | _    | _     | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N        | -    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                   | PIC16LC6X          | Greater of:<br>50 OR TCY + 40<br>N        |      |       |       | N = prescale value (1, 2, 4, 8)    |

|              |           |                                                | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                        | _    | _     | ns    |                                    |

|              |           |                                                |                   | PIC16 <b>LC</b> 6X | 100                                       |      |       | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                   |                    | DC                                        | _    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                            | clock edge to tir | ner increment      | 2Tosc                                     | _    | 7Tosc | _     |                                    |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

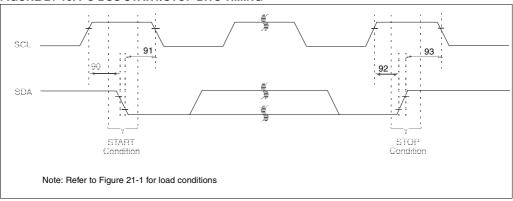

### FIGURE 21-10: I<sup>2</sup>C BUS START/STOP BITS TIMING

### TABLE 21-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |

|---------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|

| 90*           | TSU:STA | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for repeated START  |  |

|               |         | Setup time      | 400 kHz mode | 600  |     | _   | 110   | condition                         |  |

| 91*           | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period the first clock |  |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   | 113   | pulse is generated                |  |

| 92*           | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                   |  |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   | 113   |                                   |  |

| 93            | THD:STO | STOP condition  | 100 kHz mode | 4000 | _   | _   | ns    |                                   |  |

| Ì             |         | Hold time       | 400 kHz mode | 600  | _   | _   | 113   |                                   |  |

These parameters are characterized but not tested.

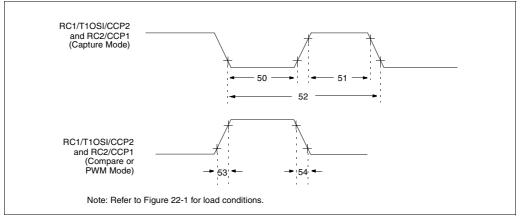

### FIGURE 22-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 22-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter No. | Sym  | Characteristic                                                            |                |                       | Min         | Тур† | Max | Units                              | Conditions |

|---------------|------|---------------------------------------------------------------------------|----------------|-----------------------|-------------|------|-----|------------------------------------|------------|

| 50*           | TccL | CCP1 and CCP2 input low time                                              | No Prescaler   |                       | 0.5Tcy + 20 | _    | _   | ns                                 |            |

|               |      |                                                                           | With Prescaler | PIC16 <b>C</b> 66/67  | 10          | _    | _   | ns                                 |            |

|               |      |                                                                           |                | PIC16 <b>LC</b> 66/67 | 20          | _    | _   | ns                                 |            |

| 51*           | TccH | COLL AND COLZ                                                             | No Prescaler   |                       | 0.5Tcy + 20 | _    | _   | ns                                 |            |

|               |      |                                                                           | With Prescaler | PIC16 <b>C</b> 66/67  | 10          | _    | _   | ns                                 |            |

|               |      |                                                                           |                | PIC16 <b>LC</b> 66/67 | 20          | _    | _   | ns                                 |            |

| 52*           | TccP | CCP1 and CCP2 input period                                                |                | 3Tcy + 40<br>N        | _           | _    | ns  | N = prescale value<br>(1,4, or 16) |            |

| 53*           | TccR | CCP1 and CCP2 output rise time PIC16 <b>C</b> 66/67 PIC16 <b>LC</b> 66/67 |                | PIC16 <b>C</b> 66/67  | _           | 10   | 25  | ns                                 |            |

|               |      |                                                                           |                | PIC16 <b>LC</b> 66/67 | _           | 25   | 45  | ns                                 |            |

| 54*           | TccF | CCP1 and CCP2 output fall time                                            |                | PIC16 <b>C</b> 66/67  | _           | 10   | 25  | ns                                 |            |

|               |      |                                                                           |                | PIC16 <b>LC</b> 66/67 | _           | 25   | 45  | ns                                 |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

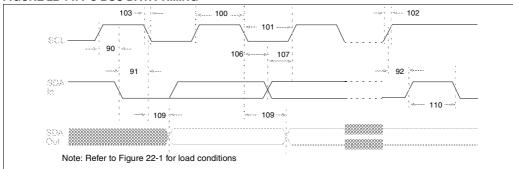

### FIGURE 22-14: I<sup>2</sup>C BUS DATA TIMING

TABLE 22-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |  |

|-----------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|--|

| No.       |         |                        |              |            |      |       |                                                  |  |

| 100*      | THIGH   | Clock high time        | 100 kHz mode | 4.0        | _    | μS    | Device must operate at a mini-<br>mum of 1.5 MHz |  |

|           |         |                        | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a mini-<br>mum of 10 MHz  |  |

|           |         |                        | SSP Module   | 1.5TcY     | _    |       |                                                  |  |

| 101*      | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a mini-<br>mum of 1.5 MHz |  |

| İ         |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |  |

|           |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |  |

| 102*      | TR      | SDA and SCL rise       | 100 kHz mode | _          | 1000 | ns    |                                                  |  |

| l         |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |  |

| 103*      | TF      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                                  |  |

|           |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |  |

| 90*       | Tsu:sta | START condition        | 100 kHz mode | 4.7        | _    | μS    | Only relevant for repeated                       |  |

|           |         | setup time             | 400 kHz mode | 0.6        | _    | μS    | START condition                                  |  |

| 91*       | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μS    | After this period the first clock                |  |

|           |         | time                   | 400 kHz mode | 0.6        | _    | μS    | pulse is generated                               |  |

| 106*      | THD:DAT | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                                  |  |

|           |         |                        | 400 kHz mode | 0          | 0.9  | μS    |                                                  |  |

| 107*      | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | _    | ns    | Note 2                                           |  |

|           |         |                        | 400 kHz mode | 100        | _    | ns    |                                                  |  |

| 92*       | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | _    | μS    |                                                  |  |

|           |         | time                   | 400 kHz mode | 0.6        | _    | μS    |                                                  |  |

| 109*      | TAA     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |  |

|           |         | clock                  | 400 kHz mode | _          | _    | ns    |                                                  |  |

| 110*      | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                        |  |

| ı         |         |                        | 400 kHz mode | 1.3        | _    | μs    | before a new transmission can start              |  |

|           | Cb      | Bus capacitive loading |              | _          | 400  | pF    |                                                  |  |

These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

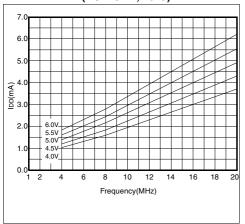

FIGURE 23-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

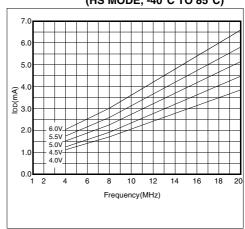

### FIGURE 23-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

Mote:

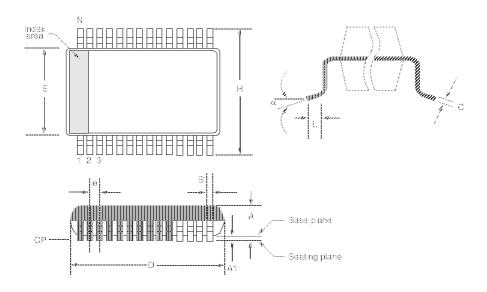

### 24.10 28-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Plastic SSOP |             |           |        |       |           |  |  |  |

|--------|-----------------------------|-------------|-----------|--------|-------|-----------|--|--|--|

|        |                             | Millimeters |           | Inches |       |           |  |  |  |

| Symbol | Min                         | Max         | Notes     | Min    | Max   | Notes     |  |  |  |

| α      | 0°                          | 8°          |           | 0°     | 8°    |           |  |  |  |

| Α      | 1.730                       | 1.990       |           | 0.068  | 0.078 |           |  |  |  |

| A1     | 0.050                       | 0.210       |           | 0.002  | 0.008 |           |  |  |  |

| В      | 0.250                       | 0.380       |           | 0.010  | 0.015 |           |  |  |  |

| С      | 0.130                       | 0.220       |           | 0.005  | 0.009 |           |  |  |  |

| D      | 10.070                      | 10.330      |           | 0.396  | 0.407 |           |  |  |  |

| E      | 5.200                       | 5.380       |           | 0.205  | 0.212 |           |  |  |  |

| е      | 0.650                       | 0.650       | Reference | 0.026  | 0.026 | Reference |  |  |  |

| Н      | 7.650                       | 7.900       |           | 0.301  | 0.311 |           |  |  |  |

| L      | 0.550                       | 0.950       |           | 0.022  | 0.037 |           |  |  |  |

| N      | 28                          | 28          |           | 28     | 28    |           |  |  |  |

| CP     | -                           | 0.102       |           | -      | 0.004 |           |  |  |  |

| Transfer Acknowledge9                                                                                                                                                                        |                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Transmission10                                                                                                                                                                               |                      |

| ID Locations14                                                                                                                                                                               | 2                    |

| IDLE_MODE10                                                                                                                                                                                  | )4                   |

| In-circuit Serial Programming14                                                                                                                                                              | 12                   |

| INDF24, 26, 28, 30, 32, 3                                                                                                                                                                    |                      |

| Indirect Addressing4                                                                                                                                                                         |                      |

| Instruction Cycle 1                                                                                                                                                                          |                      |

| Instruction Flow/Pipelining1                                                                                                                                                                 |                      |

| Instruction Format                                                                                                                                                                           |                      |

| Instruction Set                                                                                                                                                                              |                      |

| ADDLW14                                                                                                                                                                                      | 15                   |

| ADDWF                                                                                                                                                                                        |                      |

| ADDWF                                                                                                                                                                                        |                      |

|                                                                                                                                                                                              |                      |

| ANDWF14                                                                                                                                                                                      |                      |

| BCF14                                                                                                                                                                                        | -                    |

| BSF14                                                                                                                                                                                        |                      |

| BTFSC                                                                                                                                                                                        |                      |

| BTFSS14                                                                                                                                                                                      |                      |

| CALL 14                                                                                                                                                                                      |                      |

| CLRF14                                                                                                                                                                                       |                      |

| CLRW14                                                                                                                                                                                       |                      |

| CLRWDT14                                                                                                                                                                                     | 8                    |

| COMF14                                                                                                                                                                                       | 9                    |

| DECF14                                                                                                                                                                                       | 19                   |

| DECFSZ14                                                                                                                                                                                     | 19                   |

| GOTO15                                                                                                                                                                                       | 0                    |

| INCF                                                                                                                                                                                         | 60                   |

| INCFSZ15                                                                                                                                                                                     | 51                   |

| IORLW15                                                                                                                                                                                      | 51                   |

| IORWF15                                                                                                                                                                                      |                      |

| MOVF                                                                                                                                                                                         |                      |

| MOVLW                                                                                                                                                                                        |                      |

| MOVWF                                                                                                                                                                                        |                      |

| NOP                                                                                                                                                                                          |                      |

| OPTION                                                                                                                                                                                       |                      |

| RETFIE                                                                                                                                                                                       |                      |

| RETLW                                                                                                                                                                                        |                      |

|                                                                                                                                                                                              |                      |

| RETURN15                                                                                                                                                                                     |                      |

| RLF                                                                                                                                                                                          |                      |

| RRF                                                                                                                                                                                          |                      |

| SLEEP                                                                                                                                                                                        |                      |

| SUBLW                                                                                                                                                                                        |                      |

| SUBWF                                                                                                                                                                                        |                      |

| SWAPF15                                                                                                                                                                                      |                      |

| TRIS15                                                                                                                                                                                       |                      |

| XORLW15                                                                                                                                                                                      |                      |

| XORWF15                                                                                                                                                                                      |                      |

| Section14                                                                                                                                                                                    |                      |

| Summary Table14                                                                                                                                                                              | 4                    |

| INTCON24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 3                                                                                                                                              | 34                   |

| INTE3                                                                                                                                                                                        | 37                   |

| INTEDG3                                                                                                                                                                                      | 36                   |

| Interrupt Edge Select bit, INTEDG3                                                                                                                                                           | 36                   |

| Interrupt on Change Feature5                                                                                                                                                                 | 63                   |

| Interrupts                                                                                                                                                                                   |                      |

| Section13                                                                                                                                                                                    | 36                   |

| CCP                                                                                                                                                                                          |                      |

| CCP1                                                                                                                                                                                         |                      |

|                                                                                                                                                                                              | _                    |