Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66-20i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE                | 4-6:    | SPECIA               |                                                          | <b>FION RE</b>            | GISTERS        | S FOR T     | HE PIC1     | 6C66/67        | (Cont.'c  | I)                       |                                                |

|----------------------|---------|----------------------|----------------------------------------------------------|---------------------------|----------------|-------------|-------------|----------------|-----------|--------------------------|------------------------------------------------|

| Address              | Name    | Bit 7                | Bit 6                                                    | Bit 5                     | Bit 4          | Bit 3       | Bit 2       | Bit 1          | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

| Bank 1               |         |                      |                                                          |                           |                |             |             |                |           |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing           | this location                                            | uses conte                | nts of FSR to  | address dat | a memory (n | ot a physical  | register) | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU                 | INTEDG                                                   | TOCS                      | T0SE           | PSA         | PS2         | PS1            | PS0       | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)                                            | Least Sig                 | nificant Byte  |             |             |                |           | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP                  | RP1                                                      | RP0                       | TO             | PD          | Z           | DC             | С         | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data        | a memory ad                                              | dress point               | er             |             |             |                | 1         | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                    | _                                                        | PORTA Da                  | ta Direction R | legister    |             |                |           | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat            | ta Direction I                                           | Register                  |                |             |             |                |           | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Dat            | ta Direction                                             | Register                  |                | 1111 1111   | 1111 1111   |                |           |                          |                                                |

| 88h <sup>(5)</sup>   | TRISD   | PORTD Dat            | ta Direction                                             | Register                  |                | 1111 1111   | 1111 1111   |                |           |                          |                                                |

| 89h <sup>(5)</sup>   | TRISE   | IBF                  | OBF                                                      | IBOV                      | PSPMODE        | _           | PORTE Da    | ta Direction I | Bits      | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                    | Write Buffer for the upper 5 bits of the Program Counter |                           |                |             |             |                |           | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE                                                     | TOIE                      | INTE           | RBIE        | TOIF        | INTF           | RBIF      | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | PSPIE <sup>(6)</sup> | (4)                                                      | RCIE                      | TXIE           | SSPIE       | CCP1IE      | TMR2IE         | TMR1IE    | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                    | _                                                        | _                         | _              | _           | _           | _              | CCP2IE    | 0                        | 0                                              |

| 8Eh                  | PCON    | —                    | —                                                        | —                         | -              | _           | _           | POR            | BOR       | dd                       | uu                                             |

| 8Fh                  | -       | Unimpleme            | nted                                                     |                           |                |             | •           |                |           | -                        | _                                              |

| 90h                  |         | Unimpleme            | nted                                                     |                           |                |             |             |                |           | _                        | _                                              |

| 91h                  | -       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | -                        | —                                              |

| 92h                  | PR2     | Timer2 Peri          | od Register                                              |                           |                |             |             |                |           | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou           | us Serial Por                                            | t (I <sup>2</sup> C mode) | Address Reg    | gister      |             |                |           | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | SMP                  | CKE                                                      | D/A                       | Р              | S           | R/W         | UA             | BF        | 0000 0000                | 0000 0000                                      |

| 95h                  | -       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | _                        | —                                              |

| 96h                  | -       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | _                        | —                                              |

| 97h                  | -       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | _                        | —                                              |

| 98h                  | TXSTA   | CSRC                 | TX9                                                      | TXEN                      | SYNC           | —           | BRGH        | TRMT           | TX9D      | 0000 -010                | 0000 -010                                      |

| 99h                  | SPBRG   | Baud Rate            | Generator R                                              | egister                   |                |             |             |                |           | 0000 0000                | 0000 0000                                      |

| 9Ah                  | -       | Unimpleme            | Jnimplemented                                            |                           |                |             |             |                |           | _                        | _                                              |

| 9Bh                  | _       | Unimpleme            | Inimplemented                                            |                           |                |             |             |                |           | -                        | —                                              |

| 9Ch                  | _       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | —                        | _                                              |

| 9Dh                  | —       | Unimpleme            | Inimplemented                                            |                           |                |             |             |                |           | —                        | —                                              |

| 9Eh                  | _       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | —                        | —                                              |

| 9Fh                  | -       | Unimpleme            | nted                                                     |                           |                |             |             |                |           | -                        | -                                              |

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

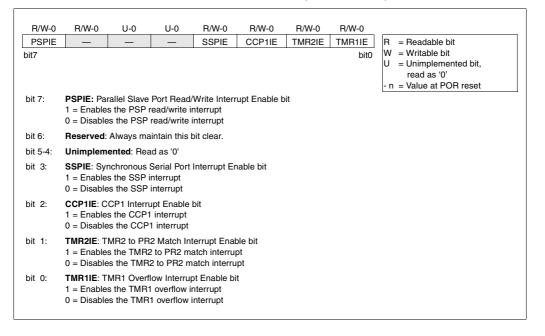

| R/W-0    | R/W-0                                           | R/W-0<br>RCIE                                                                                                              | R/W-0<br>TXIE | R/W-0<br>SSPIE | R/W-0<br>CCP1IE | R/W-0<br>TMR2IE | R/W-0<br>TMR1IE | R = Readable bit                                                                                                     |  |  |  |  |  |

|----------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit7     |                                                 |                                                                                                                            | I             |                |                 | I               | bit0            | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |  |  |  |

| bit 7-6: | Reserved:                                       | Always ma                                                                                                                  | aintain thes  | e bits clear.  |                 |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 5:   | 1 = Enable                                      | CIE: USART Receive Interrupt Enable bit<br>= Enables the USART receive interrupt<br>= Disables the USART receive interrupt |               |                |                 |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 4:   | <b>TXIE:</b> USA<br>1 = Enables<br>0 = Disable  | s the USAF                                                                                                                 | RT transmit   | interrupt      |                 |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 3:   | SSPIE: Syr<br>1 = Enables<br>0 = Disable        | s the SSP i                                                                                                                | nterrupt      | Interrupt Er   | nable bit       |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 2:   | <b>CCP1IE</b> : C<br>1 = Enables<br>0 = Disable | s the CCP1                                                                                                                 | interrupt     | oit            |                 |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 1:   | <b>TMR2IE</b> : T<br>1 = Enables<br>0 = Disable | s the TMR2                                                                                                                 | 2 to PR2 ma   |                |                 |                 |                 |                                                                                                                      |  |  |  |  |  |

| bit 0:   | <b>TMR1IE</b> : T<br>1 = Enables<br>0 = Disable | s the TMR                                                                                                                  | l overflow i  | nterrupt       | t               |                 |                 |                                                                                                                      |  |  |  |  |  |

### FIGURE 4-13: PIE1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 8Ch)

### FIGURE 4-14: PIE1 REGISTER FOR PIC16C64/64A/R64 (ADDRESS 8Ch)

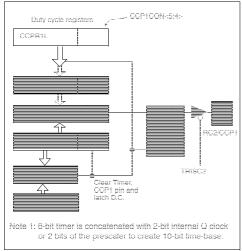

### 10.3 PWM Mode

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 10-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 10.3.3.

### FIGURE 10-4: SIMPLIFIED PWM BLOCK DIAGRAM

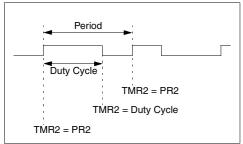

A PWM output (Figure 10-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### FIGURE 10-5: PWM OUTPUT

### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM duty cycle is latched from CCPR1L into CCPR1H

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

| Note: | The Timer2 postscaler (see Section 9.1) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be forced to the low level.

### 11.5.1.2 RECEPTION

When the R/ $\overline{W}$  bit of the address byte is clear and an address match occurs, the R/ $\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W=0         Receiving Data         ACK         Receiving Data         ACK           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | F 7<br>I I<br>I I<br>/ I PI<br>- I<br>- I<br>- I<br>- I<br>- I<br>- I<br>- I<br>- |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bus Master<br>terminates<br>transfer                                              |

| SSPOV (SSPCON<6>)<br>Bit SSPOV is set because the SSPBUF register is still full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

| ACK is not sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

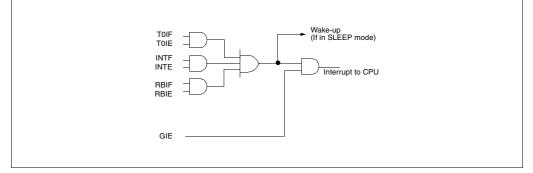

## FIGURE 13-17: INTERRUPT LOGIC FOR PIC16C61

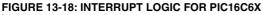

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|-------|--------|--------|--------|--------|

| PIC16C62  | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C62A | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16CR62 | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C63  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR63 | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64A | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C65  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C65A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR65 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C66  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C67  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

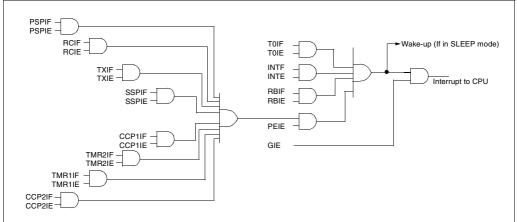

### 13.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if edge select bit INTEDG (OPTION<6>) is set, or falling, if bit INTEDG is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP, if enable bit INTE was set prior to going into SLEEP. The status of global enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 13.8 for details on SLEEP mode.

### 13.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0).

### 13.5.3 PORTB INTERRUPT ON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 5.2).

Note: For the PIC16C61/62/64/65, if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then flag bit RBIF may not get set.

### FIGURE 13-19: INT PIN INTERRUPT TIMING

| RLF               | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                   | Decode Read register 'f' Vite to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | Decode Read register data Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Example           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example           | RRF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -           After Instruction         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td></td> <td>Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -&lt;</td> |                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -< |  |  |  |  |

| <b>Applicable Devices</b> | 61 | 60 | 601 | Deg | 60 | Dec | 61 | 611 | DGA | 65 | 65A | Dee | 66 | 67 |

|---------------------------|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| Applicable Devices        | 01 | 02 | 02A | n02 | 03 | n03 | 04 | 04A | n04 | 05 | 05A | H00 | 00 | 07 |

|       |                                    | Standa   | rd Operat  | ing Co |                                                |          | ss otherwise stated)                                |  |  |

|-------|------------------------------------|----------|------------|--------|------------------------------------------------|----------|-----------------------------------------------------|--|--|

|       |                                    | Operatir | ng temper  | ature  | -40°C                                          | S ≤ TA   | $\Delta \leq +125^{\circ}C$ for extended,           |  |  |

|       | RACTERISTICS                       |          |            |        | -40°C $\leq$ TA $\leq$ +85°C for industrial an |          |                                                     |  |  |

|       | ARACIERISTICS                      |          |            |        | 0°C                                            | ≤ T⁄     | $A \leq +70^{\circ}C$ for commercial                |  |  |

|       |                                    | Operatir | ng voltage | VDD r  | ange as c                                      | describe | ed in DC spec Section 15.1 and                      |  |  |

|       |                                    | Section  | 15.2.      |        |                                                |          |                                                     |  |  |