Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c66t-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16CXX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C61** device has 36 bytes of RAM and 13 I/O pins. In addition a timer/counter is available.

The **PIC16C62/62A/R62** devices have 128 bytes of RAM and 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI<sup>TM</sup>) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus.

The **PIC16C63/R63** devices have 192 bytes of RAM, while the **PIC16C66** has 368 bytes. All three devices have 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit ( $I^2C$ ) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also know as a Serial Communications Interface or SCI.

The **PIC16C64/64A/R64** devices have 128 bytes of RAM and 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. An 8-bit Parallel Slave Port is also provided.

The **PIC16C65/65A/R65** devices have 192 bytes of RAM, while the **PIC16C67** has 368 bytes. All four devices have 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmit-

ter (USART) is also known as a Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is also provided.

The PIC16C6X device family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers a power saving mode. The user can wake the chip from SLEEP through several external and internal interrupts, and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C6X family fits perfectly in applications ranging from high-speed automotive and appliance control to low-power remote sensors, keyboards and telecom processors. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use, and I/O flexibility make the PIC16C6X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions, and co-processor applications).

#### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16CXX family of devices (Appendix B).

#### 1.2 Development Support

PIC16C6X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 15.0 for more details about Microchip's development tools.

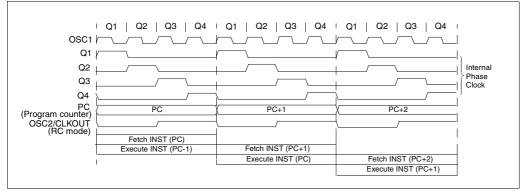

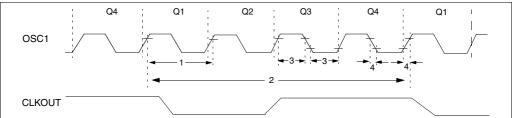

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

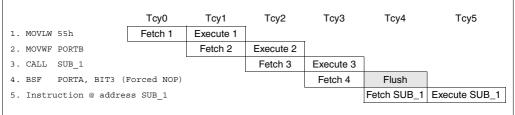

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

| Address                                   | Name    | Bit 7                              | Bit 6                                            | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1        | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|-------------------------------------------|---------|------------------------------------|--------------------------------------------------|---------------------------|---------------|--------------|-----------------|--------------|--------------------|--------------------------|------------------------------------------------|

| Bank 1                                    |         |                                    | •                                                |                           |               |              |                 |              |                    |                          |                                                |

| 80h <sup>(1)</sup>                        | INDF    | Addressing                         | this location                                    | uses conte                | nts of FSR to | address dat  | a memory (n     | ot a physica | register)          | 0000 0000                | 0000 0000                                      |

| 81h                                       | OPTION  | RBPU                               | INTEDG                                           | TOCS                      | T0SE          | PSA          | PS2             | PS1          | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>                        | PCL     | Program Co                         | ounter's (PC)                                    | Least Sig                 | nificant Byte |              |                 |              |                    | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>                        | STATUS  | IRP <sup>(5)</sup>                 | RP1 <sup>(5)</sup>                               | RP0                       | TO            | PD           | z               | DC           | С                  | 0001 1xxx                | 000q quui                                      |

| 84h <sup>(1)</sup>                        | FSR     | Indirect data                      | a memory ac                                      | Idress point              | er            |              |                 |              |                    | xxxx xxxx                | սսսս սսսս                                      |

| 85h TRISA — PORTA Data Direction Register |         |                                    |                                                  |                           |               |              |                 |              | 11 1111            | 11 1111                  |                                                |

| 86h                                       | TRISB   | SB PORTB Data Direction Register   |                                                  |                           |               |              |                 |              |                    | 1111 1111                | 1111 1111                                      |

| 87h                                       | TRISC   | RISC PORTC Data Direction Register |                                                  |                           |               |              |                 |              |                    | 1111 1111                | 1111 1111                                      |

| 88h                                       | TRISD   | ISD PORTD Data Direction Register  |                                                  |                           |               |              |                 |              |                    | 1111 1111                | 1111 1111                                      |

| 89h                                       | TRISE   | IBF                                | IBF OBF IBOV PSPMODE — PORTE Data Direction Bits |                           |               |              |                 |              |                    | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup>                      | PCLATH  | _                                  | _                                                | —                         | Write Buffer  | for the uppe | r 5 bits of the | e Program C  | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>                        | INTCON  | GIE                                | PEIE                                             | TOIE                      | INTE          | RBIE         | TOIF            | INTF         | RBIF               | 0000 000x                | 0000 0001                                      |

| 8Ch                                       | PIE1    | PSPIE                              | (6)                                              | RCIE                      | TXIE          | SSPIE        | CCP1IE          | TMR2IE       | TMR1IE             | 0000 0000                | 0000 0000                                      |

| 8Dh                                       | PIE2    | _                                  | —                                                | —                         | _             | —            | _               | _            | CCP2IE             | 0                        | (                                              |

| 8Eh                                       | PCON    | _                                  | —                                                | —                         | _             | —            | _               | POR          | BOR <sup>(4)</sup> | dd                       | ui                                             |

| 8Fh                                       | -       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | _                        | —                                              |

| 90h                                       | _       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | _                        | —                                              |

| 91h                                       | _       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | _                        | _                                              |

| 92h                                       | PR2     | Timer2 Peri                        | iod Register                                     |                           |               |              |                 |              |                    | 1111 1111                | 1111 1111                                      |

| 93h                                       | SSPADD  | Synchronou                         | us Serial Por                                    | t (I <sup>2</sup> C mode) | Address Reg   | gister       |                 |              |                    | 0000 0000                | 0000 0000                                      |

| 94h                                       | SSPSTAT | —                                  | _                                                | D/A                       | Р             | S            | R/W             | UA           | BF                 | 00 0000                  | 00 0000                                        |

| 95h                                       | -       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | -                        | —                                              |

| 96h                                       | —       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | -                        | —                                              |

| 97h                                       | -       | Unimpleme                          | nted                                             |                           |               |              |                 |              |                    | -                        | —                                              |

| 98h                                       | TXSTA   | CSRC                               | TX9                                              | TXEN                      | SYNC          | —            | BRGH            | TRMT         | TX9D               | 0000 -010                | 0000 -010                                      |

| 99h                                       | SPBRG   | Baud Rate                          | Generator R                                      | egister                   |               |              |                 |              |                    | 0000 0000                | 0000 0000                                      |

| 9Ah                                       | _       | Unimplemented                      |                                                  |                           |               |              |                 |              | -                  | —                        |                                                |

| 9Bh                                       | _       | Unimplemented                      |                                                  |                           |               |              |                 |              | _                  | _                        |                                                |

| 9Ch                                       | —       | Unimpleme                          | Unimplemented                                    |                           |               |              |                 |              |                    | —                        | —                                              |

| 9Dh                                       | —       | Unimplemented                      |                                                  |                           |               |              |                 |              | -                  | —                        |                                                |

| 9Eh                                       | —       | Unimplemented                      |                                                  |                           |               |              |                 |              | —                  | _                        |                                                |

| 9Fh                                       | _       | — Unimplemented                    |                                                  |                           |               |              |                 |              |                    |                          |                                                |

TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65 (Cont.'d)

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

# 5.0 I/O PORTS

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Some pins for these I/O ports are multiplexed with an alternate function(s) for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

#### 5.1 PORTA and TRISA Register

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

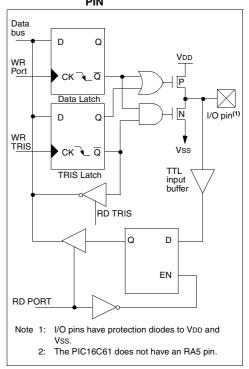

All devices have a 6-bit wide PORTA, except for the PIC16C61 which has a 5-bit wide PORTA.

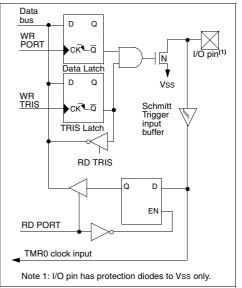

Pin RA4/T0CKI is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a bit in the TRISA register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with Timer0 module clock input to become the RA4/T0CKI pin.

#### EXAMPLE 5-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C66/67 only      |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

#### FIGURE 5-1: BLOCK DIAGRAM OF THE RA3:RA0 PINS AND THE RA5 PIN

#### FIGURE 5-2: BLOCK DIAGRAM OF THE RA4/T0CKI PIN

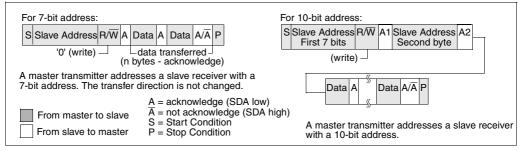

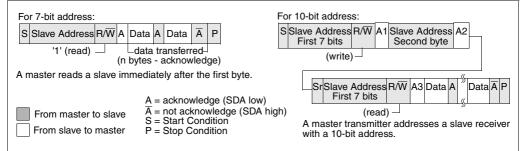

Figure 11-19 and Figure 11-20 show Master-transmitter and Master-receiver data transfer sequences.

When a master does not wish to relinquish the bus (by generating a STOP condition), a repeated START condition (Sr) must be generated. This condition is identical to the start condition (SDA goes high-to-low while

SCL is high), but occurs after a data transfer acknowledge pulse (not the bus-free state). This allows a master to send "commands" to the slave and then receive the requested information or to address a different slave device. This sequence is shown in Figure 11-21.

#### FIGURE 11-19: MASTER-TRANSMITTER SEQUENCE

## FIGURE 11-20: MASTER-RECEIVER SEQUENCE

#### FIGURE 11-21: COMBINED FORMAT

#### 11.5.1 SLAVE MODE

PIC16C6X

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 11-4 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

#### 11.5.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The

address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 11-16). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT-<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### TABLE 11-4: DATA TRANSFER RECEIVED BYTE ACTIONS

| Status Bits as Data<br>Transfer is Received |       |                    |                       | Set bit SSPIF                        |  |

|---------------------------------------------|-------|--------------------|-----------------------|--------------------------------------|--|

| BF                                          | SSPOV | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                  |  |

| 1                                           | 0     | No                 | No                    | Yes                                  |  |

| 1                                           | 1     | No                 | No                    | Yes                                  |  |

| 0                                           | 1     | No                 | No                    | Yes                                  |  |

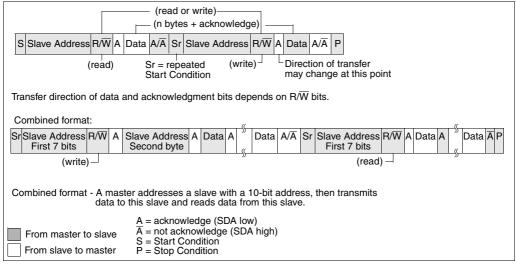

#### 12.3 USART Synchronous Master Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Synchronous Master mode the data is transmitted in a half-duplex manner i.e., transmission and reception do not occur at the same time. When transmitting data the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6 and RC7 I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

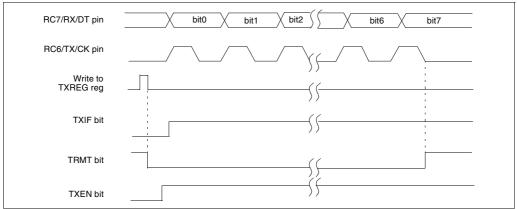

#### 12.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR register is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG register is empty and interrupt flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the status of enable bit TXIE and cannot be cleared in software. It will clear only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR register is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in reset when bits TXEN. CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG register. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hi-impedance. If, during a transmission, either bit CREN or bit SREN is set the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however, is not reset although it is disconnected from the pins. In order to reset the transmitter, the user has to clear enable bit TXEN. If enable bit SREN is set (to interrupt an on going transmission and receive a single word), then after the single word is received, enable bit SREN will be cleared, and the serial port will revert back to transmitting since enable bit TXEN is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, enable bit TXEN should be cleared.

In order to select 9-bit transmission, bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR register was empty and the TXREG register was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{TXIE}}$  .

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name                               | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | (2)       | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA                              | SPEN                 | RX9       | SREN    | CREN  |       | FERR   | OERR   | RX9D      | 0000 -00x               | x00- 0000                       |

| 19h     | TXREG                              | USART Tra            | ansmit Re | egister |       |       |        |        |           | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | (2)       | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA                              | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        | 0000 0000 | 0000 0000               |                                 |

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

#### FIGURE 12-13: SYNCHRONOUS TRANSMISSION THROUGH TXEN

#### 13.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

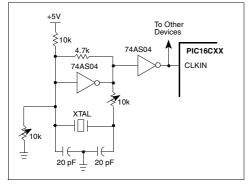

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 13-6 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 13-6: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

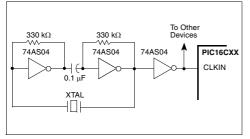

Figure 13-7 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 13-7: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

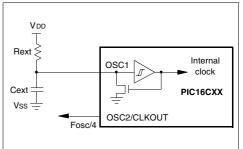

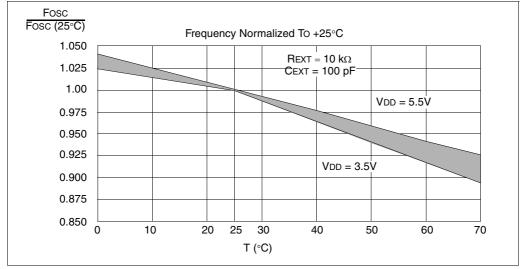

#### 13.2.4 RC OSCILLATOR

For timing insensitive applications the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 13-8 shows how the RC combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-5 for waveform).

#### FIGURE 13-8: RC OSCILLATOR MODE

| RETLW             | Return v                              | vith Liter                                                                                                                                                      | al in W                            |                                         | RETURN            | Return fi                                                                                         | rom Sub          | routine          |                    |  |

|-------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------|-------------------|---------------------------------------------------------------------------------------------------|------------------|------------------|--------------------|--|

| Syntax:           | [ label ]                             | RETLW                                                                                                                                                           | k                                  |                                         | Syntax:           | [ label ]                                                                                         | RETUR            | N                |                    |  |

| Operands:         | $0 \le k \le 2$                       | 55                                                                                                                                                              |                                    |                                         | Operands:         | None                                                                                              |                  |                  |                    |  |

| Operation:        | $k \rightarrow (W);$                  |                                                                                                                                                                 |                                    |                                         | Operation:        | $\text{TOS} \to \text{F}$                                                                         | ъС               |                  |                    |  |

|                   | $TOS \rightarrow F$                   | PC                                                                                                                                                              |                                    |                                         | Status Affected:  | None                                                                                              |                  |                  |                    |  |

| Status Affected:  | None                                  | -                                                                                                                                                               |                                    |                                         | Encoding:         | 00                                                                                                | 0000             | 0000             | 1000               |  |

| Encoding:         | 11                                    | 11 01xx kkkk kkkk                                                                                                                                               |                                    | Description:                            | Return fro        | m subrout                                                                                         | ine. The st      | ack is           |                    |  |

| Description:      | bit literal 'l<br>loaded fro          | he W register is loaded with the eight<br>it literal 'k'. The program counter is<br>baded from the top of the stack (the<br>eturn address). This is a two cycle |                                    |                                         |                   | POPed and the top of the stack<br>is loaded into the program count<br>is a two cycle instruction. |                  |                  |                    |  |

|                   | instruction                           |                                                                                                                                                                 | s is a two c                       | cycle                                   | Words:            | 1                                                                                                 |                  |                  |                    |  |

| Words:            | 1                                     |                                                                                                                                                                 |                                    |                                         | Cycles:           | 2                                                                                                 |                  |                  |                    |  |

| Cycles:           | 2                                     |                                                                                                                                                                 |                                    |                                         | Q Cycle Activity: | Q1                                                                                                | Q2               | Q3               | Q4                 |  |

| Q Cycle Activity: | Q1                                    | Q2                                                                                                                                                              | Q3                                 | Q4                                      | 1st Cycle         | Decode                                                                                            | No-<br>Operation | No-<br>Operation | Pop from the Stack |  |

| 1st Cycle         | Decode                                | Read<br>literal 'k'                                                                                                                                             | No-<br>Operation                   | Write to<br>W, Pop<br>from the<br>Stack | 2nd Cycle         | No-<br>Operation                                                                                  | No-<br>Operation | No-<br>Operation | No-<br>Operation   |  |

| 2nd Cycle         | No-                                   | No-                                                                                                                                                             | No-                                | No-                                     | Example           | RETURN                                                                                            |                  |                  |                    |  |

|                   | Operation                             | Operation                                                                                                                                                       | Operation                          | Operation                               |                   | After Interrupt                                                                                   |                  |                  |                    |  |

| Example           | CALL TABL                             | ;offse                                                                                                                                                          | tains tabl<br>t value<br>has table |                                         |                   |                                                                                                   | PC =             | TOS              |                    |  |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2<br>• | ;W = 0<br>;Begin<br>;                                                                                                                                           |                                    |                                         |                   |                                                                                                   |                  |                  |                    |  |

|                   | RETLW kn                              |                                                                                                                                                                 | of table                           |                                         |                   |                                                                                                   |                  |                  |                    |  |

|                   | Before In                             | truction                                                                                                                                                        | 0x07<br>value of k8                | 3                                       |                   |                                                                                                   |                  |                  |                    |  |

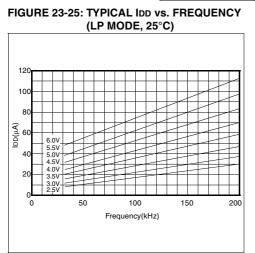

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C61

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range. Note: The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean  $+3\sigma$ ) and (mean  $-3\sigma$ ) respectively where  $\sigma$  is standard deviation.

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |          |  |  |

|--------|------|----------------------------|----------|--|--|

| 20 pF  | 4.7k | 4.52 MHz                   | ± 17.35% |  |  |

|        | 10k  | 2.47 MHz                   | ± 10.10% |  |  |

|        | 100k | 290.86 kHz                 | ± 11.90% |  |  |

| 100 pF | 3.3k | 1.92 MHz                   | ± 9.43%  |  |  |

|        | 4.7k | 1.48 MHz                   | ± 9.83%  |  |  |

|        | 10k  | 788.77 kHz                 | ± 10.92% |  |  |

|        | 100k | 88.11 kHz                  | ± 16.03% |  |  |

| 300 pF | 3.3k | 726.89 kHz                 | ± 10.97% |  |  |

|        | 4.7k | 573.95 kHz                 | ± 10.14% |  |  |

|        | 10k  | 307.31 kHz                 | ± 10.43% |  |  |

|        | 100k | 33.82 kHz                  | ± 11.24% |  |  |

TABLE 16-1: RC OSCILLATOR FREQUENCIES

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

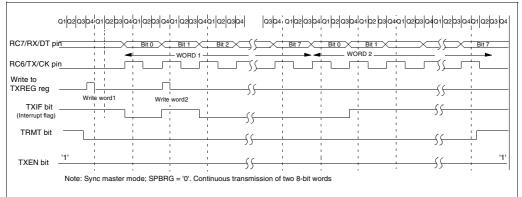

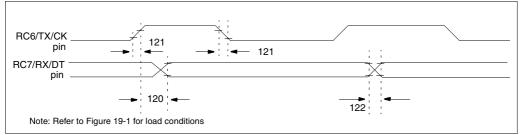

#### FIGURE 19-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No.        | Sym                          | Characteristic                    | ristic             |   |   |     | Units | Conditions |

|-------------------------|------------------------------|-----------------------------------|--------------------|---|---|-----|-------|------------|

| 120 TckH2dtV SYN        |                              | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 65  |   | — | 80  | ns    |            |

|                         | Clock high to data out valid |                                   | PIC16 <b>LC</b> 65 | - | — | 100 | ns    |            |

| 121                     | Tckrf                        | Clock out rise time and fall time | PIC16 <b>C</b> 65  |   | — | 45  | ns    |            |

|                         |                              | (Master Mode)                     | PIC16 <b>LC</b> 65 | - | — | 50  | ns    |            |

| 122 Tdtrf Data out rise |                              | Data out rise time and fall time  | PIC16 <b>C</b> 65  | _ | — | 45  | ns    |            |

|                         |                              |                                   | PIC16LC65          | _ | — | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

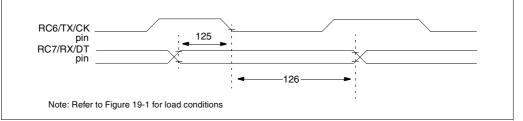

#### FIGURE 19-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Max | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  |      |     | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 22.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 22-2: EXTERNAL CLOCK TIMING

#### TABLE 22-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|--------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKIN Frequency         | DC  |      | 4      | MHz   | XT and RC osc mode |

|              |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|              |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|              |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|              |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|              |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|              |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|              |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|              |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1            | Tosc  | External CLKIN Period            | 250 |      | —      | ns    | XT and RC osc mode |

|              |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|              |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode        |

|              |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|              |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3*           | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|              | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|              |       |                                  | 15  | —    | —      | ns    | HS oscillator      |

| 4*           | TosR, | External Clock in (OSC1) Rise or | —   |      | 25     | ns    | XT oscillator      |

|              | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|              |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

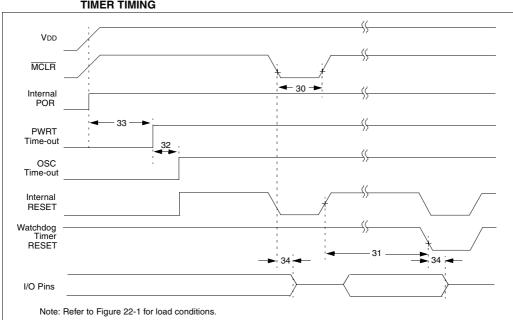

# FIGURE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

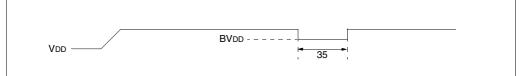

#### FIGURE 22-5: BROWN-OUT RESET TIMING

# TABLE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†      | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2   | —         |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | -   | 1024 Tosc |     | _     | TOSC = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or WDT reset      |     | _         | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100 | —         |     | μs    | $V$ DD $\leq$ BVDD (D005) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C6X

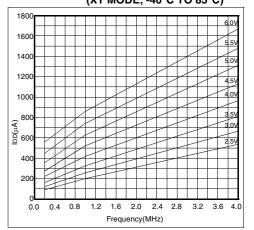

#### FIGURE 23-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

# Data based on matrix samples. See first page of this section for details.

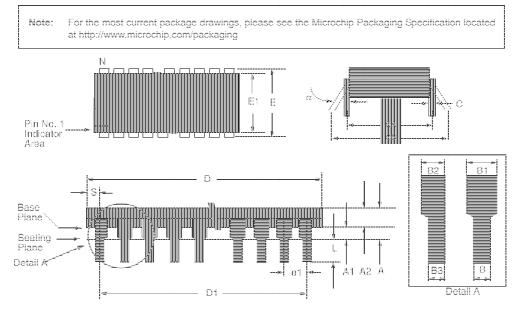

# 24.2 28-Lead Plastic Dual In-line (300 mil) (SP)

|        |        | Package Gro | up: Plastic Dual | In-Line (PLA) |        |           |

|--------|--------|-------------|------------------|---------------|--------|-----------|

|        |        | Millimeters |                  |               | Inches |           |

| Symbol | Min    | Мах         | Notes            | Min           | Мах    | Notes     |

| α      | 0°     | 10°         |                  | 0°            | 10°    |           |

| А      | 3.632  | 4.572       |                  | 0.143         | 0.180  |           |

| A1     | 0.381  | -           |                  | 0.015         | -      |           |

| A2     | 3.175  | 3.556       |                  | 0.125         | 0.140  |           |

| В      | 0.406  | 0.559       |                  | 0.016         | 0.022  |           |

| B1     | 1.016  | 1.651       | Typical          | 0.040         | 0.065  | Typical   |

| B2     | 0.762  | 1.016       | 4 places         | 0.030         | 0.040  | 4 places  |

| B3     | 0.203  | 0.508       | 4 places         | 0.008         | 0.020  | 4 places  |

| С      | 0.203  | 0.331       | Typical          | 0.008         | 0.013  | Typical   |

| D      | 34.163 | 35.179      |                  | 1.385         | 1.395  |           |

| D1     | 33.020 | 33.020      | Reference        | 1.300         | 1.300  | Reference |

| E      | 7.874  | 8.382       |                  | 0.310         | 0.330  |           |

| E1     | 7.112  | 7.493       |                  | 0.280         | 0.295  |           |

| e1     | 2.540  | 2.540       | Typical          | 0.100         | 0.100  | Typical   |

| eA     | 7.874  | 7.874       | Reference        | 0.310         | 0.310  | Reference |

| eB     | 8.128  | 9.652       |                  | 0.320         | 0.380  |           |

| L      | 3.175  | 3.683       |                  | 0.125         | 0.145  |           |

| Ν      | 28     | 28          |                  | 28            | 28     |           |

| S      | 0.584  | 1.220       |                  | 0.023         | 0.048  |           |

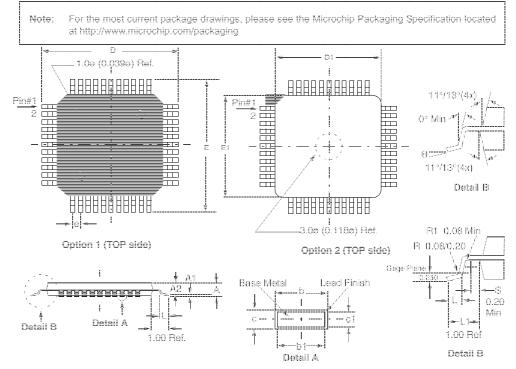

#### 24.13 44-Lead Plastic Surface Mount (TQFP 10x10 mm Body 1.0/0.10 mm Lead Form) (TQ)

| Package Group: Plastic TQFP |             |            |       |        |       |       |  |

|-----------------------------|-------------|------------|-------|--------|-------|-------|--|

|                             | Millimeters |            |       | Inches |       |       |  |

| Symbol                      | Min         | Max        | Notes | Min    | Max   | Notes |  |

| A                           | 1.00        | 1.20       |       | 0.039  | 0.047 |       |  |

| A1                          | 0.05        | 0.15       |       | 0.002  | 0.006 |       |  |

| A2                          | 0.95        | 1.05       |       | 0.037  | 0.041 |       |  |

| D                           | 11.75       | 12.25      |       | 0.463  | 0.482 |       |  |

| D1                          | 9.90        | 10.10      |       | 0.390  | 0.398 |       |  |

| E                           | 11.75       | 12.25      |       | 0.463  | 0.482 |       |  |

| E1                          | 9.90        | 10.10      |       | 0.390  | 0.398 |       |  |

| L                           | 0.45        | 0.75       |       | 0.018  | 0.030 |       |  |

| е                           | 0.80 BSC    |            |       | 0.03   | I BSC |       |  |

| b                           | 0.30        | 0.45       |       | 0.012  | 0.018 |       |  |

| b1                          | 0.30        | 0.40       |       | 0.012  | 0.016 |       |  |

| С                           | 0.09        | 0.20       |       | 0.004  | 0.008 |       |  |

| c1                          | 0.09        | 0.16       |       | 0.004  | 0.006 |       |  |

| Ν                           | 44          | 44         |       | 44     | 44    |       |  |

| Θ                           | 0°          | <b>7</b> ° |       | 0°     | 7°    |       |  |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

3: This outline conforms to JEDEC MS-026.

# **APPENDIX C: WHAT'S NEW**

Added PIC16CR63 and PIC16CR65 devices.

Added PIC16C66 and PIC16C67 devices. The PIC16C66/67 devices have 368 bytes of data memory distributed in 4 banks and 8K of program memory in 4 pages. These two devices have an enhanced SPI that supports both clock phase and polarity. The USART has been enhanced.

When upgrading to the PIC16C66/67 please note that the upper 16 bytes of data memory in banks 1,2, and 3 are mapped into bank 0. This may require relocation of data memory usage in the user application code.

Q-cycles for instruction execution were added to Section 14.0 Instruction Set Summary.

# **APPENDIX D: WHAT'S CHANGED**

Minor changes, spelling and grammatical changes.

Divided SPI section into SPI for the PIC16C66/67 (Section 11.3) and SPI for all other devices (Section 11.2).

Added the following note for the USART. This applies to all devices except the PIC16C66 and PIC16C67.

For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

# **APPENDIX E: REVISION E**

January 2013 - Added a note to each package drawing.

## F.3 PIC16C15X Family of Devices

|             |                                         | PIC16C154                           | PIC16CR154                          | PIC16C156                           | PIC16CR156                          | PIC16C158                           | PIC16CR158                          |

|-------------|-----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  |

|             | EPROM Program Memory<br>(x12 words)     | 512                                 | —                                   | 1K                                  | —                                   | 2К                                  | —                                   |

| Memory      | ROM Program Memory<br>(x12 words)       | _                                   | 512                                 | _                                   | 1K                                  | —                                   | 2К                                  |

|             | RAM Data Memory (bytes)                 | 25                                  | 25                                  | 25                                  | 25                                  | 73                                  | 73                                  |

| Peripherals | Timer Module(s)                         | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | I/O Pins                                | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  |

|             | Voltage Range (Volts)                   | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             |

| Features    | Number of Instructions                  | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

|             | Packages                                | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

## F.4 PIC16C5X Family of Devices

|             |                                         | PIC16C52            | PIC16C54                            | PIC16C54A                           | PIC16CR54A                          | PIC16C55                     | PIC16C56                            |

|-------------|-----------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------|-------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 4                   | 20                                  | 20                                  | 20                                  | 20                           | 20                                  |

|             | EPROM Program Memory<br>(x12 words)     | 384                 | 512                                 | 512                                 | —                                   | 512                          | 1K                                  |

| Memory      | ROM Program Memory<br>(x12 words)       | —                   | —                                   | —                                   | 512                                 | -                            | —                                   |

|             | RAM Data Memory (bytes)                 | 25                  | 25                                  | 25                                  | 25                                  | 24                           | 25                                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                                | TMR0                                | TMR0                                | TMR0                         | TMR0                                |

|             | I/O Pins                                | 12                  | 12                                  | 12                                  | 12                                  | 20                           | 12                                  |

|             | Voltage Range (Volts)                   | 2.5-6.25            | 2.5-6.25                            | 2.0-6.25                            | 2.0-6.25                            | 2.5-6.25                     | 2.5-6.25                            |

| Features    | Number of Instructions                  | 33                  | 33                                  | 33                                  | 33                                  | 33                           | 33                                  |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC,<br>SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

|            |                                         | PIC16C57                     | PIC16CR57B                | PIC16C58A                        | PIC16CR58A                       |

|------------|-----------------------------------------|------------------------------|---------------------------|----------------------------------|----------------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz) | 20                           | 20                        | 20                               | 20                               |

|            | EPROM Program Memory<br>(x12 words)     | 2К                           | -                         | 2К                               | _                                |

| Memory     | ROM Program Memory<br>(x12 words)       | -                            | 2К                        | —                                | 2К                               |

|            | RAM Data Memory (bytes)                 | 72                           | 72                        | 73                               | 73                               |

| Peripheral | Timer Module(s)                         | TMR0                         | TMR0                      | TMR0                             | TMR0                             |

|            | I/O Pins                                | 20                           | 20                        | 12                               | 12                               |

|            | Voltage Range (Volts)                   | 2.5-6.25                     | 2.5-6.25                  | 2.0-6.25                         | 2.5-6.25                         |

| Features   | Number of Instructions                  | 33                           | 33                        | 33                               | 33                               |

|            | Packages                                | 28-pin DIP,<br>SOIC,<br>SSOP | 28-pin DIP, SOIC,<br>SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer (except PIC16C52), selectable code protect and high I/O current capability.

# **PIN COMPATIBILITY**

Devices that have the same package type and VDD, VSs and  $\overline{\text{MCLR}}$  pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

| Pin Compatible Devices                                                                                                                                                                                                                                                                                                                                                                      | Package           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PIC12C508, PIC12C509, PIC12C671, PIC12C672                                                                                                                                                                                                                                                                                                                                                  | 8-pin             |

| PIC16C154, PIC16CR154, PIC16C156,<br>PIC16CR156, PIC16C158, PIC16CR158,<br>PIC16C52, PIC16C54, PIC16C54A,<br>PIC16C56,<br>PIC16C58A, PIC16CR58A,<br>PIC16C554, PIC16CR58A,<br>PIC16C554, PIC16C556, PIC16C558<br>PIC16C620, PIC16C621, PIC16C622<br>PIC16C641, PIC16C642, PIC16C661, PIC16C662<br>PIC16C710, PIC16C71, PIC16C711, PIC16C715<br>PIC16F83, PIC16CR83,<br>PIC16F84A, PIC16CR84 | 18-pin,<br>20-pin |

| PIC16C55, PIC16C57, PIC16CR57B                                                                                                                                                                                                                                                                                                                                                              | 28-pin            |

| PIC16CR62, PIC16C62A, PIC16C63, PIC16CR63,<br>PIC16C66, PIC16C72, PIC16C73A, PIC16C76                                                                                                                                                                                                                                                                                                       | 28-pin            |

| PIC16CR64, PIC16C64A, PIC16C65A,<br>PIC16CR65, PIC16C67, PIC16C74A, PIC16C77                                                                                                                                                                                                                                                                                                                | 40-pin            |

| PIC17CR42, PIC17C42A,<br>PIC17C43, PIC17CR43, PIC17C44                                                                                                                                                                                                                                                                                                                                      | 40-pin            |