# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                            |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-04-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 GENERAL DESCRIPTION

The PIC16CXX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C61** device has 36 bytes of RAM and 13 I/O pins. In addition a timer/counter is available.

The **PIC16C62/62A/R62** devices have 128 bytes of RAM and 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI<sup>TM</sup>) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus.

The **PIC16C63/R63** devices have 192 bytes of RAM, while the **PIC16C66** has 368 bytes. All three devices have 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit ( $I^2C$ ) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also know as a Serial Communications Interface or SCI.

The **PIC16C64/64A/R64** devices have 128 bytes of RAM and 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. An 8-bit Parallel Slave Port is also provided.

The **PIC16C65/65A/R65** devices have 192 bytes of RAM, while the **PIC16C67** has 368 bytes. All four devices have 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmit-

ter (USART) is also known as a Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is also provided.

The PIC16C6X device family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers a power saving mode. The user can wake the chip from SLEEP through several external and internal interrupts, and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C6X family fits perfectly in applications ranging from high-speed automotive and appliance control to low-power remote sensors, keyboards and telecom processors. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use, and I/O flexibility make the PIC16C6X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions, and co-processor applications).

#### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16CXX family of devices (Appendix B).

#### 1.2 Development Support

PIC16C6X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 15.0 for more details about Microchip's development tools.

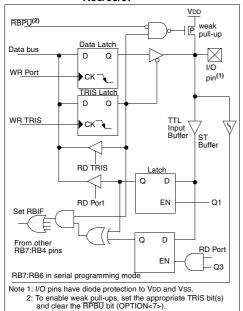

#### FIGURE 5-4: BLOCK DIAGRAM OF THE RB7:RB4 PINS FOR PIC16C62A/63/R63/64A/65A/ R65/66/67

#### TABLE 5-3: PORTB FUNCTIONS

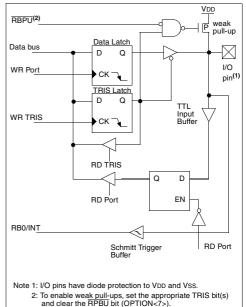

#### FIGURE 5-5: BLOCK DIAGRAM OF THE RB3:RB0 PINS

| TABLE 0 0. |      |                       | •                                                                                                                   |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| Name       | Bit# | Buffer Type           | Function                                                                                                            |

| RB0/INT    | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1        | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2        | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3        | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4        | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5        | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6        | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7        | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7                             | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------------|--------|-----------------------------------|--------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h, 106h     | PORTB  | RB7                               | RB6    | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuuu                |

| 86h, 186h     | TRISB  | ISB PORTB Data Direction Register |        |       |       |       |       |       |       |                          | 1111 1111                 |

| 81h, 181h     | OPTION | RBPU                              | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| I a source of |        |                                   |        |       |       |       |       |       |       |                          |                           |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

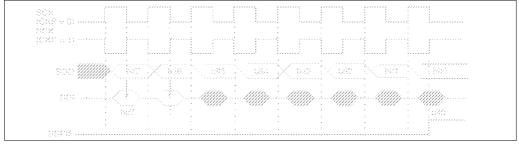

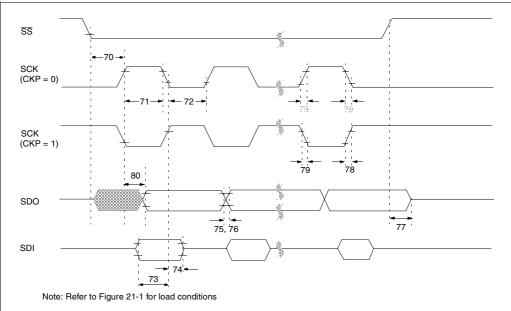

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

| TABLE 11-1: REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Name    | Bit 7                                                        | Bit 6                                                                                                                               | Bit 5                                                                                                                                                                                                                                | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                        | Value on:<br>POR,<br>BOR                                                                                                                                                                                                                                                                                                                                                                                            | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCON  | GIE                                                          | PEIE                                                                                                                                | TOIE                                                                                                                                                                                                                                 | INTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RBIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RBIF                                                                                                                                                                                                                                                                                                                                                                                                         | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIR1    | PSPIF <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIF <sup>(1)</sup>                                                                                                                                                                                                                  | TXIF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIE1    | PSPIE <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIE <sup>(1)</sup>                                                                                                                                                                                                                  | TXIE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR1IE                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPBUF  | Synchrono                                                    | ous Serial                                                                                                                          | Port Rece                                                                                                                                                                                                                            | ive Buffer/                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                           | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPCON  | WCOL                                                         | SSPOV                                                                                                                               | SSPEN                                                                                                                                                                                                                                | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPM3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPM0                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TRISA   | _                                                            |                                                                                                                                     | PORTA Da                                                                                                                                                                                                                             | ta Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              | 11 1111                                                                                                                                                                                                                                                                                                                                                                                                             | 11 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TRISC   | PORTC D                                                      | PORTC Data Direction Register                                                                                                       |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                     | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPSTAT | —                                                            | _                                                                                                                                   | D/A                                                                                                                                                                                                                                  | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BF                                                                                                                                                                                                                                                                                                                                                                                                           | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                             | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | INTCON<br>PIR1<br>PIE1<br>SSPBUF<br>SSPCON<br>TRISA<br>TRISC | INTCON GIE<br>PIR1 PSPIF <sup>(2)</sup><br>PIE1 PSPIE <sup>(2)</sup><br>SSPBUF Synchronc<br>SSPCON WCOL<br>TRISA —<br>TRISC PORTC D | INTCON     GIE     PEIE       PIR1     PSPIF <sup>(2)</sup> (3)       PIE1     PSPIE <sup>(2)</sup> (3)       SSPBUF     Synchronus Serial       SSPCON     WCOL     SSPOV       TRISA     —     —       TRISC     PORTC Data Direct | INTCON         GIE         PEIE         TOIE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> SSPBUF         Synchron-us Serial Port Rece         SSPCON         WCOL         SSPEN           TRISA         —         —         PORTA Da         PORTA Da           TRISC         PORTC Data Direction Regist         Portal Direction Regist         Portal Direction Regist | INTCON         GIE         PEIE         TOIE         INTE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> PIE1         PSPIF <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIF <sup>(1)</sup> PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPBUF         Synchronous         Serial         Port Receive Bufferr           SSPCON         WCOL         SSPOV         SSPEN         CKP           TRISA         —         —         PORTA Data Direction           TRISC         PORTC Data Direction Register         PORTA | INTCON         GIE         PEIE         TOIE         INTE         RBIE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIF           PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIF           SSPBUF         Synchron-US         Serial         Port Receive Buffer/Transmit         SSPRON           SSPCON         WCOL         SSPOV         SSPEN         CKP         SSPM3           TRISA         —         —         PORTA Data Direction Register         TRISC | INTCON     GIE     PEIE     TOIE     INTE     RBIE     TOIF       PIR1     PSPIF <sup>(2)</sup> (3)     RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIF     CCP1IF       PIE1     PSPIE <sup>(2)</sup> (3)     RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIE     CCP1IF       SSPBUF     Synchronus Serial Port Receive Buffer/Transmit Register     SSPR0     WCOL     SSPOV     SSPEN     CKP     SSPM3     SSPM2       TRISA     —     —     PORTA Data Direction Register     TRISC     PORTC Data Direction Register | INTCONGIEPEIETOIEINTERBIETOIFINTFPIR1PSPIF <sup>(2)</sup> <sup>(3)</sup> RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIFCCP1IFTMR2IFPIE1PSPIE <sup>(2)</sup> <sup>(3)</sup> RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIECCP1IETMR2IFSSPBUFSynchronus Serial Port Receive Buffer/Transmit RegisterSSPCONWCOLSSPOVSSPENCKPSSPM3SSPM2SSPM1TRISA——PORTA Data Direction RegisterTRISCPORTC Data Direction Register | INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1PSPIF(2)(3)RCIF(1)TXIF(1)SSPIFCCP1IFTMR2IFTMR1IFPIE1PSPIE(2)(3)RCIE(1)TXIE(1)SSPIECCP1IETMR2IETMR1IESSPBUFSynchron-usSerial Port Receive Buffer/Transmit RegisterSSPR0SSPM2SSPM1SSPM0SSPCONWCOLSSPOVSSPENCKPSSPM3SSPM2SSPM1SSPM0TRISA——PORTA Data Direction RegisterFUNCTION RegisterFUNCTION RegisterTRISCPORTC Data Direction RegisterFUNCTION RegisterFUNCTION Register | Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR,<br>BOR           INTCON         GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 000x           PIR1         PSPIF <sup>(2)</sup> <sup>(3)</sup> RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIE         CCP1IE         TMR2IF         TMR1IE         0000 0000           PIE1         PSPIE <sup>(2)</sup> <sup>(3)</sup> RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIE         CCP1IE         TMR2IF         TMR1IE         0000 0000           SSPBUF         Synchro |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

Note 1: These bits are associated with the USART which is implemented on the PIC16C63/R63/65/65A/R65 only.

2: PSPIF and PSPIE are reserved on the PIC16C62/62A/R62/63/R63, always maintain these bits clear.

3: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### 11.3.1 SSP MODULE IN SPI MODE FOR PIC16C66/67

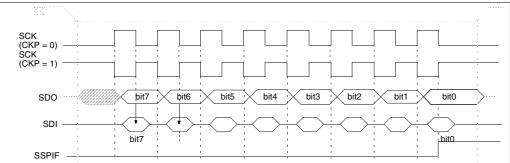

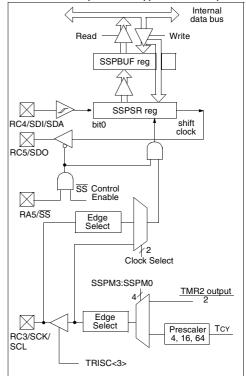

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device. MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

#### EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C66/67)

| LOOP | BCF<br>BSF<br>BTFSS | STATUS,<br>STATUS,<br>SSPSTAT, | RP0 | ;Specify Bank 1<br>;<br>;Has data been<br>;received<br>;(transmit<br>;complete)? |

|------|---------------------|--------------------------------|-----|----------------------------------------------------------------------------------|

|      | GOTO                | LOOP                           |     | ;No                                                                              |

|      | BCF                 | STATUS,                        | RP0 | ;Specify Bank 0                                                                  |

|      | MOVF                | SSPBUF,                        | W   | ;W reg = contents<br>; of SSPBUF                                                 |

|      | MOVWF               | RXDATA                         |     | ;Save in user RAM                                                                |

|      | MOVF                | TXDATA,                        | W   | ;W reg = contents<br>; of TXDATA                                                 |

|      | MOVWF               | SSPBUF                         |     | ;New data to xmit                                                                |

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

#### FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C66/67)

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                 | Name    | Bit 7                            | Bit 6              | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|-------------------------|---------|----------------------------------|--------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                              | PEIE               | TOIE                   | INTE       | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                     | PIR1    | PSPIF <sup>(1)</sup>             | (2)                | RCIF                   | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                     | PIE1    | PSPIE <sup>(1)</sup>             | (2)                | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                     | SSPBUF  | Synchrono                        | us Serial          | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                     | SSPADD  | Synchrono                        | us Serial          | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                     | SSPCON  | WCOL                             | SSPOV              | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                     | SSPSTAT | SMP <sup>(3)</sup>               | CKE <sup>(3)</sup> | D/A                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                     | TRISC   | SC PORTC Data Direction register |                    |                        |            |            |          |        |        |                         | 1111 1111                 |

#### TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

3: The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'.

#### 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                      | R/W-0                       | R/W-0        | U-0        | R/W-0    | R-1  | R/W-0 |                                                                                      |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|------------|----------|------|-------|--------------------------------------------------------------------------------------|--|--|--|

| CSRC   | TX9                                                                                                                                                                                                                                                                                                        | TXEN                        | SYNC         | —          | BRGH     | TRMT | TX9D  | R = Readable bit                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                                                            |                             |              |            |          |      | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7: | CSRC: Clo                                                                                                                                                                                                                                                                                                  | ck Source                   | Select bit   |            |          |      |       | <u>,</u>                                                                             |  |  |  |

|        | Asynchron<br>Don't care                                                                                                                                                                                                                                                                                    | <u>ous mode</u>             |              |            |          |      |       |                                                                                      |  |  |  |

|        | <u>Synchronous mode</u><br>1 = Master mode (Clock generated internally from BRG)<br>0 = Slave mode (Clock from external source)                                                                                                                                                                            |                             |              |            |          |      |       |                                                                                      |  |  |  |

| bit 6: | <b>TX9</b> : 9-bit 1 = Selects 0 = Selects                                                                                                                                                                                                                                                                 | 9-bit trans                 | smission     |            |          |      |       |                                                                                      |  |  |  |

| bit 5: | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SRE                                                                                                                                                                                                                                                | iit enabled<br>iit disabled |              | EN in SYI  | NC mode. |      |       |                                                                                      |  |  |  |

| bit 4: | <b>SYNC</b> : US<br>1 = Synchr<br>0 = Asynch                                                                                                                                                                                                                                                               | onous mod                   | le           |            |          |      |       |                                                                                      |  |  |  |

| bit 3: | Unimplem                                                                                                                                                                                                                                                                                                   | ented: Re                   | ad as '0'    |            |          |      |       |                                                                                      |  |  |  |

| bit 2: | BRGH: Hig                                                                                                                                                                                                                                                                                                  | h Baud Ra                   | ate Select b | it         |          |      |       |                                                                                      |  |  |  |

|        | Asynchron<br>1 = High sp                                                                                                                                                                                                                                                                                   |                             |              |            |          |      |       |                                                                                      |  |  |  |

|        | Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67. |                             |              |            |          |      |       |                                                                                      |  |  |  |

|        | 0 = Low sp                                                                                                                                                                                                                                                                                                 | eed                         |              |            |          |      |       |                                                                                      |  |  |  |

|        | Synchrono<br>Unused in                                                                                                                                                                                                                                                                                     |                             |              |            |          |      |       |                                                                                      |  |  |  |

| bit 1: | <b>TRMT</b> : Trai<br>1 = TSR er<br>0 = TSR fu                                                                                                                                                                                                                                                             | npty                        | Register S   | tatus bit  |          |      |       |                                                                                      |  |  |  |

| bit 0: | <b>TX9D</b> : 9th                                                                                                                                                                                                                                                                                          | bit of trans                | mit data. C  | an be pari | ty bit.  |      |       |                                                                                      |  |  |  |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

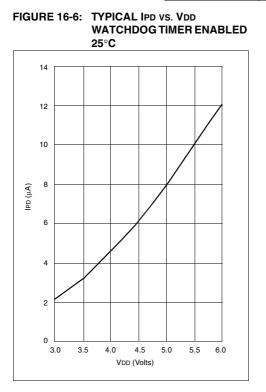

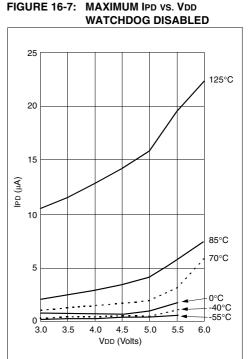

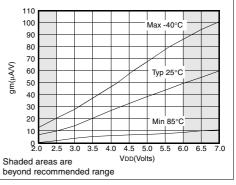

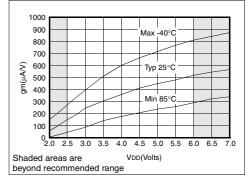

Data based on matrix samples. See first page of this section for details.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

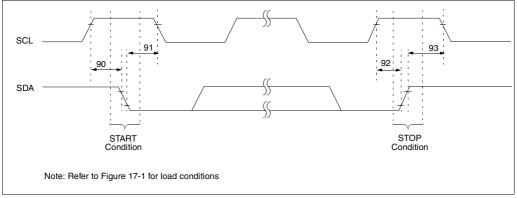

#### FIGURE 17-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

#### TABLE 17-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                                           |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | -     | Only relevant for repeated START                     |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | _   | ns    | condition                                            |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   |       | After this period the first clock pulse is generated |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   | ns    |                                                      |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | _   | _   |       |                                                      |

|                  |         | Setup time      | 400 kHz mode | 600  |     | _   | ns    |                                                      |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | _   | _   |       |                                                      |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | ns    |                                                      |

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

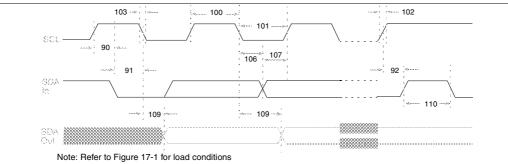

#### FIGURE 17-10: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 17-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym                | Characteristic         |              | Min        | Max  | Units | Conditions                                       |