Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-MQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-04-pq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data may be fetched from the same memory using the same bus. Separating program and data busses further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C61 addresses 1K x 14 of program memory. The PIC16C62/62A/R62/64/64A/R64 address 2K x 14 of program memory, and the PIC16C63/R63/65/65A/R65 devices address 4K x 14 of program memory. The PIC16C66/67 address 8K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of "special optimal situations" makes programming with the PIC16CXX simple yet efficient, thus significantly reducing the learning curve.

The PIC16CXX device contains an 8-bit ALU and working register (W). The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending upon the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. Bits C and DC operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

| Address               | Name   | Bit 7        | Bit 6          | Bit 5         | Bit 4         | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|-----------------------|--------|--------------|----------------|---------------|---------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 2                | •      |              |                |               |               | •            |                 |               | •         |                          |                                                |

| 100h <sup>(1)</sup>   | INDF   | Addressing   | this location  | uses conter   | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 101h                  | TMR0   | Timer0 mo    | dule's registe | r             |               |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 102h <sup>(1)</sup>   | PCL    | Program C    | ounter's (PC)  | Least Signi   | ficant Byte   |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 103h <sup>(1)</sup>   | STATUS | IRP          | RP1            | RP0           | TO            | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 104h <sup>(1)</sup>   | FSR    | Indirect dat | a memory ac    | Idress pointe | er            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 105h                  | _      | Unimpleme    | ented          |               |               |              |                 |               |           | _                        | _                                              |

| 106h                  | PORTB  | PORTB Da     | ta Latch whe   | n written: PO | ORTB pins wh  | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 107h                  | _      | Unimpleme    | ented          |               |               |              |                 |               |           | _                        | _                                              |

| 108h                  | _      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 109h                  | _      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 10Ah <sup>(1,2)</sup> | PCLATH | _            | _              | 1             | Write Buffer  | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 10Bh <sup>(1)</sup>   | INTCON | GIE          | PEIE           | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 10Ch-<br>10Fh         | _      | Unimpleme    | ented          |               |               |              |                 |               |           | _                        | _                                              |

| Bank 3                |        |              |                |               |               |              |                 |               |           |                          |                                                |

| 180h <sup>(1)</sup>   | INDF   | Addressing   | this location  | uses conter   | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 181h                  | OPTION | RBPU         | INTEDG         | T0CS          | T0SE          | PSA          | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 182h <sup>(1)</sup>   | PCL    | Program C    | ounter's (PC)  | Least Sigr    | nificant Byte |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 183h <sup>(1)</sup>   | STATUS | IRP          | RP1            | RP0           | TO            | PD           | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 184h <sup>(1)</sup>   | FSR    | Indirect dat | a memory ac    | Idress pointe | er            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 185h                  | _      | Unimpleme    | ented          |               |               |              |                 |               |           | _                        | _                                              |

| 186h                  | TRISB  | PORTB Da     | ta Direction F | Register      |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 187h                  | _      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 188h                  | _      | Unimpleme    | ented          |               |               |              |                 |               |           | _                        | _                                              |

| 189h                  | _      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 18Ah <sup>(1,2)</sup> | PCLATH | _            | _              | -             | Write Buffer  | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 18Bh <sup>(1)</sup>   | INTCON | GIE          | PEIE           | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 18Ch-<br>19Fh         | _      | Unimpleme    |                |               | anands on     |              |                 |               |           | _                        | _                                              |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'.

Shaded locations are unimplemented, read as '0'.

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

- 5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

- 6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

Note 1: These registers can be addressed from any bank.

<sup>2:</sup> The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

# FIGURE 4-13: PIE1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 8Ch)

| R/W-0   | R/W-0                                   | R/W-0       | R/W-0        | R/W-0         | R/W-0     | R/W-0  | R/W-0  |                                                                            |

|---------|-----------------------------------------|-------------|--------------|---------------|-----------|--------|--------|----------------------------------------------------------------------------|

| _       | _                                       | RCIE        | TXIE         | SSPIE         | CCP1IE    | TMR2IE | TMR1IE | R = Readable bit                                                           |

| t7      |                                         |             |              |               |           |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' n = Value at POR reset |

| it 7-6: | Reserved:                               | Always ma   | intain thes  | e bits clear. |           |        |        |                                                                            |

| it 5:   | RCIE: USA<br>1 = Enable<br>0 = Disable  | s the USAF  | RT receive i | nterrupt      |           |        |        |                                                                            |

| it 4:   | TXIE: USA<br>1 = Enable<br>0 = Disable  | s the USAF  | RT transmit  | interrupt     |           |        |        |                                                                            |

| it 3:   | SSPIE: Syr<br>1 = Enable<br>0 = Disable | s the SSP i | nterrupt     | Interrupt Er  | nable bit |        |        |                                                                            |

| it 2:   | CCP1IE: C<br>1 = Enable<br>0 = Disable  | s the CCP1  | interrupt    | oit           |           |        |        |                                                                            |

| it 1:   | TMR2IE: T<br>1 = Enable<br>0 = Disable  | s the TMR2  | to PR2 ma    | tch interru   | ot        |        |        |                                                                            |

| it 0:   | TMR1IE: T<br>1 = Enable                 | s the TMR1  |              | nterrupt      | t         |        |        |                                                                            |

# FIGURE 4-14: PIE1 REGISTER FOR PIC16C64/64A/R64 (ADDRESS 8Ch)

| R/W-0    | R/W-0                                     | U-0        | U-0           | R/W-0                     | R/W-0         | R/W-0  | R/W-0  |                                                                                                                |

|----------|-------------------------------------------|------------|---------------|---------------------------|---------------|--------|--------|----------------------------------------------------------------------------------------------------------------|

| PSPIE    | _                                         | _          | _             | SSPIE                     | CCP1IE        | TMR2IE | TMR1IE | R = Readable bit                                                                                               |

| oit7     |                                           |            |               |                           |               |        | bit0   | <ul><li>W = Writable bit</li><li>U = Unimplemented bit, read as '0'</li><li>- n = Value at POR reset</li></ul> |

| bit 7:   | PSPIE: Par<br>1 = Enables<br>0 = Disable  | the PSP i  | ead/write i   | nterrupt                  | rupt Enable b | it     |        |                                                                                                                |

| bit 6:   | Reserved:                                 | Always ma  | intain this l | bit clear.                |               |        |        |                                                                                                                |

| bit 5-4: | Unimpleme                                 | ented: Rea | ıd as '0'     |                           |               |        |        |                                                                                                                |

| bit 3:   | SSPIE: Syn<br>1 = Enables<br>0 = Disables | the SSP i  | nterrupt      | Interrupt Er              | nable bit     |        |        |                                                                                                                |

| bit 2:   | CCP1IE: C0<br>1 = Enables<br>0 = Disables | the CCP1   | interrupt     | bit                       |               |        |        |                                                                                                                |

| bit 1:   | TMR2IE: TN<br>1 = Enables<br>0 = Disables | the TMR2   | to PR2 m      | atch interru <sub>l</sub> | pt            |        |        |                                                                                                                |

| bit 0:   | TMR1IE: TM<br>1 = Enables<br>0 = Disables | the TMR    | overflow i    | nterrupt                  | t             |        |        |                                                                                                                |

# FIGURE 4-19: PIR1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 0Ch)

| R/W-0 R/W-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0  PSPIF — RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF  bit7 bit7 bit0  PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place bit 6: Reserved: Always maintain this bit clear. bit 5: RCIF: USART Receive Interrupt Flag bit |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit7 bit0 W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset  bit 7: PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place  bit 6: Reserved: Always maintain this bit clear.  bit 5: RCIF: USART Receive Interrupt Flag bit           |  |

| bit 7: PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place bit 6: Reserved: Always maintain this bit clear. bit 5: RCIF: USART Receive Interrupt Flag bit                                                                                                     |  |

| bit 5: RCIF: USART Receive Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                        |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                    |  |

| <ul><li>1 = The USART receive buffer is full (cleared by reading RCREG)</li><li>0 = The USART receive buffer is empty</li></ul>                                                                                                                                                                                                                                                      |  |

| bit 4: TXIF: USART Transmit Interrupt Flag bit  1 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is full                                                                                                                                                                                                                          |  |

| bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit  1 = The transmission/reception is complete (must be cleared in software)  0 = Waiting to transmit/receive                                                                                                                                                                                                                  |  |

| bit 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode                                                        |  |

| bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                   |  |

| bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software) 0 = No TMR1 register overflow occurred                                                                                                                                                                                                                             |  |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 11.4.4 MULTI-MASTER

The I<sup>2</sup>C protocol allows a system to have more than one master. This is called multi-master. When two or more masters try to transfer data at the same time, arbitration and synchronization occur.

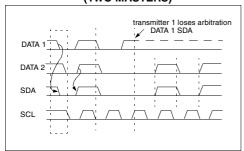

#### 11.4.4.1 ARBITRATION

Arbitration takes place on the SDA line, while the SCL line is high. The master which transmits a high when the other master transmits a low loses arbitration (Figure 11-22), and turns off its data output stage. A master which lost arbitration can generate clock pulses until the end of the data byte where it lost arbitration. When the master devices are addressing the same device, arbitration continues into the data.

FIGURE 11-22: MULTI-MASTER ARBITRATION (TWO MASTERS)

Masters that also incorporate the slave function, and have lost arbitration must immediately switch over to slave-receiver mode. This is because the winning master-transmitter may be addressing it.

Arbitration is not allowed between:

- · A repeated START condition

- · A STOP condition and a data bit

- A repeated START condition and a STOP condition

Care needs to be taken to ensure that these conditions do not occur.

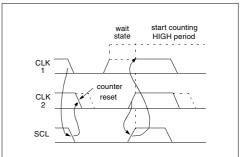

#### 11.2.4.2 Clock Synchronization

Clock synchronization occurs after the devices have started arbitration. This is performed using a wired-AND connection to the SCL line. A high to low transition on the SCL line causes the concerned devices to start counting off their low period. Once a device clock has gone low, it will hold the SCL line low until its SCL high state is reached. The low to high transition of this clock may not change the state of the SCL line, if another device clock is still within its low period. The SCL line is held low by the device with the longest low period. Devices with shorter low periods enter a high waitstate, until the SCL line comes high. When the SCL line comes high, all devices start counting off their high periods. The first device to complete its high period will pull the SCL line low. The SCL line high time is determined by the device with the shortest high period, Figure 11-23.

#### FIGURE 11-23: CLOCK SYNCHRONIZATION

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- · START condition

- · STOP condition

- · Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an  $\overline{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

TABLE 11-5: REGISTERS ASSOCIATED WITH I2C OPERATION

| Address                 | Name    | Bit 7                | Bit 6              | Bit 5                    | Bit 4     | Bit 3      | Bit 2    | Bit 1  | Bit 0  | PC   | e on<br>DR,<br>DR | Value<br>other | on all<br>resets |

|-------------------------|---------|----------------------|--------------------|--------------------------|-----------|------------|----------|--------|--------|------|-------------------|----------------|------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE               | TOIE                     | INTE      | RBIE       | TOIF     | INTF   | RBIF   | 0000 | 000x              | 0000           | 000u             |

| 0Ch                     | PIR1    | PSPIF <sup>(1)</sup> | (2)                | RCIF                     | TXIF      | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 | 0000              | 0000           | 0000             |

| 8Ch                     | PIE1    | PSPIE <sup>(1)</sup> | (2)                | RCIE                     | TXIE      | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 | 0000              | 0000           | 0000             |

| 13h                     | SSPBUF  | Synchrono            | us Serial          | Port Rece                | ive Buffe | r/Transmit | Register |        |        | xxxx | xxxx              | uuuu           | uuuu             |

| 93h                     | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C ı | mode) Ad  | ldress Re  | gister   |        |        | 0000 | 0000              | 0000           | 0000             |

| 14h                     | SSPCON  | WCOL                 | SSPOV              | SSPEN                    | CKP       | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000              | 0000           | 0000             |

| 94h                     | SSPSTAT | SMP <sup>(3)</sup>   | CKE <sup>(3)</sup> | D/Ā                      | Р         | S          | R/W      | UA     | BF     | 0000 | 0000              | 0000           | 0000             |

| 87h                     | TRISC   | PORTC Da             | ta Directi         | on registe               | r         | •          |          |        |        | 1111 | 1111              | 1111           | 1111             |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.} \\ Shaded cells are not used by SSP module in SPI mode.}$

- Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

- 2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

- The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'.

# TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Нz                          | 4 MHz  |            |                             | 3.579545 | MHz        |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

# TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 | 0 MHz      | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | 1.221    | +1.73      | 255                | 1.202  | +0.16      | 207                | 1.202  | +0.16      | 129                | 1.203     | +0.23      | 92                 |

| 2.4         | 2.404    | +0.16      | 129                | 2.404  | +0.16      | 103                | 2.404  | +0.16      | 64                 | 2.380     | -0.83      | 46                 |

| 9.6         | 9.469    | -1.36      | 32                 | 9.615  | +0.16      | 25                 | 9.766  | +1.73      | 15                 | 9.322     | -2.90      | 11                 |

| 19.2        | 19.53    | +1.73      | 15                 | 19.23  | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64     | -2.90      | 5                  |

| 76.8        | 78.13    | +1.73      | 3                  | 83.33  | +8.51      | 2                  | 78.13  | +1.73      | 1                  | NA        | -          | -                  |

| 96          | 104.2    | +8.51      | 2                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 300         | 312.5    | +4.17      | 0                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 500         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| HIGH        | 312.5    | -          | 0                  | 250    | -          | 0                  | 156.3  | -          | 0                  | 111.9     | -          | 0                  |

| LOW         | 1.221    | -          | 255                | 0.977  | -          | 255                | 0.6104 | -          | 255                | 0.437     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra            | ansmit R | egister    |       | •     |        | •      |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Generat  | or Registe | er    |       | •      | •      |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, x =

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                        | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|------------------------------|-----------|--------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>         | (2)       | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                         | RX9       | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 1Ah     | RCREG | USART Re                     | eceive Re | gister | •     |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>         | (2)       | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                         | TX9       | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |           |        |       |       |        |        |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

<sup>2:</sup> PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

<sup>2:</sup> PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

TABLE 13-1: CERAMIC RESONATORS PIC16C61

| Ranges Tested:                                        |                                        |                          |                          |  |  |  |

|-------------------------------------------------------|----------------------------------------|--------------------------|--------------------------|--|--|--|

| Mode                                                  | Freq                                   | OSC1                     | OSC2                     |  |  |  |

| XT                                                    | 455 kHz                                | 47 - 100 pF              | 47 - 100 pF              |  |  |  |

|                                                       | 2.0 MHz<br>4.0 MHz                     | 15 - 68 pF<br>15 - 68 pF | 15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                                    | 8.0 MHz                                | 15 - 68 pF               | 15 - 68 pF               |  |  |  |

|                                                       | 16.0 MHz                               | 10 - 47 pF               | 10 - 47 pF               |  |  |  |

|                                                       | se values are for<br>s at bottom of pa |                          | nce only. See            |  |  |  |

| Resonator                                             | s Used:                                |                          |                          |  |  |  |

| 455 kHz                                               | Panasonic EF                           | O-A455K04B               | ± 0.3%                   |  |  |  |

| 2.0 MHz                                               | Murata Erie CS                         | SA2.00MG                 | ± 0.5%                   |  |  |  |

| 4.0 MHz                                               | Murata Erie CS                         | SA4.00MG                 | ± 0.5%                   |  |  |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT ± 0.5%           |                          |                          |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ± 0.5%                |                                        |                          |                          |  |  |  |

| All resonators used did not have built-in capacitors. |                                        |                          |                          |  |  |  |

TABLE 13-2: CERAMIC RESONATORS PIC16C62/62A/R62/63/R63/64/ 64A/R64/65/65A/R65/66/67

| Ranges Tested: |                                                                         |                                         |                                         |  |  |  |  |

|----------------|-------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|

| Mode           | Freq                                                                    | Freq OSC1                               |                                         |  |  |  |  |

| XT             | 455 kHz<br>2.0 MHz<br>4.0 MHz                                           | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |

| HS             | 8.0 MHz<br>16.0 MHz                                                     | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |  |

|                | These values are for design guidance only. See notes at bottom of page. |                                         |                                         |  |  |  |  |

| Resonator      | rs Used:                                                                |                                         |                                         |  |  |  |  |

| 455 kHz        | Panasonic E                                                             | FO-A455K04B                             | ± 0.3%                                  |  |  |  |  |

| 2.0 MHz        | Murata Erie                                                             | CSA2.00MG                               | $\pm$ 0.5%                              |  |  |  |  |

| 4.0 MHz        | Murata Erie                                                             | CSA4.00MG                               | ± 0.5%                                  |  |  |  |  |

| 8.0 MHz        | Murata Erie CSA8.00MT ± 0.5%                                            |                                         |                                         |  |  |  |  |

| 16.0 MHz       | Murata Erie CSA16.00MX ± 0.5%                                           |                                         |                                         |  |  |  |  |

| All reso       | onators used did                                                        | d not have built-in                     | capacitors.                             |  |  |  |  |

TABLE 13-3: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR FOR PIC16C61

| Mode | Freq           | OSC1              | OSC2            |

|------|----------------|-------------------|-----------------|

| LP   | 32 kHz         | 33 - 68 pF        | 33 - 68 pF      |

|      | 200 kHz        | 15 - 47 pF        | 15 - 47 pF      |

| XT   | 100 kHz        | 47 - 100 pF       | 47 - 100 pF     |

|      | 500 kHz        | 20 - 68 pF        | 20 - 68 pF      |

|      | 1 MHz          | 15 - 68 pF        | 15 - 68 pF      |

|      | 2 MHz          | 15 - 47 pF        | 15 - 47 pF      |

|      | 4 MHz          | 15 - 33 pF        | 15 - 33 pF      |

| HS   | 8 MHz          | 15 - 47 pF        | 15 - 47 pF      |

|      | 20 MHz         | 15 - 47 pF        | 15 - 47 pF      |

| Th   | ese values are | e for design guid | lance only. See |

These values are for design guidance only. See notes at bottom of page.

TABLE 13-4: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR FOR PIC16C62/62A/R62/63/R63/64/64A/R64/65/65A/R65/66/67

| 04A/N04/03/03A/N03/00/07 |                                                                         |                  |                     |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------|------------------|---------------------|--|--|--|--|--|

| Osc Type                 | Crystal<br>Freq                                                         | Cap. Range<br>C1 | Cap.<br>Range<br>C2 |  |  |  |  |  |

| LP                       | 32 kHz                                                                  | 33 pF            | 33 pF               |  |  |  |  |  |

|                          | 200 kHz                                                                 | 15 pF            | 15 pF               |  |  |  |  |  |

| XT                       | 200 kHz                                                                 | 47-68 pF         | 47-68 pF            |  |  |  |  |  |

|                          | 1 MHz                                                                   | 15 pF            | 15 pF               |  |  |  |  |  |

|                          | 4 MHz                                                                   | 15 pF            | 15 pF               |  |  |  |  |  |

| HS                       | 4 MHz                                                                   | 15 pF            | 15 pF               |  |  |  |  |  |

|                          | 8 MHz                                                                   | 15-33 pF         | 15-33 pF            |  |  |  |  |  |

|                          | 20 MHz                                                                  | 15-33 pF         | 15-33 pF            |  |  |  |  |  |

|                          | These values are for design guidance only. See notes at bottom of page. |                  |                     |  |  |  |  |  |

| Crystals Used            |                                                                         |                  |                     |  |  |  |  |  |

| 32 kHz                   | Epson C-001R32.768K-A ± 20 PPM                                          |                  |                     |  |  |  |  |  |

| 200 kHz                  | STD XTL 2                                                               | 00.000KHz        | ± 20 PPM            |  |  |  |  |  |

ECS ECS-10-13-1

ECS ECS-40-20-1

EPSON CA-301 8.000M-C

EPSON CA-301 20.000M-C

- Note 1: Recommended values of C1 and C2 are identical to the ranges tested Table 13-1 and Table 13-2.

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

1 MHz

4 MHz 8 MHz

20 MHz

4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

± 50 PPM

± 50 PPM

± 30 PPM

± 30 PPM

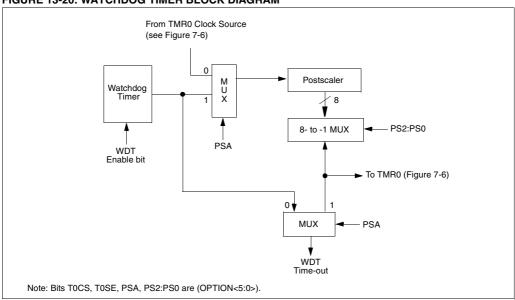

#### 13.7 Watchdog Timer (WDT)

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device reset. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (WDT Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 13.1).

#### 13.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be

assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition

The TO bit in the STATUS register will be cleared upon a WDT time-out.

#### 13.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 13-20: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 13-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 13-1, Figure 13-2, and Figure 13-3 for details of these bits for the specific device.

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$  for extended,

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

0°C ≤ IA ≤ +/0°C for commercial

Operating voltage VDD range as described in DC spec Section 15.1 and Section 15.2.

|              | Occilion 10.2.                             |       |         |      |     |       |                                                                   |  |  |

|--------------|--------------------------------------------|-------|---------|------|-----|-------|-------------------------------------------------------------------|--|--|

| Param<br>No. | Characteristic                             | Sym   | Min     | Тур† | Max | Units | Conditions                                                        |  |  |

|              | Output High Voltage                        |       |         |      |     |       |                                                                   |  |  |

| D090         | I/O ports (Note 3)                         | Vон   | VDD-0.7 | -    | -   | V     | IOH = -3.0 mA,<br>VDD = 4.5V, -40°C to +85°C                      |  |  |

| D090A        |                                            |       | VDD-0.7 | -    | -   | V     | IOH = -2.5 mA,<br>VDD = 4.5V, -40°C to +125°C                     |  |  |

| D092         | OSC2/CLKOUT (RC osc config)                |       | VDD-0.7 | -    | -   | V     | IOH = -1.3 mA,<br>VDD = 4.5V, -40°C to +85°C                      |  |  |

| D092A        |                                            |       | VDD-0.7 | -    | -   | V     | IOH = -1.0 mA,<br>VDD = 4.5V, -40°C to +125°C                     |  |  |

| D150*        | Open-Drain High Voltage                    | Vod   | -       | -    | 14  | V     | RA4 pin                                                           |  |  |

|              | Capacitive Loading Specs on<br>Output Pins |       |         |      |     |       |                                                                   |  |  |

| D100         | OSC2 pin                                   | Cosc2 |         |      | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |

| D101         | All I/O pins and OSC2 (in RC mode)         | Cıo   |         |      | 50  | pF    |                                                                   |  |  |

\* The parameters are characterized but not tested.

DC CHARACTERISTICS

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

- The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

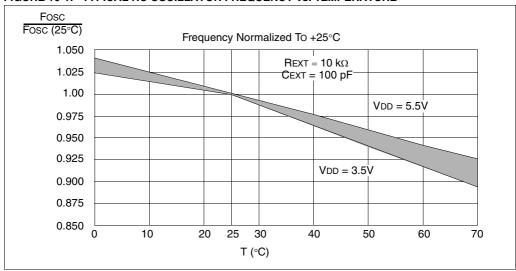

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C61

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

Note: The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean +3σ) and (mean -3σ) respectively where σ is standard deviation.

FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

TABLE 16-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |          |  |

|--------|------|----------------------------|----------|--|

| 20 pF  | 4.7k | 4.52 MHz                   | ± 17.35% |  |

|        | 10k  | 2.47 MHz                   | ± 10.10% |  |

|        | 100k | 290.86 kHz                 | ± 11.90% |  |

| 100 pF | 3.3k | 1.92 MHz                   | ± 9.43%  |  |

|        | 4.7k | 1.48 MHz                   | ± 9.83%  |  |

|        | 10k  | 788.77 kHz                 | ± 10.92% |  |

|        | 100k | 88.11 kHz                  | ± 16.03% |  |

| 300 pF | 3.3k | 726.89 kHz                 | ± 10.97% |  |

|        | 4.7k | 573.95 kHz                 | ± 10.14% |  |

|        | 10k  | 307.31 kHz                 | ± 10.43% |  |

|        | 100k | 33.82 kHz                  | ± 11.24% |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

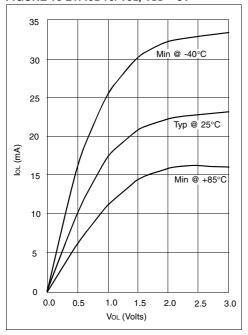

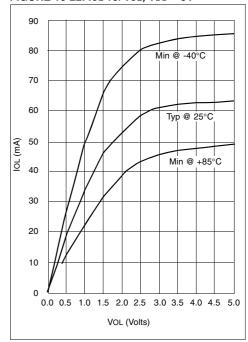

FIGURE 16-21: IOL VS. VOL, VDD = 3V

FIGURE 16-22: IOL VS. VOL, VDD = 5V

TABLE 16-2: INPUT CAPACITANCE\*

| Pin Name    | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

|             | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1/CLKIN  | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| T0CKI       | 3.2                      | 2.8      |  |  |  |

\*All capacitance values are typical at 25°C. A part to part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

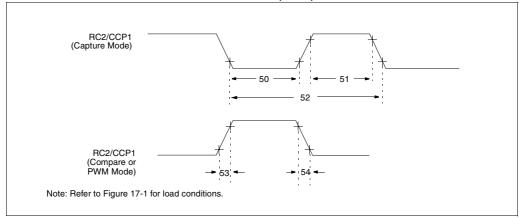

# FIGURE 17-6: CAPTURE/COMPARE/PWM TIMINGS (CCP1)

TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Parameter No. | Sym  | Characteristic        |                   |                       | Min            | Тур† | Max | Units | Conditions                        |

|---------------|------|-----------------------|-------------------|-----------------------|----------------|------|-----|-------|-----------------------------------|

| 50*           | TccL | CCP1                  | No Prescaler      |                       | 0.5Tcy + 20    | _    | _   | ns    |                                   |

|               |      | input low time        | With Prescaler    | PIC16 <b>C</b> 62/64  | 10             | _    | _   | ns    |                                   |

|               |      |                       |                   | PIC16 <b>LC</b> 62/64 | 20             | _    | _   | ns    |                                   |

| 51*           | TccH | CCP1                  | CCP1 No Prescaler |                       | 0.5Tcy + 20    | _    | _   | ns    |                                   |

|               |      | input high time       | With Prescaler    | PIC16 <b>C</b> 62/64  | 10             | _    | _   | ns    |                                   |

|               |      |                       |                   | PIC16 <b>LC</b> 62/64 | 20             | _    | _   | ns    |                                   |

| 52*           | TccP | CCP1 input period     |                   |                       | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53            | TccR | CCP1 output rise time | 9                 | PIC16 <b>C</b> 62/64  |                | 10   | 25  | ns    |                                   |

|               |      |                       |                   |                       | _              | 25   | 45  | ns    |                                   |

| 54            | TccF | CCP1 output fall time |                   | PIC16 <b>C</b> 62/64  | _              | 10   | 25  | ns    |                                   |

|               |      |                       |                   | PIC16 <b>LC</b> 62/64 | _              | 25   | 45  | ns    |                                   |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

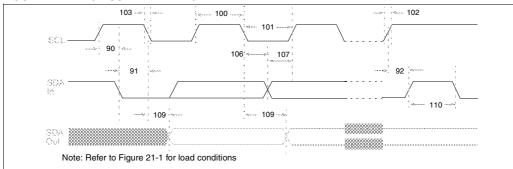

#### FIGURE 21-11: I<sup>2</sup>C BUS DATA TIMING

TABLE 21-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|---------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100*          | THIGH   | Clock high time        | 100 kHz mode | 4.0        | _    | μS    | Device must operate at a mini-<br>mum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a mini-<br>mum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5TcY     | _    |       |                                                  |

| 101*          | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a mini-<br>mum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a mini-<br>mum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102*          | TR      | SDA and SCL rise       | 100 kHz mode | _          | 1000 | ns    |                                                  |

|               |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |

| 103*          | TF      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                                  |

|               |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |

| 90*           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | _    | μS    | Only relevant for repeated                       |

|               |         | setup time             | 400 kHz mode | 0.6        | _    | μS    | START condition                                  |

| 91*           | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μS    | After this period the first clock                |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μS    | pulse is generated                               |

| 106*          | THD:DAT | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                                  |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μS    |                                                  |

| 107*          | Tsu:dat | Data input setup time  | 100 kHz mode | 250        | _    | ns    | Note 2                                           |

|               |         |                        | 400 kHz mode | 100        | _    | ns    | 1                                                |

| 92*           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | _    | μS    |                                                  |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μS    | 1                                                |

| 109*          | TAA     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|               |         | clock                  | 400 kHz mode | _          | _    | ns    |                                                  |

| 110*          | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                        |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | before a new transmission can start              |

|               | Cb      | Bus capacitive loading |              | _          | 400  | pF    |                                                  |

These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

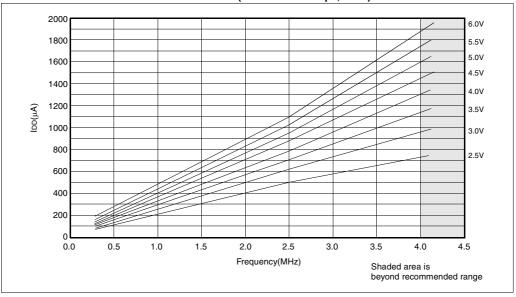

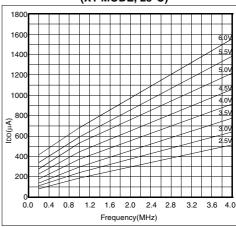

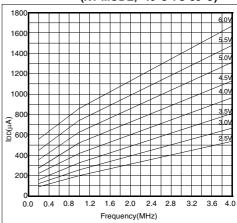

FIGURE 23-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

FIGURE 23-13: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 22 pF, -40°C TO 85°C)

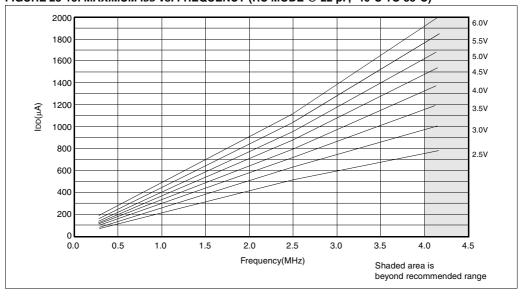

FIGURE 23-25: TYPICAL IDD vs. FREQUENCY (LP MODE, 25°C)

FIGURE 23-26: MAXIMUM IDD vs. FREQUENCY (LP MODE, 85°C TO -40°C)

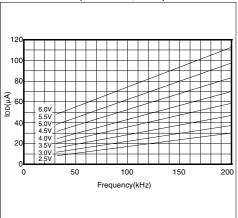

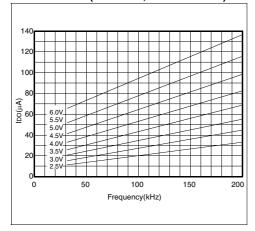

FIGURE 23-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

FIGURE 23-28: MAXIMUM IDD vs. FREQUENCY (XT MODE, -40°C TO 85°C)

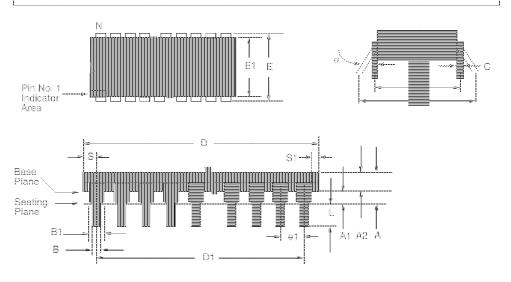

# 24.3 40-Lead Plastic Dual In-line (600 mil) (P)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Plastic Dual In-Line (PLA) |        |           |        |       |           |  |  |  |

|--------|-------------------------------------------|--------|-----------|--------|-------|-----------|--|--|--|

|        | Millimeters                               |        |           | Inches |       |           |  |  |  |

| Symbol | Min                                       | Max    | Notes     | Min    | Max   | Notes     |  |  |  |

| α      | 0°                                        | 10°    |           | 0°     | 10°   |           |  |  |  |

| Α      | _                                         | 5.080  |           | _      | 0.200 |           |  |  |  |

| A1     | 0.381                                     | _      |           | 0.015  | _     |           |  |  |  |

| A2     | 3.175                                     | 4.064  |           | 0.125  | 0.160 |           |  |  |  |

| В      | 0.355                                     | 0.559  |           | 0.014  | 0.022 |           |  |  |  |

| B1     | 1.270                                     | 1.778  | Typical   | 0.050  | 0.070 | Typical   |  |  |  |

| С      | 0.203                                     | 0.381  | Typical   | 0.008  | 0.015 | Typical   |  |  |  |

| D      | 51.181                                    | 52.197 |           | 2.015  | 2.055 |           |  |  |  |

| D1     | 48.260                                    | 48.260 | Reference | 1.900  | 1.900 | Reference |  |  |  |

| E      | 15.240                                    | 15.875 |           | 0.600  | 0.625 |           |  |  |  |

| E1     | 13.462                                    | 13.970 |           | 0.530  | 0.550 |           |  |  |  |

| e1     | 2.489                                     | 2.591  | Typical   | 0.098  | 0.102 | Typical   |  |  |  |

| eA     | 15.240                                    | 15.240 | Reference | 0.600  | 0.600 | Reference |  |  |  |

| eB     | 15.240                                    | 17.272 |           | 0.600  | 0.680 |           |  |  |  |

| L      | 2.921                                     | 3.683  |           | 0.115  | 0.145 |           |  |  |  |

| N      | 40                                        | 40     |           | 40     | 40    |           |  |  |  |

| S      | 1.270                                     | _      |           | 0.050  | _     |           |  |  |  |

| S1     | 0.508                                     | _      |           | 0.020  | _     |           |  |  |  |

| gisters             |                          | PORTD   |                        |

|---------------------|--------------------------|---------|------------------------|

| CCP1CON             |                          | Section | 57                     |

| Diagram             | 78                       | Summary | 28, 30, 32             |

| Section             | 78                       | PORTE   |                        |

| Summary             |                          | Section | 58                     |

| CCP2CON             | 2 1, 20, 20, 00, 02      |         | 28, 30, 32             |

| Diagram             | 79                       | PR2     | 20, 00, 02             |

| •                   |                          |         | 05 07 00 01 00         |

| Section             |                          |         | 25, 27, 29, 31, 33     |

| Summary             | 26, 30, 32               | RCREG   |                        |

| CCPR1H              |                          | -       | 26, 30, 32             |

| Summary             | 24, 26, 28, 30, 32       | RCSTA   |                        |