Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-11-                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-04i-p |

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63

| Address              | Name    | Bit 7              | Bit 6                             | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|-----------------------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                                   |               |                |               |                 |               |           |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location                     | uses conter   | nts of FSR to  | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe                    | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                     | Least Signi   | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                | RP0           | TO             | PD            | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad                       | dress pointe  | er             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | _                  | _                                 | PORTA Dat     | a Latch wher   | written: PO   | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat          | a Latch whe                       | n written: P0 | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat          | ta Latch whe                      | n written: Po | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | -       | Unimpleme          | nted                              |               |                |               |                 |               |           | _                        | _                                              |

| 09h                  | _       | Unimpleme          | nted                              |               |                |               |                 |               |           | _                        | _                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                                 | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                              | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | (5)                | (5)                               | TMR1IF        | 0000 0000      | 0000 0000     |                 |               |           |                          |                                                |

| 0Dh                  | PIR2    | _                  | _                                 | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L                   | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the N                   | Nost Signific | ant Byte of th | ne 16-bit TMI | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | _                  | _                                 | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe                    | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                  | TOUTPS3                           | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | ıs Serial Port                    | Receive Bu    | ıffer/Transmit | Register      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV                             | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM                         | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM                         | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                  | -                                 | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | SPEN RX9 SREN CREN — FERR OERR RX |               |                |               |                 |               |           |                          | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai         | JSART Transmit Data Register      |               |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red          | ceive Data R                      | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM                         | 2 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM                         | 2 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | -                  | _                                 | CCP2X         | CCP2Y          | ССР2М3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | Unimplemented                     |               |                |               |                 |               |           |                          | _                                              |

$\label{eq:location} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value} \ \textbf{depends} \ \textbf{on condition}, \ \textbf{-} = \textbf{unimplemented} \ \textbf{location} \ \textbf{read} \ \textbf{as} \ \textbf{'0'}.$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

- $5: \quad \text{PIE1} < 7:6 \text{> and PIR1} < 7:6 \text{> are reserved on the PIC16C63/R63, always maintain these bits clear.} \\$

TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64

| Address              | Name    | Bit 7              | Bit 6              | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |  |

|----------------------|---------|--------------------|--------------------|----------------|----------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|--|

| Bank 0               |         |                    |                    |                |                |              |                 |               | •         |                          |                                                |  |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter    | nts of FSR to  | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |  |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r              |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signi    | ficant Byte    |              |                 |               |           | 0000 0000                | 0000 0000                                      |  |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0            | TO             | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |  |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac        | Idress pointe  | er             |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 05h                  | PORTA   | _                  | _                  | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |  |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe       | n written: PC  | ORTB pins wh   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe       | n written: PO  | ORTC pins w    | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 08h                  | PORTD   | PORTD Da           | ta Latch whe       |                | xxxx xxxx      | uuuu uuuu    |                 |               |           |                          |                                                |  |

| 09h                  | PORTE   | _                  | _                  | RE0            | xxx            | uuu          |                 |               |           |                          |                                                |  |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                  | -              | Write Buffer   | for the uppe | r 5 bits of the | Program C     | ounter    | 0 0000                   | 0 0000                                         |  |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE           | INTE           | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |  |

| 0Ch                  | PIR1    | PSPIF              | (6)                | -              | _              | SSPIF        | CCP1IF          | TMR2IF        | TMR1IF    | 00 0000                  | 00 0000                                        |  |

| 0Dh                  | _       | Unimpleme          | nted               |                |                | •            |                 |               |           | _                        | _                                              |  |

| 0Eh                  | TMR1L   | Holding reg        | ister for the I    | _east Signific | ant Byte of t  | he 16-bit TM | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 0Fh                  | TMR1H   | Holding reg        | ister for the I    | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 10h                  | T1CON   | _                  | _                  | T1CKPS1        | T1CKPS0        | T10SCEN      | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |  |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r              | •              | •            |                 |               |           | 0000 0000                | 0000 0000                                      |  |

| 12h                  | T2CON   | _                  | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |  |

| 13h                  | SSPBUF  | Synchronou         | ıs Serial Por      |                | xxxx xxxx      | uuuu uuuu    |                 |               |           |                          |                                                |  |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPM0          | 0000 0000      | 0000 0000    |                 |               |           |                          |                                                |  |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |  |

| 17h                  | CCP1CON | _                  | _                  | CCP1X          | CCP1Y          | CCP1M3       | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |  |

| 18h-1Fh              | _       | Unimpleme          | nimplemented       |                |                |              |                 |               |           |                          |                                                |  |

$\begin{tabular}{ll} Legend: & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented location read as '0'. \end{tabular}$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

- $\hbox{6:} \quad \hbox{PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear. } \\$

TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64 (Cont.'d)

| Address              | Name    | Bit 7              | Bit 6              | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1          | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|---------------------------|---------------|--------------|-----------------|----------------|--------------------|--------------------------|------------------------------------------------|

| Bank 1               |         |                    |                    |                           |               |              |                 |                |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter               | nts of FSR to | address data | a memory (n     | ot a physical  | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU               | INTEDG             | T0CS                      | T0SE          | PSA          | PS2             | PS1            | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Sigr                | nificant Byte |              |                 |                |                    | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0                       | TO            | PD           | Z               | DC             | С                  | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ac        | Idress pointe             | er            |              |                 |                |                    | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                  | _                  | PORTA Dat                 | a Direction R | egister      |                 |                |                    | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Date         | ta Direction F     | Register                  |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da           | ta Direction F     | Register                  |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | TRISD   | PORTD Da           | ta Direction F     | Register                  |               | 1111 1111    | 1111 1111       |                |                    |                          |                                                |

| 89h                  | TRISE   | IBF                | OBF                | IBOV                      | PSPMODE       | _            | PORTE Da        | ta Direction I | Bits               | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                  | _                         | Write Buffer  | for the uppe | r 5 bits of the | Program C      | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE                      | INTE          | RBIE         | TOIF            | INTF           | RBIF               | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | PSPIE              | (6)                | _                         | _             | SSPIE        | CCP1IE          | TMR2IE         | TMR1IE             | 00 0000                  | 00 0000                                        |

| 8Dh                  | _       | Unimpleme          | nted               |                           |               |              |                 |                |                    | -                        | _                                              |

| 8Eh                  | PCON    | _                  | _                  | _                         | _             | _            | _               | POR            | BOR <sup>(4)</sup> | qq                       | uu                                             |

| 8Fh                  | _       | Unimpleme          | nted               |                           |               |              |                 |                |                    | _                        | -                                              |

| 90h                  | _       | Unimpleme          | nted               |                           |               |              |                 |                |                    | _                        | _                                              |

| 91h                  | _       | Unimpleme          | Jnimplemented      |                           |               |              |                 |                |                    |                          | _                                              |

| 92h                  | PR2     | Timer2 Peri        | od Register        |                           |               | ·            | ·               | ·              |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou         | us Serial Port     | t (I <sup>2</sup> C mode) | Address Reg   | gister       |                 |                |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | _                  | _                  | D/Ā                       | Р             | S            | R/W             | UA             | BF                 | 00 0000                  | 00 0000                                        |

| 95h-9Fh              | _       | Unimpleme          | nted               |                           |               | _            | _               |                |                    |                          |                                                |

$\label{eq:location} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value} \ \textbf{depends} \ \textbf{on condition}, \ \textbf{-} = \textbf{unimplemented} \ \textbf{location} \ \textbf{read} \ \textbf{as} \ \textbf{'0'}.$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

- 6: PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

|                      |         |                      |                |                           |                |              |                 |                | •         | •                        |                                                |  |  |  |

|----------------------|---------|----------------------|----------------|---------------------------|----------------|--------------|-----------------|----------------|-----------|--------------------------|------------------------------------------------|--|--|--|

| Address              | Name    | Bit 7                | Bit 6          | Bit 5                     | Bit 4          | Bit 3        | Bit 2           | Bit 1          | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |  |  |  |

| Bank 1               |         |                      | 1              |                           |                |              |                 |                | 1         |                          |                                                |  |  |  |

| 80h <sup>(1)</sup>   | INDF    | Addressing           | this location  | uses conte                | nts of FSR to  | address dat  | a memory (n     | ot a physical  | register) | 0000 0000                | 0000 0000                                      |  |  |  |

| 81h                  | OPTION  | RBPU                 | INTEDG         | T0CS                      | TOSE           | PSA          | PS2             | PS1            | PS0       | 1111 1111                | 1111 1111                                      |  |  |  |

| 82h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)  | Least Sigr                | nificant Byte  |              |                 |                |           | 0000 0000                | 0000 0000                                      |  |  |  |

| 83h <sup>(1)</sup>   | STATUS  | IRP                  | RP1            | RP0                       | TO             | PD           | Z               | DC             | С         | 0001 1xxx                | 000q quuu                                      |  |  |  |

| 84h <sup>(1)</sup>   | FSR     | Indirect data        | a memory ad    | Idress pointe             | er             |              |                 |                |           | xxxx xxxx                | uuuu uuuu                                      |  |  |  |

| 85h                  | TRISA   | _                    | _              | PORTA Da                  | ta Direction R | egister      |                 |                |           | 11 1111                  | 11 1111                                        |  |  |  |

| 86h                  | TRISB   | PORTB Dat            | ta Direction F | Register                  |                |              |                 |                |           | 1111 1111                | 1111 1111                                      |  |  |  |

| 87h                  | TRISC   | PORTC Da             | ta Direction F | Register                  |                |              |                 |                |           | 1111 1111                | 1111 1111                                      |  |  |  |

| 88h <sup>(5)</sup>   | TRISD   | PORTD Da             | ta Direction F | Register                  |                |              |                 |                |           | 1111 1111                | 1111 1111                                      |  |  |  |

| 89h <sup>(5)</sup>   | TRISE   | IBF                  | OBF            | IBOV                      | PSPMODE        | _            | PORTE Da        | ta Direction I | Bits      | 0000 -111                | 0000 -111                                      |  |  |  |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                    | _              | _                         | Write Buffer   | for the uppe | r 5 bits of the | Program C      | ounter    | 0 0000                   | 0 0000                                         |  |  |  |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE           | TOIE                      | INTE           | RBIE         | TOIF            | INTF           | RBIF      | 0000 000x                | 0000 000u                                      |  |  |  |

| 8Ch                  | PIE1    | PSPIE <sup>(6)</sup> | (4)            | RCIE                      | TMR1IE         | 0000 0000    | 0000 0000       |                |           |                          |                                                |  |  |  |

| 8Dh                  | PIE2    | _                    | _              | _                         | CCP2IE         | 0            | 0               |                |           |                          |                                                |  |  |  |

| 8Eh                  | PCON    | _                    | _              | -                         | _              | _            | _               | POR            | BOR       | qq                       | uu                                             |  |  |  |

| 8Fh                  | _       | Unimpleme            | nted           |                           |                | •            | •               | •              |           | _                        | _                                              |  |  |  |

| 90h                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 91h                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 92h                  | PR2     | Timer2 Peri          | od Register    |                           |                |              |                 |                |           | 1111 1111                | 1111 1111                                      |  |  |  |

| 93h                  | SSPADD  | Synchronou           | ıs Serial Port | t (I <sup>2</sup> C mode) | Address Reg    | gister       |                 |                |           | 0000 0000                | 0000 0000                                      |  |  |  |

| 94h                  | SSPSTAT | SMP                  | CKE            | D/Ā                       | Р              | S            | R/W             | UA             | BF        | 0000 0000                | 0000 0000                                      |  |  |  |

| 95h                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 96h                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 97h                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 98h                  | TXSTA   | CSRC                 | TX9            | TXEN                      | SYNC           | _            | BRGH            | TRMT           | TX9D      | 0000 -010                | 0000 -010                                      |  |  |  |

| 99h                  | SPBRG   | Baud Rate            | Generator Re   | egister                   |                | 0000 0000    | 0000 0000       |                |           |                          |                                                |  |  |  |

| 9Ah                  | _       | Unimpleme            | nted           |                           | _              | _            |                 |                |           |                          |                                                |  |  |  |

| 9Bh                  | _       | Unimpleme            | mplemented     |                           |                |              |                 |                |           |                          |                                                |  |  |  |

| 9Ch                  | _       | Unimpleme            | mplemented —   |                           |                |              |                 |                |           |                          |                                                |  |  |  |

| 9Dh                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 9Eh                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

| 9Fh                  | _       | Unimpleme            | nted           |                           |                |              |                 |                |           | _                        | _                                              |  |  |  |

|                      |         |                      | ala anana a    |                           |                |              |                 |                |           | 101                      |                                                |  |  |  |

$\label{eq:location} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value depends on condition}, \ \textbf{-} = \textbf{unimplemented location read as '0'}.$

- Note 1: These registers can be addressed from any bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

- 5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

- 6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

## FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| U = Unimplemented bit, read as '0' - n = Value at POR reset  1.7-6: Reserved: Always maintain these bits clear.  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  1.4: TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  1.3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  1.2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1. TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                                                                                   | R/W-0    | R/W-0                                                                   | R-0                                                                              | R-0                                   | R/W-0                                 | R/W-0         | R/W-0         | R/W-0    |                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------|---------------|----------|------------------------------------|

| U = Unimplemented bit, read as '0' - n = Value at POR reset  RCIF: USART Receive Interrupt Flag bit 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  TXIF: USART transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred (must be cleared in software) 1 : TMR1F: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software) | _        | _                                                                       | RCIF                                                                             | TXIF                                  | SSPIF                                 | CCP1IF        | TMR2IF        | TMR1IF   |                                    |

| t 5: RCIF: USART Receive Interrupt Flag bit  1 = The USART receive buffer is full (cleared by reading RCREG)  0 = The USART receive buffer is empty  44: TXIF: USART Transmit Interrupt Flag bit  1 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is full  1 = The transmission/reception is complete (must be cleared in software)  0 = Waiting to transmit/receive  1 = CCP1IF: CCP1 Interrupt Flag bit  Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2IF: TMR2 to PR2 match occurred  0 = No TMR1 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 O: TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                             | oit7     |                                                                         |                                                                                  |                                       |                                       |               |               | bit0     | U = Unimplemented bit, read as '0' |

| 1 = The USART receive buffer is full (cleared by reading RCREG) 0 = The USART receive buffer is empty  14:  TXIF: USART Transmit Interrupt Flag bit 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2:  CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1:  TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: 1:  TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow loccurred (must be cleared in software)                                                                                                                                                                                                                                                                                                | bit 7-6: | Reserved:                                                               | Always ma                                                                        | intain thes                           | e bits clear.                         |               |               |          |                                    |

| 1 = The USART transmit buffer is empty (cleared by writing to TXREG) 0 = The USART transmit buffer is full  3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  4: 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  4: 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 5:   | 1 = The US                                                              | ART receiv                                                                       | e buffer is                           | full (cleared                         | d by reading  | RCREG)        |          |                                    |

| 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive  2 : CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode  1 = TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR1 to PR2 match occurred 1 to: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 4:   | 1 = The US                                                              | ART transi                                                                       | nit buffer is                         | empty (cle                            | ared by writi | ng to TXRE    | G)       |                                    |

| Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software)  0 = No TMR1 register capture occurred  Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software)  0 = No TMR1 register compare match occurred  PWM Mode  Unused in this mode  1 : TMR2IF: TMR2 to PR2 Match Interrupt Flag bit  1 = TMR2 to PR2 match occurred (must be cleared in software)  0 = No TMR2 to PR2 match occurred  1 : TMR1IF: TMR1 Overflow Interrupt Flag bit  1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 3:   | 1 = The tra                                                             | nsmission/i                                                                      | reception is                          |                                       |               | ared in softv | vare)    |                                    |

| 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred  t 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 2:   | Capture Mo 1 = A TMR 0 = No TMI Compare M 1 = A TMR 0 = No TMI PWM Mode | ode<br>1 register c<br>R1 register<br><u>lode</u><br>1 register c<br>R1 register | apture occ<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | ed (must be o | ,             | oftware) |                                    |

| 1 = TMR1 register overflow occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1:   | 1 = TMR2 t                                                              | o PR2 mat                                                                        | ch occurre                            | d (must be                            |               | oftware)      |          |                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 0:   | 1 = TMR1 ı                                                              | egister ove                                                                      | rflow occu                            | rred (must l                          | oe cleared in | software)     |          |                                    |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 7.2 <u>Using Timer0 with External Clock</u>

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

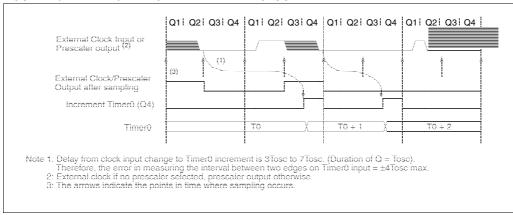

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

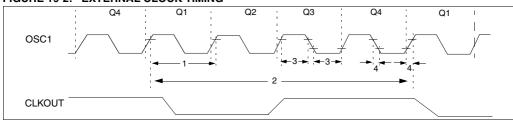

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

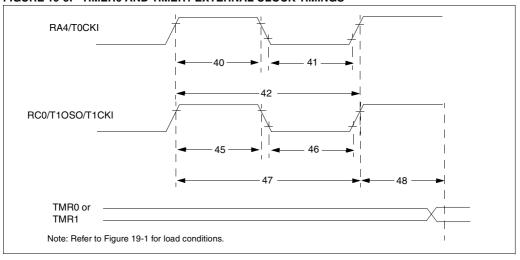

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

FIGURE 7-5: TIMERO TIMING WITH EXTERNAL CLOCK

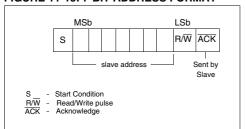

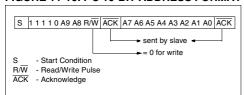

## 11.4.2 ADDRESSING I2C DEVICES

There are two address formats. The simplest is the 7-bit address format with a  $R\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

### FIGURE 11-16: I2C 10-BIT ADDRESS FORMAT

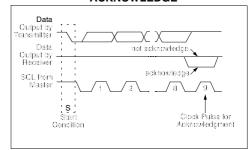

#### 11.4.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

## FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

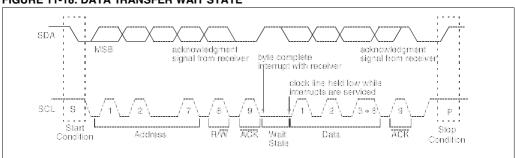

### FIGURE 11-18: DATA TRANSFER WAIT STATE

## 12.1 USART Baud Rate Generator (BRG)

| Αp | pli | cable | e Dev | vice | es  |    |     |     |    |     |     |    |    |

|----|-----|-------|-------|------|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62  | 62A   | R62   | 63   | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

## EXAMPLE 12-1: CALCULATING BAUD RATE FRROR

Desired Baud rate = Fosc / (64 (X + 1))

9600 = 16000000 / (64 (X + 1)) $X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X+1)) equation can reduce the baud rate error in some cases.

Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------|-----------|-------------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9       | TXEN        | SYNC  | -     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9       | SREN        | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| 99h     | SPBRG | Baud Rat | te Genera | tor Registe | er    |       |       |       |       | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

## TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Нz                          | 4 MHz  |            |                             | 3.579545 | MHz        |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

## TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 | 0 MHz      | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | 1.221    | +1.73      | 255                | 1.202  | +0.16      | 207                | 1.202  | +0.16      | 129                | 1.203     | +0.23      | 92                 |

| 2.4         | 2.404    | +0.16      | 129                | 2.404  | +0.16      | 103                | 2.404  | +0.16      | 64                 | 2.380     | -0.83      | 46                 |

| 9.6         | 9.469    | -1.36      | 32                 | 9.615  | +0.16      | 25                 | 9.766  | +1.73      | 15                 | 9.322     | -2.90      | 11                 |

| 19.2        | 19.53    | +1.73      | 15                 | 19.23  | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64     | -2.90      | 5                  |

| 76.8        | 78.13    | +1.73      | 3                  | 83.33  | +8.51      | 2                  | 78.13  | +1.73      | 1                  | NA        | -          | -                  |

| 96          | 104.2    | +8.51      | 2                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 300         | 312.5    | +4.17      | 0                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 500         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| HIGH        | 312.5    | -          | 0                  | 250    | -          | 0                  | 156.3  | -          | 0                  | 111.9     | -          | 0                  |

| LOW         | 1.221    | -          | 255                | 0.977  | -          | 255                | 0.6104 | -          | 255                | 0.437     | -          | 255                |

|                     | Fosc = | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |