# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                            |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-20-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7                                                        | Bit 6                        | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------------------------------------------------|------------------------------|---------------|----------------|---------------|-------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                                                              |                              |               |                |               |             |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing                                                   | this location                | uses conten   | ts of FSR to   | address data  | a memory (n | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod                                                   | lule's registe               | r             |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co                                                   | ounter's (PC)                | Least Signif  | ficant Byte    |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>                                           | RP1 <sup>(5)</sup>           | RP0           | TO             | PD            | z           | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                                                | a memory ad                  | Idress pointe | ər             |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | -                                                            | _                            | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat                                                    | ta Latch whe                 | n written: PC | ORTB pins wi   | nen read      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat                                                    | ta Latch whe                 | n written: PC | ORTC pins w    | hen read      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat                                                    | ta Latch whe                 | n written: PC | ORTD pins w    | hen read      |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                                                              | _                            | _             | _              | _             | RE2         | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | — — Write Buffer for the upper 5 bits of the Program Counter |                              |               |                |               |             |               | 0 0000    | 0 0000                   |                                                |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                                          | PEIE                         | TOIE          | INTE           | RBIE          | TOIF        | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF                                                        | (6)                          | RCIF          | TXIF           | SSPIF         | CCP1IF      | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                                                              | _                            | _             |                | _             | _           | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg                                                  | ister for the L              | east Signific | cant Byte of t | he 16-bit TM  | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg                                                  | ister for the M              | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                                                              | _                            | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod                                                   | lule's registe               | r             |                |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                                                            | TOUTPS3                      | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON      | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou                                                   | is Serial Port               | Receive Bu    | ffer/Transmit  | Register      |             | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                                                         | SSPOV                        | SSPEN         | CKP            | SSPM3         | SSPM2       | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co                                                   | mpare/PWM                    | 1 (LSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co                                                   | mpare/PWM                    | 1 (MSB)       |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                                                            | —                            | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2      | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                                                         | RX9                          | SREN          | CREN           | —             | FERR        | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai                                                   | USART Transmit Data Register |               |                |               |             |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Receive Data Register                                  |                              |               |                |               |             |               | 0000 0000 | 0000 0000                |                                                |

| 1Bh                  | CCPR2L  | Capture/Co                                                   | Capture/Compare/PWM2 (LSB)   |               |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  |                                                              |                              |               |                |               |             | xxxx xxxx     | uuuu uuuu |                          |                                                |

| 1Dh                  | CCP2CON | —                                                            | —                            | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2      | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme                                                    | nted                         |               |                |               |             |               |           | —                        | _                                              |

### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

### TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                       |  |

|------------|------|-------------|--------------------------------------------------------------------------------|--|

| RA0        | bit0 | TTL         | Input/output                                                                   |  |

| RA1        | bit1 | TTL         | Input/output                                                                   |  |

| RA2        | bit2 | TTL         | Input/output                                                                   |  |

| RA3        | bit3 | TTL         | Input/output                                                                   |  |

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0.<br>Output is open drain type. |  |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.                |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

### TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5                                        | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|----------------------------------------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | —     | —     | RA5 <sup>(1)</sup>                           | RA4   | RA3   | RA2   | RA1   | RA0   | xx xxxx                  | uu uuuu                   |

| 85h     | TRISA | —     | —     | PORTA Data Direction Register <sup>(1)</sup> |       |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

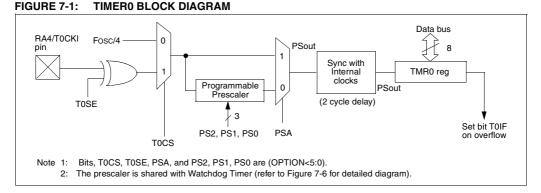

#### 7.0 TIMER0 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

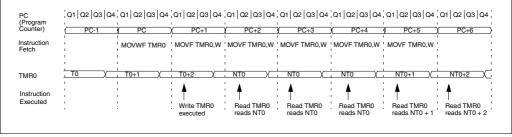

Timer mode is selected by clearing bit T0CS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 TMR0 Interrupt

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the TImer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

© 1997-2013 Microchip Technology Inc.

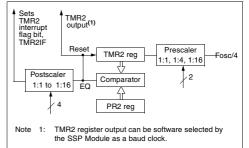

### 9.0 TIMER2 MODULE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

### 9.1 Timer2 Prescaler and Postscaler

### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

### 9.2 Output of TMR2

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

### EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 78.125 kHz, Fosc = 20 MHz TMR2 prescale = 1

$1/78.125 \text{ kHz} = [(PR2) + 1] \cdot 4 \cdot 1/20 \text{ MHz} \cdot 1$   $12.8 \ \mu s = [(PR2) + 1] \cdot 4 \cdot 50 \text{ ns} \cdot 1$ PR2 = 63

Find the maximum resolution of the duty cycle that can be used with a 78.125 kHz frequency and 20 MHz oscillator:

| 1/78.125 kHz | = $2^{\text{PWM RESOLUTION}} \cdot 1/20 \text{ MHz} \cdot 1$  |

|--------------|---------------------------------------------------------------|

| 12.8 µs      | = $2^{\text{PWM RESOLUTION}} \bullet 50 \text{ ns} \bullet 1$ |

| 256          | $= 2^{\text{PWM RESOLUTION}}$                                 |

| log(256)     | = (PWM Resolution) • $log(2)$                                 |

| 8.0          | = PWM Resolution                                              |

|              |                                                               |

At most, an 8-bit resolution duty cycle can be obtained from a 78.125 kHz frequency and a 20 MHz oscillator, i.e.,  $0 \leq$  CCPR1L:CCP1CON<5:4>  $\leq$  255. Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-3 lists example PWM frequencies and resolutions for Fosc = 20 MHz. The TMR2 prescaler and PR2 values are also shown.

10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

### TABLE 10-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

### TABLE 10-4: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Add                  | Name    | Bit 7                | Bit 6                         | Bit 5               | Bit 4               | Bit 3                    | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|----------------------|---------|----------------------|-------------------------------|---------------------|---------------------|--------------------------|------------|------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                          | TOIE                | INTE                | RBIE                     | T0IF       | INTF       | RBIF   |      |                    | 0000  |                       |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup> | (3)                           | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF                    | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 0Dh <sup>(4)</sup>   | PIR2    | —                    | _                             | _                   | _                   | -                        | -          | -          | CCP2IF |      | 0                  |       | 0                     |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup> | (3)                           | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE                    | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 8Dh <sup>(4)</sup>   | PIE2    | —                    | _                             | _                   | _                   |                          | —          |            | CCP2IE |      | 0                  |       | 0                     |

| 87h                  | TRISC   | PORTC D              | PORTC Data Direction register |                     |                     |                          |            |            |        |      |                    | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding re           | egister for                   | the Least           | Significant         | Byte of the              | 16-bit TMF | R1 registe | r      | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding re           | egister for                   | the Most S          | Significant I       | Byte of the <sup>·</sup> | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h                  | T1CON   | _                    | _                             | T1CKPS1             | T1CKPS0             | T1OSCEN                  | T1SYNC     | TMR1CS     | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/C            | Compare/                      | PWM1 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture/C            | Compare/                      | PWM1 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                  | CCP1CON | —                    | _                             | CCP1X               | CCP1Y               | CCP1M3                   | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00    | 0000                  |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/C            | Compare/                      | PWM2 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/C            | Compare/                      | PWM2 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh <sup>(4)</sup>   | CCP2CON | —                    | _                             | CCP2X               | CCP2Y               | CCP2M3                   | CCP2M2     | CCP2M1     | CCP2M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

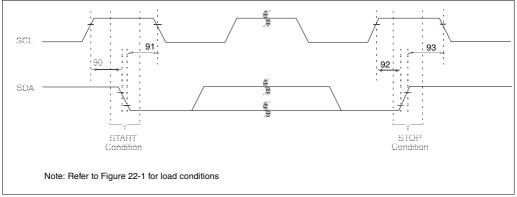

### 11.4.4 MULTI-MASTER

PIC16C6X

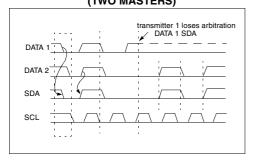

The  $I^2C$  protocol allows a system to have more than one master. This is called multi-master. When two or more masters try to transfer data at the same time, arbitration and synchronization occur.

### 11.4.4.1 ARBITRATION

Arbitration takes place on the SDA line, while the SCL line is high. The master which transmits a high when the other master transmits a low loses arbitration (Figure 11-22), and turns off its data output stage. A master which lost arbitration can generate clock pulses until the end of the data byte where it lost arbitration. When the master devices are addressing the same device, arbitration continues into the data.

### FIGURE 11-22: MULTI-MASTER ARBITRATION (TWO MASTERS)

Masters that also incorporate the slave function, and have lost arbitration must immediately switch over to slave-receiver mode. This is because the winning master-transmitter may be addressing it.

Arbitration is not allowed between:

- A repeated START condition

- · A STOP condition and a data bit

- A repeated START condition and a STOP condition

Care needs to be taken to ensure that these conditions do not occur.

### 11.2.4.2 Clock Synchronization

Clock synchronization occurs after the devices have started arbitration. This is performed using a wired-AND connection to the SCL line. A high to low transition on the SCL line causes the concerned devices to start counting off their low period. Once a device clock has gone low, it will hold the SCL line low until its SCL high state is reached. The low to high transition of this clock may not change the state of the SCL line, if another device clock is still within its low period. The SCL line is held low by the device with the longest low period. Devices with shorter low periods enter a high waitstate, until the SCL line comes high. When the SCL line comes high, all devices start counting off their high periods. The first device to complete its high period will pull the SCL line low. The SCL line high time is determined by the device with the shortest high period, Figure 11-23.

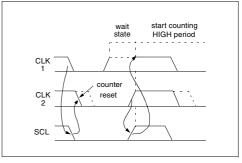

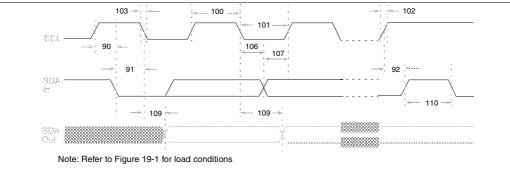

### FIGURE 11-23: CLOCK SYNCHRONIZATION

### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                           | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|---------------------------------|----------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>            | (2)      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                            | RX9      | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra                       | ansmit R | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>            | (2)      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                            | TX9      | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | IG Baud Rate Generator Register |          |         |       |       |        |        |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### Value on Value on Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. all other BOR Resets PSPIF<sup>(1)</sup> 0Ch PIR1 RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000 (2) 18h RCSTA SPEN RX9 SREN CREN FFRR OFBB 0000 -00x 0000 -00x RX9D 0000 0000 0000 0000 1Ah RCREG USART Receive Register PSPIE<sup>(1)</sup> CCP1IE 0000 0000 0000 0000 8Ch PIE1 RCIE TXIE SSPIE TMR2IE TMR1IE (2) 0000 -010 0000 -010 98h TXSTA CSRC BRGH TRMT TX9D TX9 TXEN SYNC \_ 0000 0000 0000 0000 SPBRG 99h Baud Rate Generator Register

### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] C                                                    | LRF f                   |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$                                                      | 7                       |                 |                       |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | 1                       |                 |                       |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | _REG            |                       |  |  |  |

|                   | Before In                                                             |                         |                 |                       |  |  |  |

|                   | FLAG_REG = 0x5A<br>After Instruction                                  |                         |                 |                       |  |  |  |

|                   |                                                                       | FLAG RE                 | EG =            | 0x00                  |  |  |  |

|                   |                                                                       | Z                       | =               | 1                     |  |  |  |

| CLRW                                                                | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                            |                                                              |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|

| Syntax:                                                             | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLRW                                                      |                                                            |                                                              |

| Operands:                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |

| Operation:                                                          | $00h \rightarrow (N 1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V)                                                        |                                                            |                                                              |

| Status Affected:                                                    | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Encoding:                                                           | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0001                                                      | 0xxx                                                       | xxxx                                                         |

| Description:                                                        | W register<br>set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | is cleared                                                | . Zero bit (                                               | (Z) is                                                       |

| Words:                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Cycles:                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Q Cycle Activity:                                                   | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q2                                                        | Q3                                                         | Q4                                                           |

|                                                                     | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No-<br>Operation                                          | Process<br>data                                            | Write to<br>W                                                |

| Example                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |

|                                                                     | Before In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | struction                                                 |                                                            |                                                              |

|                                                                     | After Inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 0x5A                                                       |                                                              |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           | 0x00                                                       |                                                              |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z =                                                       | 1                                                          |                                                              |