Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-20i-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

-

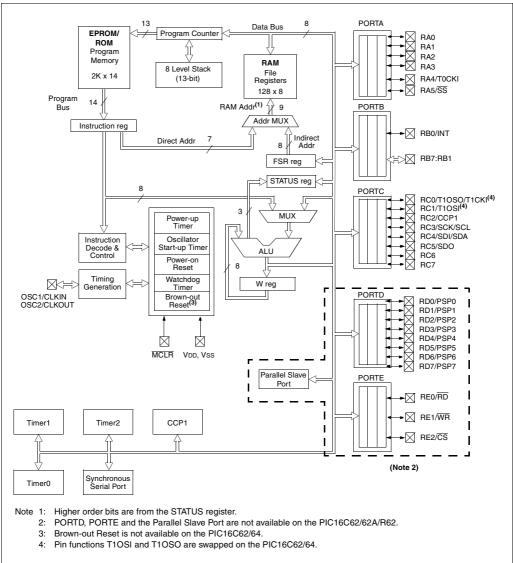

FIGURE 3-2: PIC16C62/62A/R62/64/64A/R64 BLOCK DIAGRAM

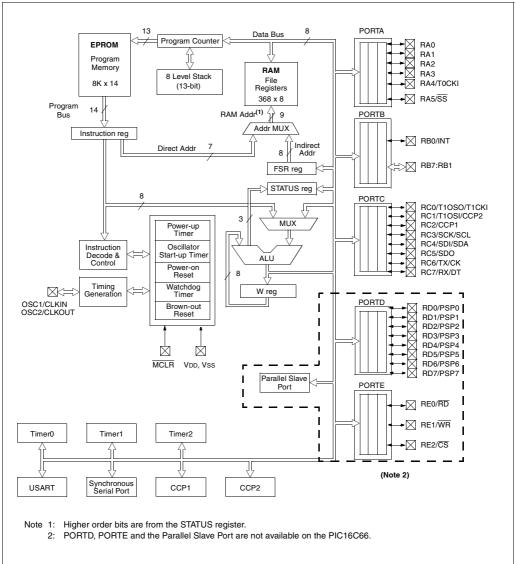

FIGURE 3-4: PIC16C66/67 BLOCK DIAGRAM

### 4.0 MEMORY ORGANIZATION

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

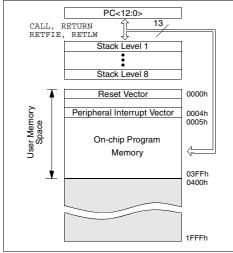

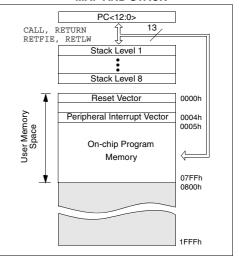

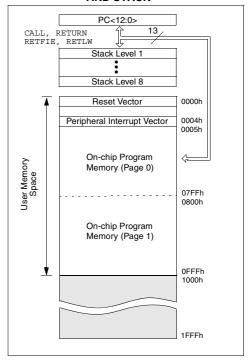

#### 4.1 Program Memory Organization

The PIC16C6X family has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |  |  |  |

|-----------|-------------------|---------------|--|--|--|

| PIC16C61  | 1K x 14           | 0000h-03FFh   |  |  |  |

| PIC16C62  | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16C62A | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16CR62 | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16C63  | 4K x 14           | 0000h-0FFFh   |  |  |  |

| PIC16CR63 | 4K x 14           | 0000h-0FFFh   |  |  |  |

| PIC16C64  | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16C64A | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16CR64 | 2K x 14           | 0000h-07FFh   |  |  |  |

| PIC16C65  | 4K x 14           | 0000h-0FFFh   |  |  |  |

| PIC16C65A | 4K x 14           | 0000h-0FFFh   |  |  |  |

| PIC16CR65 | 4K x 14           | 0000h-0FFFh   |  |  |  |

| PIC16C66  | 8K x 14           | 0000h-1FFFh   |  |  |  |

| PIC16C67  | 8K x 14           | 0000h-1FFFh   |  |  |  |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC16C61 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-2: PIC16C62/62A/R62/64/64A/ R64 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-3: PIC16C63/R63/65/65A/R65 PROGRAM MEMORY MAP AND STACK

| IABLE                | 4-4:                                              | SPECIA             | LFUNC              |                           | GISTERS       | FOR II       |                 | 0004/04/       | 4/H04 ((           | cont.a)                  |                                                |

|----------------------|---------------------------------------------------|--------------------|--------------------|---------------------------|---------------|--------------|-----------------|----------------|--------------------|--------------------------|------------------------------------------------|

| Address              | Name                                              | Bit 7              | Bit 6              | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1          | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

| Bank 1               |                                                   |                    |                    |                           |               |              |                 |                |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF                                              | Addressing         | this location      | uses conte                | nts of FSR to | address dat  | a memory (n     | ot a physical  | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION                                            | RBPU               | INTEDG             | TOCS                      | T0SE          | PSA          | PS2             | PS1            | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL Program Counter's (PC) Least Significant Byte |                    |                    |                           |               |              |                 |                |                    |                          | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS                                            | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0                       | TO            | PD           | Z               | DC             | С                  | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR                                               | Indirect dat       |                    | xxxx xxxx                 | uuuu uuuu     |              |                 |                |                    |                          |                                                |

| 85h                  | TRISA                                             | _                  | —                  |                           | 11 1111       | 11 1111      |                 |                |                    |                          |                                                |

| 86h                  | TRISB                                             | PORTB Da           | ta Direction F     | Register                  |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC PORTC Data Direction Register               |                    |                    |                           |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | TRISD PORTD Data Direction Register               |                    |                    |                           |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 89h                  | TRISE                                             | IBF                | OBF                | IBOV                      | PSPMODE       | —            | PORTE Da        | ta Direction I | Bits               | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH                                            | —                  | —                  | —                         | Write Buffer  | for the uppe | r 5 bits of the | e Program C    | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON                                            | GIE                | PEIE               | TOIE                      | INTE          | RBIE         | TOIF            | INTF           | RBIF               | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1                                              | PSPIE              | (6)                | —                         | —             | SSPIE        | CCP1IE          | TMR2IE         | TMR1IE             | 00 0000                  | 00 0000                                        |

| 8Dh                  | -                                                 | Unimpleme          | nted               |                           |               |              |                 |                |                    | -                        | —                                              |

| 8Eh                  | PCON                                              | —                  | —                  | —                         | —             | —            | —               | POR            | BOR <sup>(4)</sup> | qq                       | uu                                             |

| 8Fh                  | _                                                 | Unimpleme          | nted               |                           |               |              |                 |                |                    | -                        | _                                              |

| 90h                  | -                                                 | Unimpleme          | nted               |                           |               |              |                 |                |                    | _                        | —                                              |

| 91h                  | -                                                 | Unimpleme          | nted               |                           |               |              |                 |                |                    | -                        | —                                              |

| 92h                  | PR2                                               | Timer2 Peri        | iod Register       |                           |               |              |                 |                |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD                                            | Synchronou         | us Serial Por      | t (I <sup>2</sup> C mode) | Address Reg   | jister       |                 |                |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT                                           | _                  | —                  | D/Ā                       | Р             | S            | R/W             | UA             | BF                 | 00 0000                  | 00 0000                                        |

| 95h-9Fh              | _                                                 | Unimpleme          | nted               |                           |               |              |                 |                |                    | _                        | —                                              |

|                      |                                                   |                    |                    |                           |               |              |                 |                |                    |                          |                                                |

TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64 (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

#### 4.2.2.3 INTCON REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INTCON Register is a readable and writable register which contains the various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts.

#### Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### FIGURE 4-11: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh 18Bh)

| R/W-0<br>GIE | R/W-0<br>PEIE                                               | R/W-0<br>T0IE      | R/W-0<br>INTE                                | R/W-0<br>RBIE | R/W-0<br>T0IF            | R/W-0<br>INTF | R/W-x<br>RBIF | R = Readable bit                                                                                     |

|--------------|-------------------------------------------------------------|--------------------|----------------------------------------------|---------------|--------------------------|---------------|---------------|------------------------------------------------------------------------------------------------------|

| bit7         | 1 212                                                       | TOLE               | INTE                                         | TIDIL         | 1011                     |               | bit0          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset<br>x = unknown |

| bit 7:       | <b>GIE:</b> <sup>(1)</sup> Glo<br>1 = Enable<br>0 = Disable | s all un-ma        | sked interro                                 |               |                          |               |               |                                                                                                      |

| bit 6:       | PEIE: <sup>(2)</sup> Pe<br>1 = Enable<br>0 = Disable        | s all un-ma        | sked peripl                                  | neral interru | ipts                     |               |               |                                                                                                      |

| bit 5:       |                                                             | s the TMR          | Interrupt E<br>0 overflow ii<br>0 overflow i | nterrupt      |                          |               |               |                                                                                                      |

| bit 4:       | 1 = Enable                                                  | s the RB0/         | nal Interrup<br>INT externa<br>INT externa   |               |                          |               |               |                                                                                                      |

| bit 3:       |                                                             | s the RB p         | e Interrupt<br>ort change<br>ort change      | interrupt     |                          |               |               |                                                                                                      |

| bit 2:       | <b>TOIF:</b> TMR<br>1 = TMR0<br>0 = TMR0                    | register ove       | erflowed (m                                  | ust be clea   | red in softwa            | re)           |               |                                                                                                      |

| bit 1:       |                                                             | 30/INT exte        | rnal interru                                 |               | (must be cle<br>ccur     | ared in soft  | ware)         |                                                                                                      |

| bit 0:       |                                                             | t one of the       | RB7:RB4                                      |               | ed state (see<br>d state | Section 5.2   | to clear the  | interrupt)                                                                                           |

|              | be re-enab<br>description                                   | led by the 1<br>1. | RETFIE ins                                   | truction in t | he user's Inte           | errupt Servi  |               | red, the GIE bit may unintentionally<br>Refer to Section 13.5 for a detailed                         |

|              | The PEIE I                                                  | bit (bit6) is      |                                              |               | PIC16C61, r              |               |               |                                                                                                      |

| globa        |                                                             | GIE (INTC          |                                              |               |                          |               |               | corresponding enable bit or the<br>rupt flag bits are clear prior to                                 |

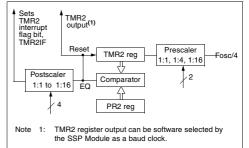

### 9.0 TIMER2 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

#### 9.2 Output of TMR2

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

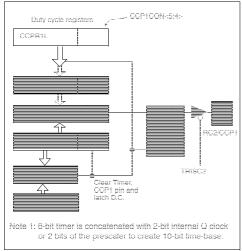

#### 10.3 PWM Mode

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 10-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 10.3.3.

#### FIGURE 10-4: SIMPLIFIED PWM BLOCK DIAGRAM

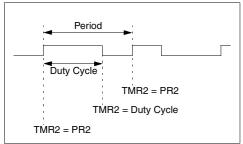

A PWM output (Figure 10-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 10-5: PWM OUTPUT

#### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM duty cycle is latched from CCPR1L into CCPR1H

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

| Note: | The Timer2 postscaler (see Section 9.1) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be forced to the low level.

| Addr                                    | Name                          | Bit 7                | Bit 6        | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------------------------|-------------------------------|----------------------|--------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh                    | INTCON                        | GIE                  | PEIE         | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000<br>000x             | 0000<br>000u                    |

| 0Ch                                     | PIR1                          | PSPIF <sup>(2)</sup> | (3)          | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000                     | 0000                            |

| 0Dh <sup>(4)</sup>                      | PIR2                          | —                    | _            | _                   | _                   | _       | _      | _       | CCP2IF  |                          | <br>0                           |

| 8Ch                                     | PIE1                          | PSPIE <sup>(2)</sup> | (3)          | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000                     | 0000                            |

| 8Dh <sup>(4)</sup>                      | PIE2                          | —                    | _            | -                   | _                   | -       | _      | -       | CCP2IE  |                          | <br>0                           |

| 87h TRISC PORTC Data Direction register |                               |                      |              |                     |                     |         |        |         |         |                          | 1111<br>1111                    |

| 11h                                     | TMR2 Timer2 module's register |                      |              |                     |                     |         |        |         |         |                          | 0000                            |

| 92h                                     | PR2                           | Timer2 m             | iodule's Per | iod register        |                     |         |        |         |         | 1111<br>1111             | 1111<br>1111                    |

| 12h                                     | T2CON                         | —                    | TOUTPS3      | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000<br>0000             | -000<br>0000                    |

| 15h                                     | CCPR1L                        | Capture/0            | Compare/P    | VM1 (LSB)           | 1                   |         |        |         |         | xxxx<br>xxxx             | uuuu<br>uuuu                    |

| 16h                                     | CCPR1H                        | Capture/0            | Compare/P    | VM1 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 17h                                     | CCP1CON                       | —                    | —            | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00<br>0000               | 00<br>0000                      |

| 1Bh <sup>(4)</sup>                      | CCPR2L                        | Capture/0            | Compare/P\   | VM2 (LSB)           | 1                   |         | 1      |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Ch <sup>(4)</sup>                      | CCPR2H                        | Capture/0            | Compare/P\   | VM2 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Dh <sup>(4)</sup>                      | CCP2CON                       | -                    | —            | CCP2X               | CCP2Y               | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00<br>0000               | 00<br>0000                      |

#### TABLE 10-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend:

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode.

Note

1:

These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

To enable the serial port, SSP enable bit SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear enable bit SSPEN, re-initialize SSPCON register, and then set enable bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if implemented)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

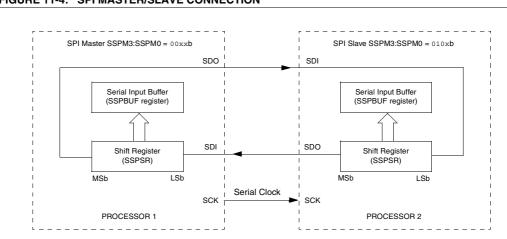

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the software protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched interrupt flag bit SSPIF (PIR1<3>) is set.

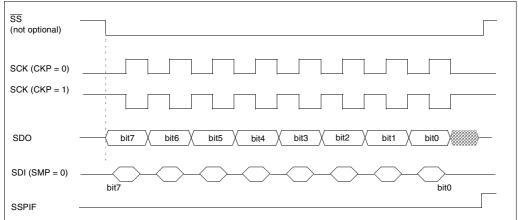

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5 and Figure 11-6 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

#### 11.3.1 SSP MODULE IN SPI MODE FOR PIC16C66/67

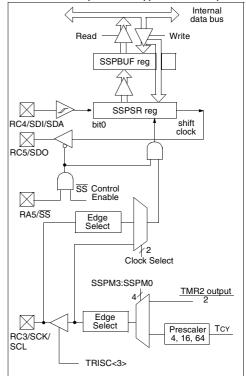

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device. MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

#### EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C66/67)

| LOOP | BCF<br>BSF<br>BTFSS | STATUS,<br>STATUS,<br>SSPSTAT, | RP0 | ;Specify Bank 1<br>;<br>;Has data been<br>;received<br>;(transmit<br>;complete)? |

|------|---------------------|--------------------------------|-----|----------------------------------------------------------------------------------|

|      | GOTO                | LOOP                           |     | ;No                                                                              |

|      | BCF                 | STATUS,                        | RP0 | ;Specify Bank 0                                                                  |

|      | MOVF                | SSPBUF,                        | W   | ;W reg = contents<br>; of SSPBUF                                                 |

|      | MOVWF               | RXDATA                         |     | ;Save in user RAM                                                                |

|      | MOVF                | TXDATA,                        | W   | ;W reg = contents<br>; of TXDATA                                                 |

|      | MOVWF               | SSPBUF                         |     | ;New data to xmit                                                                |

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

#### FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C66/67)

#### FIGURE 11-13: SPI MODE TIMING (SLAVE MODE WITH CKE = 1) (PIC16C66/67)

| TABLE 11-2: | <b>REGISTERS ASSOCIATED WITH SPI OPERATION (PIC16C66/67)</b> |  |

|-------------|--------------------------------------------------------------|--|

|             |                                                              |  |

| Address               | Name    | Bit 7                            | Bit 6                             | Bit 5     | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Pow  | e on<br>er-on<br>set |      | on all<br>resets |

|-----------------------|---------|----------------------------------|-----------------------------------|-----------|------------|------------|----------|--------|--------|------|----------------------|------|------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                              | PEIE                              | TOIE      | INTE       | RBIE       | T0IF     | INTF   | RBIF   | 0000 | 000x                 | 0000 | 000u             |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>             | (2)                               | RCIF      | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 | 0000                 | 0000 | 0000             |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>             | (2)                               | RCIE      | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 | 0000                 | 0000 | 0000             |

| 13h                   | SSPBUF  | Synchrono                        | ous Serial                        | Port Rece | eive Buffe | r/Transmit | Register |        |        | xxxx | xxxx                 | uuuu | uuuu             |

| 14h                   | SSPCON  | WCOL                             | SSPOV                             | SSPEN     | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000                 | 0000 | 0000             |

| 85h                   | TRISA   | _                                | — — PORTA Data Direction register |           |            |            |          |        |        |      |                      | 11   | 1111             |

| 87h                   | TRISC   | SC PORTC Data Direction register |                                   |           |            |            |          |        |        | 1111 | 1111                 | 1111 | 1111             |

| 94h                   | SSPSTAT | SMP                              | CKE                               | D/A       | Р          | S          | R/W      | UA     | BF     | 0000 | 0000                 | 0000 | 0000             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### 11.5.1 SLAVE MODE

PIC16C6X

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 11-4 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

#### 11.5.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The

address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 11-16). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT-<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### TABLE 11-4: DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>s Received |                    |                       | Set bit SSPIF                        |

|----|--------------------------|--------------------|-----------------------|--------------------------------------|

| BF | SSPOV                    | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |

| 0  | 0                        | Yes                | Yes                   | Yes                                  |

| 1  | 0                        | No                 | No                    | Yes                                  |

| 1  | 1                        | No                 | No                    | Yes                                  |

| 0  | 1                        | No                 | No                    | Yes                                  |

Г

#### FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                | R/W-0                       | R/W-0          | U-0         | R-0          | R-0          | R-x         |                    |                                                                                                                               |

|--------|----------------------------------------------------------------------|-----------------------------|----------------|-------------|--------------|--------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                  | SREN                        | CREN           | —           | FERR         | OERR         | RX9D        | R                  | = Readable bit                                                                                                                |

| bit7   |                                                                      |                             |                |             |              |              | bitO        | W<br>U<br>- n<br>x | <ul> <li>Writable bit</li> <li>Unimplemented</li> <li>bit, read as '0'</li> <li>Value at POR rese</li> <li>unknown</li> </ul> |

| bit 7: | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p             | s RC7/RX/l                  | DT and RC<br>d | 6/TX/CK     | pins as seri | al port pins | s when bits | TRIS               | C<7:6> are set)                                                                                                               |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion          |             |              |              |             |                    |                                                                                                                               |

| bit 5: | SREN: Sing                                                           | gle Receiv                  | e Enable bi    | t           |              |              |             |                    |                                                                                                                               |

|        | Asynchrone<br>Don't care                                             | ous mode                    |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{Synchronof}{1 = Enables}$ $0 = Disables$ This bit is c        | s single ree<br>s single re | ceive<br>ceive | is comple   | ete.         |              |             |                    |                                                                                                                               |

|        | Synchrono<br>Unused in t                                             |                             | <u>slave</u>   |             |              |              |             |                    |                                                                                                                               |

| bit 4: | CREN: Cor                                                            | ntinuous R                  | eceive Ena     | ble bit     |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Asynchrono}}{1 = \text{Enable}}$ $0 = \text{Disable}$   | s continuo                  |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Synchronor}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                | until enabl | le bit CREN  | l is cleared | (CREN ov    | erride             | s SREN)                                                                                                                       |

| bit 3: | Unimplem                                                             | ented: Rea                  | ad as '0'      |             |              |              |             |                    |                                                                                                                               |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                | ed by rea   | ding RCRE    | G register   | and receive | e next             | valid byte)                                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                | d by clea   | ring bit CRI | EN)          |             |                    |                                                                                                                               |

| bit 0: | <b>RX9D</b> : 9th                                                    |                             |                |             |              |              |             |                    |                                                                                                                               |

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|------------------------------|-------|-------|-------|-------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>         | (2)   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                         | RX9   | SREN  | CREN  | _     | FERR   | OERR   | RX9D      | 0000 -00x               | 0000 -00x                       |

| 1Ah     | RCREG | USART Receive Register       |       |       |       |       |        |        | 0000 0000 | 0000 0000               |                                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>         | (2)   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                         | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |       |       |       |       |        |        | 0000 0000 | 0000 0000               |                                 |

#### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: PSPIE and PSPIF are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|------------------------------|-------|-------|-------|-------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>         | (2)   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                         | RX9   | SREN  | CREN  | _     | FERR   | OERR      | RX9D      | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Transmit Register      |       |       |       |       |        | 0000 0000 | 0000 0000 |                         |                                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>         | (2)   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                         | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |       |       |       |       |        | 0000 0000 | 0000 0000 |                         |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### Value on Value on Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. all other BOR Resets PSPIF<sup>(1)</sup> 0Ch PIR1 RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000 (2) 18h RCSTA SPEN RX9 SREN CREN FFRR OFBB 0000 -00x 0000 -00x RX9D 0000 0000 0000 0000 1Ah RCREG USART Receive Register PSPIE<sup>(1)</sup> CCP1IE 0000 0000 0000 0000 8Ch PIE1 RCIE TXIE SSPIE TMR2IE TMR1IE (2) 0000 -010 0000 -010 98h TXSTA CSRC BRGH TRMT TX9D TX9 TXEN SYNC \_ 0000 0000 0000 0000 SPBRG 99h Baud Rate Generator Register

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

# PIC16C6X

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

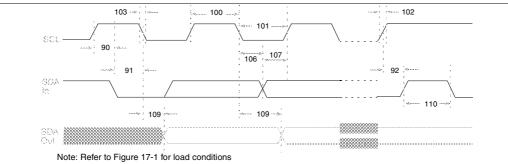

#### FIGURE 17-10: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 17-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Тнідн   | Clock high time        | 100 kHz mode | 4.0        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     |      |       |                                                  |

| 102              | TR      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        |      | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | —          | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

## PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

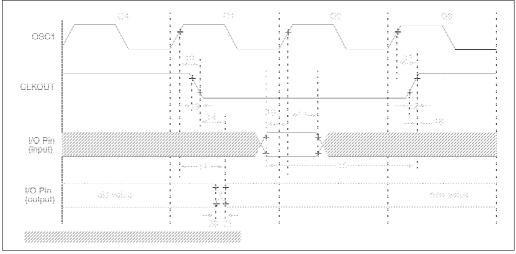

#### FIGURE 18-3: CLKOUT AND I/O TIMING

#### **CLKOUT AND I/O TIMING REQUIREMENTS TABLE 18-3:**

| Parameters | Sym      | Characteristic                                                        |                                     | Min        | Typ† | Max         | Units  | Conditions |

|------------|----------|-----------------------------------------------------------------------|-------------------------------------|------------|------|-------------|--------|------------|

| 10*        | TosH2ckL | OSC1↑ to CLKOUT↓                                                      |                                     | -          | 75   | 200         | ns     | Note 1     |

| 11*        | TosH2ckH | OSC1↑ to CLKOUT↑                                                      | _                                   | 75         | 200  | ns          | Note 1 |            |

| 12*        | TckR     | CLKOUT rise time                                                      | _                                   | 35         | 100  | ns          | Note 1 |            |

| 13*        | TckF     | CLKOUT fall time                                                      |                                     | _          | 35   | 100         | ns     | Note 1     |

| 14*        | TckL2ioV | CLKOUT ↓ to Port out valid                                            |                                     | _          | _    | 0.5TCY + 20 | ns     | Note 1     |

| 15*        | TioV2ckH | Port in valid before CLKOUT $\uparrow$                                |                                     | Tosc + 200 | _    | _           | ns     | Note 1     |

| 16*        | TckH2iol | Port in hold after CLKOUT $\uparrow$                                  |                                     | 0          | _    | _           | ns     | Note 1     |

| 17*        | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out va                           | lid                                 | —          | 50   | 150         | ns     |            |

| 18*        | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | 100        | _    | —           | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | 200        | _    | _           | ns     |            |

| 19*        | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in                         | setup time)                         | 0          | _    | _           | ns     |            |

| 20*        | TioR     | Port output rise time                                                 | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | —          | 10   | 40          | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | _          | _    | 80          | ns     |            |

| 21*        | TioF     | Port output fall time                                                 | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | —          | 10   | 40          | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | _          | -    | 80          | ns     |            |

| 22††*      | Tinp     | RB0/INT pin high or low time                                          |                                     | Тсү        | _    | _           | ns     |            |

| 23††*      | Trbp     | RB7:RB4 change int high or low                                        | Тсү                                 | —          | —    | ns          |        |            |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**††** These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x TOSC.

### PIC16C6X

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 22.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                    | 3. TCC:ST      | (I <sup>2</sup> C specifications only)                                    |

|-----------------------|---------------------------------------|----------------|---------------------------------------------------------------------------|

| 2. TppS               |                                       | 4. Ts          | (I <sup>2</sup> C specifications only)                                    |

| т                     |                                       |                |                                                                           |

| F                     | Frequency                             | Т              | Time                                                                      |

| Lowerca               | se letters (pp) and their meanings:   |                |                                                                           |

| рр                    |                                       |                |                                                                           |

| CC                    | CCP1                                  | OSC            | OSC1                                                                      |

| ck                    |                                       | rd             | RD                                                                        |

| CS                    | CS                                    | rw             | RD or WR                                                                  |

| di                    | SDI                                   | SC             | SCK                                                                       |

| do                    | SDO                                   | SS             | SS                                                                        |

| dt                    | Data in                               | tO             | TOCKI                                                                     |

| io                    | I/O port                              | t1             | T1CKI                                                                     |

| mc                    | MCLR                                  | wr             | WR                                                                        |

|                       | se letters and their meanings:        |                |                                                                           |

| S                     |                                       | _              |                                                                           |

| F                     | Fall                                  | Р              | Period                                                                    |

| Н                     | High                                  | R              | Rise                                                                      |

| 1                     | Invalid (Hi-impedance)                | V              | Valid                                                                     |

| L                     | Low                                   | Z              | Hi-impedance                                                              |

| I <sup>2</sup> C only |                                       |                |                                                                           |

| AA                    | output access                         | High           | High                                                                      |

| BUF                   | Bus free                              | Low            | Low                                                                       |

| TCC:ST (              | I <sup>2</sup> C specifications only) |                |                                                                           |

| CC                    |                                       |                |                                                                           |

| HD                    | Hold                                  | SU             | Setup                                                                     |

| ST                    |                                       |                |                                                                           |

| DAT                   | DATA input hold                       | STO            | STOP condition                                                            |

| STA                   | START condition                       |                |                                                                           |

| FIGURE 2              | 2-1: LOAD CONDITIONS FOR D            | EVICE TIMING S | PECIFICATIONS                                                             |

|                       | Load condition 1                      |                | Load condition 2                                                          |

|                       |                                       |                |                                                                           |

|                       | VDD/2                                 |                |                                                                           |

|                       | J                                     |                |                                                                           |

|                       | $\gtrsim$ RL                          | F              |                                                                           |

|                       | $\sim$                                |                | *                                                                         |

|                       | •                                     |                | Vss                                                                       |

|                       |                                       | RL = 464Ω      |                                                                           |

|                       | +                                     |                |                                                                           |

|                       | Vss                                   |                | for all pins except OSC2/CLKOUT<br>but including D and E outputs as ports |

| Note 1:               | PORTD and PORTE are not imple-        |                | • • •                                                                     |

|                       | mented on the PIC16C66.               | 15 pF          | for OSC2 output                                                           |

|                       |                                       | -              |                                                                           |

-