Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

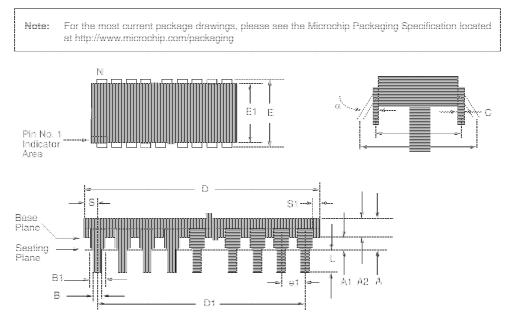

| Mounting Type              | Surface Mount                                                             |

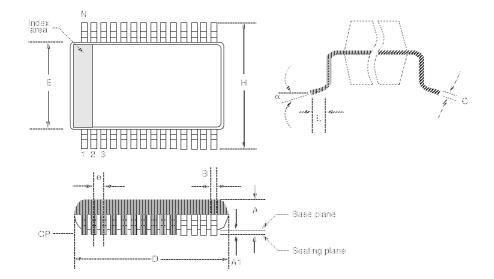

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c67-20i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC16C6X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C6X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C6X family of devices, there are four device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**64. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC64. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**64. These devices have ROM program memory and operate over the standard voltage range.

- 4. LCR, as in PIC16LCR64. These devices have ROM program memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C6X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

ROM devices do not allow serialization information in the program memory space. The user may have this information programmed in the data memory space.

For information on submitting ROM code, please contact your regional sales office.

### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

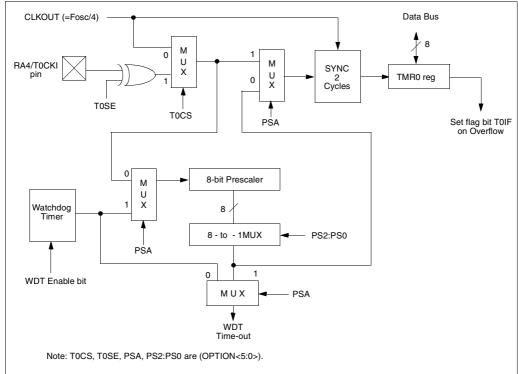

#### 7.3 Prescaler

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF TMR0, MOVWF TMR0, BSF TMR0, bitx) will clear the prescaler count. When assigned to the Watchdog Timer, a CLRWDT instruction will clear the Watchdog Timer and the prescaler count. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## 8.0 TIMER1 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

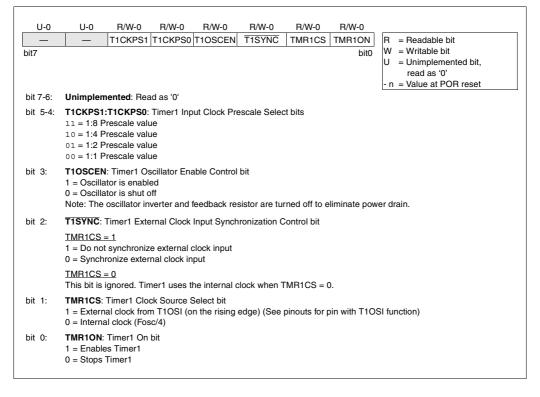

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

#### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

#### 8.5 <u>Resetting Timer1 using a CCP Trigger</u> Output

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

CCP2 is implemented on the PIC16C63/R63/65/65A/ R65/66/67 only.

If CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCPxM3:CCPxM0 = 1011), this signal will reset Timer1.

Note: The "special event trigger" from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF(PIR1<0>).

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If the Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for the Timer1 module.

#### 8.6 <u>Resetting of TMR1 Register Pair</u> (TMR1H:TMR1L)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR1H and TMR1L registers are not reset to 00h on a POR or any other reset except by the CCP1 or CCP2 special event trigger.

The T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescaler. In all other resets, the register is unaffected.

#### 8.7 <u>Timer1 Prescaler</u>

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address              | Name   | Bit 7                | Bit 6   | Bit 5               | Bit 4               | Bit 3          | Bit 2       | Bit 1       | Bit 0  | Value<br>PC<br>BC | ,    | all c | e on<br>other<br>sets |

|----------------------|--------|----------------------|---------|---------------------|---------------------|----------------|-------------|-------------|--------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON | GIE                  | PEIE    | TOIE                | INTE                | RBIE           | TOIF        | INTF        | RBIF   | 0000              | 000x | 0000  | 000u                  |

| 0Ch                  | PIR1   | PSPIF <sup>(2)</sup> | (3)     | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF          | CCP1IF      | TMR2IF      | TMR1IF | 0000              | 0000 | 0000  | 0000                  |

| 8Ch                  | PIE1   | PSPIE <sup>(2)</sup> | (3)     | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE          | CCP1IE      | TMR2IE      | TMR1IE | 0000              | 0000 | 0000  | 0000                  |

| 0Eh                  | TMR1L  | Holding re           | egister | for the Lea         | st Significar       | nt Byte of the | e 16-bit TN | /R1 registe | er     | xxxx              | xxxx | uuuu  | uuuu                  |

| 0Fh                  | TMR1H  | Holding re           | egister | for the Mos         | t Significan        | t Byte of the  | 16-bit TM   | IR1 registe | r      | xxxx              | xxxx | uuuu  | uuuu                  |

| 10h                  | T1CON  | _                    |         | T1CKPS1             | T1CKPS0             | T1OSCEN        | T1SYNC      | TMR1CS      | TMR10N | 00                | 0000 | uu    | uuuu                  |

#### TABLE 8-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: The USART is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

## 10.0 CAPTURE/COMPARE/PWM (CCP) MODULE(s)

#### Applicable Devices

| 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP1 |

|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|------|

| 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP2 |

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM master/slave duty cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP modules(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### CCP1 module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the *Embedded Control Handbook*, "Using the CCP Modules" (AN594).

#### TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

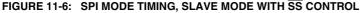

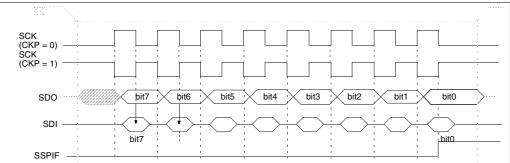

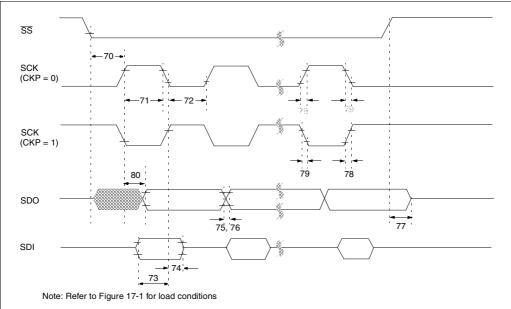

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

| TABLE 11-1: REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Name    | Bit 7                                                        | Bit 6                                                                                                                               | Bit 5                                                                                                                                                                                                                                | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                        | Value on:<br>POR,<br>BOR                                                                                                                                                                                                                                                                                                                                                                                            | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCON  | GIE                                                          | PEIE                                                                                                                                | TOIE                                                                                                                                                                                                                                 | INTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RBIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RBIF                                                                                                                                                                                                                                                                                                                                                                                                         | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIR1    | PSPIF <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIF <sup>(1)</sup>                                                                                                                                                                                                                  | TXIF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIE1    | PSPIE <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIE <sup>(1)</sup>                                                                                                                                                                                                                  | TXIE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR1IE                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPBUF  | Synchrono                                                    | ous Serial                                                                                                                          | Port Rece                                                                                                                                                                                                                            | ive Buffer/                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                              | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                           | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPCON  | WCOL                                                         | SSPOV                                                                                                                               | SSPEN                                                                                                                                                                                                                                | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPM3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM0                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TRISA   | _                                                            |                                                                                                                                     | PORTA Da                                                                                                                                                                                                                             | ta Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                              | 11 1111                                                                                                                                                                                                                                                                                                                                                                                                             | 11 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TRISC   | PORTC D                                                      | ata Directi                                                                                                                         | on Regist                                                                                                                                                                                                                            | er                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SSPSTAT | —                                                            | _                                                                                                                                   | D/A                                                                                                                                                                                                                                  | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BF                                                                                                                                                                                                                                                                                                                                                                                                           | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                             | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | INTCON<br>PIR1<br>PIE1<br>SSPBUF<br>SSPCON<br>TRISA<br>TRISC | INTCON GIE<br>PIR1 PSPIF <sup>(2)</sup><br>PIE1 PSPIE <sup>(2)</sup><br>SSPBUF Synchrond<br>SSPCON WCOL<br>TRISA —<br>TRISC PORTC D | INTCON     GIE     PEIE       PIR1     PSPIF <sup>(2)</sup> (3)       PIE1     PSPIE <sup>(2)</sup> (3)       SSPBUF     Synchronus Serial       SSPCON     WCOL     SSPOV       TRISA     —     —       TRISC     PORTC Data Direct | INTCON         GIE         PEIE         TOIE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> SSPBUF         Synchron-us Serial Port Rece         SSPCON         WCOL         SSPEN           TRISA         —         —         PORTA Da         PORTA Da           TRISC         PORTC Data Direction Register         Portal Direction Register         Portal Direction Register | INTCON         GIE         PEIE         TOIE         INTE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> PIE1         PSPIF <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIF <sup>(1)</sup> PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPBUF         Synchronous         Serial         Port Receive Bufferr           SSPCON         WCOL         SSPOV         SSPEN         CKP           TRISA         —         —         PORTA Data Direction           TRISC         PORTC Data Direction Register         PORTA | INTCON         GIE         PEIE         TOIE         INTE         RBIE           PIR1         PSPIF <sup>(2)</sup> (3)         RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIF           PIE1         PSPIE <sup>(2)</sup> (3)         RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIF           SSPBUF         Synchron-US         Serial         Port Receive Buffer/Transmit         SSPRON           SSPCON         WCOL         SSPOV         SSPEN         CKP         SSPM3           TRISA         —         —         PORTA Data Direction Register         TRISC | INTCON     GIE     PEIE     TOIE     INTE     RBIE     TOIF       PIR1     PSPIF <sup>(2)</sup> <sup>(3)</sup> RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIF     CCP1IF       PIE1     PSPIE <sup>(2)</sup> <sup>(3)</sup> RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIE     CCP1IF       SSPBUF     Synchronous Serial Port Receive Buffer/Transmit Register     SSPR0     WCOL     SSPOV     SSPEN     CKP     SSPM3     SSPM2       TRISA     —     —     PORTA Data Direction Register     TRISC     PORTC Data Direction Register | INTCONGIEPEIETOIEINTERBIETOIFINTFPIR1PSPIF <sup>(2)</sup> <sup>(3)</sup> RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIFCCP1IFTMR2IFPIE1PSPIE <sup>(2)</sup> <sup>(3)</sup> RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIECCP1IETMR2IFSSPBUFSynchronus Serial Port Receive Buffer/Transmit RegisterSSPCONWCOLSSPOVSSPENCKPSSPM3SSPM2SSPM1TRISA——PORTA Data Direction RegisterTRISCPORTC Data Direction Register | INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1PSPIF(2)(3)RCIF(1)TXIF(1)SSPIFCCP1IFTMR2IFTMR1IFPIE1PSPIE(2)(3)RCIE(1)TXIE(1)SSPIECCP1IETMR2IETMR1IESSPBUFSynchron-usSerial Port Receive Buffer/Transmit RegisterSSPR0SSPM2SSPM1SSPM0SSPCONWCOLSSPOVSSPENCKPSSPM3SSPM2SSPM1SSPM0TRISA——PORTA Data Direction RegisterFUNCTION RegisterFUNCTION RegisterTRISCPORTC Data Direction RegisterFUNCTION RegisterFUNCTION Register | Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR,<br>BOR           INTCON         GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 000x           PIR1         PSPIF <sup>(2)</sup> <sup>(3)</sup> RCIF <sup>(1)</sup> TXIF <sup>(1)</sup> SSPIE         CCP1IE         TMR2IF         TMR1IE         0000 0000           PIE1         PSPIE <sup>(2)</sup> <sup>(3)</sup> RCIE <sup>(1)</sup> TXIE <sup>(1)</sup> SSPIE         CCP1IE         TMR2IF         TMR1IE         0000 0000           SSPBUF         Synchro |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

Note 1: These bits are associated with the USART which is implemented on the PIC16C63/R63/65/65A/R65 only.

2: PSPIF and PSPIE are reserved on the PIC16C62/62A/R62/63/R63, always maintain these bits clear.

3: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

Γ

## FIGURE 11-8: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)(PIC16C66/67)

| R/W-0    | R/W-0                                                                                                                    | R/W-0                                                                                                                               | R/W-0                                                                                                                                      | R/W-0                                                                                      | R/W-0                                                                                         | R/W-0                                              | R/W-0                   |                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                    | SSPEN                                                                                                                               | CKP                                                                                                                                        | SSPM3                                                                                      | SSPM2                                                                                         | SSPM1                                              | SSPM0                   | R = Readable bit<br>W = Writable bit                                                                             |

| oit7     |                                                                                                                          |                                                                                                                                     |                                                                                                                                            |                                                                                            |                                                                                               |                                                    | bit0                    | U = Unimplemented bit, rea<br>as '0'<br>- n =Value at POR reset                                                  |

| bit 7:   | WCOL: W<br>1 = The SS<br>(must be c<br>0 = No col                                                                        | SPBUF reg                                                                                                                           | gister is wi                                                                                                                               |                                                                                            | e it is still ti                                                                              | ransmitting                                        | g the previo            | us word                                                                                                          |

| bit 6:   | SSPOV: R                                                                                                                 | eceive Ov                                                                                                                           | erflow Indi                                                                                                                                | cator bit                                                                                  |                                                                                               |                                                    |                         |                                                                                                                  |

|          | the data in<br>if only tran                                                                                              | byte is rece<br>SSPSR is<br>smitting da<br>tion (and t                                                                              | lost. Over<br>ata, to avo                                                                                                                  | flow can c<br>bid setting                                                                  | only occur<br>overflow.                                                                       | in slave m<br>n master                             | ode. The us             | revious data. In case of overflo<br>er must read the SSPBUF, eve<br>verflow bit is not set since eac<br>egister. |

|          | $\frac{\ln l^2 C \mod}{1 = A \text{ byte}}$<br>in transmit<br>0 = No over                                                | is received<br>mode. SS                                                                                                             |                                                                                                                                            |                                                                                            |                                                                                               |                                                    |                         | us byte. SSPOV is a "don't car                                                                                   |

| oit 5:   | SSPEN: S                                                                                                                 | ynchronou                                                                                                                           | is Serial P                                                                                                                                | ort Enable                                                                                 | bit                                                                                           |                                                    |                         |                                                                                                                  |

|          | $\frac{\text{In SPI mod}}{1 = \text{Enable}}$ $0 = \text{Disable}$                                                       | es serial po                                                                                                                        |                                                                                                                                            |                                                                                            |                                                                                               |                                                    | is serial por<br>t pins | t pins                                                                                                           |

|          | 0 = Disable                                                                                                              | es the seria                                                                                                                        | ort and co                                                                                                                                 | nfigures th                                                                                | nese pins a                                                                                   | as I/O port                                        | t pins                  | ial port pins<br>s input or output.                                                                              |

| bit 4:   | <b>CKP</b> : Cloc<br>In SPI mod<br>1 = Idle sta<br>0 = Idle sta<br>In $I^2C$ mod<br>SCK relea<br>1 = Enable<br>0 = Holds | <u>de</u><br>ate for cloc<br>ate for cloc<br><u>de</u><br>se control<br>e clock                                                     | k is a high<br>k is a low                                                                                                                  | level                                                                                      | to ensure                                                                                     | data setu                                          | p time)                 |                                                                                                                  |

| bit 3-0: | $0110 =  ^{2}(0)$ $0111 =  ^{2}(0)$ $1011 =  ^{2}(0)$ $1110 =  ^{2}(0)$                                                  | PI master r<br>PI master r<br>PI master r<br>PI master r<br>PI slave mo<br>CI slave mo<br>CI slave mo<br>CI slave mo<br>CI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock<br>ode, clock<br>de, 7-bit a<br>de, 10-bit<br>controllec<br>de, 7-bit a | k = Fosc/. $k = Fosc/.$ $k = Fosc/.$ $k = TMR2$ $= SCK pir$ $ddress$ $address$ $ddress wi$ | 4<br>64<br>output/2<br>a. <u>SS</u> pin c<br>a. <u>SS</u> pin c<br>node (slave<br>th start an | ontrol ena<br>ontrol disa<br>e idle)<br>d stop bit |                         |                                                                                                                  |

## 11.5 <u>SSP I<sup>2</sup>C Operation</u>

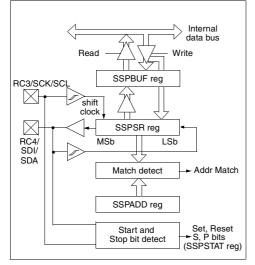

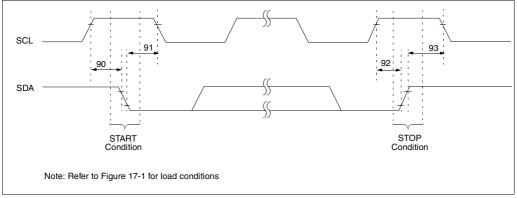

The SSP module in  $I^2C$  mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

#### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

| Register | r Applicable Devices Po |    |     |     |    |     |    | Power-o<br>Browi<br>Res | n-out | MCLR Reset during:<br>– normal operation<br>– SLEEP<br>WDT Reset | Wake-up via<br>interrupt or<br>WDT Wake-up |     |    |    |      |      |           |           |

|----------|-------------------------|----|-----|-----|----|-----|----|-------------------------|-------|------------------------------------------------------------------|--------------------------------------------|-----|----|----|------|------|-----------|-----------|

| TRISD    | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 1111 | 1111 | 1111 1111 | uuuu uuuu |

| TRISE    | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0000 | -111 | 0000 -111 | uuuu -uuu |

| PIE1     | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 00   | 0000 | 00 0000   | uu uuuu   |

|          | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0000 | 0000 | 0000 0000 | uuuu uuuu |

| PIE2     | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 |      | 0    | 0         | u         |

| PCON     | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 |      | 0u   | uu        | uu        |

| FCON     | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 |      | 0-   | u-        | u-        |

| PR2      | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 1111 | 1111 | 1111 1111 | 1111 1111 |

| SSPADD   | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0000 | 0000 | 0000 0000 | uuuu uuuu |

| SSPSTAT  | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0 0  | 0000 | 00 0000   | uu uuuu   |

| TXSTA    | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0000 | -010 | 0000 -010 | uuuu -uuu |

| SPBRG    | 61                      | 62 | 62A | R62 | 63 | R63 | 64 | 64A                     | R64   | 65                                                               | 65A                                        | R65 | 66 | 67 | 0000 | 0000 | 0000 0000 | uuuu uuuu |

#### TABLE 13-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0', q = value depends on condition.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

3: See Table 13-10 and Table 13-11 for reset value for specific conditions.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67