Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I²C, SPI                                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62a-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7              | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                    |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad        | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | -                  | _                  | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat          | ta Latch whe       | n written: PC | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat          | ta Latch whe       | n written: PC | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat          | ta Latch whe       | n written: PC | ORTD pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                    | _                  | _             | _              | _             | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                  | —                  | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                    | _                  | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L    | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the M    | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                    | _                  | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                  | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | is Serial Port     | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                  | —                  | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                | SREN          | CREN           | —             | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai         | nsmit Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red          | ceive Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM          | 2 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM          | 2 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                  | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted               |               |                |               |                 |               |           | —                        | _                                              |

### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

| Address              | Name    | Bit 7                                                    | Bit 6                                        | Bit 5                     | Bit 4          | Bit 3       | Bit 2       | Bit 1        | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------------------------------------------|----------------------------------------------|---------------------------|----------------|-------------|-------------|--------------|--------------------|--------------------------|------------------------------------------------|

| Bank 1               |         |                                                          | •                                            |                           |                |             |             |              |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing                                               | this location                                | uses conte                | nts of FSR to  | address dat | a memory (n | ot a physica | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU                                                     | INTEDG                                       | TOCS                      | T0SE           | PSA         | PS2         | PS1          | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co                                               | rogram Counter's (PC) Least Significant Byte |                           |                |             |             |              | 0000 0000          | 0000 0000                |                                                |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>                                       | RP1 <sup>(5)</sup>                           | RP0                       | TO             | PD          | z           | DC           | С                  | 0001 1xxx                | 000q quui                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data                                            | a memory ac                                  | Idress point              | er             |             |             |              |                    | xxxx xxxx                | սսսս սսսս                                      |

| 85h                  | TRISA   | —                                                        | —                                            | PORTA Da                  | ta Direction R | egister     |             |              |                    | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat                                                | ta Direction F                               | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da                                                 | ta Direction I                               | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | TRISD   | PORTD Da                                                 | ta Direction I                               | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 89h                  | TRISE   | IBF                                                      | OBF                                          | IBOV                      | PSPMODE        | —           | PORTE Da    | ta Direction | Bits               | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH  | Write Buffer for the upper 5 bits of the Program Counter |                                              |                           |                |             |             | 0 0000       | 0 0000             |                          |                                                |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                                                      | E PEIE TOIE INTE RBIE TOIF INTE RBIF         |                           |                |             |             |              | 0000 000x          | 0000 0001                |                                                |

| 8Ch                  | PIE1    | PSPIE                                                    | (6)                                          | RCIE                      | TXIE           | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE             | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                                                        | —                                            | —                         | _              | —           | _           | —            | CCP2IE             | 0                        | (                                              |

| 8Eh                  | PCON    | _                                                        | —                                            | —                         | _              | —           | _           | POR          | BOR <sup>(4)</sup> | dd                       | ui                                             |

| 8Fh                  | -       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | _                        | —                                              |

| 90h                  | _       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | _                        | _                                              |

| 91h                  | _       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | _                        | _                                              |

| 92h                  | PR2     | Timer2 Peri                                              | iod Register                                 |                           |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou                                               | us Serial Por                                | t (I <sup>2</sup> C mode) | Address Reg    | gister      |             |              |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | —                                                        | _                                            | D/A                       | Р              | S           | R/W         | UA           | BF                 | 00 0000                  | 00 0000                                        |

| 95h                  | -       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | -                        | —                                              |

| 96h                  | —       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | -                        | —                                              |

| 97h                  | -       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | -                        | —                                              |

| 98h                  | TXSTA   | CSRC                                                     | TX9                                          | TXEN                      | SYNC           | —           | BRGH        | TRMT         | TX9D               | 0000 -010                | 0000 -010                                      |

| 99h                  | SPBRG   | Baud Rate                                                | Generator R                                  | egister                   |                |             |             |              |                    | 0000 0000                | 0000 0000                                      |

| 9Ah                  | _       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | -                        | —                                              |

| 9Bh                  | _       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | _                        | —                                              |

| 9Ch                  | —       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | —                        | —                                              |

| 9Dh                  | —       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | -                        | —                                              |

| 9Eh                  | —       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    | —                        | _                                              |

| 9Fh                  | _       | Unimpleme                                                | nted                                         |                           |                |             |             |              |                    |                          |                                                |

TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65 (Cont.'d)

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

### 5.6 I/O Programming Considerations

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stavs in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential read-modify-write instructions on an I/O port.

### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| ; |     |         |     |   | PORT | latch | PORT | pins |

|---|-----|---------|-----|---|------|-------|------|------|

| ; |     |         |     |   |      |       |      |      |

| ' | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp | pppp |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | 11pp | pppp |

|   | BSF | STATUS, | RP0 | ; |      |       |      |      |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp | pppp |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp | pppp |

|   |     |         |     |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp pppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

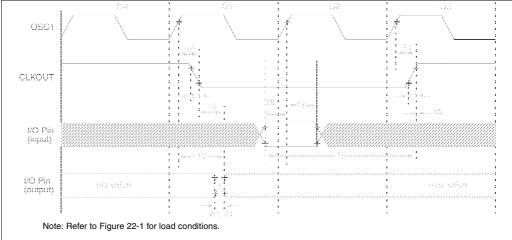

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

| PC                      | X PC                             | X PC + 1                         | X           | PC + 2                   | ( PC + 3 )                                | This example shows a write to POI                                                       |

|-------------------------|----------------------------------|----------------------------------|-------------|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|

| Instruction<br>fetched  | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W                     |             | NOP                      | NOP                                       | followed by a read from PORTB.<br>Note that:                                            |

| RB7:RB0                 | PORTB                            | 1<br>1<br>1                      | X           | <br>                     | ۱<br>ــــــــــــــــــــــــــــــــــــ | data setup time = (0.25TCY - TPD)                                                       |

|                         | 1<br>1<br>1                      | 1<br>1<br>1                      |             | Port pin<br>sampled here |                                           | where TCY = instruction cycle<br>TPD = propagation delay                                |

| Instruction<br>executed |                                  | MOVWF PORTB<br>write to<br>PORTB | - TPD<br>MO | 1                        | NOP                                       | Therefore, at higher clock frequence<br>a write followed by a read may be p<br>lematic. |

|                         | i<br>i                           | i<br>i                           |             | 1                        |                                           |                                                                                         |

### FIGURE 5-10: SUCCESSIVE I/O OPERATION

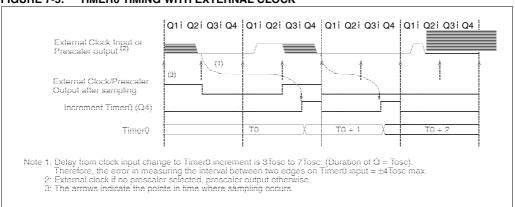

## 7.2 Using Timer0 with External Clock

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

## FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0 R/W-0 R            | /W-0 R/W-0         | R/W-0        | R/W-0         | R/W-0        |                                       |  |  |  |

|----------|------------------------|--------------------|--------------|---------------|--------------|---------------------------------------|--|--|--|

| —        | - CCPxX CC             | CPxY CCPxM3        | CCPxM2       | CCPxM1        | CCPxM0       | R = Readable bit                      |  |  |  |

| bit7     |                        |                    |              |               | bit0         | W = Writable bit                      |  |  |  |

|          |                        |                    |              |               |              | U = Unimplemented bit, read<br>as '0' |  |  |  |

|          |                        |                    |              |               |              | - n =Value at POR reset               |  |  |  |

| bit 7-6: | Unimplemented: F       | Poad as '0'        |              |               |              |                                       |  |  |  |

|          | •                      |                    |              |               |              |                                       |  |  |  |

| bit 5-4: | CCPxX:CCPxY: PV        | VM Least Significa | ant bits     |               |              |                                       |  |  |  |

|          | Capture Mode<br>Unused |                    |              |               |              |                                       |  |  |  |

|          | Compare Mode           |                    |              |               |              |                                       |  |  |  |

|          | Unused                 |                    |              |               |              |                                       |  |  |  |

|          | PWM Mode               |                    |              |               |              |                                       |  |  |  |

|          | These bits are the t   | wo LSbs of the P   | NM duty cy   | cle. The eig  | ht MSbs are  | found in CCPRxL.                      |  |  |  |

| bit 3-0: | CCPxM3:CCPxM0          | : CCPx Mode Sele   | ect bits     |               |              |                                       |  |  |  |

|          | 0000 = Capture/Co      | •                  |              | k module)     |              |                                       |  |  |  |

|          | 0100 = Capture mo      |                    | •            |               |              |                                       |  |  |  |

|          | 0101 = Capture mo      |                    | •            |               |              |                                       |  |  |  |

|          | 0110 = Capture mo      | · ·                | 0 0          |               |              |                                       |  |  |  |

|          | 1000 = Compare m       | · ·                | • •          | CCPxIF is     | set)         |                                       |  |  |  |

|          | 1001 = Compare m       |                    | •            |               | ,            |                                       |  |  |  |

|          | •                      |                    | •            |               | ,            | is set, CCPx pin is unaffected)       |  |  |  |

|          | •                      |                    | al event (CC | PxIF bit is s | et; CCP1 res | ets TMR1; CCP2 resets TMR1)           |  |  |  |

|          | 11xx = PWM mode        | 9                  |              |               |              |                                       |  |  |  |

|          |                        |                    |              |               |              |                                       |  |  |  |

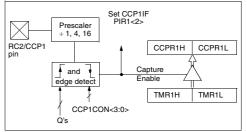

### 10.1 Capture Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

## 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an   |

|-------|-------------------------------------------|

|       | output, a write to PORTC can cause a cap- |

|       | ture condition.                           |

# FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work consistently.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture event is changed, a false capture interrupt may be generated. The user should clear enable bit CCP1IE (PIE1<2>) to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

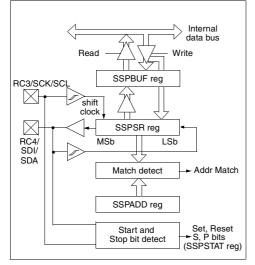

# 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in  $I^2C$  mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

## FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

NOTES:

-

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                                                                                        | IORLW             | Inclusive OR Literal with W                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [label] INCFSZ f,d                                                                                                                                                                                                                                                                            | Syntax:           | [label] IORLW k                                                               |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                                                                                             | Operands:         | $0 \le k \le 255$                                                             |

|                   | d ∈ [0,1]                                                                                                                                                                                                                                                                                     | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                  |

| Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                    | Status Affected:  | Z                                                                             |

| Status Affected:  | None                                                                                                                                                                                                                                                                                          | Encoding:         | 11 1000 kkkk kkkk                                                             |

| Encoding:         | 00 1111 dfff ffff                                                                                                                                                                                                                                                                             | Description:      | The contents of the W register is                                             |

| Description:      | The contents of register 'f' are incre-                                                                                                                                                                                                                                                       |                   | OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Description.      | mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is                                                                                                                                                                                                      | Words:            | 1                                                                             |

|                   | placed back in register 'f'.<br>If the result is 1, the next instruction is                                                                                                                                                                                                                   | Cycles:           | 1                                                                             |

|                   | executed. If the result is 0, a NOP is exe-<br>cuted instead making it a 2TCY instruc-                                                                                                                                                                                                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

|                   | tion.                                                                                                                                                                                                                                                                                         |                   | Decode Read Process Write to literal 'k' data W                               |

| Words:            | 1                                                                                                                                                                                                                                                                                             |                   |                                                                               |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                          | Example           | IORLW 0x35                                                                    |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                   | ·                 | Before Instruction                                                            |

|                   | Decode Read Process Write to<br>register 'f' data destination                                                                                                                                                                                                                                 |                   | W = 0x9A                                                                      |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                   |                   | After Instruction<br>W = 0xBF                                                 |

| ii enipi          | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |                   | Z = 1                                                                         |

|                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                                                                                              |                   |                                                                               |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•                                                                                                                                                                                                                                              |                   |                                                                               |

|                   | $\begin{array}{rcl} Before \mbox{ Instruction} & PC & = & \mbox{ address HERE} \\ After \mbox{ Instruction} & \\ CNT & = & CNT + 1 & \\ \mbox{ if } CNT = & 0, & \\ PC & = & \mbox{ address CONTINUE} & \\ \mbox{ if } CNT \neq & 0, & \\ PC & = & \mbox{ address HERE } +1 & \\ \end{array}$ |                   |                                                                               |

#### SLEEP

| Syntax:           | [ label ]                                                                                                                                                                                                                                        | SLEEP            |                  |                |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------|--|--|--|--|

| Operands:         | None                                                                                                                                                                                                                                             |                  |                  |                |  |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \mbox{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                       |                  |                  |                |  |  |  |  |

| Status Affected:  | TO, PD                                                                                                                                                                                                                                           |                  |                  |                |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                               | 0000             | 0110             | 0011           |  |  |  |  |

| Description:      | The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. See<br>Section 13.8 for more details. |                  |                  |                |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                |                  |                  |                |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                |                  |                  |                |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                               | Q2               | Q3               | Q4             |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                           | No-<br>Operation | No-<br>Operation | Go to<br>Sleep |  |  |  |  |

| Example:          | SLEEP                                                                                                                                                                                                                                            |                  |                  |                |  |  |  |  |

|                   |                                                                                                                                                                                                                                                  |                  |                  |                |  |  |  |  |

| SUBLW             | Subtract                   | W from              | _iteral                                      |              |  |  |  |

|-------------------|----------------------------|---------------------|----------------------------------------------|--------------|--|--|--|

| Syntax:           | [ label ]                  | SUBLW               | k                                            |              |  |  |  |

| Operands:         | $0 \le k \le 255$          |                     |                                              |              |  |  |  |

| Operation:        | $k \text{ - } (W) \to (W)$ |                     |                                              |              |  |  |  |

| Status Affected:  | C, DC, Z                   |                     |                                              |              |  |  |  |

| Encoding:         | 11                         | 110x                | kkkk                                         | kkkk         |  |  |  |

| Description:      | ment meth                  | od) from th         | otracted (2's<br>ne eight bit<br>n the W reg | literal 'k'. |  |  |  |

| Words:            | 1                          |                     |                                              |              |  |  |  |

| Cycles:           | 1                          |                     |                                              |              |  |  |  |

| Q Cycle Activity: | Q1                         | Q2                  | Q3                                           | Q4           |  |  |  |

|                   | Decode                     | Read<br>literal 'k' | Process<br>data                              | Write to W   |  |  |  |

| Example 1:        | SUBLW                      | 0x02                |                                              |              |  |  |  |

|                   | Before Ins                 | struction           |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 1<br>?<br>?                                  |              |  |  |  |

|                   | After Instr                | ruction             |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 1<br>1; result is<br>0                       | positive     |  |  |  |

| Example 2:        | Before Ins                 | struction           |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 2<br>?<br>?                                  |              |  |  |  |

|                   | After Instr                | ruction             |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 0<br>1; result i<br>1                        | s zero       |  |  |  |

| Example 3:        | Before Ins                 | struction           |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 3<br>?<br>?                                  |              |  |  |  |

|                   | After Inst                 | ruction             |                                              |              |  |  |  |

|                   |                            | W =<br>C =<br>Z =   | 0xFF<br>0; result is<br>0                    | negative     |  |  |  |

-

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 17.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | S                                      | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------|----------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                        | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                        |           |                                        |

| F                     | Frequency                              | Т         | Time                                   |

| Lowercas              | se letters (pp) and their meanings:    |           |                                        |

| рр                    |                                        |           |                                        |

| сс                    | CCP1                                   | OSC       | OSC1                                   |

| ck                    | CLKOUT                                 | rd        | RD                                     |

| CS                    | CS                                     | rw        | RD or WR                               |

| di                    | SDI                                    | SC        | SCK                                    |

| do                    | SDO                                    | SS        | SS                                     |

| dt                    | Data in                                | tO        | TOCKI                                  |

| io                    | I/O port                               | t1        | T1CKI                                  |

| mc                    | MCLR                                   | wr        | WR                                     |

| 1                     | se letters and their meanings:         |           |                                        |

| S                     |                                        |           |                                        |

| F                     | Fall                                   | Р         | Period                                 |

| Н                     | High                                   | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                 | V         | Valid                                  |

| L                     | Low                                    | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                        |           |                                        |

| AA                    | output access                          | High      | High                                   |

| BUF                   | Bus free                               | Low       | Low                                    |

| TCC:ST (l             | <sup>2</sup> C specifications only)    |           |                                        |

| CC                    |                                        |           |                                        |

| HD                    | Hold                                   | SU        | Setup                                  |

| ST                    |                                        |           |                                        |

| DAT                   | DATA input hold                        | STO       | STOP condition                         |

| STA                   | START condition                        |           |                                        |

| FIGURE 17             | 7-1: LOAD CONDITIONS FOR DEVICE        | TIMING SP | ECIFICATIONS                           |

|                       | Load condition 1 VDD/2                 |           | Load condition 2                       |

|                       | Ŷ                                      |           |                                        |

|                       | SRL                                    |           | $\checkmark$                           |

|                       | $\leq$ "                               |           |                                        |

|                       |                                        | F         |                                        |

|                       |                                        |           | ▼                                      |

|                       | Pin CL                                 |           | Vss                                    |

|                       | v<br>Vss                               |           |                                        |

| RL = 464              |                                        | No        | ote 1: PORTD and PORTE are not imple-  |

| CL = 50               | pF for all pins except OSC2/CLKOUT     |           | mented on the PIC16C62.                |

| 02 - 50               | but including D and E outputs as ports |           |                                        |

| 15                    |                                        |           |                                        |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

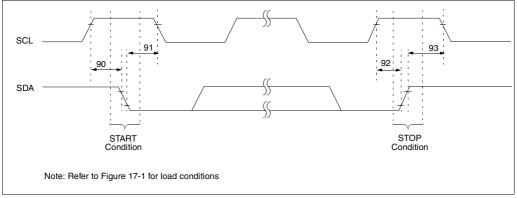

# FIGURE 17-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

# TABLE 17-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | -     | Only relevant for repeated START  |  |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | —   | ns    | condition                         |  |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   |       | After this period the first clock |  |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | —   | ns    | pulse is generated                |  |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | _   | _   |       |                                   |  |

|                  |         | Setup time      | 400 kHz mode | 600  |     | _   | ns    |                                   |  |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | _   | _   |       |                                   |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | ns    |                                   |  |

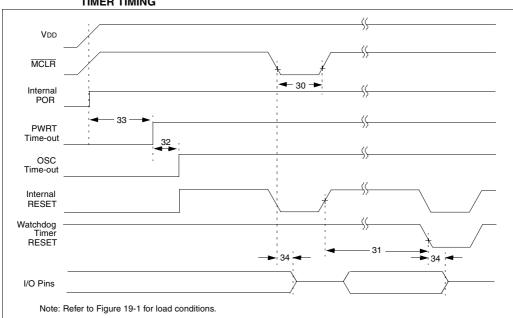

# FIGURE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                     | Min | Тур†     | Max | Units | Conditions                                        |

|------------------|-------|----------------------------------------------------|-----|----------|-----|-------|---------------------------------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                             | 100 | —        | —   | ns    | VDD = 5V, -40°C to +85°C                          |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)   | 7   | 18       | 33  | ms    | $VDD = 5V$ , $-40^{\circ}C$ to $+85^{\circ}C$     |

| 32               | Tost  | Oscillation Start-up Timer Period                  | —   | 1024Tosc | _   | —     | TOSC = OSC1 period                                |

| 33*              | Tpwrt | Power-up Timer Period or WDT reset                 | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34               | Tioz  | I/O Hi-impedance from $\overline{\text{MCLR}}$ Low | _   | —        | 100 | ns    |                                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 21.3 DC Characteristics: PIC16CR63/R65-04 (Commercial, Industrial) PIC16CR63/R65-10 (Commercial, Industrial) PIC16CR63/R65-20 (Commercial, Industrial) PIC16LCR63/R65-04 (Commercial, Industrial)

|              |                                    |                     | rd Operat |          |                   |       | ss otherwise stated)<br>$A \le +85^{\circ}C$ for industrial and    |

|--------------|------------------------------------|---------------------|-----------|----------|-------------------|-------|--------------------------------------------------------------------|

| DC CHA       | RACTERISTICS                       | Operatir<br>Section |           | Vdd      | 0°C<br>range as o |       | $A \le +70^{\circ}C$ for commercial ed in DC spec Section 21.1 and |

| Param<br>No. | Characteristic                     | Sym                 | Min       | Тур<br>† | Мах               | Units | Conditions                                                         |

|              | Input Low Voltage                  |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | VIL                 |           |          |                   |       |                                                                    |

| D030         | with TTL buffer                    |                     | Vss       | -        | 0.15Vdd           | v     | For entire VDD range                                               |

| D030A        |                                    |                     | Vss       | -        | 0.8V              | v     | $4.5V \le VDD \le 5.5V$                                            |

| D031         | with Schmitt Trigger buffer        |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D032         | MCLR, OSC1 (in RC mode)            |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D033         | OSC1 (in XT, HS and LP)            |                     | Vss       | -        | 0.3VDD            | v     | Note1                                                              |

|              | Input High Voltage                 |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | VIH                 |           | -        |                   |       |                                                                    |

| D040         | with TTL buffer                    |                     | 2.0       | -        | Vdd               | v     | $4.5V \le V$ DD $\le 5.5V$                                         |

| D040A        |                                    |                     | 0.25VDD   | -        | Vdd               | v     | For entire VDD range                                               |

|              |                                    |                     | + 0.8V    |          |                   |       |                                                                    |

| D041         | with Schmitt Trigger buffer        |                     | 0.8VDD    | -        | Vdd               | v     | For entire VDD range                                               |

| D042         | MCLR                               |                     | 0.8VDD    | -        | Vdd               | V     |                                                                    |

| D042A        | OSC1 (XT, HS and LP)               |                     | 0.7Vdd    | -        | Vdd               | V     | Note1                                                              |

| D043         | OSC1 (in RC mode)                  |                     | 0.9Vdd    | -        | Vdd               | V     |                                                                    |

| D070         | PORTB weak pull-up current         | IPURB               | 50        | 250      | 400               | μΑ    | VDD = 5V, VPIN = VSS                                               |

|              | Input Leakage Current (Notes 2, 3) |                     |           |          |                   |       |                                                                    |

| D060         | I/O ports                          | lı∟                 | -         | -        | ±1                | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance                |

| D061         | MCLR, RA4/T0CKI                    |                     | -         | -        | ±5                | μA    | $Vss \le VPIN \le VDD$                                             |

| D063         | OSC1                               |                     | -         | -        | ±5                | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and                             |

|              |                                    |                     |           |          |                   |       | LP osc configuration                                               |

|              | Output Low Voltage                 |                     |           |          |                   |       | -                                                                  |

| D080         | I/O ports                          | Vol                 | -         | -        | 0.6               | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

| D083         | OSC2/CLKOUT (RC osc config)        |                     | -         | -        | 0.6               | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

|              | Output High Voltage                |                     |           |          |                   |       |                                                                    |

| D090         | I/O ports (Note 3)                 | Vон                 | VDD-0.7   | -        | -                 | v     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                       |

| D092         | OSC2/CLKOUT (RC osc config)        |                     | VDD-0.7   | -        | -                 | v     | IOH = -1.3  mA,  VDD = 4.5 V,<br>-40°C to +85°C                    |

| D150*        | Open-Drain High Voltage            | Vod                 | -         | -        | 14                | V     | RA4 pin                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 21.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                     | 3. Tcc:st  | (I <sup>2</sup> C specifications only)                                    |

|-----------------------|----------------------------------------|------------|---------------------------------------------------------------------------|

| 2. TppS               |                                        | 4. Ts      | (I <sup>2</sup> C specifications only)                                    |

| т                     |                                        |            |                                                                           |

| F                     | Frequency                              | Т          | Time                                                                      |

| Lowerca               | ase letters (pp) and their meanings:   | ш          |                                                                           |

| рр                    |                                        |            |                                                                           |

| сс                    | CCP1                                   | osc        | OSC1                                                                      |

| ck                    | CLKOUT                                 | rd         | RD                                                                        |

| cs                    | CS                                     | rw         | RD or WR                                                                  |

| di                    | SDI                                    | sc         | SCK                                                                       |

| do                    | SDO                                    | ss         | SS                                                                        |

| dt                    | Data in                                | tO         | TOCKI                                                                     |

| io                    | I/O port                               | t1         | T1CKI                                                                     |

| mc                    | MCLR                                   | wr         | WR                                                                        |

| Upperca               | ase letters and their meanings:        |            |                                                                           |

| S                     | -                                      |            |                                                                           |

| F                     | Fall                                   | Р          | Period                                                                    |

| н                     | High                                   | R          | Rise                                                                      |

| I                     | Invalid (Hi-impedance)                 | v          | Valid                                                                     |

| L                     | Low                                    | z          | Hi-impedance                                                              |

| I <sup>2</sup> C only |                                        |            |                                                                           |

| AA                    | output access                          | High       | High                                                                      |

| BUF                   | Bus free                               | Low        | Low                                                                       |

|                       | (I <sup>2</sup> C specifications only) | 2011       |                                                                           |

| CC                    |                                        |            |                                                                           |

| HD                    | Hold                                   | SU         | Setup                                                                     |

| ST                    | Tiold                                  | 30         | Selup                                                                     |

| DAT                   | DATA input hold                        | STO        | STOP condition                                                            |