#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62a-04-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

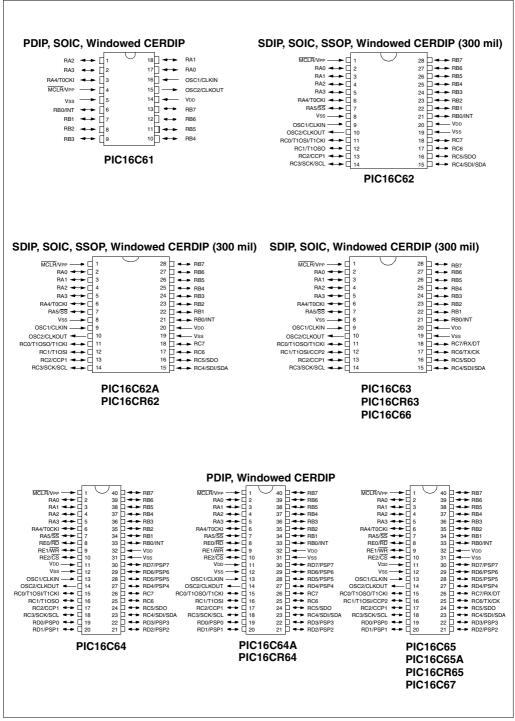

#### **Pin Diagrams**

# TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

#### **TABLE 3-3:** PIC16C64/64A/R64/65/65A/R65/67 PINOUT DESCRIPTION

| Pin Name                                      | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>MQFP<br>Pin# | Pin<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                        |

|-----------------------------------------------|-------------|--------------|----------------------|-------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN                                    | 13          | 14           | 30                   | Ι           | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                              |

| OSC2/CLKOUT                                   | 14          | 15           | 31                   | 0           | _                      | Oscillator crystal output. Connects to crystal or resonator in<br>crystal oscillator mode. In RC mode, the pin outputs CLK-<br>OUT which has 1/4 the frequency of OSC1, and denotes the<br>instruction cycle rate. |

| MCLR/VPP                                      | 1           | 2            | 18                   | I/P         | ST                     | Master clear reset input or programming voltage input. This                                                                                                                                                        |

|                                               |             |              |                      |             |                        | pin is an active low reset to the device.                                                                                                                                                                          |

|                                               |             |              |                      |             |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                |

| RA0                                           | 2           | 3            | 19                   | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RA1                                           | 3           | 4            | 20                   | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RA2                                           | 4           | 5            | 21                   | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RA3                                           | 5           | 6            | 22                   | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RA4/T0CKI                                     | 6           | 7            | 23                   | I/O         | ST                     | RA4 can also be the clock input to the Timer0<br>timer/counter. Output is open drain type.                                                                                                                         |

| RA5/SS                                        | 7           | 8            | 24                   | I/O         | TTL                    | RA5 can also be the slave select for the synchronous<br>serial port.                                                                                                                                               |

|                                               |             |              |                      |             |                        | PORTB is a bi-directional I/O port. PORTB can be software<br>programmed for internal weak pull-up on all inputs.                                                                                                   |

| RB0/INT                                       | 33          | 36           | 8                    | I/O         | TTL/ST <sup>(4)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                        |

| RB1                                           | 34          | 37           | 9                    | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RB2                                           | 35          | 38           | 10                   | I/O         | TTL                    |                                                                                                                                                                                                                    |

| RB3                                           | 36          | 39           | 11                   | 1/0         | TTL                    |                                                                                                                                                                                                                    |

| RB4                                           | 37          | 41           | 14                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                           |

| RB5                                           | 38          | 42           | 15                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                           |

| RB6                                           | 39          | 43           | 16                   | 1/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                                 |

| RB7                                           | 40          | 44           | 17                   | 1/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                                  |

|                                               | 10          |              |                      | 1/0         | 112/01                 | PORTC is a bi-directional I/O port.                                                                                                                                                                                |

| RC0/T1OSO <sup>(1)</sup> /T1CKI               | 15          | 16           | 32                   | I/O         | ST                     | RC0 can also be the Timer1 oscillator output <sup>(1)</sup> or Timer1 clock input.                                                                                                                                 |

| RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> | 16          | 18           | 35                   | I/O         | ST                     | RC1 can also be the Timer1 oscillator input <sup>(1)</sup> or<br>Capture2 input/Compare2 output/PWM2 output <sup>(2)</sup> .                                                                                       |

| RC2/CCP1                                      | 17          | 19           | 36                   | I/O         | ST                     | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                               |

| RC3/SCK/SCL                                   | 18          | 20           | 37                   | I/O         | ST                     | RC3 can also be the synchronous serial clock input/out-<br>put for both SPI and I <sup>2</sup> C modes.                                                                                                            |

| RC4/SDI/SDA                                   | 23          | 25           | 42                   | I/O         | ST                     | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^{2}C$ mode).                                                                                                                                         |

| RC5/SDO                                       | 24          | 26           | 43                   | I/O         | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                       |

| RC6/TX/CK <sup>(2)</sup>                      | 25          | 27           | 44                   | I/O         | ST                     | RC6 can also be the USART Asynchronous Transmit <sup>(2)</sup><br>or Synchronous Clock <sup>(2)</sup> .                                                                                                            |

| RC7/RX/DT <sup>(2)</sup>                      | 26          | 29           | 1                    | I/O         | ST                     | RC7 can also be the USART Asynchronous Receive <sup>(2)</sup> or Synchronous Data <sup>(2)</sup> .                                                                                                                 |

| Legend: I = input C                           | D = outp    | ut           | I/C                  | D = input   | /output                | P = power                                                                                                                                                                                                          |

— = Not used TTL = TTL input

ST = Schmitt Trigger input Note 1: Pin functions T1OSO and T1OSI are reversed on the PIC16C64.

2: CCP2 and the USART are not available on the PIC16C64/64A/R64.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: This buffer is a Schmitt Trigger input when configured as the external interrupt.

5: This buffer is a Schmitt Trigger input when used in serial programming mode.

6: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

#### 5.5 PORTE and TRISE Register

# Applicable Devices

## 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTE has three pins, RE2/CS, RE1/WR, and RE0/RD which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). In this mode the input buffers are TTL.

Figure 5-9 shows the TRISE register, which controls the parallel slave port operation and also controls the direction of the PORTE pins.

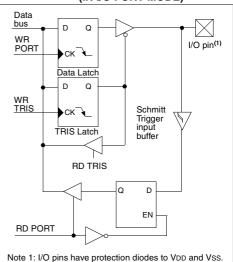

#### FIGURE 5-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

#### FIGURE 5-9: TRISE REGISTER (ADDRESS 89h)

| R-0     | R-0                                            | R/W-0       | R/W-0                                             | U-0          | R/W-1        | R/W-1   | R/W-1        |                                                                                                                        |

|---------|------------------------------------------------|-------------|---------------------------------------------------|--------------|--------------|---------|--------------|------------------------------------------------------------------------------------------------------------------------|

| IBF     | OBF                                            | IBOV        | PSPMODE                                           | _            | bit2         | bit1    | bit0         | R = Readable bit                                                                                                       |

| bit7    |                                                |             |                                                   |              |              |         | bit0         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7 : | <b>IBF:</b> Input<br>1 = A word<br>0 = No wor  | has been    | received and                                      | is waiting t | o be read by | the CPU |              |                                                                                                                        |

| bit 6:  | 1 = The ou                                     | tput buffer | ull Status bit<br>still holds a p<br>has been rea |              | ritten word  |         |              |                                                                                                                        |

| bit 5:  |                                                | occurred    |                                                   |              |              |         | (must be cle | ared in software)                                                                                                      |

| bit 4:  | PSPMODE<br>1 = Paralle<br>0 = Genera           | I slave por |                                                   | de Select t  | bit          |         |              |                                                                                                                        |

| bit 3:  | Unimplem                                       | ented: Re   | ad as '0'                                         |              |              |         |              |                                                                                                                        |

|         | PORTE D                                        | ata Direc   | tion Bits                                         |              |              |         |              |                                                                                                                        |

| bit 2:  | <b>Bit2</b> : Direc<br>1 = Input<br>0 = Output |             | ol bit for pin Rl                                 | E2/CS        |              |         |              |                                                                                                                        |

| bit 1:  | <b>Bit1</b> : Direc<br>1 = Input<br>0 = Output |             | ol bit for pin RI                                 | E1/WR        |              |         |              |                                                                                                                        |

| bit 0:  | Bit0: Direc<br>1 = Input                       | tion Contro | ol bit for pin RI                                 | E0/RD        |              |         |              |                                                                                                                        |

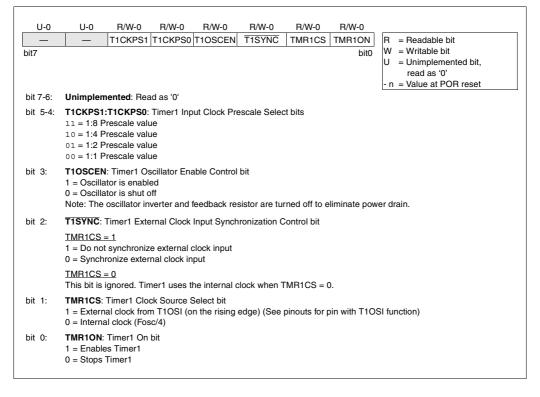

# 8.0 TIMER1 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

## FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

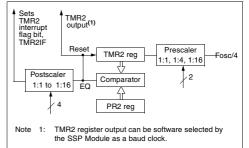

# 9.0 TIMER2 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

#### 9.2 Output of TMR2

## Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

## FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

#### EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 78.125 kHz, Fosc = 20 MHz TMR2 prescale = 1

$1/78.125 \text{ kHz} = [(PR2) + 1] \cdot 4 \cdot 1/20 \text{ MHz} \cdot 1$   $12.8 \ \mu s = [(PR2) + 1] \cdot 4 \cdot 50 \text{ ns} \cdot 1$ PR2 = 63

Find the maximum resolution of the duty cycle that can be used with a 78.125 kHz frequency and 20 MHz oscillator:

| 1/78.125 kHz | = $2^{\text{PWM RESOLUTION}} \cdot 1/20 \text{ MHz} \cdot 1$  |

|--------------|---------------------------------------------------------------|

| 12.8 µs      | = $2^{\text{PWM RESOLUTION}} \bullet 50 \text{ ns} \bullet 1$ |

| 256          | $= 2^{\text{PWM RESOLUTION}}$                                 |

| log(256)     | = (PWM Resolution) • $log(2)$                                 |

| 8.0          | = PWM Resolution                                              |

|              |                                                               |

At most, an 8-bit resolution duty cycle can be obtained from a 78.125 kHz frequency and a 20 MHz oscillator, i.e.,  $0 \leq$  CCPR1L:CCP1CON<5:4>  $\leq$  255. Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-3 lists example PWM frequencies and resolutions for Fosc = 20 MHz. The TMR2 prescaler and PR2 values are also shown.

10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 10-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

## TABLE 10-4: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Add                  | Name    | Bit 7                | Bit 6       | Bit 5               | Bit 4               | Bit 3                    | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|----------------------|---------|----------------------|-------------|---------------------|---------------------|--------------------------|------------|------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                  | PEIE        | TOIE                | INTE                | RBIE                     | T0IF       | INTF       | RBIF   |      |                    | 0000  |                       |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup> | (3)         | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF                    | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 0Dh <sup>(4)</sup>   | PIR2    | —                    | _           | _                   | _                   | -                        | -          | -          | CCP2IF |      | 0                  |       | 0                     |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup> | (3)         | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE                    | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 8Dh <sup>(4)</sup>   | PIE2    | —                    | CCP2IE -    |                     |                     |                          |            |            |        | 0    |                    | 0     |                       |

| 87h                  | TRISC   | PORTC D              | ata Direc   | ction registe       | er                  |                          |            |            |        | 1111 | 1111               | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding re           | egister for | the Least           | Significant         | Byte of the              | 16-bit TMF | R1 registe | r      | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding re           | egister for | the Most S          | Significant I       | Byte of the <sup>·</sup> | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h                  | T1CON   | _                    | _           | T1CKPS1             | T1CKPS0             | T1OSCEN                  | T1SYNC     | TMR1CS     | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/C            | Compare/    | PWM1 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture/C            | Compare/    | PWM1 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                  | CCP1CON | —                    | _           | CCP1X               | CCP1Y               | CCP1M3                   | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00    | 0000                  |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/C            | Compare/    | PWM2 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/C            | Compare/    | PWM2 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh <sup>(4)</sup>   | CCP2CON | —                    | _           | CCP2X               | CCP2Y               | CCP2M3                   | CCP2M2     | CCP2M1     | CCP2M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

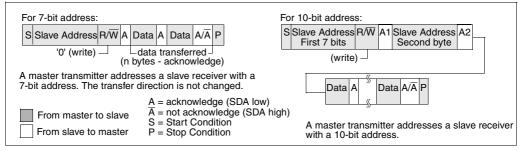

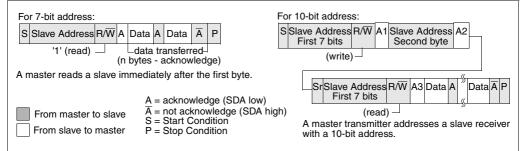

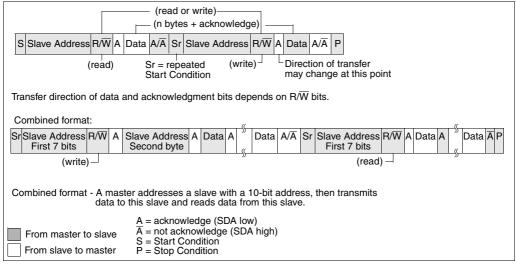

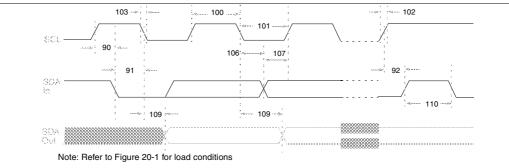

Figure 11-19 and Figure 11-20 show Master-transmitter and Master-receiver data transfer sequences.

When a master does not wish to relinquish the bus (by generating a STOP condition), a repeated START condition (Sr) must be generated. This condition is identical to the start condition (SDA goes high-to-low while

SCL is high), but occurs after a data transfer acknowledge pulse (not the bus-free state). This allows a master to send "commands" to the slave and then receive the requested information or to address a different slave device. This sequence is shown in Figure 11-21.

## FIGURE 11-19: MASTER-TRANSMITTER SEQUENCE

## FIGURE 11-20: MASTER-RECEIVER SEQUENCE

## FIGURE 11-21: COMBINED FORMAT

#### 12.2 USART Asynchronous Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In this mode, the USART uses standard nonreturn-tozero (NRZ) format (one start bit, eight or nine data bits and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 12.2.1 USART ASYNCHRONOUS TRANSMITTER

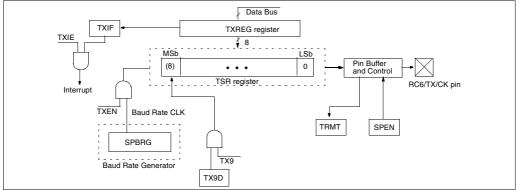

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY) the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt is enabled/dis-

abled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data     |

|---------|--------------------------------------------|

|         | memory so it is not available to the user. |

Note 2: Flag bit TXIF is set when enable bit TXEN is set.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 12-7). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register resulting in an empty TXREG register. A back-to-back transfer is thus possible (Figure 12-9). Clearing enable bit TXEN during a transmission will cause the transmistion to be aborted and will reset the transmitter. As a result the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit maybe loaded in the TSR register.

#### FIGURE 12-7: USART TRANSMIT BLOCK DIAGRAM

| CLRF              | Clear f                                                               |                         |                 |                       |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|

| Syntax:           | [ <i>label</i> ] C                                                    | LRF f                   |                 |                       |

| Operands:         | $0 \le f \le 12$                                                      | 7                       |                 |                       |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | 1                       |                 |                       |

| Status Affected:  | Z                                                                     |                         |                 |                       |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |

| Description:      | The conter<br>and the Z                                               |                         | ster 'f' are    | cleared               |

| Words:            | 1                                                                     |                         |                 |                       |

| Cycles:           | 1                                                                     |                         |                 |                       |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |

| Example           | CLRF                                                                  | FLAG                    | _REG            |                       |

|                   | Before In                                                             |                         |                 |                       |

|                   | After Inst                                                            | FLAG_RE                 | EG =            | 0x5A                  |

|                   |                                                                       | FLAG RE                 | EG =            | 0x00                  |

|                   |                                                                       | Z                       | =               | 1                     |

| CLRW                                                                | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                            |                                                              |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|

| Syntax:                                                             | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLRW                                                      |                                                            |                                                              |

| Operands:                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |

| Operation:                                                          | $00h \rightarrow (N 1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V)                                                        |                                                            |                                                              |

| Status Affected:                                                    | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Encoding:                                                           | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0001                                                      | 0xxx                                                       | xxxx                                                         |

| Description:                                                        | W register<br>set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | is cleared                                                | . Zero bit (                                               | (Z) is                                                       |

| Words:                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Cycles:                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Q Cycle Activity:                                                   | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q2                                                        | Q3                                                         | Q4                                                           |

|                                                                     | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No-<br>Operation                                          | Process<br>data                                            | Write to<br>W                                                |

| Example                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |