Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62a-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.6 I/O Programming Considerations

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stavs in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential read-modify-write instructions on an I/O port.

### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| ; |     |         |     |   | PORT | latch | PORT | pins |

|---|-----|---------|-----|---|------|-------|------|------|

| ; |     |         |     |   |      |       |      |      |

| ' | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp | pppp |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | 11pp | pppp |

|   | BSF | STATUS, | RP0 | ; |      |       |      |      |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp | pppp |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp | pppp |

|   |     |         |     |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp pppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

| PC                      | X PC                             | X PC + 1                         | X           | PC + 2                   | ( PC + 3 )                                | This example shows a write to POI                                                       |

|-------------------------|----------------------------------|----------------------------------|-------------|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|

| Instruction<br>fetched  | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W                     |             | NOP                      | NOP                                       | followed by a read from PORTB.<br>Note that:                                            |

| RB7:RB0                 | PORTB                            | 1<br>1<br>1                      | X           | <br>                     | ۱<br>ــــــــــــــــــــــــــــــــــــ | data setup time = (0.25TCY - TPD)                                                       |

|                         | 1<br>1<br>1                      | 1<br>1<br>1                      |             | Port pin<br>sampled here |                                           | where TCY = instruction cycle<br>TPD = propagation delay                                |

| Instruction<br>executed |                                  | MOVWF PORTB<br>write to<br>PORTB | - TPD<br>MO | 1                        | NOP                                       | Therefore, at higher clock frequence<br>a write followed by a read may be p<br>lematic. |

|                         | i<br>i                           | i<br>i                           |             | 1                        |                                           |                                                                                         |

### FIGURE 5-10: SUCCESSIVE I/O OPERATION

### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0 R/W-0 R            | /W-0 R/W-0         | R/W-0        | R/W-0         | R/W-0        |                                       |

|----------|------------------------|--------------------|--------------|---------------|--------------|---------------------------------------|

| —        | - CCPxX CC             | CPxY CCPxM3        | CCPxM2       | CCPxM1        | CCPxM0       | R = Readable bit                      |

| bit7     |                        |                    |              |               | bit0         | W = Writable bit                      |

|          |                        |                    |              |               |              | U = Unimplemented bit, read<br>as '0' |

|          |                        |                    |              |               |              | - n =Value at POR reset               |

| bit 7-6: | Unimplemented: F       | Poad as '0'        |              |               |              |                                       |

|          | •                      |                    |              |               |              |                                       |

| bit 5-4: | CCPxX:CCPxY: PV        | VM Least Significa | ant bits     |               |              |                                       |

|          | Capture Mode<br>Unused |                    |              |               |              |                                       |

|          | Compare Mode           |                    |              |               |              |                                       |

|          | Unused                 |                    |              |               |              |                                       |

|          | PWM Mode               |                    |              |               |              |                                       |

|          | These bits are the t   | wo LSbs of the P   | NM duty cy   | cle. The eig  | ht MSbs are  | found in CCPRxL.                      |

| bit 3-0: | CCPxM3:CCPxM0          | : CCPx Mode Sele   | ect bits     |               |              |                                       |

|          | 0000 = Capture/Co      | •                  |              | k module)     |              |                                       |

|          | 0100 = Capture mo      |                    | •            |               |              |                                       |

|          | 0101 = Capture mo      |                    | •            |               |              |                                       |

|          | 0110 = Capture mo      | · ·                | 0 0          |               |              |                                       |

|          | 1000 = Compare m       | · ·                | • •          | CCPxIF is     | set)         |                                       |

|          | 1001 = Compare m       |                    | •            |               | ,            |                                       |

|          | •                      |                    | •            |               | ,            | is set, CCPx pin is unaffected)       |

|          | •                      |                    | al event (CC | PxIF bit is s | et; CCP1 res | ets TMR1; CCP2 resets TMR1)           |

|          | 11xx = PWM mode        | 9                  |              |               |              |                                       |

|          |                        |                    |              |               |              |                                       |

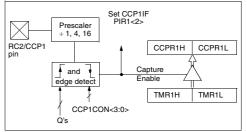

### 10.1 Capture Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an   |

|-------|-------------------------------------------|

|       | output, a write to PORTC can cause a cap- |

|       | ture condition.                           |

# FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work consistently.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture event is changed, a false capture interrupt may be generated. The user should clear enable bit CCP1IE (PIE1<2>) to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

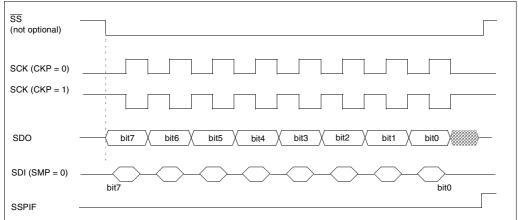

## FIGURE 11-13: SPI MODE TIMING (SLAVE MODE WITH CKE = 1) (PIC16C66/67)

| TABLE 11-2: | REGISTERS ASSOCIATED WITH SPI OPERATION | (PIC16C66/67) |  |

|-------------|-----------------------------------------|---------------|--|

|             |                                         |               |  |

| Address               | Name    | Bit 7                | Bit 6      | Bit 5       | Bit 4      | Bit 3       | Bit 2    | Bit 1  | Bit 0  | Pow  | e on<br>er-on<br>set |      | on all<br>resets |

|-----------------------|---------|----------------------|------------|-------------|------------|-------------|----------|--------|--------|------|----------------------|------|------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE        | INTE       | RBIE        | T0IF     | INTF   | RBIF   | 0000 | 000x                 | 0000 | 000u             |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | (2)        | RCIF        | TXIF       | SSPIF       | CCP1IF   | TMR2IF | TMR1IF | 0000 | 0000                 | 0000 | 0000             |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | (2)        | RCIE        | TXIE       | SSPIE       | CCP1IE   | TMR2IE | TMR1IE | 0000 | 0000                 | 0000 | 0000             |

| 13h                   | SSPBUF  | Synchrono            | ous Serial | Port Rece   | eive Buffe | r/Transmit  | Register |        |        | xxxx | xxxx                 | uuuu | uuuu             |

| 14h                   | SSPCON  | WCOL                 | SSPOV      | SSPEN       | CKP        | SSPM3       | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000                 | 0000 | 0000             |

| 85h                   | TRISA   | _                    | _          | PORTA D     | ata Direc  | tion regist | er       |        |        | 11   | 1111                 | 11   | 1111             |

| 87h                   | TRISC   | PORTC D              | ata Direct | ion registe | n register |             |          |        |        |      |                      | 1111 | 1111             |

| 94h                   | SSPSTAT | SMP                  | CKE        | D/A         | Р          | S           | R/W      | UA     | BF     | 0000 | 0000                 | 0000 | 0000             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

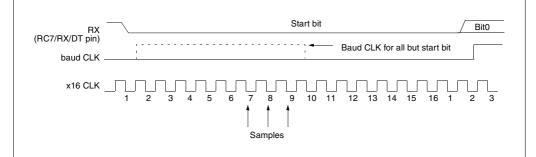

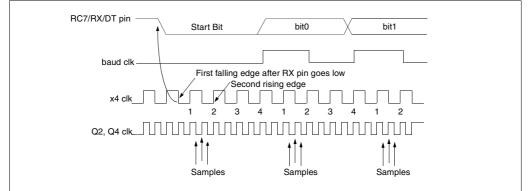

### 12.1.1 SAMPLING

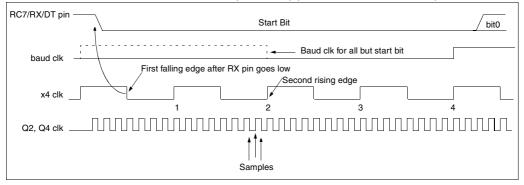

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

### FIGURE 12-3: RX PIN SAMPLING SCHEME (BRGH = 0) PIC16C63/R63/65/65A/R65)

### FIGURE 12-4: RX PIN SAMPLING SCHEME (BRGH = 1) (PIC16C63/R63/65/65A/R65)

### 12.2 USART Asynchronous Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In this mode, the USART uses standard nonreturn-tozero (NRZ) format (one start bit, eight or nine data bits and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

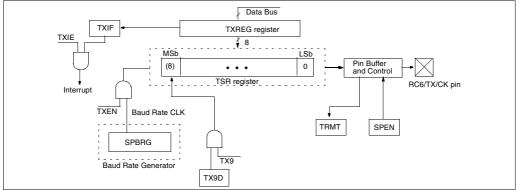

#### 12.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY) the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt is enabled/dis-

abled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data     |

|---------|--------------------------------------------|

|         | memory so it is not available to the user. |

Note 2: Flag bit TXIF is set when enable bit TXEN is set.

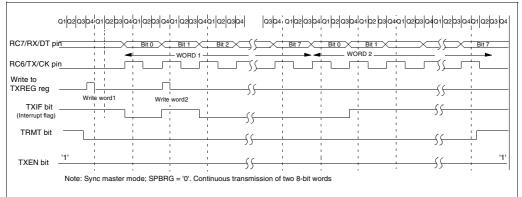

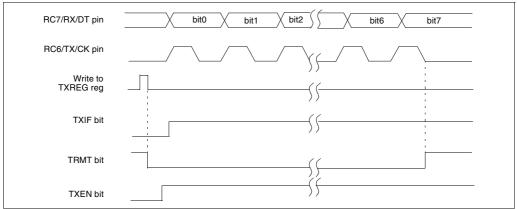

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 12-7). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register resulting in an empty TXREG register. A back-to-back transfer is thus possible (Figure 12-9). Clearing enable bit TXEN during a transmission will cause the transmistion to be aborted and will reset the transmitter. As a result the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit maybe loaded in the TSR register.

### FIGURE 12-7: USART TRANSMIT BLOCK DIAGRAM

### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |  |

|---------|-------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|--|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)                          | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |  |

| 18h     | RCSTA | SPEN                 | RX9                          | SREN    | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x               | x00- 0000                       |  |

| 19h     | TXREG | USART Tra            | ansmit Re                    | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |  |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)                          | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |  |

| 98h     | TXSTA | CSRC                 | TX9                          | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |  |

| 99h     | SPBRG | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |                         | 0000 0000                       |  |

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

### FIGURE 12-13: SYNCHRONOUS TRANSMISSION THROUGH TXEN

### 13.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

Applicable Devices 61|62|62A|R62|63|R63|64|64A|R64|65|65A|R65|66|67

### 13.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{MCLR}/VPP$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

### 13.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 13.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 13.4.4 BROWN-OUT RESET (BOR)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

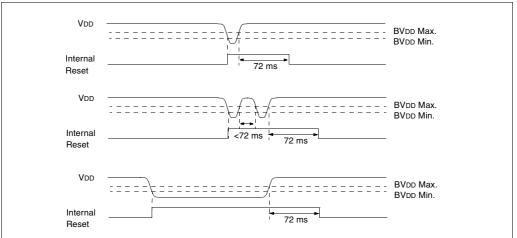

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (parameter D005 in Electrical Specification section) for greater than parameter #34 (see Electrical Specification section), the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #34. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 13-10 shows typical brown-out situations.

## FIGURE 13-10: BROWN-OUT SITUATIONS

### 13.5 Interrupts

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The PIC16C6X family has up to 11 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or global enable bit, GIE.            |

Global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enable interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flag bits are contained in the INTCON register.

The peripheral interrupt flag bits are contained in special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2 and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, bit GIE is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the RB0/INT pin or RB port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 13-19). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C61/62/64/65, if an interrupt occurs while the Global Interrupt Enable bit, GIE is being cleared, bit GIE may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

- 4. Perform the following to ensure that interrupts are globally disabled.

| LOOP | BCF II | NTCON,GIE  | ;Disable Global    |

|------|--------|------------|--------------------|

|      |        |            | ;Interrupt bit     |

|      | BTFSC  | INTCON,GIE | ;Global Interrupt  |

|      |        |            | ;Disabled?         |

|      | GOTO   | LOOP       | ;NO, try again     |

|      | :      |            | ;Yes, continue     |

|      |        |            | ;with program flow |

| BTFSS             | Bit Test f                                                                                                                                                  | , Skip if S               | Set                       |                  | _ | CALL              | Call Sub                               | routine                                              |                                        |                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------------------|---|-------------------|----------------------------------------|------------------------------------------------------|----------------------------------------|-------------------------------|

| Syntax:           | [ <i>label</i> ] BT                                                                                                                                         | FSS f,b                   |                           |                  |   | Syntax:           | [ label ]                              | CALL k                                               |                                        |                               |

| Operands:         | $0 \leq f \leq 12$                                                                                                                                          | 7                         |                           |                  |   | Operands:         | $0 \le k \le 2$                        | 047                                                  |                                        |                               |

|                   | 0 ≤ b < 7                                                                                                                                                   |                           |                           |                  |   | Operation:        | (PC)+ 1-                               | ,                                                    |                                        |                               |

| Operation:        | skip if (f <l< td=""><td>b&gt;) = 1</td><td></td><td></td><td></td><td></td><td><math>k \rightarrow PC &lt;</math></td><td>,</td><td></td><td>44.</td></l<> | b>) = 1                   |                           |                  |   |                   | $k \rightarrow PC <$                   | ,                                                    |                                        | 44.                           |

| Status Affected:  | None                                                                                                                                                        |                           | 1                         |                  | 7 | o                 | (PCLATH                                | 1<4:3>) -                                            | > PG<12:                               | 11>                           |

| Encoding:         | 01                                                                                                                                                          | 11bb                      | bfff                      | ffff             |   | Status Affected:  | None                                   | 1                                                    |                                        | ·                             |

| Description:      | If bit 'b' in r<br>instruction                                                                                                                              |                           |                           | ne next          |   | Encoding:         | 10                                     | 0kkk                                                 | kkkk                                   | kkkk                          |

|                   | If bit 'b' is '<br>discarded<br>instead, m                                                                                                                  | 1', then the<br>and a NOF | e next instr<br>s execute | əd               |   | Description:      | (PC+1) is<br>eleven bit<br>into PC bit | putine. Firs<br>pushed on<br>immediate<br>ts <10:0>. | to the stac<br>address is<br>The upper | k. The<br>s loaded<br>bits of |

| Words:            | 1                                                                                                                                                           |                           |                           |                  |   |                   | the PC are<br>is a two cy              |                                                      |                                        | H. CALL                       |

| Cycles:           | 1(2)                                                                                                                                                        |                           |                           |                  |   | Words:            | 1                                      |                                                      |                                        |                               |

| Q Cycle Activity: | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | - | Cycles:           | 2                                      |                                                      |                                        |                               |

|                   | Decode                                                                                                                                                      | Read<br>register 'f'      | Process<br>data           | No-<br>Operation |   | Q Cycle Activity: | Q1                                     | Q2                                                   | Q3                                     | Q4                            |

| If Skip:          | (2nd Cyc                                                                                                                                                    | le)                       |                           |                  |   | 1st Cycle         | Decode                                 | Read<br>literal 'k',                                 | Process<br>data                        | Write to<br>PC                |

| ·                 | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | 7 |                   |                                        | Push PC<br>to Stack                                  | uulu                                   | 10                            |

|                   | No-<br>Operation                                                                                                                                            | No-<br>Operation          | No-<br>Operation          | No-<br>Operation |   | 2nd Cycle         | No-<br>Operation                       | No-<br>Operation                                     | No-<br>Operation                       | No-<br>Operation              |

| Example           | HERE<br>FALSE                                                                                                                                               | BTFSC<br>GOTO             | FLAG,1<br>PROCESS         | CODE             |   | Example           | HERE                                   | CALL                                                 | THERE                                  |                               |

|                   | TRUE                                                                                                                                                        | •                         |                           |                  |   |                   |                                        | PC = A                                               | ddress HE                              | RE                            |

|                   |                                                                                                                                                             | •                         |                           |                  |   |                   | After Inst                             | truction<br>PC = A                                   | ddroce TTU                             | סמס                           |

|                   | Before In:                                                                                                                                                  |                           | address I                 | TEDE             |   |                   |                                        | TOS = A                                              |                                        |                               |

|                   | After Inst                                                                                                                                                  |                           | address r                 | IERE             |   |                   |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             | f FLAG<1:                 | - /                       |                  |   |                   |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             | PC =<br>if FLAG<1;        | address Fi                | ALSE             |   |                   |                                        |                                                      |                                        |                               |

|                   |                                                                                                                                                             |                           | > = 1,<br>address TI      | RUE              |   |                   |                                        |                                                      |                                        |                               |

| XORLW             | Exclusiv                                   | /e OR Li            | teral wit       | h W           |

|-------------------|--------------------------------------------|---------------------|-----------------|---------------|

| Syntax:           | [ <i>label</i> ]                           | XORLV               | Vk              |               |

| Operands:         | $0 \le k \le 2$                            | 55                  |                 |               |

| Operation:        | (W) .XO                                    | $R. k \to (N$       | N)              |               |

| Status Affected:  | Z                                          |                     |                 |               |

| Encoding:         | 11                                         | 1010                | kkkk            | kkkk          |

| Description:      | The conte<br>XOR'ed v<br>The resul<br>ter. | vith the eig        | ght bit lite    | ral 'k'.      |

| Words:            | 1                                          |                     |                 |               |

| Cycles:           | 1                                          |                     |                 |               |

| Q Cycle Activity: | Q1                                         | Q2                  | Q3              | Q4            |

|                   | Decode                                     | Read<br>literal 'k' | Process<br>data | Write to<br>W |

| Example:          | XORLW                                      | 0xAF                |                 |               |

|                   | Before Ir                                  | nstruction          | n               |               |

|                   |                                            | W =                 | 0xB5            |               |

|                   | After Ins                                  | truction            |                 |               |

|                   |                                            | W =                 | 0x1A            |               |

|                   |                                            |                     |                 |               |

| XORWF             | Exclusiv                                                       | e OR W                    | with f                         |                          |

|-------------------|----------------------------------------------------------------|---------------------------|--------------------------------|--------------------------|

| Syntax:           | [label]                                                        | XORWF                     | f,d                            |                          |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 27                        |                                |                          |

| Operation:        | (W) .XOF                                                       | $R.(f) \to (f)$           | destinatio                     | on)                      |

| Status Affected:  | Z                                                              |                           |                                |                          |

| Encoding:         | 00                                                             | 0110                      | dfff                           | ffff                     |

| Description:      | Exclusive<br>register wi<br>result is st<br>1 the resu         | th registe<br>ored in the | r 'f'. If 'd' is<br>e W regist | s 0 the<br>er. If 'd' is |

| Words:            | 1                                                              |                           |                                |                          |

| Cycles:           | 1                                                              |                           |                                |                          |

| Q Cycle Activity: | Q1                                                             | Q2                        | Q3                             | Q4                       |

|                   | Decode                                                         | Read<br>register<br>'f'   | Process<br>data                | Write to destination     |

| Example           | XORWF                                                          | REG                       | 1                              |                          |

|                   | Before In                                                      | struction                 | I                              |                          |

|                   |                                                                | REG<br>W                  | 0/1                            | AF<br>B5                 |

|                   | After Inst                                                     | ruction                   |                                |                          |

|                   |                                                                | REG<br>W                  | 0/1                            | 1A<br>B5                 |

=

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

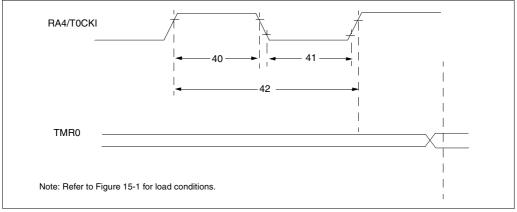

# FIGURE 15-5: TIMER0 EXTERNAL CLOCK TIMINGS

## TABLE 15-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                                             | Тур† | Max | Units | Conditions         |

|------------------|------|------------------------|----------------|-------------------------------------------------|------|-----|-------|--------------------|

| 40*              | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20                                     | _    | _   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | _   | ns    | parameter 42       |

| 41*              | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TCY + 20                                     | —    | —   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | —   | ns    | parameter 42       |

| 42*              | Tt0P | T0CKI Period           | No Prescaler   | TCY + 40                                        | _    | _   |       | N = prescale value |

|                  |      |                        | With Prescaler | Greater of:<br>20 ns or<br><u>Tcy + 40</u><br>N | _    | _   | ns    | (2, 4,, 256)       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

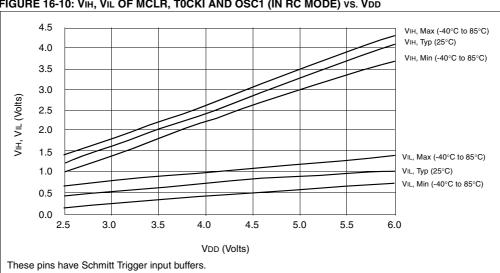

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 18.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | opS                                    | 3. Tcc:st   | (I <sup>2</sup> C specifications only)                                    |

|-----------------------|----------------------------------------|-------------|---------------------------------------------------------------------------|

| 2. TppS               |                                        | 4. Ts       | (I <sup>2</sup> C specifications only)                                    |

| т                     |                                        |             |                                                                           |

| F                     | Frequency                              | т           | Time                                                                      |

| Lowerc                | ase letters (pp) and their meanings:   |             |                                                                           |

| рр                    |                                        |             |                                                                           |

| сс                    | CCP1                                   | osc         | OSC1                                                                      |

| ck                    | CLKOUT                                 | rd          | RD                                                                        |

| cs                    | CS                                     | rw          | RD or WR                                                                  |

| di                    | SDI                                    | SC          | SCK                                                                       |

| do                    | SDO                                    | SS          | SS                                                                        |

| dt                    | Data in                                | tO          | TOCKI                                                                     |

| io                    | I/O port                               | t1          | T1CKI                                                                     |

| mc                    | MCLR                                   | wr          | WR                                                                        |

| 1                     | ase letters and their meanings:        |             |                                                                           |

| S                     |                                        |             |                                                                           |

| F                     | Fall                                   | P           | Period                                                                    |

| Н                     | High                                   | R           | Rise                                                                      |

| I                     | Invalid (Hi-impedance)                 | V           | Valid                                                                     |

| L                     | Low                                    | Z           | Hi-impedance                                                              |

| I <sup>2</sup> C only |                                        |             |                                                                           |

| AA                    | output access                          | High        | High                                                                      |

| BUF                   | Bus free                               | Low         | Low                                                                       |

| Tcc:st                | (I <sup>2</sup> C specifications only) |             |                                                                           |

| CC                    |                                        |             |                                                                           |

| HD                    | Hold                                   | SU          | Setup                                                                     |

| ST                    |                                        |             |                                                                           |

| DAT                   | DATA input hold                        | STO         | STOP condition                                                            |

| STA                   | START condition                        |             |                                                                           |

| FIGURE                | 18-1: LOAD CONDITIONS FOR DEVI         | CE TIMING S | SPECIFICATIONS                                                            |

|                       | Load condition 1                       |             | Load condition 2                                                          |

|                       | N/ /0                                  |             |                                                                           |

|                       | VDD/2                                  |             |                                                                           |

|                       | J                                      |             |                                                                           |

|                       | $\leq$ RL                              |             |                                                                           |

|                       | $\leq$                                 |             | · ····                                                                    |

|                       | • • • • • • • • • • • • • • • • • • •  |             | Vss                                                                       |

|                       |                                        |             |                                                                           |

|                       | +                                      |             |                                                                           |

|                       | Vss                                    | RL = 464Ω   |                                                                           |

|                       |                                        |             | for all pipe execut OSC2/CL/CUT                                           |

|                       |                                        | CL = 50 pF  | for all pins except OSC2/CLKOUT<br>but including D and E outputs as ports |

| Note 1:               | PORTD and PORTE are not                | 15-5        | ÷                                                                         |

|                       | implemented on the                     | 15 pF       | for OSC2 output                                                           |

|                       | PIC16C62A/R62.                         |             |                                                                           |

|                       |                                        |             |                                                                           |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

NOTES:

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

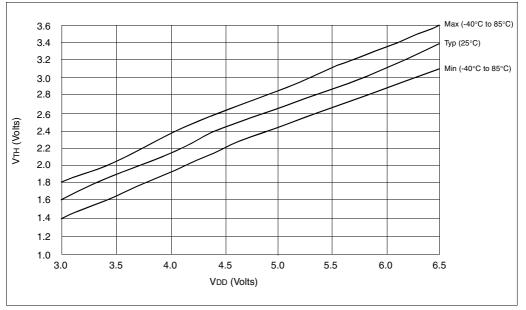

### 20.2 DC Characteristics: PIC16LC63/65A-04 (Commercial, Industrial)

| DC CHA       |                                                                  | <b>Standaı</b><br>Operatir |      | •    |     | °C ≤  | <b>Inless otherwise stated)</b><br>TA $\leq$ +85°C for industrial and<br>TA $\leq$ +70°C for commercial |

|--------------|------------------------------------------------------------------|----------------------------|------|------|-----|-------|---------------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                                   | Sym                        | Min  | Тур† | Max | Units | Conditions                                                                                              |

| D001         | Supply Voltage                                                   | Vdd                        | 2.5  | -    | 6.0 | V     | LP, XT, RC osc configuration (DC - 4 MHz)                                                               |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                           | Vdr                        | -    | 1.5  | -   | V     |                                                                                                         |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                       | -    | Vss  | -   | V     | See section on Power-on Reset for details                                                               |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                       | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details                                                               |

| D005         | Brown-out Reset Voltage                                          | BVDD                       | 3.7  | 4.0  | 4.3 | V     | BODEN configuration bit is enabled                                                                      |

| D010         | Supply Current (Note 2, 5)                                       | IDD                        | -    | 2.0  | 3.8 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                           |

| D010A        |                                                                  |                            | -    | 22.5 | 48  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                         |

| D015*        | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR              | -    | 350  | 425 | μA    | BOR enabled, VDD = 5.0V                                                                                 |

| D020         | Power-down Current                                               | IPD                        | -    | 7.5  | 30  | μA    | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                 |

| D021         | (Note 3, 5)                                                      |                            | -    | 0.9  | 5   | μA    | VDD = 3.0V, WDT disabled, 0°C to +70°C                                                                  |

| D021A        |                                                                  |                            | -    | 0.9  | 5   | μA    | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                |

| D023*        | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR              | -    | 350  | 425 | μA    | BOR enabled, VDD = 5.0V                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 20.5 <u>Timing Diagrams and Specifications</u>

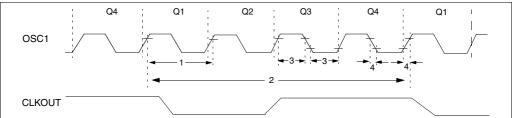

### FIGURE 20-2: EXTERNAL CLOCK TIMING

## TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|--------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKIN Frequency         | DC  | I    | 4      | MHz   | XT and RC osc mode |

|              |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|              |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|              |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|              |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|              |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|              |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|              |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|              |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1            | Tosc  | External CLKIN Period            | 250 |      | —      | ns    | XT and RC osc mode |

|              |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|              |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode        |

|              |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|              |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3*           | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|              | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|              |       |                                  | 15  | —    | —      | ns    | HS oscillator      |

| 4*           | TosR, | External Clock in (OSC1) Rise or | —   | _    | 25     | ns    | XT oscillator      |

|              | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|              |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

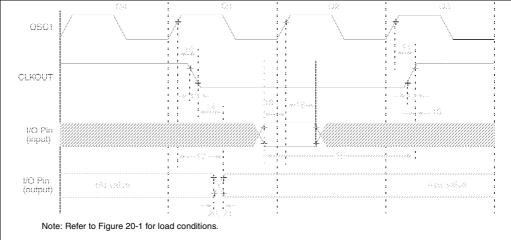

## FIGURE 20-3: CLKOUT AND I/O TIMING

| TABLE 20-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

| Parameter<br>No. | Sym      | Characteristic                                |                               | Min | Тур† | Max         | Units | Conditions |

|------------------|----------|-----------------------------------------------|-------------------------------|-----|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                              |                               | _   | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                              |                               | _   | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                              |                               | _   | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                              |                               | —   | 35   | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid         |                               | _   | _    | 0.5TCY + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOUT ↑                 | Port in valid before CLKOUT 1 |     | _    | -           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT ↑                   |                               | 0   | _    | _           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out val  | lid                           | _   | 50   | 150         | ns    |            |

| 18*              | TosH2iol | OSC1↑ (Q2 cycle) to Port input                | PIC16 <b>C</b> 63/65A         | 100 | _    | _           | ns    |            |

|                  |          | invalid (I/O in hold time)                    | PIC16LC63/65A                 | 200 | _    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in | setup time)                   | 0   | _    | _           | ns    |            |

| 20*              | TioR     | Port output rise time                         | PIC16 <b>C</b> 63/65A         | _   | 10   | 40          | ns    |            |

|                  |          |                                               | PIC16LC63/65A                 | _   | _    | 80          | ns    |            |

| 21*              | TioF     | Port output fall time                         | PIC16 <b>C</b> 63/65A         | _   | 10   | 40          | ns    |            |

|                  |          |                                               | PIC16LC63/65A                 | _   | _    | 80          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                      | 1                             | TCY | _    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high or low                | / time                        | Тсү | —    | _           | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

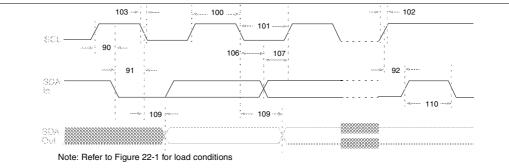

## FIGURE 22-14: I<sup>2</sup>C BUS DATA TIMING

## TABLE 22-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100*             | Тнідн   | Clock high time        | 100 kHz mode | 4.0        | -    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                                  |

| 101*             | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | —    |       |                                                  |

| 102*             | TR      | SDA and SCL rise       | 100 kHz mode | -          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10-400 pF          |

| 103*             | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |

| 90*              | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91*              | THD:STA | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106*             | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    | -                                                |

| 107*             | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92*              | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109*             | TAA     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | —          | —    | ns    |                                                  |

| 110*             | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                  |

These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

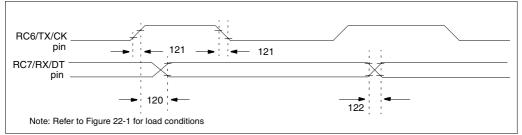

### FIGURE 22-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 22-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                    |                       | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-----------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120*             | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 66/67  |     | —    | 80  | ns    |            |

|                  |          | Clock high to data out valid      | PIC16 <b>LC</b> 66/67 | -   | —    | 100 | ns    |            |

| 121*             | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 66/67  |     | —    | 45  | ns    |            |

|                  |          | (Master Mode)                     | PIC16LC66/67          |     | —    | 50  | ns    |            |

| 122*             | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 66/67  | _   | —    | 45  | ns    |            |

|                  |          |                                   | PIC16LC66/67          | _   | —    | 50  | ns    |            |

\* These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

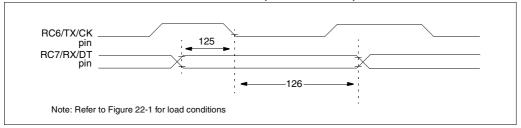

### FIGURE 22-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 22-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Max | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup time) | 15  |      | _   | ns    |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    | _   | ns    |            |

These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| TMR0                                           |

|------------------------------------------------|

| TMR0 Clock Source Select bit, T0CS             |

| TMR0 Interrupt                                 |

| TMR0 Overflow Interrupt Enable bit, T0IE       |

| TMR0 Overflow Interrupt Flag bit, T0IF         |

| TMR0 Prescale Selection Table                  |

| TMR0 Source Edge Select bit, T0SE              |

| TMR1 Overflow Interrupt Enable bit, TMR1IE     |

| TMR1 Overflow Interrupt Flag bit, TMR1IF       |

| TMR1CS                                         |

| TMR1H                                          |

| TMR1IE                                         |

| TMR1IF                                         |

| TMR1L                                          |

| TMR10N                                         |

| TMR2                                           |

| TMR2 Register                                  |

| TMR2 to PR2 Match Interrupt Enable bit, TMR2IE |

| TMR2 to PR2 Match Interrupt Flag bit, TMR2IF   |

| TMR216 TH2 Match menupit hag bit, TMR217       |

| TMR2IE                                         |

| TMR20N                                         |

| TO                                             |

| TOUTPS3:TOUTPS0                                |

| Transmit Enable bit, TXEN                      |

| Transmit Enable bit, TXEN                      |

| Transmit Status and Control Register           |

| TRISA                                          |

|                                                |

| TRISB                                          |

| TRISC                                          |

| TRISD                                          |

| TRISE                                          |