### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI                                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62a-04i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7              | Bit 6                                             | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|---------------------------------------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                                                   |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location                                     | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe                                    | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                                     | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                                | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad                                       | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | -                  | _                                                 |               | xx xxxx        | uu uuuu       |                 |               |           |                          |                                                |

| 06h                  | PORTB   | PORTB Dat          | RTB Data Latch when written: PORTB pins when read |               |                |               |                 |               |           |                          | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat          | Data Latch when written: PORTC pins when read     |               |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat          | ta Latch whe                                      | n written: PC | ORTD pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                    | _                                                 | _             | _              | _             | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                  | —                                                 | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                              | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                                               | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                    | _                                                 | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L                                   | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the M                                   | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                    | _                                                 | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe                                    | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                  | TOUTPS3                                           | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | is Serial Port                                    | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV                                             | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM                                         | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM                                         | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                  | —                                                 | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                                               | SREN          | CREN           | —             | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai         | nsmit Data R                                      | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red          | ceive Data R                                      | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM                                         | 2 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM                                         | 2 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                                                 | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted                                              |               |                |               |                 |               |           | —                        | _                                              |

### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

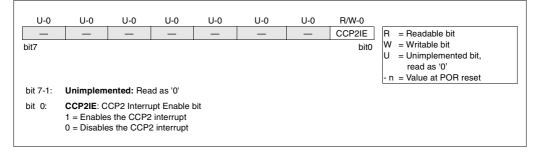

### 4.2.2.6 PIE2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt enable bit.

### FIGURE 4-20: PIE2 REGISTER (ADDRESS 8Dh)

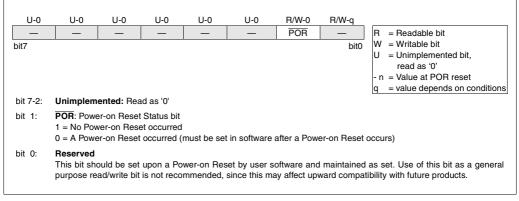

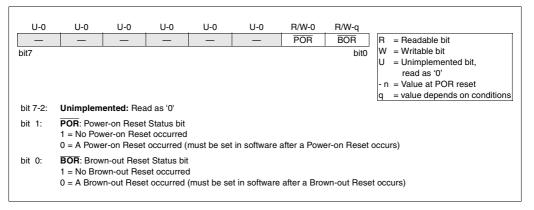

### 4.2.2.8 PCON REGISTER

### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control register (PCON) contains a flag bit to allow differentiation between a Power-on Reset to an external MCLR reset or WDT reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Poweron Reset condition.

### Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

# FIGURE 4-22: PCON REGISTER FOR PIC16C62/64/65 (ADDRESS 8Eh)

### FIGURE 4-23: PCON REGISTER FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 (ADDRESS 8Eh)

NOTES:

-

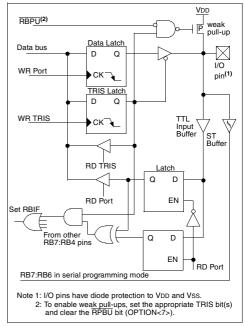

### 5.2 PORTB and TRISB Register

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

### EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are also disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB port change interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, Application Note, *"Implementing Wake-up on Key Stroke"* (AN552).

| Note: | For PIC16C61/62/64/65, if a change on the     |

|-------|-----------------------------------------------|

|       | I/O pin should occur when a read operation    |

|       | is being executed (start of the Q2 cycle),    |

|       | then interrupt flag bit RBIF may not get set. |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### FIGURE 5-3: BLOCK DIAGRAM OF THE RB7:RB4 PINS FOR PIC16C61/62/64/65

### SWITCHING PRESCALER ASSIGNMENT 7.3.1

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

| Note: | To avoid an unintended device RESET, the |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | following instruction sequence (shown in |  |  |  |  |  |  |  |  |  |

|       | Example 7-1) must be executed when       |  |  |  |  |  |  |  |  |  |

|       | changing the prescaler assignment from   |  |  |  |  |  |  |  |  |  |

|       | Timer0 to the WDT. This precaution must  |  |  |  |  |  |  |  |  |  |

|       | be followed even if the WDT is disabled. |  |  |  |  |  |  |  |  |  |

### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

|                                                                   | 1)  | BSF    | STATUS, RPO | ;Bank 1                                    |

|-------------------------------------------------------------------|-----|--------|-------------|--------------------------------------------|

| Lines 2 and 3 do NOT have to                                      | 2)  | MOVLW  | b'xx0x0xxx' | ;Select clock source and prescale value of |

| be included if the final desired                                  | 3)  | MOVWF  | OPTION_REG  | ;other than 1:1                            |

| prescale value is other than 1:1.                                 | 4)  | BCF    | STATUS, RPO | ;Bank 0                                    |

| If 1:1 is final desired value, then a temporary prescale value is | 5)  | CLRF   | TMR0        | ;Clear TMR0 and prescaler                  |

| set in lines 2 and 3 and the final                                | 6)  | BSF    | STATUS, RP1 | ;Bank 1                                    |

| prescale value will be set in lines                               | 7)  | MOVLW  | b'xxxx1xxx' | ;Select WDT, do not change prescale value  |

| 10 and 11.                                                        | 8)  | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 9)  | CLRWDT |             | ;Clears WDT and prescaler                  |

|                                                                   | 10) | MOVLW  | b'xxxx1xxx' | ;Select new prescale value and WDT         |

|                                                                   | 11) | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 12) | BCF    | STATUS, RPO | ;Bank 0                                    |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

### EXAMPLE 7-2: CHANGING PRESCALER (WDT → TIMER0)

CLRWDT ;Clear WDT and prescaler BSF STATUS, RP0 ;Bank 1 MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and clock source MOVWF OPTION REG ; BCF STATUS, RPO ;Bank 0

### TABLE 7-1: **REGISTERS ASSOCIATED WITH TIMER0**

| Address               | Name   | Bit 7  | Bit 6               | Bit 5      | Bit 4       | Bit 3     | Bit 2   | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|---------------------|------------|-------------|-----------|---------|-------|-------|--------------------------|---------------------------|

| 01h, 101h             | TMR0   | Timer0 | module's r          |            | xxxx xxxx   | uuuu uuuu |         |       |       |                          |                           |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE <sup>(1)</sup> | TOIE       | INTE        | RBIE      | TOIF    | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h, 181h             | OPTION | RBPU   | INTEDG              | T0CS       | T0SE        | PSA       | PS2     | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | —      | _                   | PORTA Data | Direction F | 11 1111   | 11 1111 |       |       |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

### 11.2 <u>SPI Mode for PIC16C62/62A/R62/63/</u> R63/64/64A/R64/65/65A/R65

This section contains register definitions and operational characteristics of the SPI module for the PIC16C62, PIC16C62A, PIC16CR62, PIC16C63, PIC16CR63, PIC16C64A, PIC16CR64, PIC16CR64, PIC16C65, PIC16C65A, PIC16CR65.

### FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| U-0      | U-0      | R-0                           | B-0        | B-0                                                     | R-0                                 | B-0          | B-0          |                                                                                      |  |  |  |  |

|----------|----------|-------------------------------|------------|---------------------------------------------------------|-------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------|--|--|--|--|

| _        | _        | D/A                           | P          | S                                                       | R/W                                 | UA           | BF           | R = Readable bit                                                                     |  |  |  |  |

| bit7     |          |                               | 1          |                                                         |                                     | <u>I</u>     | bit0         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |  |

| bit 7-6: | Unimpl   | emented                       | Read as    | '0'                                                     |                                     |              |              |                                                                                      |  |  |  |  |

| bit 5:   | 1 = Indi | cates that                    | the last b | ,                                                       | )<br>d or transmit<br>d or transmit |              |              |                                                                                      |  |  |  |  |

| bit 4:   | 1 = Indi |                               | a stop bi  | has been                                                | cleared when<br>detected last       |              |              | abled, SSPEN is cleared)<br>T)                                                       |  |  |  |  |

| bit 3:   |          |                               |            |                                                         |                                     |              |              |                                                                                      |  |  |  |  |

| bit 2:   | This bit | holds the<br>o the next<br>ad | R/W bit i  | ation (I <sup>2</sup> C r<br>nformation<br>stop bit, or | following the                       | e last addre | ess match. T | his bit is valid from the address                                                    |  |  |  |  |

| bit 1:   | 1 = Indi | cates that                    | the user   | it I <sup>2</sup> C mode<br>needs to up<br>to be upda   | odate the add                       | dress in the | SSPADD re    | egister                                                                              |  |  |  |  |

| bit 0:   | BF: Buf  | fer Full St                   | atus bit   |                                                         |                                     |              |              |                                                                                      |  |  |  |  |

|          | 1 = Rec  |                               | olete, SSF | es)<br>PBUF is full<br>SSPBUF is                        |                                     |              |              |                                                                                      |  |  |  |  |

|          | 1 = Trar |                               | ogress, S  | SPBUF is f<br>PBUF is err                               |                                     |              |              |                                                                                      |  |  |  |  |

| TABLE 12-3: BAUD RATES FOR SYNCHRONOUS M |

|------------------------------------------|

|------------------------------------------|

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz SPBRG |            |                    | 7.15909 | SPBRG      |                    |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------------|------------|--------------------|---------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD        | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA           | -          | -                  | NA      | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA           | -          | -                  | NA      | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA           | -          | -                  | NA      | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766        | +1.73      | 255                | 9.622   | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23        | +0.16      | 129                | 19.24   | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76        | -1.36      | 32                 | 77.82   | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15        | +0.16      | 25                 | 94.20   | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5        | +4.17      | 7                  | 298.3   | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500          | 0          | 4                  | NA      | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500         | -          | 0                  | 1789.8  | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766        | -          | 255                | 6.991   | -          | 255                |

|                     | Fosc = 5 | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.579545 MHz |            |                             | 1 MHz  |            |                             | 32.768 kHz |            |                             |

|---------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|--------------|------------|-----------------------------|--------|------------|-----------------------------|------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA       | -          | -                           | NA     | -          | -                           | NA           | -          | -                           | NA     | -          | -                           | 0.303      | +1.14      | 26                          |

| 1.2                 | NA       | -          | -                           | NA     | -          | -                           | NA           | -          | -                           | 1.202  | +0.16      | 207                         | 1.170      | -2.48      | 6                           |

| 2.4                 | NA       | -          | -                           | NA     | -          | -                           | NA           | -          | -                           | 2.404  | +0.16      | 103                         | NA         | -          | -                           |

| 9.6                 | 9.6      | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622        | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA         | -          | -                           |

| 19.2                | 19.2     | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04        | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA         | -          | -                           |

| 76.8                | 79.2     | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57        | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA         | -          | -                           |

| 96                  | 97.48    | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43        | +3.57      | 8                           | NA     | -          | -                           | NA         | -          | -                           |

| 300                 | 316.8    | +5.60      | 3                           | NA     | -          | -                           | 298.3        | -0.57      | 2                           | NA     | -          | -                           | NA         | -          | -                           |

| 500                 | NA       | -          | -                           | NA     | -          | -                           | NA           | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| HIGH                | 1267     | -          | 0                           | 100    | -          | 0                           | 894.9        | -          | 0                           | 250    | -          | 0                           | 8.192      | -          | 0                           |

| LOW                 | 4.950    | -          | 255                         | 3.906  | -          | 255                         | 3.496        | -          | 255                         | 0.9766 | -          | 255                         | 0.032      | -          | 255                         |

# TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD FOSC = 20 MHz SPBRG |       |            | 16 MHz             |       | SPBRG      | 10 MHz             |        | SPBRG      | 7.15909 I          | SPBRG |            |                    |

|--------------------------|-------|------------|--------------------|-------|------------|--------------------|--------|------------|--------------------|-------|------------|--------------------|

| RATE<br>(K)              | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |

| 0.3                      | NA    | -          | -                  | NA    |            | -                  | NA     |            | -                  | NA    | -          |                    |

| 1.2                      | 1.221 | +1.73      | 255                | 1.202 | +0.16      | 207                | 1.202  | +0.16      | 129                | 1.203 | +0.23      | 92                 |

| 2.4                      | 2.404 | +0.16      | 129                | 2.404 | +0.16      | 103                | 2.404  | +0.16      | 64                 | 2.380 | -0.83      | 46                 |

| 9.6                      | 9.469 | -1.36      | 32                 | 9.615 | +0.16      | 25                 | 9.766  | +1.73      | 15                 | 9.322 | -2.90      | 11                 |

| 19.2                     | 19.53 | +1.73      | 15                 | 19.23 | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64 | -2.90      | 5                  |

| 76.8                     | 78.13 | +1.73      | 3                  | 83.33 | +8.51      | 2                  | 78.13  | +1.73      | 1                  | NA    | -          | -                  |

| 96                       | 104.2 | +8.51      | 2                  | NA    | -          | -                  | NA     | -          | -                  | NA    | -          | -                  |

| 300                      | 312.5 | +4.17      | 0                  | NA    | -          | -                  | NA     | -          | -                  | NA    | -          | -                  |

| 500                      | NA    | -          | -                  | NA    | -          | -                  | NA     | -          | -                  | NA    | -          | -                  |

| HIGH                     | 312.5 | -          | 0                  | 250   | -          | 0                  | 156.3  | -          | 0                  | 111.9 | -          | 0                  |

| LOW                      | 1.221 | -          | 255                | 0.977 | -          | 255                | 0.6104 | -          | 255                | 0.437 | -          | 255                |

|                     | Fosc = 5 | 5.0688 MI  | Ηz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31     | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2      | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4      | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9      | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8     | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2     | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2     | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094   | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

### 13.5 Interrupts

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The PIC16C6X family has up to 11 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or global enable bit, GIE.            |

Global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enable interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flag bits are contained in the INTCON register.

The peripheral interrupt flag bits are contained in special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2 and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, bit GIE is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the RB0/INT pin or RB port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 13-19). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C61/62/64/65, if an interrupt occurs while the Global Interrupt Enable bit, GIE is being cleared, bit GIE may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

- 4. Perform the following to ensure that interrupts are globally disabled.

| LOOP | BCF II | NTCON,GIE  | ;Disable Global    |

|------|--------|------------|--------------------|

|      |        |            | ;Interrupt bit     |

|      | BTFSC  | INTCON,GIE | ;Global Interrupt  |

|      |        |            | ;Disabled?         |

|      | GOTO   | LOOP       | ;NO, try again     |

|      | :      |            | ;Yes, continue     |

|      |        |            | ;with program flow |

### 13.7 <u>Watchdog Timer (WDT)</u>

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device reset. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (WDT Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 13.1).

### 13.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be

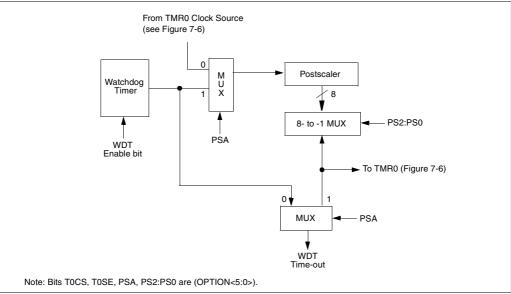

### FIGURE 13-20: WATCHDOG TIMER BLOCK DIAGRAM

assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

13.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

### FIGURE 13-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 13-1, Figure 13-2, and Figure 13-3 for details of these bits for the specific device.

### 13.8 Power-down Mode (SLEEP)

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, status bit  $\overline{PD}$  (STATUS<3>) is cleared, status bit  $\overline{TO}$  (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, and disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC).

### 13.8.1 WAKE-UP FROM SLEEP

The device can wake from SLEEP through one of the following events:

- 1. External reset input on MCLR/VPP pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or some peripheral interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. USART TX or RX (synchronous slave mode).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the substruction after the substruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 13.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{\text{PD}}$  bit. If the  $\overline{\text{PD}}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| Applicable Devices |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|

|                    |  |  |  |  |  |  |  |

|       |                                    | Standa                                                               | rd Operat | ing Co |       |                                                          | ss otherwise stated)                                |  |  |  |  |

|-------|------------------------------------|----------------------------------------------------------------------|-----------|--------|-------|----------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

|       |                                    | Operatir                                                             | ng temper | ature  | -40°C | S ≤ TA                                                   | $\Delta \leq +125^{\circ}C$ for extended,           |  |  |  |  |

|       | RACTERISTICS                       |                                                                      |           |        | -40°C | $^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and |                                                     |  |  |  |  |

|       | ARACIERISTICS                      |                                                                      |           |        | 0°C   | ≤ T⁄                                                     | $A \leq +70^{\circ}C$ for commercial                |  |  |  |  |

|       |                                    | Operating voltage VDD range as described in DC spec Section 15.1 and |           |        |       |                                                          |                                                     |  |  |  |  |

|       |                                    | Section                                                              | 15.2.     |        |       |                                                          |                                                     |  |  |  |  |

| Param | Characteristic                     | Sym                                                                  | Min       | Typ†   | Max   | Units                                                    | Conditions                                          |  |  |  |  |

| No.   |                                    |                                                                      |           | · · ·  |       |                                                          |                                                     |  |  |  |  |

|       | Output High Voltage                |                                                                      |           |        |       |                                                          |                                                     |  |  |  |  |

| D090  | I/O ports (Note 3)                 | Voh                                                                  | VDD-0.7   | -      | -     | v                                                        | IOH = -3.0 mA,                                      |  |  |  |  |

|       |                                    |                                                                      |           |        |       | -                                                        | $VDD = 4.5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |  |  |  |  |

| D090A |                                    |                                                                      | VDD-0.7   | -      | -     | v                                                        | IOH = -2.5 mA,                                      |  |  |  |  |

|       |                                    |                                                                      |           |        |       |                                                          | VDD = 4.5V, -40°C to +125°C                         |  |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)        |                                                                      | VDD-0.7   | -      | -     | V                                                        | IOH = -1.3 mA,                                      |  |  |  |  |

|       |                                    |                                                                      |           |        |       |                                                          | VDD = 4.5V, -40°C to +85°C                          |  |  |  |  |

| D092A |                                    |                                                                      | VDD-0.7   | -      | -     | V                                                        | IOH = -1.0 mA,                                      |  |  |  |  |

|       |                                    |                                                                      |           |        |       |                                                          | VDD = 4.5V, -40°C to +125°C                         |  |  |  |  |

| D150* | Open-Drain High Voltage            | Vod                                                                  | -         | -      | 14    | V                                                        | RA4 pin                                             |  |  |  |  |

|       | Capacitive Loading Specs on        |                                                                      |           |        |       |                                                          |                                                     |  |  |  |  |

|       | Output Pins                        |                                                                      |           |        |       |                                                          |                                                     |  |  |  |  |

| D100  | OSC2 pin                           | Cosc2                                                                |           |        | 15    | pF                                                       | In XT, HS and LP modes when                         |  |  |  |  |

|       |                                    |                                                                      |           |        |       |                                                          | external clock is used to drive                     |  |  |  |  |

|       |                                    |                                                                      |           |        |       |                                                          | OSC1.                                               |  |  |  |  |

| D101  | All I/O pins and OSC2 (in RC mode) | Cio                                                                  |           |        | 50    | pF                                                       |                                                     |  |  |  |  |

The parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 18.1 DC Characteristics: PIC16C62A/R62/64A/R64-04 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-10 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-20 (Commercial, Industrial, Extended)

| DC CHA        |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ Ta $\leq$ +125°C for extended, $-40^{\circ}$ C $\leq$ Ta $\leq$ +85°C for industrial and |            |            |            |        |                                                                     |  |  |  |  |

|---------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|--------|---------------------------------------------------------------------|--|--|--|--|

|               |                                                                  |                                                                                                                                                                                              |            |            | -4(<br>0°( |        | A = A = A + 85 °C for industrial and $A = A + 70$ °C for commercial |  |  |  |  |

| Param<br>No.  | Characteristic                                                   | Sym                                                                                                                                                                                          | Min        | Тур†       | Max        | Units  | Conditions                                                          |  |  |  |  |

| D001<br>D001A | Supply Voltage                                                   | Vdd                                                                                                                                                                                          | 4.0<br>4.5 | -          | 6.0<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration             |  |  |  |  |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | Vdr                                                                                                                                                                                          | -          | 1.5        | -          | V      |                                                                     |  |  |  |  |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                                                                                                                                                                                         | -          | Vss        | -          | V      | See section on Power-on Reset for details                           |  |  |  |  |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                                                                                                                                                                                         | 0.05       | -          | -          | V/ms   | See section on Power-on Reset for details                           |  |  |  |  |

| D005          | Brown-out Reset Voltage                                          | Bvdd                                                                                                                                                                                         | 3.7        | 4.0        | 4.3        | V      | BODEN bit in configuration word enabled                             |  |  |  |  |

|               |                                                                  |                                                                                                                                                                                              | 3.7        | 4.0        | 4.4        | v      | Extended Range Only                                                 |  |  |  |  |

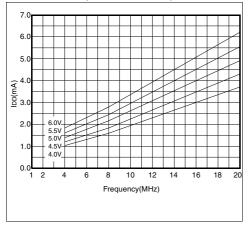

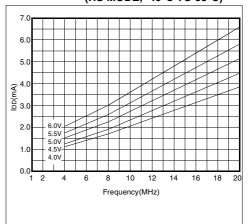

| D010          | Supply Current (Note 2, 5)                                       | Idd                                                                                                                                                                                          | -          | 2.7        | 5          | mA     | XT, RC, osc configuration Fosc = 4 MHz,<br>VDD = 5.5V (Note 4)      |  |  |  |  |

| D013          |                                                                  |                                                                                                                                                                                              | -          | 10         | 20         | mA     | HS osc configuration FOSC = 20 MHz,<br>VDD = 5.5V                   |  |  |  |  |

| D015*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor                                                                                                                                                                                | -          | 350        | 425        | μA     | BOR enabled, VDD = 5.0V                                             |  |  |  |  |

| D020          | Power-down Current (Note                                         | IPD                                                                                                                                                                                          | -          | 10.5       | 42         | μA     | VDD = 4.0V, WDT enabled, -40°C to +85°C                             |  |  |  |  |

| D021          | 3, 5)                                                            |                                                                                                                                                                                              | -          | 1.5        | 16         | μA     | VDD = 4.0V, WDT disabled, $-0^{\circ}C$ to $+70^{\circ}C$           |  |  |  |  |

| D021A         |                                                                  |                                                                                                                                                                                              | -          | 1.5<br>2.5 | 19         | μA     | $V_{DD} = 4.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$    |  |  |  |  |

| D021B         |                                                                  |                                                                                                                                                                                              | -          | 2.5        | 19         | μA     | VDD = 4.0V, WDT disabled, -40°C to +125°C                           |  |  |  |  |

| D023*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor                                                                                                                                                                                | -          | 350        | 425        | μA     | BOR enabled, VDD = 5.0V                                             |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# PIC16C6X

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

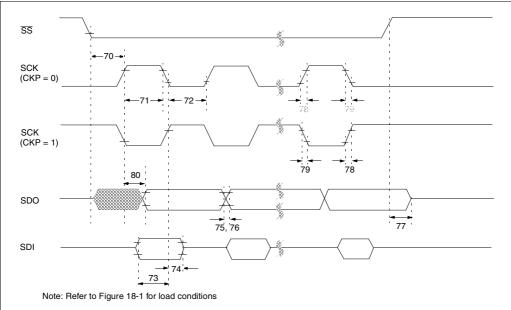

### TABLE 18-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input  | Тсү      | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)         | TCY + 20 | —    |     | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)          | TCY + 20 | —    |     | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                |          | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | —    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)       |          | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 21.3 DC Characteristics: PIC16CR63/R65-04 (Commercial, Industrial) PIC16CR63/R65-10 (Commercial, Industrial) PIC16CR63/R65-20 (Commercial, Industrial) PIC16LCR63/R65-04 (Commercial, Industrial)

|              |                                    |                     | rd Operat |          |                   |       | ss otherwise stated)<br>$A \le +85^{\circ}C$ for industrial and    |

|--------------|------------------------------------|---------------------|-----------|----------|-------------------|-------|--------------------------------------------------------------------|

| DC CHA       | RACTERISTICS                       | Operatir<br>Section |           | Vdd      | 0°C<br>range as o |       | $A \le +70^{\circ}C$ for commercial ed in DC spec Section 21.1 and |

| Param<br>No. | Characteristic                     | Sym                 | Min       | Тур<br>† | Мах               | Units | Conditions                                                         |

|              | Input Low Voltage                  |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | VIL                 |           |          |                   |       |                                                                    |

| D030         | with TTL buffer                    |                     | Vss       | -        | 0.15Vdd           | v     | For entire VDD range                                               |

| D030A        |                                    |                     | Vss       | -        | 0.8V              | v     | $4.5V \le VDD \le 5.5V$                                            |

| D031         | with Schmitt Trigger buffer        |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D032         | MCLR, OSC1 (in RC mode)            |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D033         | OSC1 (in XT, HS and LP)            |                     | Vss       | -        | 0.3VDD            | v     | Note1                                                              |

|              | Input High Voltage                 |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | VIH                 |           | -        |                   |       |                                                                    |

| D040         | with TTL buffer                    |                     | 2.0       | -        | Vdd               | v     | $4.5V \le V$ DD $\le 5.5V$                                         |

| D040A        |                                    |                     | 0.25VDD   | -        | Vdd               | v     | For entire VDD range                                               |

|              |                                    |                     | + 0.8V    |          |                   |       |                                                                    |

| D041         | with Schmitt Trigger buffer        |                     | 0.8VDD    | -        | Vdd               | v     | For entire VDD range                                               |

| D042         | MCLR                               |                     | 0.8VDD    | -        | Vdd               | V     |                                                                    |

| D042A        | OSC1 (XT, HS and LP)               |                     | 0.7Vdd    | -        | Vdd               | V     | Note1                                                              |

| D043         | OSC1 (in RC mode)                  |                     | 0.9Vdd    | -        | Vdd               | V     |                                                                    |

| D070         | PORTB weak pull-up current         | IPURB               | 50        | 250      | 400               | μΑ    | VDD = 5V, VPIN = VSS                                               |

|              | Input Leakage Current (Notes 2, 3) |                     |           |          |                   |       |                                                                    |

| D060         | I/O ports                          | lı∟                 | -         | -        | ±1                | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance                |

| D061         | MCLR, RA4/T0CKI                    |                     | -         | -        | ±5                | μA    | $Vss \le VPIN \le VDD$                                             |

| D063         | OSC1                               |                     | -         | -        | ±5                | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and                             |

|              |                                    |                     |           |          |                   |       | LP osc configuration                                               |

|              | Output Low Voltage                 |                     |           |          |                   |       | -                                                                  |

| D080         | I/O ports                          | Vol                 | -         | -        | 0.6               | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

| D083         | OSC2/CLKOUT (RC osc config)        |                     | -         | -        | 0.6               | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

|              | Output High Voltage                |                     |           |          |                   |       |                                                                    |

| D090         | I/O ports (Note 3)                 | Vон                 | VDD-0.7   | -        | -                 | v     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                       |

| D092         | OSC2/CLKOUT (RC osc config)        |                     | VDD-0.7   | -        | -                 | v     | IOH = -1.3  mA,  VDD = 4.5 V,<br>-40°C to +85°C                    |

| D150*        | Open-Drain High Voltage            | Vod                 | -         | -        | 14                | V     | RA4 pin                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

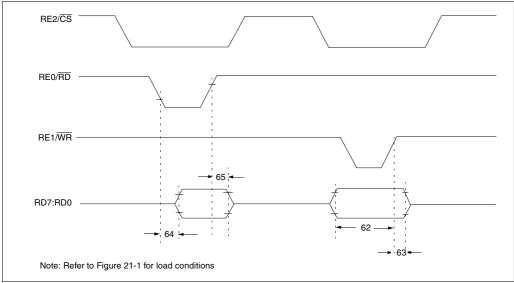

# FIGURE 21-8: PARALLEL SLAVE PORT TIMING (PIC16CR65)

### TABLE 21-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16CR65)