#### Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc63-04-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

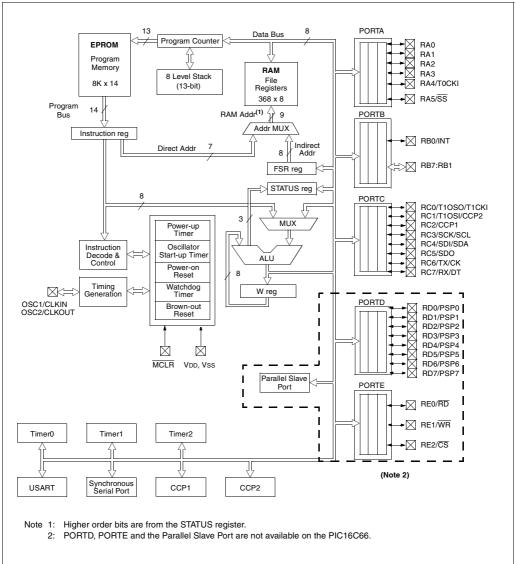

FIGURE 3-4: PIC16C66/67 BLOCK DIAGRAM

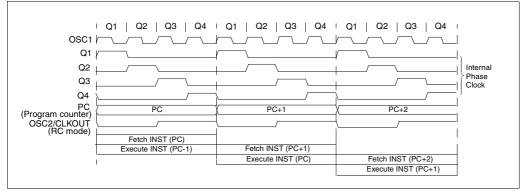

# 3.1 Clocking Scheme/Instruction Cycle

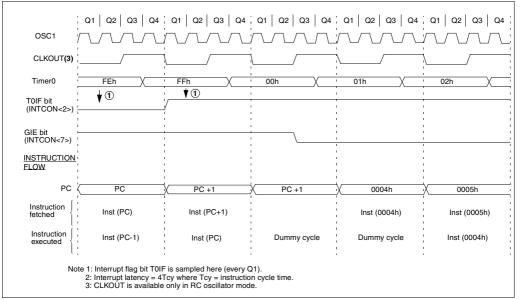

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

## 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

# TABLE 5-11: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                                           |

|--------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Read control input in parallel slave port mode.<br>RD<br>1 = Not a read operation<br>0 = Read operation. The system reads the PORTD register (if<br>chip selected)        |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Write control input in parallel slave port mode.<br>WR<br>1 = Not a write operation<br>0 = Write operation. The system writes to the PORTD register (if<br>chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Chip select control input in parallel slave port<br>mode.<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                   |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port (PSP) mode.

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|---------------------------|-------|-----------|--------------------------|---------------------------|

| 09h     | PORTE |       | —     | _     | —       |       | RE2                       | RE1   | RE0       | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Data Direction Bits |       | 0000 -111 | 0000 -111                |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells not used by PORTE.

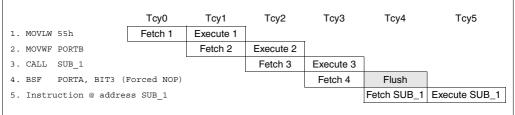

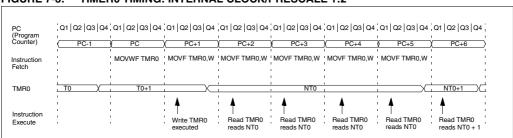

#### TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2 FIGURE 7-3:

#### FIGURE 7-4: **TMR0 INTERRUPT TIMING**

# FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0 R/W-0 R            | /W-0 R/W-0         | R/W-0        | R/W-0         | R/W-0        |                                       |

|----------|------------------------|--------------------|--------------|---------------|--------------|---------------------------------------|

| —        | - CCPxX CC             | CPxY CCPxM3        | CCPxM2       | CCPxM1        | CCPxM0       | R = Readable bit                      |

| bit7     |                        |                    |              |               | bit0         | W = Writable bit                      |

|          |                        |                    |              |               |              | U = Unimplemented bit, read<br>as '0' |

|          |                        |                    |              |               |              | - n =Value at POR reset               |

| bit 7-6: | Unimplemented: F       | Poad as '0'        |              |               |              |                                       |

|          | •                      |                    |              |               |              |                                       |

| bit 5-4: | CCPxX:CCPxY: PV        | VM Least Significa | ant bits     |               |              |                                       |

|          | Capture Mode<br>Unused |                    |              |               |              |                                       |

|          | Compare Mode           |                    |              |               |              |                                       |

|          | Unused                 |                    |              |               |              |                                       |

|          | PWM Mode               |                    |              |               |              |                                       |

|          | These bits are the t   | wo LSbs of the P   | NM duty cy   | cle. The eig  | ht MSbs are  | found in CCPRxL.                      |

| bit 3-0: | CCPxM3:CCPxM0          | : CCPx Mode Sele   | ect bits     |               |              |                                       |

|          | 0000 = Capture/Co      | •                  |              | k module)     |              |                                       |

|          | 0100 = Capture mo      |                    | •            |               |              |                                       |

|          | 0101 = Capture mo      |                    | •            |               |              |                                       |

|          | 0110 = Capture mo      | · ·                | 0 0          |               |              |                                       |

|          | 1000 = Compare m       | · ·                | • •          | CCPxIF is     | set)         |                                       |

|          | 1001 = Compare m       |                    | •            |               | ,            |                                       |

|          | •                      |                    | •            |               | ,            | is set, CCPx pin is unaffected)       |

|          | •                      |                    | al event (CC | PxIF bit is s | et; CCP1 res | ets TMR1; CCP2 resets TMR1)           |

|          | 11xx = PWM mode        | 9                  |              |               |              |                                       |

|          |                        |                    |              |               |              |                                       |

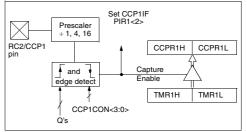

## 10.1 Capture Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

# 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an   |

|-------|-------------------------------------------|

|       | output, a write to PORTC can cause a cap- |

|       | ture condition.                           |

# FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work consistently.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture event is changed, a false capture interrupt may be generated. The user should clear enable bit CCP1IE (PIE1<2>) to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

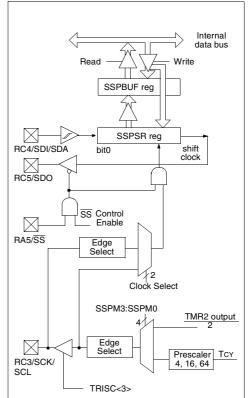

#### 11.2.1 OPERATION OF SSP MODULE IN SPI MODE

Applicable Devices 61 62 624 R62 63 R63 64 644 R64 65 654 R65 66 67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

Serial Data Out (SDO)

PIC16C6X

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- · Slave Mode (SCK is the clock input)

- Clock Polarity (Output/Input data on the Rising/ Falling edge of SCK)

- · Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full bit, BF (SSPSTAT<0>) and flag bit SSPIF are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>) will be set. User software must clear bit WCOL so that it can be determined if the following write(s) to the SSPBUF completed successfully. When the application software is expecting to receive valid data, the SSPBUF register should be read before the next byte of data to transfer is written to the SSPBUF register. The Buffer Full bit BF (SSPSTAT<0>) indicates when the SSPBUF register has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF register must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-1 shows the loading of the SSPBUF (SSPSR) register for data transmission. The shaded instruction is only required if the received data is meaningful.

# EXAMPLE 11-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      |       | •       | ,    |                   |

|------|-------|---------|------|-------------------|

|      | BSF   | STATUS, | RP0  | ;Specify Bank 1   |

| LOOP | BTFSS | SSPSTAT | , BF | ;Has data been    |

|      |       |         |      | ;received         |

|      |       |         |      | ;(transmit        |

|      |       |         |      | ;complete)?       |

|      | GOTO  | LOOP    |      | ;No               |

|      | BCF   | STATUS, | RP0  | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, | W    | ;W reg = contents |

|      |       |         |      | ; of SSPBUF       |

|      | MOVWF | RXDATA  |      | ;Save in user RAM |

|      | MOVF  | TXDATA, | W    | ;W reg = contents |

|      |       |         |      | ; of TXDATA       |

|      | MOVWF | SSPBUF  |      | ;New data to xmit |

|      |       |         |      |                   |

The block diagram of the SSP module, when in SPI mode (Figure 11-3), shows that the SSPSR register is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

# FIGURE 11-3: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and  $\overline{SS}$  could be used as general purpose outputs by clearing their corresponding TRIS register bits.

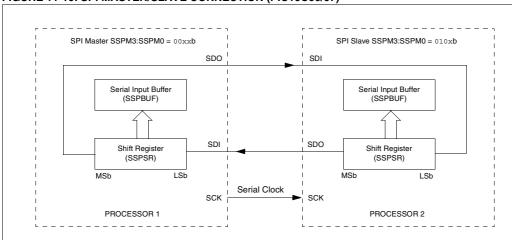

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

## FIGURE 11-10: SPI MASTER/SLAVE CONNECTION (PIC16C66/67)

# 12.2 USART Asynchronous Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In this mode, the USART uses standard nonreturn-tozero (NRZ) format (one start bit, eight or nine data bits and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

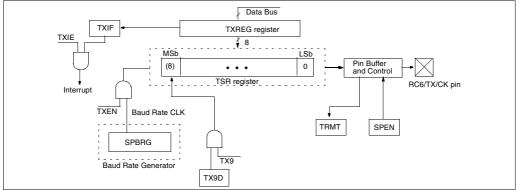

#### 12.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY) the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt is enabled/dis-

abled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data     |

|---------|--------------------------------------------|

|         | memory so it is not available to the user. |

Note 2: Flag bit TXIF is set when enable bit TXEN is set.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 12-7). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register resulting in an empty TXREG register. A back-to-back transfer is thus possible (Figure 12-9). Clearing enable bit TXEN during a transmission will cause the transmistion to be aborted and will reset the transmitter. As a result the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit maybe loaded in the TSR register.

## FIGURE 12-7: USART TRANSMIT BLOCK DIAGRAM

## SLEEP

| Syntax:           | [label] SLEEP                                                                                                                                                                                                                                    |                  |                  |                |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------|--|--|--|--|

| Operands:         | None                                                                                                                                                                                                                                             |                  |                  |                |  |  |  |  |

| Operation:        | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                            |                  |                  |                |  |  |  |  |

| Status Affected:  | TO, PD                                                                                                                                                                                                                                           |                  |                  |                |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                               | 0000             | 0110             | 0011           |  |  |  |  |

| Description:      | The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. See<br>Section 13.8 for more details. |                  |                  |                |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                |                  |                  |                |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                |                  |                  |                |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                               | Q2               | Q3               | Q4             |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                           | No-<br>Operation | No-<br>Operation | Go to<br>Sleep |  |  |  |  |

| Example:          | SLEEP                                                                                                                                                                                                                                            |                  |                  |                |  |  |  |  |

|                   |                                                                                                                                                                                                                                                  |                  |                  |                |  |  |  |  |

| SUBLW             | Subtract              | W from              | _iteral                                      |              |  |  |  |  |

|-------------------|-----------------------|---------------------|----------------------------------------------|--------------|--|--|--|--|

| Syntax:           | [ label ]             | SUBLW               | k                                            |              |  |  |  |  |

| Operands:         | $0 \le k \le 25$      | 5                   |                                              |              |  |  |  |  |

| Operation:        | k - (W) $\rightarrow$ | (W)                 |                                              |              |  |  |  |  |

| Status Affected:  | C, DC, Z              |                     |                                              |              |  |  |  |  |

| Encoding:         | 11                    | 110x                | kkkk                                         | kkkk         |  |  |  |  |

| Description:      | ment meth             | od) from th         | otracted (2's<br>ne eight bit<br>n the W reg | literal 'k'. |  |  |  |  |

| Words:            | 1                     |                     |                                              |              |  |  |  |  |

| Cycles:           | 1                     |                     |                                              |              |  |  |  |  |

| Q Cycle Activity: | Q1                    | Q2                  | Q3                                           | Q4           |  |  |  |  |

|                   | Decode                | Read<br>literal 'k' | Process<br>data                              | Write to W   |  |  |  |  |

| Example 1:        | SUBLW                 | 0x02                |                                              |              |  |  |  |  |

|                   | Before Ins            | struction           |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 1<br>?<br>?                                  |              |  |  |  |  |

|                   | After Instr           | ruction             |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 1<br>1; result is<br>0                       | positive     |  |  |  |  |

| Example 2:        | Before Ins            | struction           |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 2<br>?<br>?                                  |              |  |  |  |  |

|                   | After Instr           | ruction             |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 0<br>1; result i<br>1                        | s zero       |  |  |  |  |

| Example 3:        | Before Ins            | struction           |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 3<br>?<br>?                                  |              |  |  |  |  |

|                   | After Inst            | ruction             |                                              |              |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =   | 0xFF<br>0; result is<br>0                    | negative     |  |  |  |  |

-

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# 15.2 DC Characteristics: PIC16LC61-04 (Commercial, Industrial)

|              |                                                                  | Standa   | rd Ope  | rating ( | Condi | tions (u | Inless otherwise stated)                                         |  |  |  |

|--------------|------------------------------------------------------------------|----------|---------|----------|-------|----------|------------------------------------------------------------------|--|--|--|

| DC CHA       | RACTERISTICS                                                     | Operatir | ng temp | perature | -40   | °C ≤     | $TA \le +85^{\circ}C$ for industrial and                         |  |  |  |

|              |                                                                  |          |         |          | 0°C   | ≥ ≤      | $TA \leq +70^{\circ}C$ for commercial                            |  |  |  |

| Param<br>No. | Characteristic                                                   | Sym      | Min     | Тур†     | Max   | Units    | Conditions                                                       |  |  |  |

| D001         | Supply Voltage                                                   | Vdd      | 3.0     | -        | 6.0   | V        | XT, RC, and LP osc configuration                                 |  |  |  |

| D002*        | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr      | -       | 1.5      | -     | V        |                                                                  |  |  |  |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR     | -       | Vss      | -     | V        | See section on Power-on Reset for details                        |  |  |  |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD     | 0.05    | -        | -     | V/ms     | See section on Power-on Reset for details                        |  |  |  |

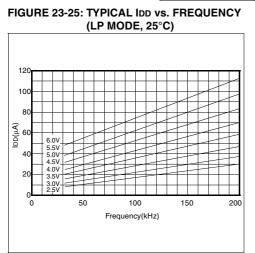

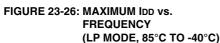

| D010         | Supply Current (Note 2)                                          | Idd      | -       | 1.4      | 2.5   | mA       | Fosc = 4 MHz, VDD = 3.0V (Note 4)                                |  |  |  |

| D010A        |                                                                  |          | -       | 15       | 32    | μA       | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc configuration |  |  |  |

| D020         | Power-down Current                                               | IPD      | -       | 5        | 20    | μΑ       | VDD = 3.0V, WDT enabled, -40°C to +85°C                          |  |  |  |

| D021         | (Note 3)                                                         |          | -       | 0.6      | 9     | μA       | VDD = 3.0V, WDT disabled, 0°C to +70°C                           |  |  |  |

| D021A        |                                                                  |          | -       | 0.6      | 12    | μA       | VDD = 3.0V, WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$       |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

| Applicable Devices |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|

|                    |  |  |  |  |  |  |  |

|       |                                    | Standa                                                              | rd Operat | ing Co |       |        | ss otherwise stated)                                |  |  |  |  |

|-------|------------------------------------|---------------------------------------------------------------------|-----------|--------|-------|--------|-----------------------------------------------------|--|--|--|--|

|       |                                    | Operatir                                                            | ng temper | ature  | -40°C | S ≤ TA | $\Delta \leq +125^{\circ}C$ for extended,           |  |  |  |  |

|       | RACTERISTICS                       |                                                                     |           |        | -40°C | ≤ T/   | $\Delta \leq +85^{\circ}$ C for industrial and      |  |  |  |  |

|       | ARACIERISTICS                      |                                                                     |           |        | 0°C   | ≤ T⁄   | $A \leq +70^{\circ}C$ for commercial                |  |  |  |  |

|       |                                    | Operating voltage VDD range as described in DC spec Section 15.1 at |           |        |       |        |                                                     |  |  |  |  |

|       |                                    | Section 15.2.                                                       |           |        |       |        |                                                     |  |  |  |  |

| Param | Characteristic                     | Sym                                                                 | Min       | Typ†   | Max   | Units  | Conditions                                          |  |  |  |  |

| No.   |                                    |                                                                     |           |        |       |        |                                                     |  |  |  |  |

|       | Output High Voltage                |                                                                     |           |        |       |        |                                                     |  |  |  |  |

| D090  | I/O ports (Note 3)                 | Voh                                                                 | VDD-0.7   | -      | -     | v      | IOH = -3.0 mA,                                      |  |  |  |  |

|       |                                    |                                                                     |           |        |       | -      | $VDD = 4.5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |  |  |  |  |

| D090A |                                    |                                                                     | VDD-0.7   | -      | -     | v      | IOH = -2.5 mA,                                      |  |  |  |  |

|       |                                    |                                                                     |           |        |       |        | VDD = 4.5V, -40°C to +125°C                         |  |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)        |                                                                     | VDD-0.7   | -      | -     | V      | IOH = -1.3 mA,                                      |  |  |  |  |

|       |                                    |                                                                     |           |        |       |        | VDD = 4.5V, -40°C to +85°C                          |  |  |  |  |

| D092A |                                    |                                                                     | VDD-0.7   | -      | -     | V      | IOH = -1.0 mA,                                      |  |  |  |  |

|       |                                    |                                                                     |           |        |       |        | VDD = 4.5V, -40°C to +125°C                         |  |  |  |  |

| D150* | Open-Drain High Voltage            | Vod                                                                 | -         | -      | 14    | V      | RA4 pin                                             |  |  |  |  |

|       | Capacitive Loading Specs on        |                                                                     |           |        |       |        |                                                     |  |  |  |  |

|       | Output Pins                        |                                                                     |           |        |       |        |                                                     |  |  |  |  |

| D100  | OSC2 pin                           | Cosc2                                                               |           |        | 15    | pF     | In XT, HS and LP modes when                         |  |  |  |  |

|       |                                    |                                                                     |           |        |       |        | external clock is used to drive                     |  |  |  |  |

|       |                                    |                                                                     |           |        |       |        | OSC1.                                               |  |  |  |  |

| D101  | All I/O pins and OSC2 (in RC mode) | Cio                                                                 |           |        | 50    | pF     |                                                     |  |  |  |  |

The parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

| DC CHA       | RACTERISTICS                       | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |     |          |     |       |                                                                   |  |  |  |

|--------------|------------------------------------|-------------------------------------------------------|-----|----------|-----|-------|-------------------------------------------------------------------|--|--|--|

| Param<br>No. | Characteristic                     | Sym                                                   | Min | Typ<br>+ | Max | Units | Conditions                                                        |  |  |  |

| 110.         | Capacitive Loading Specs on Output |                                                       |     | 1        |     |       |                                                                   |  |  |  |

|              | Pins                               |                                                       |     |          |     |       |                                                                   |  |  |  |

| D100         | OSC2 pin                           | Cosc2                                                 | -   | -        | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |

| D101         | All I/O pins and OSC2 (in RC mode) | Cio                                                   | -   | -        | 50  | pF    |                                                                   |  |  |  |

| D102         | SCL, SDA in I <sup>2</sup> C mode  | Cb                                                    | -   | -        | 400 | pF    |                                                                   |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

| Applicable Devices | 61 | 62 | 62A | <b>B62</b> | 63 | <b>B63</b> | 64 | 64A | <b>R64</b> | 65 | 65A | <b>B65</b> | 66 | 67 |

|--------------------|----|----|-----|------------|----|------------|----|-----|------------|----|-----|------------|----|----|

|                    |    |    |     |            |    |            |    |     |            |    |     |            |    |    |

|       |                                              | Standa                                                | rd Operat                                                                     | ing C | ondition | s (unle | ss otherwise stated)                                                    |  |  |  |

|-------|----------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|-------|----------|---------|-------------------------------------------------------------------------|--|--|--|

|       |                                              | Operatir                                              | ng temper                                                                     | ature | -40°     | Ć≤T     | $A \le +125^{\circ}C$ for extended,                                     |  |  |  |

|       | RACTERISTICS                                 |                                                       |                                                                               |       | -40°     | C ≤T    | $A \le +85^{\circ}C$ for industrial and                                 |  |  |  |

|       | RACIERISTICS                                 | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |                                                                               |       |          |         |                                                                         |  |  |  |

|       |                                              | •                                                     | Operating voltage VDD range as described in DC spec Section 20.1 Section 20.2 |       |          |         |                                                                         |  |  |  |

| Param | Characteristic                               | Sym                                                   | Min                                                                           | Тур   | Max      | Units   | Conditions                                                              |  |  |  |

| No.   |                                              |                                                       |                                                                               | †     |          |         |                                                                         |  |  |  |

|       | Output High Voltage                          |                                                       |                                                                               |       |          |         |                                                                         |  |  |  |

| D090  | I/O ports (Note 3)                           | Vон                                                   | VDD-0.7                                                                       | -     | -        | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D090A |                                              |                                                       | VDD-0.7                                                                       | -     | -        | V       | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)                  |                                                       | VDD-0.7                                                                       | -     | -        | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D092A |                                              |                                                       | VDD-0.7                                                                       | -     | -        | V       | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D150* | Open-Drain High Voltage                      | Vod                                                   | -                                                                             | -     | 14       | V       | RA4 pin                                                                 |  |  |  |

|       | Capacitive Loading Specs on Out-<br>put Pins |                                                       |                                                                               |       |          |         |                                                                         |  |  |  |

| D100  | OSC2 pin                                     | Cosc <sub>2</sub>                                     | -                                                                             | -     | 15       | pF      | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101  | All I/O pins and OSC2 (in RC mode)           | Cio                                                   | -                                                                             | -     | 50       | pF      |                                                                         |  |  |  |

| D102  | SCL, SDA in I <sup>2</sup> C mode            | Cb                                                    | -                                                                             | -     | 400      | pF      |                                                                         |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

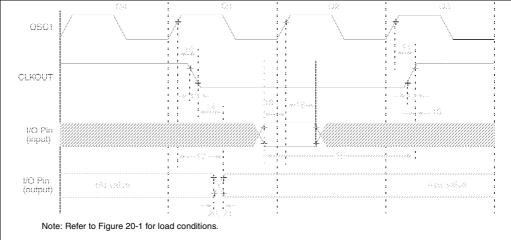

# FIGURE 20-3: CLKOUT AND I/O TIMING

| TABLE 20-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

| Parameter<br>No. | Sym      | Characteristic                                |                         | Min        | Тур† | Max         | Units  | Conditions |

|------------------|----------|-----------------------------------------------|-------------------------|------------|------|-------------|--------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                              | _                       | 75         | 200  | ns          | Note 1 |            |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                              | _                       | 75         | 200  | ns          | Note 1 |            |

| 12*              | TckR     | CLKOUT rise time                              | _                       | 35         | 100  | ns          | Note 1 |            |

| 13*              | TckF     | CLKOUT fall time                              | —                       | 35         | 100  | ns          | Note 1 |            |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid         |                         | _          | _    | 0.5TCY + 20 | ns     | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOUT ↑                 |                         | Tosc + 200 | _    | -           | ns     | Note 1     |

| 16*              | TckH2iol | ort in hold after CLKOUT ↑                    |                         | 0          | _    | _           | ns     | Note 1     |

| 17*              | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid            |                         | _          | 50   | 150         | ns     |            |

| 18*              | TosH2iol | OSC1↑ (Q2 cycle) to Port input                | PIC16 <b>C</b> 63/65A   | 100        | _    | _           | ns     |            |

|                  |          | invalid (I/O in hold time)                    | PIC16LC63/65A           | 200        | _    | _           | ns     |            |

| 19*              | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in | setup time)             | 0          | _    | _           | ns     |            |

| 20*              | TioR     | Port output rise time                         | PIC16 <b>C</b> 63/65A   | _          | 10   | 40          | ns     |            |

|                  |          |                                               | PIC16LC63/65A           | _          | _    | 80          | ns     |            |

| 21*              | TioF     | Port output fall time                         | PIC16 <b>C</b> 63/65A   | _          | 10   | 40          | ns     |            |

|                  |          |                                               | PIC16LC63/65A           | _          | _    | 80          | ns     |            |

| 22††*            | Tinp     | INT pin high or low time                      | IT pin high or low time |            | _    | _           | ns     |            |

| 23††*            | Trbp     | RB7:RB4 change INT high or low                | / time                  | Тсү        | —    | _           | ns     |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

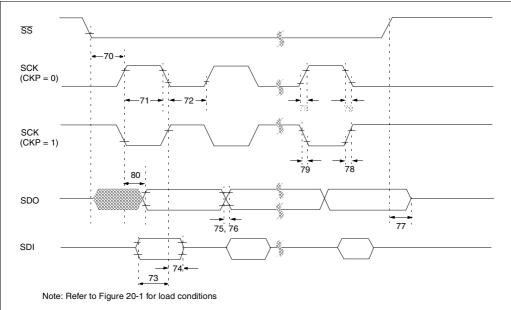

# TABLE 20-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|----------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү      | _    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)                                      | TCY + 20 | —    | _   | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)                                       | TCY + 20 | _    | _   | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 50       | —    | —   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 50       | _    | —   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                                             | _        | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                                             | _        | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10       | —    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | _        | _    | 50  | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

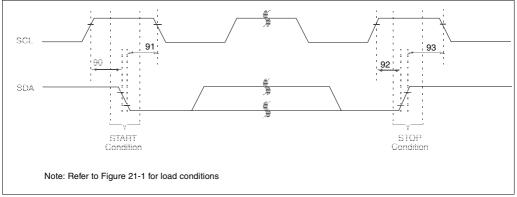

# FIGURE 21-10: I<sup>2</sup>C BUS START/STOP BITS TIMING

#### I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS **TABLE 21-9:**

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Мах | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90*              | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   |     |       | condition                         |

| 91*              | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |

| 92*              | TSU:STO | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 115   |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | -     |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | ns    |                                   |

These parameters are characterized but not tested.

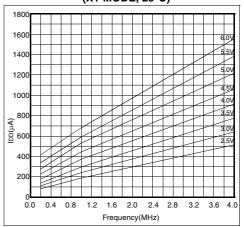

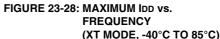

# FIGURE 23-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

# Data based on matrix samples. See first page of this section for details.

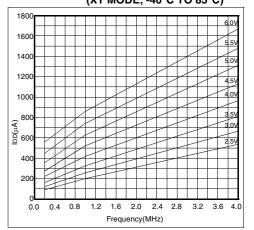

# 24.3 40-Lead Plastic Dual In-line (600 mil) (P)

|        |        | Package Gro | up: Plastic Dual | In-Line (PLA) |        |           |  |  |

|--------|--------|-------------|------------------|---------------|--------|-----------|--|--|

|        |        | Millimeters |                  |               | Inches |           |  |  |

| Symbol | Min    | Max         | Notes            | Min           | Max    | Notes     |  |  |

| α      | 0°     | 10°         |                  | 0°            | 10°    |           |  |  |

| А      | _      | 5.080       |                  | _             | 0.200  |           |  |  |

| A1     | 0.381  | _           |                  | 0.015         | _      |           |  |  |

| A2     | 3.175  | 4.064       |                  | 0.125         | 0.160  |           |  |  |

| В      | 0.355  | 0.559       |                  | 0.014         | 0.022  |           |  |  |

| B1     | 1.270  | 1.778       | Typical          | 0.050         | 0.070  | Typical   |  |  |

| С      | 0.203  | 0.381       | Typical          | 0.008         | 0.015  | Typical   |  |  |

| D      | 51.181 | 52.197      |                  | 2.015         | 2.055  |           |  |  |

| D1     | 48.260 | 48.260      | Reference        | 1.900         | 1.900  | Reference |  |  |

| E      | 15.240 | 15.875      |                  | 0.600         | 0.625  |           |  |  |

| E1     | 13.462 | 13.970      |                  | 0.530         | 0.550  |           |  |  |

| e1     | 2.489  | 2.591       | Typical          | 0.098         | 0.102  | Typical   |  |  |

| eA     | 15.240 | 15.240      | Reference        | 0.600         | 0.600  | Reference |  |  |

| eB     | 15.240 | 17.272      |                  | 0.600         | 0.680  |           |  |  |

| L      | 2.921  | 3.683       |                  | 0.115         | 0.145  |           |  |  |

| N      | 40     | 40          |                  | 40            | 40     |           |  |  |

| S      | 1.270  | -           |                  | 0.050         | -      |           |  |  |

| S1     | 0.508  | -           |                  | 0.020         | -      |           |  |  |

| I <sup>2</sup> C Bus Start/Stop Bits |     |

|--------------------------------------|-----|

| Oscillator Start-up Timer            | 239 |

| Parallel Slave Port                  |     |

| Power-up Timer                       | 239 |

| Reset                                | 239 |

| SPI Mode                             | 243 |

| Timer0                               |     |

| Timer1                               |     |

| USART Synchronous Receive            |     |

| (Master/Slave)                       | 246 |

| Watchdog Timer                       |     |

| PIC16C66                             | 209 |

| Brown-out Reset                      | 071 |

| Capture/Compare/PWM                  | 271 |

| CLKOUT and I/O                       | 273 |

|                                      |     |

| External Clock                       |     |

| I <sup>2</sup> C Bus Data            |     |

| I <sup>2</sup> C Bus Start/Stop Bits |     |

| Oscillator Start-up Timer            |     |

| Power-up Timer                       |     |

| Reset                                |     |

| Timer0                               | 272 |

| Timer1                               | 272 |

| USART Synchronous Receive            |     |

| (Master/Slave)                       | 280 |

| Watchdog Timer                       | 271 |

| PIC16C67                             |     |

| Brown-out Reset                      | 271 |

| Capture/Compare/PWM                  |     |

| CLKOUT and I/O                       |     |

| External Clock                       |     |

| I <sup>2</sup> C Bus Data            |     |

| I <sup>2</sup> C Bus Start/Stop Bits |     |

| Oscillator Start-up Timer            |     |

| Parallel Slave Port                  |     |

| Power-up Timer                       |     |

| Reset                                |     |

| Timer0                               |     |

|                                      |     |

| Timer1                               | 272 |

| USART Synchronous Receive            | 000 |

| (Master/Slave)                       |     |

| Watchdog Timer                       | 271 |

| PIC16CR62                            |     |

| Capture/Compare/PWM                  |     |

| CLKOUT and I/O                       |     |

| External Clock                       |     |

| I <sup>2</sup> C Bus Data            |     |

| I <sup>2</sup> C Bus Start/Stop Bits |     |

| Oscillator Start-up Timer            |     |

| Power-up Timer                       | 207 |

| Reset                                | 207 |

| SPI Mode                             | 211 |

| Timer0                               |     |

|                                      | 208 |

| Timer1                               |     |

| PIC16CR63                              |       |

|----------------------------------------|-------|

| Brown-out Reset                        | . 255 |

| Capture/Compare/PWM                    | . 257 |

| CLKOUT and I/O                         | . 254 |

| External Clock                         |       |

| I <sup>2</sup> C Bus Data              |       |

| I <sup>2</sup> C Bus Start/Stop Bits   |       |

| Oscillator Start-up Timer              |       |

| Power-up Timer                         |       |

| Reset                                  |       |

| SPI Mode<br>Timer0                     |       |

| Timer1                                 |       |

| USART Synchronous Receive              | . 200 |

| (Master/Slave)                         | 262   |

| Watchdog Timer                         |       |

| PIC16CR64                              | . 200 |

| Capture/Compare/PWM                    | . 209 |

| CLKOUT and I/O                         |       |

| External Clock                         |       |

| I <sup>2</sup> C Bus Data              | . 213 |

| I <sup>2</sup> C Bus Start/Stop Bits   | . 212 |

| Oscillator Start-up Timer              |       |

| Parallel Slave Port                    | . 210 |

| Power-up Timer                         |       |

| Reset                                  |       |

| SPI Mode                               |       |

| Timer0                                 |       |

| Timer1                                 |       |

| Watchdog Timer                         | . 207 |

| PIC16CR65<br>Brown-out Reset           | 255   |

| Capture/Compare/PWM                    |       |

| CLKOUT and I/O                         |       |

| External Clock                         |       |

| I <sup>2</sup> C Bus Data              |       |

| I <sup>2</sup> C Bus Start/Stop Bits   |       |

| Oscillator Start-up Timer              |       |

| Parallel Slave Port                    |       |

| Power-up Timer                         |       |

| Reset                                  | . 255 |

| SPI Mode                               | . 259 |

| Timer0                                 | . 256 |

| Timer1                                 | . 256 |

| USART Synchronous Receive              |       |

| (Master/Slave)                         | . 262 |

| Watchdog Timer                         |       |

| Power-up Timer                         |       |

| PWM Output                             |       |

| RB0/INT Interrupt                      |       |

| RX Pin Sampling                        |       |

| SPI Mode, Master/Slave Mode,           | 93    |

| No SS Control                          | 88    |

| SPI Mode, Slave Mode With SS Control   | 88    |

| SPI Slave Mode (CKE = 1)               |       |

| SPI Slave Mode Timing (CKE = 0)        | 93    |

| Timer0 with External Clock             |       |

| TMR0 Interrupt Timing                  |       |

| USART Asynchronous Master Transmission |       |

| USART Asynchronous Master Transmission |       |

| (Back to Back)                         |       |

| USART Asynchronous Reception           | . 114 |

| USART Synchronous Reception in         |       |

| Master Mode                            |       |

| USART Synchronous Tranmission          |       |

| Wake-up from SLEEP Through Interrupts  | . 142 |

-

-