Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

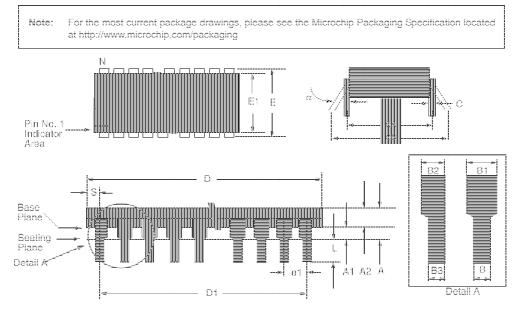

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc63t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.1 STATUS REGISTER

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The STATUS register, shown in Figure 4-9, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                                                             | R/W-0                                                      | R-1                                        | R-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-x                                                               | R/W-x                         | R/W-x        |                                                                                     |

|----------|-----------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|--------------|-------------------------------------------------------------------------------------|

| IRP      | RP1                                                                               | RP0                                                        | TO                                         | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Z                                                                   | DC                            | С            | R = Readable bit                                                                    |

| bit7     |                                                                                   |                                                            |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                               | bit0         | W = Writable bit<br>- n = Value at POR reset<br>x = unknown                         |

| bit 7:   | IRP: Regls<br>1 = Bank 2<br>0 = Bank 0                                            | , 3 (100h - 1                                              | 1FFh)                                      | ed for indire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ect addressir                                                       | ng)                           |              |                                                                                     |

| bit 6-5: | <b>RP1:RP0</b> :<br>11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank<br>Each bank | 3 (180h - 1)<br>2 (100h - 1<br>1 (80h - FF<br>0 (00h - 7F) | FFh)<br>7Fh)<br>h)<br>n)                   | bits (used fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | or direct addr                                                      | essing)                       |              |                                                                                     |

| bit 4:   | <b>TO</b> : Time-or<br>1 = After points $0 = A WDT$                               | ower-up, CL                                                |                                            | uction, or S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LEEP instruc                                                        | tion                          |              |                                                                                     |

| bit 3:   | <b>PD</b> : Power-<br>1 = After po<br>0 = By exec                                 | ower-up or                                                 |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tion                                                                |                               |              |                                                                                     |

| bit 2:   | <b>Z</b> : Zero bit<br>1 = The res $0 = The res$                                  |                                                            |                                            | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tion is zero<br>tion is not ze                                      | ero                           |              |                                                                                     |

| bit 1:   |                                                                                   | -out from th                                               | e 4th low o                                | order bit of t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | he result occ                                                       |                               | nstructions) | (For borrow the polarity is reversed).                                              |

| bit 0:   | 1 = A carry<br>0 = No carr<br>Note: a sub                                         | -out from th<br>y-out from<br>otraction is o               | the most sig<br>the most si<br>executed by | nificant bit of gnificant bit of gnifica | of the result of<br>t of the result<br>tof the result<br>two's comp | occurred<br>t<br>lement of th | ne second of | orrow the polarity is reversed).<br>perand.<br>ow order bit of the source register. |

### FIGURE 4-9: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

## TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                       |

|------------|------|-------------|--------------------------------------------------------------------------------|

| RA0        | bit0 | TTL         | Input/output                                                                   |

| RA1        | bit1 | TTL         | Input/output                                                                   |

| RA2        | bit2 | TTL         | Input/output                                                                   |

| RA3        | bit3 | TTL         | Input/output                                                                   |

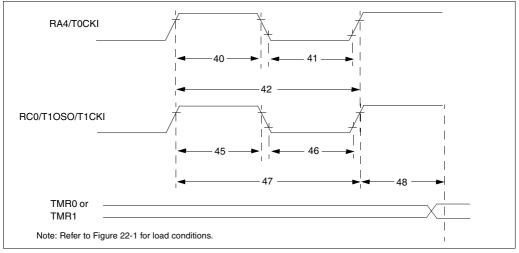

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0.<br>Output is open drain type. |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

### TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5              | Bit 4        | Bit 3                  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|--------------------|--------------|------------------------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | —     | —     | RA5 <sup>(1)</sup> | RA4          | RA3                    | RA2   | RA1   | RA0   | xx xxxx                  | uu uuuu                   |

| 85h     | TRISA | —     | —     | PORTA Data         | Direction Re | egister <sup>(1)</sup> |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

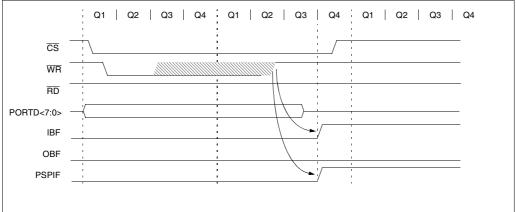

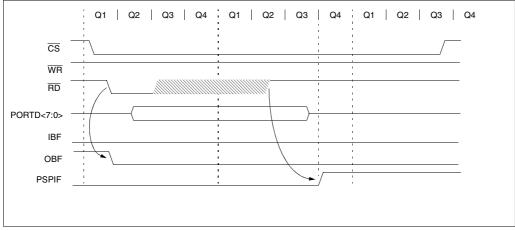

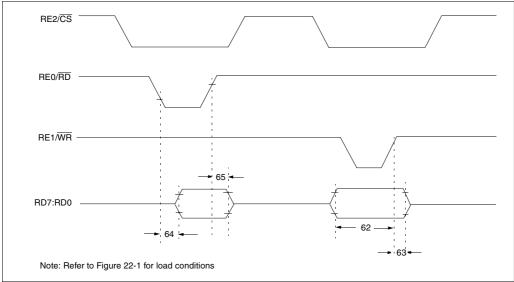

### FIGURE 5-12: PARALLEL SLAVE PORT WRITE WAVEFORMS

### TABLE 5-13: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name  | Bit 7 | Bit 6 | Bit 5               | Bit 4               | Bit 3 | Bit 2    | Bit 1         | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|---------------------|---------------------|-------|----------|---------------|--------|--------------------------|---------------------------|

| 08h     | PORTD | PSP7  | PSP6  | PSP5                | PSP4                | PSP3  | PSP2     | PSP1          | PSP0   | xxxx xxxx                | uuuu uuuu                 |

| 09h     | PORTE | _     |       |                     | _                   | _     | RE2      | RE1           | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV                | PSPMODE             | _     | PORTE Da | ata Directior | n Bits | 0000 -111                | 0000 -111                 |

| 0Ch     | PIR1  | PSPIF | (1)   | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF | CCP1IF   | TMR2IF        | TRM1IF | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE | (1)   | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE | CCP1IE   | TMR2IE        | TMR1IE | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by the PSP.

Note 1: These bits are reserved, always maintain these bits clear.

2: These bits are implemented on the PIC16C65/65A/R65/67 only.

### 8.5 <u>Resetting Timer1 using a CCP Trigger</u> Output

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

CCP2 is implemented on the PIC16C63/R63/65/65A/ R65/66/67 only.

If CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCPxM3:CCPxM0 = 1011), this signal will reset Timer1.

Note: The "special event trigger" from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF(PIR1<0>).

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If the Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for the Timer1 module.

### 8.6 <u>Resetting of TMR1 Register Pair</u> (TMR1H:TMR1L)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR1H and TMR1L registers are not reset to 00h on a POR or any other reset except by the CCP1 or CCP2 special event trigger.

The T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescaler. In all other resets, the register is unaffected.

### 8.7 <u>Timer1 Prescaler</u>

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address              | Name   | Bit 7                | Bit 6   | Bit 5               | Bit 4               | Bit 3          | Bit 2       | Bit 1       | Bit 0  | Value<br>PC<br>BC | ,    | all c | e on<br>other<br>sets |

|----------------------|--------|----------------------|---------|---------------------|---------------------|----------------|-------------|-------------|--------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON | GIE                  | PEIE    | TOIE                | INTE                | RBIE           | TOIF        | INTF        | RBIF   | 0000              | 000x | 0000  | 000u                  |

| 0Ch                  | PIR1   | PSPIF <sup>(2)</sup> | (3)     | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF          | CCP1IF      | TMR2IF      | TMR1IF | 0000              | 0000 | 0000  | 0000                  |

| 8Ch                  | PIE1   | PSPIE <sup>(2)</sup> | (3)     | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE          | CCP1IE      | TMR2IE      | TMR1IE | 0000              | 0000 | 0000  | 0000                  |

| 0Eh                  | TMR1L  | Holding re           | egister | for the Lea         | st Significar       | nt Byte of the | e 16-bit TN | /R1 registe | er     | xxxx              | xxxx | uuuu  | uuuu                  |

| 0Fh                  | TMR1H  | Holding re           | egister | for the Mos         | t Significan        | t Byte of the  | 16-bit TM   | IR1 registe | r      | xxxx              | xxxx | uuuu  | uuuu                  |

| 10h                  | T1CON  | _                    |         | T1CKPS1             | T1CKPS0             | T1OSCEN        | T1SYNC      | TMR1CS      | TMR10N | 00                | 0000 | uu    | uuuu                  |

### TABLE 8-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: The USART is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

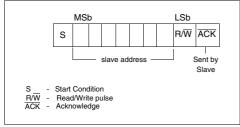

### 11.4.2 ADDRESSING I<sup>2</sup>C DEVICES

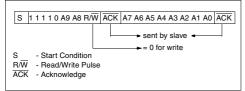

There are two address formats. The simplest is the 7-bit address format with a R/W bit (Figure 11-15). The more complex is the 10-bit address with a R/W bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

## FIGURE 11-16: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

### 11.4.3 TRANSFER ACKNOWLEDGE

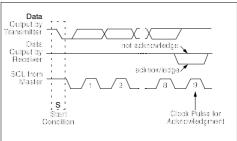

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

### FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

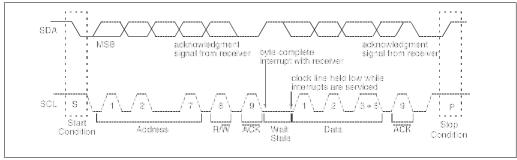

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

### FIGURE 11-18: DATA TRANSFER WAIT STATE

### 11.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

## FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W=0         Receiving Data         ACK         Receiving Data         ACK           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | F 7<br>I I<br>I I<br>/ I PI<br>- I<br>- I<br>- I<br>- I<br>- I<br>- I<br>- I<br>- |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bus Master<br>terminates<br>transfer                                              |

| SSPOV (SSPCON<6>)<br>Bit SSPOV is set because the SSPBUF register is still full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

| ACK is not sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

#### Instruction Descriptions 14.1

| Add Lite           | ral and                                                                                                                                                                               | w                                                      |                                                                                                                                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ <i>label</i> ] A | DDLW                                                                                                                                                                                  | k                                                      |                                                                                                                                                                                                                                                |

| $0 \le k \le 25$   | 55                                                                                                                                                                                    |                                                        |                                                                                                                                                                                                                                                |

| (W) + k –          | → (W)                                                                                                                                                                                 |                                                        |                                                                                                                                                                                                                                                |

| C, DC, Z           |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| 11                 | 111x                                                                                                                                                                                  | kkkk                                                   | kkkk                                                                                                                                                                                                                                           |

| added to t         | he eight b                                                                                                                                                                            | it literal 'k'                                         | and the                                                                                                                                                                                                                                        |

| 1                  |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| 1                  |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| Q1                 | Q2                                                                                                                                                                                    | Q3                                                     | Q4                                                                                                                                                                                                                                             |

| Decode             | Read<br>literal 'k'                                                                                                                                                                   | Process<br>data                                        | Write to<br>W                                                                                                                                                                                                                                  |

| After Inst         | W =<br>ruction                                                                                                                                                                        | 0x10<br>0x25                                           |                                                                                                                                                                                                                                                |

|                    | [ <i>label</i> ] All<br>$0 \le k \le 2\xi$<br>(W) + k -<br>C, DC, Z<br>11<br>The conte<br>added to the<br>result is pl<br>1<br>1<br>Q1<br>Decode<br>ADDLW<br>Before Inn<br>After Inst | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$ | $0 \le k \le 255$ (W) + k → (W) C, DC, Z $11  111x  kkkk$ The contents of the W register added to the eight bit literal 'k' result is placed in the W regist 1 1 2 2 2 2 2 3 2 2 2 3 2 2 3 2 3 2 3 3 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |

| ANDLW             | AND Lite           | eral with                                                                                                           | W               |               |  |  |  |  |

|-------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A | NDLW                                                                                                                | k               |               |  |  |  |  |

| Operands:         | $0 \le k \le 25$   | 55                                                                                                                  |                 |               |  |  |  |  |

| Operation:        | (W) .AND           | D. (k) $\rightarrow$ (                                                                                              | W)              |               |  |  |  |  |

| Status Affected:  | Z                  |                                                                                                                     |                 |               |  |  |  |  |

| Encoding:         | 11                 | 1001                                                                                                                | kkkk            | kkkk          |  |  |  |  |

| Description:      | AND'ed wi          | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                 |               |  |  |  |  |

| Words:            | 1                  |                                                                                                                     |                 |               |  |  |  |  |

| Cycles:           | 1                  |                                                                                                                     |                 |               |  |  |  |  |

| Q Cycle Activity: | Q1                 | Q2                                                                                                                  | Q3              | Q4            |  |  |  |  |

|                   | Decode             | Read<br>literal "k"                                                                                                 | Process<br>data | Write to<br>W |  |  |  |  |

| Example           | ANDLW              | 0x5F                                                                                                                |                 |               |  |  |  |  |

|                   | Before In          | Before Instruction                                                                                                  |                 |               |  |  |  |  |

|                   | After Inst         |                                                                                                                     | 0xA3            |               |  |  |  |  |

|                   |                    | W =                                                                                                                 | 0x03            |               |  |  |  |  |

| ADDWF             | Add W a                                                        | nd f                       |                                                       |                         |

|-------------------|----------------------------------------------------------------|----------------------------|-------------------------------------------------------|-------------------------|

| Syntax:           | [ <i>label</i> ] A                                             | DDWF                       | f,d                                                   |                         |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | .7                         |                                                       |                         |

| Operation:        | (W) + (f)                                                      | $\rightarrow$ (dest        | ination)                                              |                         |

| Status Affected:  | C, DC, Z                                                       |                            |                                                       |                         |

| Encoding:         | 00                                                             | 0111                       | dfff                                                  | ffff                    |

| Description:      | register 'f'.                                                  | If 'd' is 0<br>egister. If | the W reg<br>the result i<br>'d' is 1 the<br>ter 'f'. | s stored                |

| Words:            | 1                                                              |                            |                                                       |                         |

| Cycles:           | 1                                                              |                            |                                                       |                         |

| Q Cycle Activity: | Q1                                                             | Q2                         | Q3                                                    | Q4                      |

|                   | Decode                                                         | Read<br>register<br>'f'    | Process<br>data                                       | Write to<br>destination |

| Evennle           | ADDUE                                                          | BOD                        | <u>.</u>                                              |                         |

| Example           | ADDWF                                                          |                            | 0                                                     |                         |

|                   | Before In                                                      | structior                  | ו<br>0x17                                             |                         |

|                   |                                                                | FSR =                      | 0xC2                                                  |                         |

|                   | After Inst                                                     |                            |                                                       |                         |

|                   |                                                                | W =<br>FSR =               | 0xD9<br>0xC2                                          |                         |

| ANDWF             | AND W v                                                        | vith f                    |                 |                      |

|-------------------|----------------------------------------------------------------|---------------------------|-----------------|----------------------|

| Syntax:           | [ <i>label</i> ] Al                                            | NDWF                      | f,d             |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                         |                 |                      |

| Operation:        | (W) .AND                                                       | 0. (f) $\rightarrow$ (e   | destinatio      | on)                  |

| Status Affected:  | Z                                                              |                           |                 |                      |

| Encoding:         | 0.0                                                            | 0101                      | dfff            | ffff                 |

| Description:      | AND the W<br>is 0 the res<br>ter. If 'd' is<br>register 'f'.   | sult is stor<br>1 the res | red in the      | W regis-             |

| Words:            | 1                                                              |                           |                 |                      |

| Cycles:           | 1                                                              |                           |                 |                      |

| Q Cycle Activity: | Q1                                                             | Q2                        | Q3              | Q4                   |

|                   | Decode                                                         | Read<br>register<br>'f'   | Process<br>data | Write to destination |

| Example           | ANDWF                                                          | FSR,                      | 1               |                      |

|                   | Before In                                                      |                           |                 |                      |

|                   |                                                                | W =<br>FSR =              | 0x17<br>0xC2    |                      |

|                   | After Inst                                                     |                           | 0102            |                      |

|                   |                                                                | W =                       | 0x17            |                      |

|                   |                                                                | FSR =                     | 0x02            |                      |

| SUBWF             | Subtract                                                                   | W from f                     |                                   |                      |

|-------------------|----------------------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|

| Syntax:           | [ label ]                                                                  | SUBWF                        | f,d                               |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$ | ,                            |                                   |                      |

| Operation:        | (f) - (W) $\rightarrow$                                                    | (destina                     | tion)                             |                      |

| Status Affected:  | C, DC, Z                                                                   |                              |                                   |                      |

| Encoding:         | 00                                                                         | 0010                         | dfff                              | ffff                 |

| Description:      | Subtract (2'<br>ister from re<br>stored in the<br>result is sto            | egister 'f'. l<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the        |

| Words:            | 1                                                                          |                              |                                   |                      |

| Cycles:           | 1                                                                          |                              |                                   |                      |

| Q Cycle Activity: | Q1                                                                         | Q2                           | Q3                                | Q4                   |

|                   | Decode                                                                     | Read<br>register 'f'         | Process<br>data                   | Write to destination |

| Example 1:        | SUBWF                                                                      | reg1,1                       |                                   |                      |

|                   | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 3                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | Z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 1                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | nositive             |

|                   | z                                                                          | =                            | 0                                 | poolavo              |

| Example 2:        | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 2                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | Z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 0                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | 7010                 |

|                   | z                                                                          | =                            | 1                                 | 2010                 |

| Example 3:        | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 1                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 0xFF                              |                      |

|                   | W<br>C                                                                     | =                            | 2<br>0; result is                 | negative             |

|                   | z                                                                          | =                            | 0                                 | guivo                |

|                   |                                                                            |                              |                                   |                      |

| SWAPF             | Swap Ni                                                                                                                                                               | bbles in                                                        | f               |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:           | [label]                                                                                                                                                               | SWAPF 1                                                         | ,d              |                      |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$<br>$d \in [0,1]$                                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                 |                      |  |  |  |  |  |

| Operation:        | · · ·                                                                                                                                                                 | ightarrow (destin $ ightarrow$ (destin                          |                 |                      |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                  |                                                                 |                 |                      |  |  |  |  |  |

| Encoding:         | 0 0                                                                                                                                                                   | 1110                                                            | dfff            | ffff                 |  |  |  |  |  |

| Description:      | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |                                                                 |                 |                      |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                     |                                                                 |                 |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                     |                                                                 |                 |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                    | Q2                                                              | Q3              | Q4                   |  |  |  |  |  |

|                   | Decode                                                                                                                                                                | Read<br>register 'f'                                            | Process<br>data | Write to destination |  |  |  |  |  |

| Example           | SWAPF                                                                                                                                                                 | REG,                                                            | 0               |                      |  |  |  |  |  |

|                   | Before In                                                                                                                                                             | struction                                                       |                 |                      |  |  |  |  |  |

|                   | REG1 = 0xA5                                                                                                                                                           |                                                                 |                 |                      |  |  |  |  |  |

|                   | After Instruction                                                                                                                                                     |                                                                 |                 |                      |  |  |  |  |  |

|                   |                                                                                                                                                                       | REG1<br>W                                                       | = 0x/<br>= 0x5  | .0                   |  |  |  |  |  |

| TRIS             | Load TR                                                                                                                                                                             | IS Regis | ster |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|--|--|--|--|

| Syntax:          | [label]                                                                                                                                                                             | TRIS     | f    |      |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                   |          |      |      |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |          |      |      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |          |      |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                  | 0000     | 0110 | Offf |  |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |          |      |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |          |      |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |          |      |      |  |  |  |  |

| Example          |                                                                                                                                                                                     |          |      |      |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |          |      |      |  |  |  |  |

|                  |                                                                                                                                                                                     |          |      |      |  |  |  |  |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 15.3 DC Characteristics: PIC16C61-04 (Commercial, Industrial, Extended) PIC16C61-20 (Commercial, Industrial, Extended) PIC16LC61-04 (Commercial, Industrial)