Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| - · ·                      |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

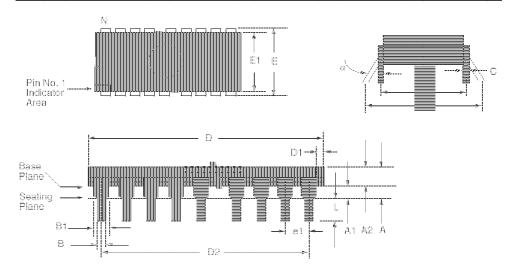

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64a-04-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C6X

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

# FIGURE 4-12: PIE1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 8Ch)

| RW-0     | R/W-0                                                                                                                                     | U-0      | U-0          | R/W-0    | R/W-0  | R/W-0  | R/W-0  |                                                                              |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|----------|--------|--------|--------|------------------------------------------------------------------------------|--|--|--|--|--|

| _        | _                                                                                                                                         | _        | _            | SSPIE    | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                             |  |  |  |  |  |

| bit7     |                                                                                                                                           |          |              |          |        |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |  |  |  |  |  |

| bit 7-6: | it 7-6: Reserved: Always maintain these bits clear.                                                                                       |          |              |          |        |        |        |                                                                              |  |  |  |  |  |

| bit 5-4: | Unimplemented: Read as '0'                                                                                                                |          |              |          |        |        |        |                                                                              |  |  |  |  |  |

| bit 3:   | SSPIE: Synchronous Serial Port Interrupt Enable bit  1 = Enables the SSP interrupt  0 = Disables the SSP interrupt                        |          |              |          |        |        |        |                                                                              |  |  |  |  |  |

| bit 2:   | CCP1IE: C0<br>1 = Enables<br>0 = Disables                                                                                                 | the CCP1 | I interrupt  | bit      |        |        |        |                                                                              |  |  |  |  |  |

| bit 1:   | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit  1 = Enables the TMR2 to PR2 match interrupt  0 = Disables the TMR2 to PR2 match interrupt |          |              |          |        |        |        |                                                                              |  |  |  |  |  |

| bit 0:   | TMR1IE: TM<br>1 = Enables<br>0 = Disables                                                                                                 | the TMR1 | 1 overflow i | nterrupt | t      |        |        |                                                                              |  |  |  |  |  |

## FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| R/W-0    | R/W-0                                         | R-0                                                                       | R-0                                   | R/W-0                                 | R/W-0                           | R/W-0         | R/W-0    |                                                                              |

|----------|-----------------------------------------------|---------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------|---------------|----------|------------------------------------------------------------------------------|

| _        | _                                             | RCIF                                                                      | TXIF                                  | SSPIF                                 | CCP1IF                          | TMR2IF        | TMR1IF   | R = Readable bit                                                             |

| oit7     |                                               |                                                                           |                                       |                                       |                                 |               | bit0     | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7-6: | Reserved:                                     | Always ma                                                                 | intain thes                           | e bits clear.                         |                                 |               |          |                                                                              |

| bit 5:   | RCIF: USA<br>1 = The US<br>0 = The US         | ART receiv                                                                | e buffer is                           | full (cleared                         | d by reading                    | RCREG)        |          |                                                                              |

| bit 4:   | TXIF: USA<br>1 = The US<br>0 = The US         | ART transi                                                                | nit buffer is                         | empty (cle                            | ared by writi                   | ng to TXRE    | G)       |                                                                              |

| bit 3:   | SSPIF: Syr<br>1 = The tra<br>0 = Waiting      | nsmission/i                                                               | reception is                          |                                       | ag bit<br>(must be clea         | ared in softv | vare)    |                                                                              |

| bit 2:   | 0 = No TMI<br>Compare N                       | ode<br>1 register c<br>R1 register<br>Mode<br>1 register c<br>R1 register | apture occ<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | t be cleared i<br>ed (must be o | ,             | oftware) |                                                                              |

| bit 1:   | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TMI | o PR2 mat                                                                 | ch occurre                            | d (must be                            | bit<br>cleared in so            | ftware)       |          |                                                                              |

| bit 0:   | <b>TMR1IF</b> : T<br>1 = TMR1 i<br>0 = No TMI | egister ove                                                               | rflow occu                            | rred (must l                          | oe cleared in                   | software)     |          |                                                                              |

|          |                                               |                                                                           |                                       |                                       |                                 |               |          |                                                                              |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 5.6 <u>I/O Programming Considerations</u>

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stavs in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential read-modify-write instructions on an I/O port.

# EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

;Initial PORT settings: PORTB<7:4> Inputs

PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

; not connected to other circuitry

PORT latch PORT pins

BCF PORTB, 7

; 01pp pppp

11pp pppp

BCF PORTB, 6

; 10pp pppp

11pp pppp

BSF STATUS, RPO

BCF TRISB, 7

; 10pp pppp

11pp pppp

BCF TRISB, 6

; 10pp pppp

10pp pppp

; Note that the user may have expected the

;pin values to be 00pp pppp. The 2nd BCF

; caused RB7 to be latched as the pin value

: (high).

```

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

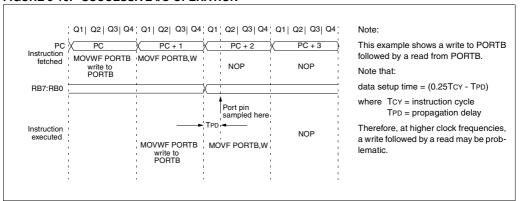

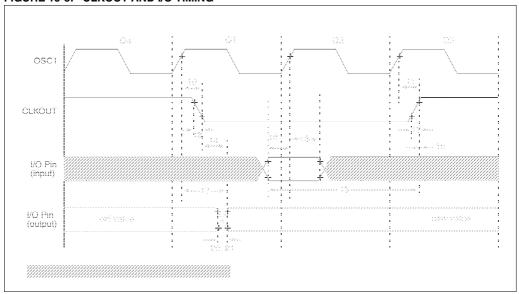

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU separate than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-10: SUCCESSIVE I/O OPERATION

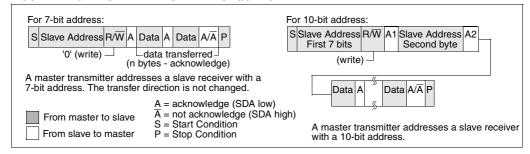

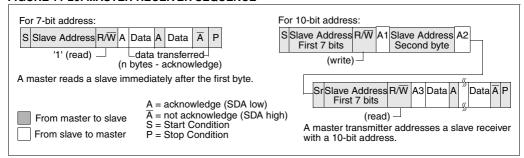

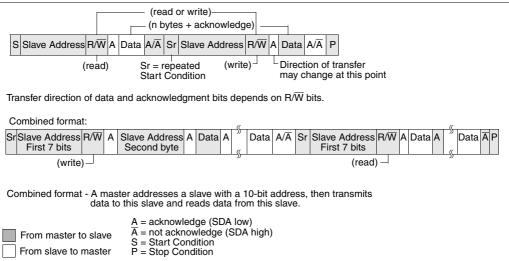

Figure 11-19 and Figure 11-20 show Master-transmitter and Master-receiver data transfer sequences.

When a master does not wish to relinquish the bus (by generating a STOP condition), a repeated START condition (Sr) must be generated. This condition is identical to the start condition (SDA goes high-to-low while

SCL is high), but occurs after a data transfer acknowledge pulse (not the bus-free state). This allows a master to send "commands" to the slave and then receive the requested information or to address a different slave device. This sequence is shown in Figure 11-21.

#### FIGURE 11-19: MASTER-TRANSMITTER SEQUENCE

#### FIGURE 11-20: MASTER-RECEIVER SEQUENCE

#### FIGURE 11-21: COMBINED FORMAT

# PIC16C6X

#### 13.3 Reset

#### **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The PIC16CXX differentiates between various kinds of reset:

- · Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) Not on PIC16C61/62/ 64/65

Some registers are not affected in any reset condition, their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on MCLR or WDT Reset, on MCLR reset during SLEEP, and on Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation.

The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 13-7, Table 13-8, and Table 13-9. These bits are used in software to determine the nature of the reset. See Table 13-12 for a full description of reset states of all registers.

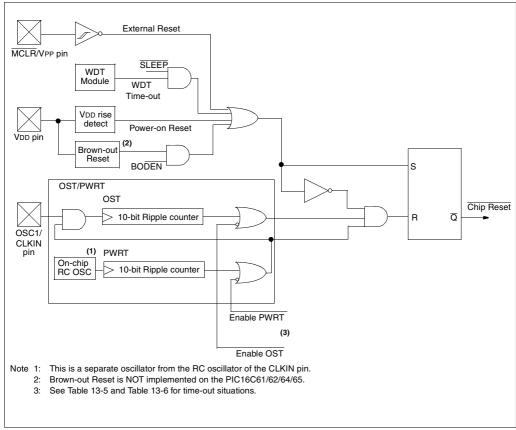

A simplified block diagram of the on-chip reset circuit is shown in Figure 13-9.

On the PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67, the MCLR reset path has a noise filter to detect and ignore small pulses. See parameter #34 for pulse width specifications.

It should be noted that a WDT Reset does not drive the MCLR pin low.

FIGURE 13-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

FIGURE 15-3: CLKOUT AND I/O TIMING

TABLE 15-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter No. | Sym      | Characteristic                                          |                                                           | Min | Typ†        | Max | Units  | Conditions |

|---------------|----------|---------------------------------------------------------|-----------------------------------------------------------|-----|-------------|-----|--------|------------|

| 10*           | TosH2ckL | OSC1↑ to CLKOUT↓                                        |                                                           | _   | 15          | 30  | ns     | Note 1     |

| 11*           | TosH2ckH | OSC1↑ to CLKOUT↑                                        |                                                           | _   | 15          | 30  | ns     | Note 1     |

| 12*           | TckR     | CLKOUT rise time                                        | _                                                         | 5   | 15          | ns  | Note 1 |            |

| 13*           | TckF     | CLKOUT fall time                                        | _                                                         | 5   | 15          | ns  | Note 1 |            |

| 14*           | TckL2ioV | CLKOUT ↓ to Port out valid                              | _                                                         |     | 0.5Tcy + 20 | ns  | Note 1 |            |

| 15*           | TioV2ckH | Port in valid before CLKOU                              | 0.25Tcy + 25                                              |     | _           | ns  | Note 1 |            |

| 16*           | TckH2ioI | Port in hold after CLKOUT                               | 0                                                         |     | _           | ns  | Note 1 |            |

| 17*           | TosH2ioV | OSC1↑ (Q1 cycle) to Port                                | _                                                         |     | 80 - 100    | ns  |        |            |

| 18*           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port (I/O in hold time) | OSC1↑ (Q2 cycle) to Port input invalid (I/O in hold time) |     |             | _   | ns     |            |

| 19*           | TioV2osH | Port input valid to OSC1↑ (time)                        | (I/O in setup                                             | TBD | -           | _   | ns     |            |

| 20*           | TioR     | Port output rise time                                   | PIC16 <b>C</b> 61                                         | _   | 10          | 25  | ns     |            |

|               |          |                                                         | PIC16 <b>LC</b> 61                                        | _   | _           | 60  | ns     |            |

| 21*           | TioF     | Port output fall time                                   | PIC16 <b>C</b> 61                                         | _   | 10          | 25  | ns     |            |

|               |          |                                                         | PIC16 <b>LC</b> 61                                        |     | _           | 60  | ns     |            |

| 22††*         | Tinp     | RB0/INT pin high or low tin                             | ne                                                        | 20  | _           | _   | ns     | -          |

| 23††*         | Trbp     | RB7:RB4 change int high                                 | or low time                                               | 20  |             | _   | ns     |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

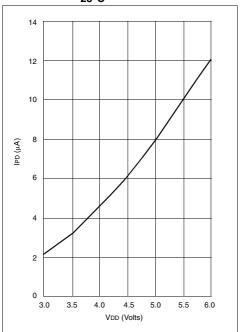

FIGURE 16-6: TYPICAL IPD VS. VDD

WATCHDOG TIMER ENABLED

25°C

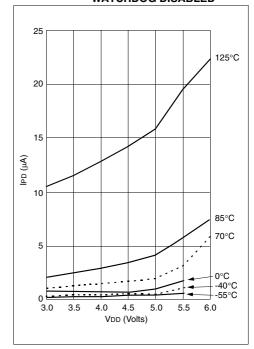

FIGURE 16-7: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

Data based on matrix samples. See first page of this section for details.

## **ELECTRICAL CHARACTERISTICS FOR PIC16C62/64**

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                     | 55°C to +85°C        |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | -0.3V to +7.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +14V           |

| Voltage on RA4 with respect to Vss                                 | 0V to +14V           |

| Total power dissipation (Note 1)                                   | 1.0W                 |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       | 250 mA               |

| Input clamp current, Iικ (VI < 0 or VI > VDD)                      | ±20 mA               |

| Output clamp current, loκ (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA, PORTB, and PORTE* (combined)        | 200 mA               |

| Maximum current sourced by PORTA, PORTB, and PORTE* (combined)     | 200 mA               |

| Maximum current sunk by PORTC and PORTD* (combined)                | 200 mA               |

| Maximum current sourced by PORTC and PORTD* (combined)             | 200 mA               |

| * PORTD and PORTE not available on the PIC16C62.                   |                      |

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62-04<br>PIC16C64-04                                                                                 | PIC16C62-10<br>PIC16C64-10                                                                            | PIC16C62-20<br>PIC16C64-20                                                                 | PIC16LC62-04<br>PIC16LC64-04                                                                              | JW Devices                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V IDD: 3.8 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                      | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 μA typ. at 4V Freq:4 MHz max.                     | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 μA typ. at 4V Freq:4 MHz max.          | VDD: 3.0V to 6.0V IDD: 3.8 mA max. at 3.0V IPD: 13.5 $\mu$ A max. at 3V Freq: 4 MHz max.                  | VDD: 4.0V to 6.0V IDD: 3.8 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                  |

| XT  | VDD: 4.0V to 6.0V IDD: 3.8 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                      | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq:4 MHz max.            | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq:4 MHz max. | VDD: 3.0V to 6.0V IDD: 3.8 mA max. at 3.0V IPD: 13.5 $\mu$ A max. at 3.0V Freq: 4 MHz max.                | VDD: $4.0V$ to $6.0V$ IDD: $3.8$ mA max. at $5.5V$ IPD: $21~\mu$ A max. at $4V$ Freq:4 MHz max.        |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq:4 MHz max.              | VDD: $4.5V$ to $5.5V$ IDD: $15$ mA max. at $5.5V$ IPD: $1.5$ $\mu$ A typ. at $4.5V$ Freq: 10 MHz max. | VDD: 4.5V to 5.5V IDD: 30 mA max. at 5.5V IPD: 1.5 $\mu$ A typ. at 4.5V Freq: 20 MHz max.  | Not recommended for use in HS mode                                                                        | VDD: 4.5V to 5.5V IDD: 30 mA max. at 5.5V IPD: 1.5 $\mu$ A typ. at 4.5V Freq: 20 MHz max.              |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq:200 kHz max. | Not recommended for use in LP mode                                                                    | Not recommended for use in LP mode                                                         | VDD: 3.0V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq:200 kHz max. | VDD: 3.0V to 6.0V IDD: 48 $\mu$ A max. at 32 kHz, 3.0V IPD:13.5 $\mu$ A max. at 3.0V Freq:200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (Vol x IOL)

#### 17.2 DC Characteristics: PIC16LC62/64-04 (Commercial, Industrial)

| DC CHA | ARACTERISTICS                                                     |      | Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C |      |      |              |                                                               |  |  |  |

|--------|-------------------------------------------------------------------|------|--------------------------------------------------------------------------------------|------|------|--------------|---------------------------------------------------------------|--|--|--|

| Param  | Characteristic                                                    | Sym  | Min                                                                                  | Typ† |      | ; ≤<br>Units | Ta ≤ +70°C for commercial  Conditions                         |  |  |  |

| No.    |                                                                   | -    |                                                                                      |      |      |              |                                                               |  |  |  |

| D001   | Supply Voltage                                                    | VDD  | 3.0                                                                                  | -    | 6.0  | ٧            | LP, XT, RC osc configuration (DC - 4 MHz)                     |  |  |  |

| D002*  | RAM Data Retention<br>Voltage (Note 1)                            | VDR  | -                                                                                    | 1.5  | -    | ٧            |                                                               |  |  |  |

| D003   | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR | -                                                                                    | Vss  | -    | V            | See section on Power-on Reset for details                     |  |  |  |

| D004*  | VDD rise rate to ensure internal Power-on Reset signal            | SVDD | 0.05                                                                                 | -    | -    | V/ms         | See section on Power-on Reset for details                     |  |  |  |

| D010   | Supply Current (Note 2, 5)                                        | IDD  | -                                                                                    | 2.0  | 3.8  | mA           | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4) |  |  |  |

| D010A  |                                                                   |      | -                                                                                    | 22.5 | 48   | μΑ           | LP osc configuration FOSC = 32 kHz, VDD = 3.0V, WDT disabled  |  |  |  |

| D020   | Power-down Current                                                | IPD  | -                                                                                    | 7.5  | 30   | μΑ           | VDD = 3.0V, WDT enabled, -40°C to +85°C                       |  |  |  |

| D021   | (Note 3, 5)                                                       |      | -                                                                                    | 0.9  | 13.5 | μA           | VDD = 3.0V, WDT disabled, 0°C to +70°C                        |  |  |  |

| D021A  |                                                                   |      | -                                                                                    | 0.9  | 18   | μΑ           | VDD = 3.0V, WDT disabled, -40°C to +85°C                      |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

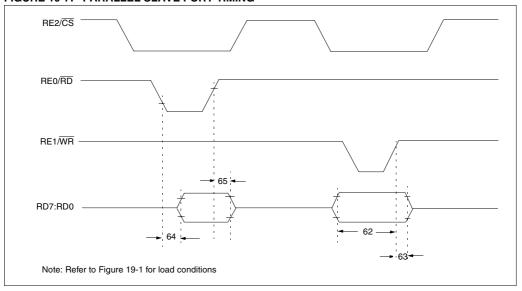

FIGURE 19-7: PARALLEL SLAVE PORT TIMING

TABLE 19-7: PARALLEL SLAVE PORT REQUIREMENTS

| Parameter No. | Sym      | Characteristic                               |                    | Min | Typ† | Max | Units | Conditions |

|---------------|----------|----------------------------------------------|--------------------|-----|------|-----|-------|------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS↑ (setup time) |                    |     | _    | _   | ns    |            |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data–in invalid (hold          | PIC16 <b>C</b> 65  | 20  | _    | _   | ns    |            |

|               |          | time)                                        | PIC16 <b>LC</b> 65 | 35  | _    | _   | ns    |            |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid                |                    |     | _    | 80  | ns    |            |

| 65            | TrdH2dtl | RD↑ or CS↑ to data–out invalid               |                    | 10  | _    | 30  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

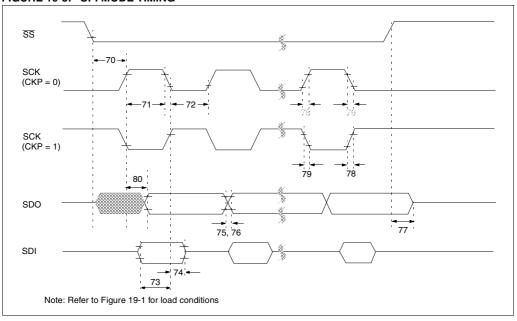

FIGURE 19-8: SPI MODE TIMING

**TABLE 19-8: SPI MODE REQUIREMENTS**

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Typ† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                | _        | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)       | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

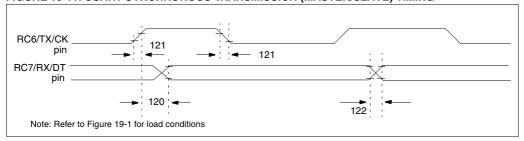

## FIGURE 19-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter No. | Sym                              | Characteristic                    |                    | Min | Тур† | Max | Units | Conditions |

|---------------|----------------------------------|-----------------------------------|--------------------|-----|------|-----|-------|------------|

| 120           | TckH2dtV                         | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 65  |     | _    | 80  | ns    |            |

|               | Clock high to data out valid     | PIC16 <b>LC</b> 65                |                    | _   | 100  | ns  |       |            |

| 121           | 121 Tckrf                        | Clock out rise time and fall time | PIC16 <b>C</b> 65  |     | _    | 45  | ns    |            |

|               |                                  | (Master Mode)                     | PIC16 <b>LC</b> 65 |     | _    | 50  | ns    |            |

| 122           | 122 Tdtrf Data out rise time and |                                   | PIC16 <b>C</b> 65  | -   | _    | 45  | ns    |            |

|               |                                  |                                   | PIC16 <b>LC</b> 65 | _   | _    | 50  | ns    |            |

t: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# FIGURE 19-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### **TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter No. | Sym      | Characteristic                                                    | Min | Typ† | Max | Units | Conditions |

|---------------|----------|-------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125           | TdtV2ckL | SYNC RCV (MASTER & SLAVE)  Data setup before CK ↓ (DT setup time) | 15  | _    | _   | ns    |            |

| 126           | TckL2dtl | Data hold after CK ↓ (DT hold time)                               | 15  | _    | _   | ns    |            |

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

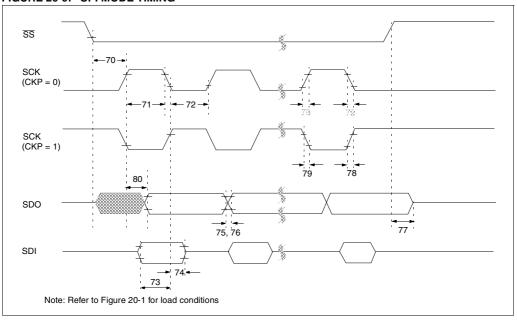

## FIGURE 20-9: SPI MODE TIMING

**TABLE 20-8: SPI MODE REQUIREMENTS**

| Parameter No. | Sym                   | Characteristic                           | Min      | Typ† | Max | Units | Conditions |

|---------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71*           | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72*           | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75*           | TdoR                  | SDO data output rise time                | l        | 10   | 25  | ns    |            |

| 76*           | TdoF                  | SDO data output fall time                | l        | 10   | 25  | ns    |            |

| 77*           | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78*           | TscR                  | SCK output rise time (master mode)       | l        | 10   | 25  | ns    |            |

| 79*           | TscF                  | SCK output fall time (master mode)       |          | 10   | 25  | ns    |            |

| 80*           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 21.0 ELECTRICAL CHARACTERISTICS FOR PIC16CR63/R65

# Absolute Maximum Ratings (†) Ambient temperature under bias .....-55°C to +125°C Storage temperature .....-65°C to +150°C Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)......-...-...-0.3V to (VDD + 0.3V) Voltage on VDD with respect to Vss ......-0.3V to +7.5V Input clamp current. IIK (VI < 0 or VI > VDD)..... Output clamp current, lox (Vo < 0 or Vo > VDD) Maximum output current sunk by any I/O pin.......25 mA Maximum output current sourced by any I/O pin ..... Maximum current sunk by PORTA, PORTB, and PORTE (Note 3) (combined)...... Maximum current sourced by PORTA, PORTB, and PORTE (Note 3) (combined) ...... Maximum current sunk by PORTC and PORTD (Note 3) (combined) ..... Maximum current sourced by PORTC and PORTD (Note 3) (combined)......

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD - ∑ION} + ∑ (VDD-VOH) x IOH} + ∑(VOI x IOL)

Note 2: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

Note 3: PORTD and PORTE not available on the P(C16CR63).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 21-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16CR63-04<br>PIC16CR65-04                                                                                | PIC16CR63-10<br>PIC16CR65-10                                                                | PIC16CR63-20<br>PIC16CR65-20                                                            | PIC16LCR63-04<br>PIC16LCR65-04                                                                          | JW Devices                                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 µA max. at 4V<br>Freq: 4 MHz max)                    | VDD: 4.5V to 5.5V<br>IDD: 2,7 mA typ. at 5.5V<br>IRD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V IDD: 2.7 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max. | VDD: 3.0V to 5.5V<br>IDD: 3.8 mA max. at 3V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                           |

| XT  | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 µA max. at 4V<br>Freq: 4 MHz max.                    | Voo: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V IDD: 2.7 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max. | VDD: 3.0V to 5.5V<br>IDD: 3.8 mA max. at 3V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                           |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at<br>5.5V                                                           | VDD: 4.5V to 5.5V<br>IDD: 10 mA max. at 5.5V                                                | VDD: 4.5V to 5.5V IDD: 20 mA max. at 5.5V                                               | Not recommended for use in HS mode                                                                      | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at<br>5.5V                                                                    |

|     | IPD: $1.5~\mu\text{A}$ typ. at $4.5\text{V}$ Freq: $4~\text{MHz}$ max.                                      | IPD 1.5 μA typ. at 4.5V Freq: 10 MHz max.                                                   | IPD: $1.5 \mu A$ typ. at $4.5 V$ Freq: 20 MHz max.                                      | use in 113 mode                                                                                         | IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.                                                                      |

| LP  | VDD: 4.0V to 5.5V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                          | Not recommended for use in LP mode                                                      | VDD: 3.0V to 5.5V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: $3.0V$ to $5.5V$ IDD: $48~\mu A$ max. at $32~kHz$ , $3.0V$ IPD: $5~\mu A$ max. at $3.0V$ Freq: $200~kHz$ max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

#### 22.2 DC Characteristics: PIC16LC66/67-04 (Commercial, Industrial)

| DC CHA       |                                                                  | <b>Standa</b><br>Operatir | •    | •    |     | °C ≤  | Inless otherwise stated) TA ≤ +85°C for industrial and TA ≤ +70°C for commercial |

|--------------|------------------------------------------------------------------|---------------------------|------|------|-----|-------|----------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                                   | Sym                       | Min  | Тур† | Max | Units | Conditions                                                                       |

| D001         | Supply Voltage                                                   | VDD                       | 2.5  | -    | 6.0 | ٧     | LP, XT, RC osc configuration (DC - 4 MHz)                                        |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                           | VDR                       | -    | 1.5  | -   | V     |                                                                                  |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                      | -    | Vss  | -   | V     | See section on Power-on Reset for details                                        |

| D004*        | VDD rise rate to ensure internal Power-on Reset signal           | SVDD                      | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details                                        |

| D005         | Brown-out Reset Voltage                                          | BVDD                      | 3.7  | 4.0  | 4.3 | V     | BODEN configuration bit is enabled                                               |

| D010         | Supply Current (Note 2, 5)                                       | IDD                       | -    | 2.0  | 3.8 | mA    | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 3.0V (Note 4)                    |

| D010A        |                                                                  |                           | -    | 22.5 | 48  | μА    | LP osc configuration<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                  |

| D015*        | Brown-out Reset Current (Note 6)                                 | $\Delta \text{IBOR}$      | -    | 350  | 425 | μА    | BOR enabled, VDD = 5.0V                                                          |

| D020         | Power-down Current                                               | IPD                       | -    | 7.5  | 30  | μΑ    | VDD = 3.0V, WDT enabled, -40°C to +85°C                                          |

| D021         | (Note 3, 5)                                                      |                           | -    | 0.9  | 5   | μΑ    | VDD = 3.0V, WDT disabled, 0°C to +70°C                                           |

| D021A        |                                                                  |                           | -    | 0.9  | 5   | μΑ    | VDD = 3.0V, WDT disabled, -40°C to +85°C                                         |

| D023*        | Brown-out Reset Current (Note 6)                                 | ΔIBOR                     | -    | 350  | 425 | μА    | BOR enabled, VDD = 5.0V                                                          |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

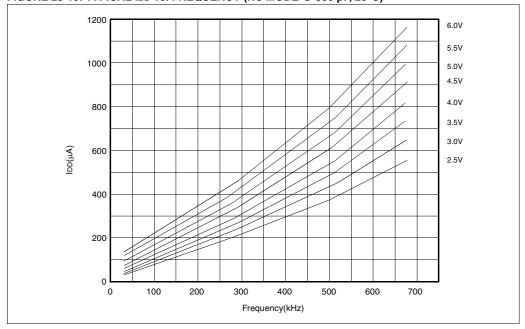

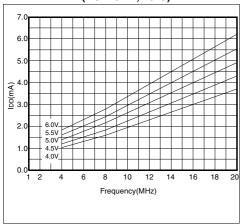

FIGURE 23-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

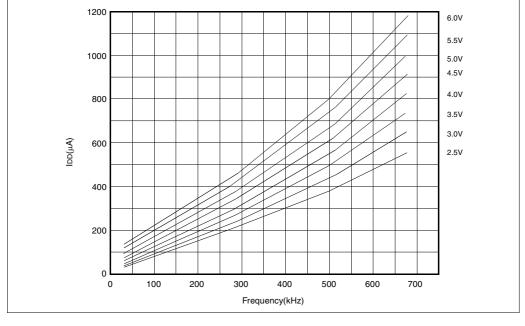

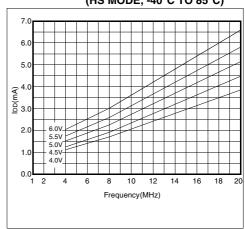

FIGURE 23-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

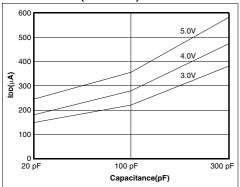

FIGURE 23-18: TYPICAL IDD vs.

CAPACITANCE @ 500 kHz

(RC MODE)

TABLE 23-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |        |  |  |

|--------|------|----------------------------|--------|--|--|

| Cext   | next |                            |        |  |  |

| 22 pF  | 5k   | 4.12 MHz                   | ± 1.4% |  |  |

|        | 10k  | 2.35 MHz                   | ± 1.4% |  |  |

|        | 100k | 268 kHz                    | ± 1.1% |  |  |

| 100 pF | 3.3k | 1.80 MHz                   | ± 1.0% |  |  |

|        | 5k   | 1.27 MHz                   | ± 1.0% |  |  |

|        | 10k  | 688 kHz                    | ± 1.2% |  |  |

|        | 100k | 77.2 kHz                   | ± 1.0% |  |  |

| 300 pF | 3.3k | 707 kHz                    | ± 1.4% |  |  |

|        | 5k   | 501 kHz                    | ± 1.2% |  |  |

|        | 10k  | 269 kHz                    | ± 1.6% |  |  |

|        | 100k | 28.3 kHz                   | ± 1.1% |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

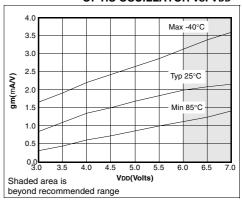

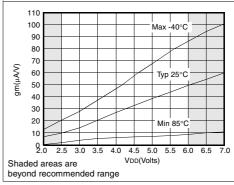

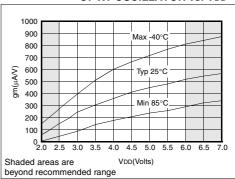

FIGURE 23-19: TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

FIGURE 23-20: TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

FIGURE 23-21: TRANSCONDUCTANCE(gm)

OF XT OSCILLATOR vs. VDD

FIGURE 23-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

# FIGURE 23-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

## 24.7 28-Lead Ceramic CERDIP Dual In-line with Window (300 mil)) (JW)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |       |             |           |        |       |           |

|--------------------------------------------------|-------|-------------|-----------|--------|-------|-----------|

|                                                  |       | Millimeters |           | Inches |       |           |

| Symbol                                           | Min   | Max         | Notes     | Min    | Max   | Notes     |

| α                                                | 0°    | 10°         |           | 0°     | 10°   |           |

| Α                                                | 3.30  | 5.84        |           | .130   | 0.230 |           |

| A1                                               | 0.38  | _           |           | 0.015  | _     |           |

| A2                                               | 2.92  | 4.95        |           | 0.115  | 0.195 |           |

| В                                                | 0.35  | 0.58        |           | 0.014  | 0.023 |           |

| B1                                               | 1.14  | 1.78        | Typical   | 0.045  | 0.070 | Typical   |

| С                                                | 0.20  | 0.38        | Typical   | 0.008  | 0.015 | Typical   |

| D                                                | 34.54 | 37.72       |           | 1.360  | 1.485 |           |

| D2                                               | 32.97 | 33.07       | Reference | 1.298  | 1.302 | Reference |

| E                                                | 7.62  | 8.25        |           | 0.300  | 0.325 |           |

| E1                                               | 6.10  | 7.87        |           | 0.240  | 0.310 |           |

| е                                                | 2.54  | 2.54        | Typical   | 0.100  | 0.100 | Typical   |

| eA                                               | 7.62  | 7.62        | Reference | 0.300  | 0.300 | Reference |

| eB                                               | _     | 11.43       |           |        | 0.450 |           |

| L                                                | 2.92  | 5.08        |           | 0.115  | 0.200 |           |

| N                                                | 28    | 28          |           | 28     | 28    |           |

| D1                                               | 0.13  | _           |           | 0.005  |       |           |

# PIC16C6X

| Figure 11-2:  | SSPCON: Sync Serial Port<br>Control Register (Address 14h)85 | Figure 13-2:  | Configuration Word for PIC16C62/64/65   | 124 |

|---------------|--------------------------------------------------------------|---------------|-----------------------------------------|-----|

| Figure 11-3:  | SSP Block Diagram (SPI Mode) 86                              | Figure 13-3:  | Configuration Word for                  |     |

| Figure 11-4:  | SPI Master/Slave Connection 87                               | •             | PIC16C62A/R62/63/R63/64A/R64/           |     |

| Figure 11-5:  | SPI Mode Timing, Master Mode or                              |               | 65A/R65/66/67                           | 124 |

| 3             | Slave Mode w/o SS Control88                                  | Figure 13-4:  | Crystal/Ceramic Resonator Operation     |     |

| Figure 11-6:  | SPI Mode Timing, Slave Mode with                             |               | (HS, XT or LP OSC Configuration)        | 125 |

| ga            | SS Control                                                   | Figure 13-5:  | External Clock Input Operation          | 0   |

| Figure 11-7:  | SSPSTAT: Sync Serial Port Status                             | rigulo 10 0.  | (HS, XT or LP OSC Configuration)        | 125 |

| rigule 11-7.  | •                                                            | Figure 10 Cr  | External Parallel Resonant              | 123 |

| Fi 44.0       | Register (Address 94h)(PIC16C66/67) 89                       | Figure 13-6:  |                                         | 407 |

| Figure 11-8:  | SSPCON: Sync Serial Port Control                             | F: 40 7       | Crystal Oscillator Circuit              | 127 |

|               | Register (Address 14h)(PIC16C66/67)90                        | Figure 13-7:  | External Series Resonant                |     |

| Figure 11-9:  | SSP Block Diagram (SPI Mode)                                 |               | Crystal Oscillator Circuit              |     |

|               | (PIC16C66/67)91                                              | Figure 13-8:  | RC Oscillator Mode                      | 127 |

| Figure 11-10: | SPI Master/Slave Connection                                  | Figure 13-9:  | Simplified Block Diagram of             |     |

|               | (PIC16C66/67)92                                              |               | On-chip Reset Circuit                   |     |

| Figure 11-11: | SPI Mode Timing, Master Mode                                 | Figure 13-10: | Brown-out Situations                    | 129 |

|               | (PIC16C66/67)93                                              | Figure 13-11: | Time-out Sequence on Power-up           |     |

| Figure 11-12: | SPI Mode Timing (Slave Mode With                             |               | (MCLR not Tied to VDD): Case 1          | 134 |

|               | CKE = 0) (PIC16C66/67)                                       | Figure 13-12: | Time-out Sequence on Power-up           |     |

| Figure 11-13: | SPI Mode Timing (Slave Mode With                             |               | (MCLR Not Tied To VDD): Case 2          | 134 |

|               | CKE = 1) (PIC16C66/67)                                       | Figure 13-13: | Time-out Sequence on Power-up           |     |

| Figure 11-14: | Start and Stop Conditions95                                  | •             | (MCLR Tied to VDD)                      | 134 |

|               | 7-bit Address Format96                                       | Figure 13-14: | External Power-on Reset Circuit         |     |

|               | I <sup>2</sup> C 10-bit Address Format96                     | 3             | (For Slow VDD Power-up)                 | 135 |

|               | Slave-receiver Acknowledge96                                 | Figure 13-15  | External Brown-out                      |     |

|               | Data Transfer Wait State96                                   | rigulo to to. | Protection Circuit 1                    | 135 |

| •             | Master-transmitter Sequence                                  | Figure 13-16: | External Brown-out                      | 100 |

|               | Master-receiver Sequence                                     | rigule 13-10. | Protection Circuit 2                    | 125 |

|               | Combined Format                                              | Eiguro 12 17: |                                         |     |

|               |                                                              |               | Interrupt Logic for PIC16C61            |     |

| rigure 11-22. | Multi-master Arbitration                                     |               | Interrupt Logic for PIC16C6X            |     |

| F' 11 00      | (Two Masters)                                                |               | INT Pin Interrupt Timing                |     |

|               | Clock Synchronization                                        |               | Watchdog Timer Block Diagram            | 140 |

|               | SSP Block Diagram (I <sup>2</sup> C Mode)99                  | Figure 13-21: | Summary of Watchdog                     |     |

| Figure 11-25: | I <sup>2</sup> C Waveforms for Reception                     |               | Timer Registers                         | 140 |

|               | (7-bit Address)101                                           | Figure 13-22: | Wake-up from Sleep                      |     |

| Figure 11-26: | I <sup>2</sup> C Waveforms for Transmission                  |               | Through Interrupt                       | 142 |

|               | (7-bit Address) 102                                          | Figure 13-23: | Typical In-circuit Serial               |     |

| Figure 11-27: | Operation of the I <sup>2</sup> C Module in                  |               | Programming Connection                  | 142 |

|               | IDLE_MODE, RCV_MODE or                                       | Figure 14-1:  | General Format for Instructions         | 143 |

|               | XMIT_MODE 104                                                | Figure 16-1:  | Load Conditions for Device Timing       |     |

| Figure 12-1:  | TXSTA: Transmit Status and                                   |               | Specifications                          | 168 |

|               | Control Register (Address 98h) 105                           | Figure 16-2:  | External Clock Timing                   | 169 |

| Figure 12-2:  | RCSTA: Receive Status and                                    | Figure 16-3:  | CLKOUT and I/O Timing                   | 170 |

| •             | Control Register (Address 18h) 106                           | Figure 16-4:  | Reset, Watchdog Timer, Oscillator       |     |

| Figure 12-3:  | RX Pin Sampling Scheme (BRGH = 0)                            | Ü             | Start-up Timer and Power-up Timer       |     |

| Ü             | PIC16C63/R63/65/65A/R65)110                                  |               | Timing                                  | 171 |

| Figure 12-4:  | RX Pin Sampling Scheme (BRGH = 1)                            | Figure 16-5:  | Timer0 External Clock Timings           |     |

| 9             | (PIC16C63/R63/65/65A/R65)110                                 | Figure 17-1:  | Typical RC Oscillator                   |     |

| Figure 12-5:  | RX Pin Sampling Scheme (BRGH = 1)                            | rigulo 17 1.  | Frequency vs. Temperature               | 173 |

| rigaro 12 o.  | (PIC16C63/R63/65/65A/R65)110                                 | Figure 17-2:  | Typical RC Oscillator                   |     |

| Eiguro 10 6:  | ,                                                            | rigule 17-2.  | Frequency vs. VDD                       | 17/ |

| Figure 12-6:  | RX Pin Sampling Scheme (BRGH = 0 or = 1)                     | Fig 17.0.     |                                         | 1/4 |

| Figure 12-7:  | (PIC16C66/67)                                                | Figure 17-3:  | Typical RC Oscillator Frequency vs. VDD | 17/ |

|               | USART Transmit Block Diagram                                 | Fig 47 4.     | Typical RC Oscillator                   | 1/4 |

| Figure 12-8:  | Asynchronous Master Transmission 113                         | Figure 17-4:  | Typical RC Oscillator                   | 474 |

| Figure 12-9:  | Asynchronous Master Transmission                             |               | Frequency vs. VDD                       | 1/4 |

|               | (Back to Back)                                               | Figure 17-5:  | Typical IPD vs. VDD Watchdog Timer      |     |

| •             | USART Receive Block Diagram 114                              |               | Disabled 25°C                           | 174 |

|               | Asynchronous Reception114                                    | Figure 17-6:  | Typical IPD vs. VDD Watchdog Timer      |     |

|               | Synchronous Transmission117                                  |               | Enabled 25°C                            | 175 |

| Figure 12-13: | Synchronous Transmission                                     | Figure 17-7:  | Maximum IPD vs. VDD Watchdog            |     |

|               | through TXEN117                                              |               | Disabled                                | 175 |

| Figure 12-14: | Synchronous Reception                                        | Figure 17-8:  | Maximum IPD vs. VDD Watchdog            |     |

|               | (Master Mode, SREN)119                                       |               | Enabled*                                | 176 |

| Figure 13-1:  | Configuration Word for PIC16C61123                           | Figure 17-9:  | VTH (Input Threshold Voltage) of        |     |

| -             |                                                              | -             | I/O Pins vs. VDD                        | 176 |

|               |                                                              |               |                                         |     |