Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

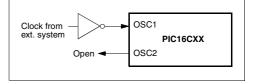

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64a-04i-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16CXX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C61** device has 36 bytes of RAM and 13 I/O pins. In addition a timer/counter is available.

The **PIC16C62/62A/R62** devices have 128 bytes of RAM and 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI<sup>TM</sup>) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus.

The **PIC16C63/R63** devices have 192 bytes of RAM, while the **PIC16C66** has 368 bytes. All three devices have 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit ( $I^2C$ ) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also know as a Serial Communications Interface or SCI.

The **PIC16C64/64A/R64** devices have 128 bytes of RAM and 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. An 8-bit Parallel Slave Port is also provided.

The **PIC16C65/65A/R65** devices have 192 bytes of RAM, while the **PIC16C67** has 368 bytes. All four devices have 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmit-

ter (USART) is also known as a Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is also provided.

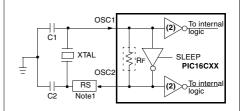

The PIC16C6X device family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers a power saving mode. The user can wake the chip from SLEEP through several external and internal interrupts, and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C6X family fits perfectly in applications ranging from high-speed automotive and appliance control to low-power remote sensors, keyboards and telecom processors. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use, and I/O flexibility make the PIC16C6X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions, and co-processor applications).

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16CXX family of devices (Appendix B).

### 1.2 Development Support

PIC16C6X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 15.0 for more details about Microchip's development tools.

## TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

NOTES:

-

### 3.1 Clocking Scheme/Instruction Cycle

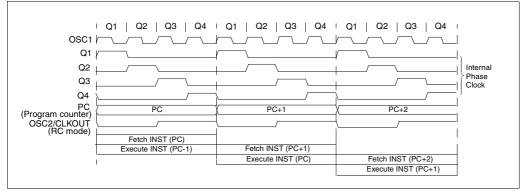

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

### 3.2 Instruction Flow/Pipelining

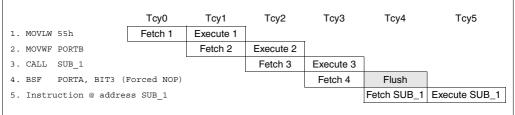

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### 4.2.2 SPECIAL FUNCTION REGISTERS:

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). The registers associated with the "core" functions are described in this section and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| TABLE 4-1: | SPECIAL FUNCTION REGISTERS FOR THE PIC16C61 |

|------------|---------------------------------------------|

| TADLE 4-1. | SPECIAL FUNCTION REGISTERS FOR THE PICTOCOT |

| Address              | Name   | Bit 7              | Bit 6                                                                                          | Bit 5         | Bit 4        | Bit 3         | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|--------|--------------------|------------------------------------------------------------------------------------------------|---------------|--------------|---------------|------------------|---------------|-----------|------------------|------------------------------------------------|

| Bank 0               |        |                    |                                                                                                |               |              |               |                  |               |           |                  |                                                |

| 00h <sup>(1)</sup>   | INDF   | Addressing         | Addressing this location uses contents of FSR to address data memory (not a physical register) |               |              |               |                  |               |           |                  | 0000 0000                                      |

| 01h                  | TMR0   | Timer0 mod         | lule's registe                                                                                 | r             |              |               |                  |               |           | XXXX XXXX        | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)                                                                                  | Least Signif  | icant Byte   |               |                  |               |           | 0000 0000        | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                             | RP0           | TO           | PD            | Z                | DC            | С         | 0001 1xxx        | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ad                                                                                    | dress pointe  | er           |               |                  |               |           | xxxx xxxx        | uuuu uuuu                                      |

| 05h                  | PORTA  | _                  | —                                                                                              | —             | PORTA Dat    | a Latch whe   | n written: PC    | RTA pins wh   | en read   | x xxxx           | u uuuu                                         |

| 06h                  | PORTB  | PORTB Dat          | ta Latch whe                                                                                   | n written: PC | ORTB pins wi | nen read      |                  |               |           | xxxx xxxx        | uuuu uuuu                                      |

| 07h                  | -      | Unimpleme          | nted                                                                                           |               |              |               |                  |               |           | —                | —                                              |

| 08h                  | -      | Unimpleme          | nted                                                                                           |               |              |               |                  |               |           | —                | —                                              |

| 09h                  | -      | Unimplemented      |                                                                                                |               |              |               |                  | _             | _         |                  |                                                |

| 0Ah <sup>(1,2)</sup> | PCLATH | _                  | _                                                                                              | —             | Write Buffer | for the uppe  | er 5 bits of th  | e Program C   | ounter    | 0 0000           | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON | GIE                | _                                                                                              | TOIE          | INTE         | RBIE          | TOIF             | INTF          | RBIF      | 0-00 000x        | 0-00 000u                                      |

| Bank 1               |        |                    |                                                                                                |               |              |               |                  |               |           |                  |                                                |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location                                                                                  | uses conter   | ts of FSR to | address data  | a memory (n      | ot a physical | register) | 0000 0000        | 0000 0000                                      |

| 81h                  | OPTION | RBPU               | INTEDG                                                                                         | TOCS          | TOSE         | PSA           | PS2              | PS1           | PS0       | 1111 1111        | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)                                                                                  | Least Signif  | icant Byte   |               |                  |               |           | 0000 0000        | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                             | RP0           | TO           | PD            | z                | DC            | с         | 0001 1xxx        | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ad                                                                                    | dress pointe  | er           |               |                  |               |           | xxxx xxxx        | uuuu uuuu                                      |

| 85h                  | TRISA  | _                  | —                                                                                              | —             | PORTA Dat    | a Direction F | Register         |               |           | 1 1111           | 1 1111                                         |

| 86h                  | TRISB  | PORTB Dat          | ta Direction C                                                                                 | Control Regis | ster         |               |                  |               |           | 1111 1111        | 1111 1111                                      |

| 87h                  | -      | Unimplemented      |                                                                                                |               |              |               |                  | _             | —         |                  |                                                |

| 88h                  | -      | Unimplemented      |                                                                                                |               |              |               |                  | _             | _         |                  |                                                |

| 89h                  | -      | Unimpleme          | nted                                                                                           |               |              |               |                  |               |           | _                | —                                              |

| 8Ah <sup>(1,2)</sup> | PCLATH | _                  | —                                                                                              | —             | Write Buffer | for the uppe  | er 5 bits of the | e Program C   | ounter    | 0 0000           | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON | GIE                | _                                                                                              | TOIE          | INTE         | RBIE          | TOIF             | INTF          | RBIF      | 0-00 000x        | 0-00 000u                                      |

|                      | 1      | 1                  |                                                                                                | l             | 1            |               | 1                |               |           | 1                | l                                              |

$\label{eq:logend: condition for the set of the set of$

Shaded locations are unimplemented and read as '0'

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C61, always maintain these bits clear.

| Address              | Name    | Bit 7              | Bit 6                                                                                         | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|-----------------------------------------------------------------------------------------------|----------------|----------------|--------------|-----------------|-------------|---------|--------------------------|------------------------------------------------|

| Bank 0               | 1       | 1                  | 1                                                                                             | 1              |                | 1            | 1               | 1           | 1       | 1                        | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | ddressing this location uses contents of FSR to address data memory (not a physical register) |                |                |              |                 |             |         |                          | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | dule's registe                                                                                | r              |                |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                                                                                 | Least Signif   | icant Byte     |              |                 |             |         | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                            | RP0            | TO             | PD           | Z               | DC          | С       | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac                                                                                   | Idress pointe  | er             |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | —                  | —                                                                                             | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh     | en read     |         | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe                                                                                  | n written: PC  | ORTB pins wh   | nen read     |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe                                                                                  | n written: PC  | ORTC pins wi   | nen read     |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | _       | Unimpleme          | nted                                                                                          |                |                |              |                 |             |         | —                        | _                                              |

| 09h                  | —       | Unimpleme          | nted                                                                                          |                |                |              |                 |             |         | —                        | —                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                                                                                             | _              | Write Buffer   | for the uppe | r 5 bits of the | e Program C | ounter  | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                                                                          | TOIE           | INTE           | RBIE         | TOIF            | INTF        | RBIF    | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | (5)                | (5)                                                                                           | RCIF           | TXIF           | SSPIF        | CCP1IF          | TMR2IF      | TMR1IF  | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | _                  | _                                                                                             | —              | _              | _            | _               | _           | CCP2IF  | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the I                                                                               | _east Signific | ant Byte of t  | ne 16-bit TM | R1 register     |             | 1       | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the I                                                                               | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register     |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                  | —                                                                                             | T1CKPS1        | T1CKPS0        | T1OSCEN      | T1SYNC          | TMR1CS      | TMR10N  | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | dule's registe                                                                                | r              |                |              |                 |             |         | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                  | TOUTPS3                                                                                       | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | us Serial Por                                                                                 | t Receive Bu   | ffer/Transmit  | Register     |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV                                                                                         | SSPEN          | CKP            | SSPM3        | SSPM2           | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM                                                                                     | 1 (LSB)        |                |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM                                                                                     | 1 (MSB)        |                |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                  | _                                                                                             | CCP1X          | CCP1Y          | CCP1M3       | CCP1M2          | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                                                                                           | SREN           | CREN           | —            | FERR            | OERR        | RX9D    | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra          | nsmit Data F                                                                                  | legister       |                |              |                 |             |         | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re           | ceive Data R                                                                                  | egister        |                |              |                 |             |         | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM                                                                                     | 2 (LSB)        |                |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM                                                                                     | 2 (MSB)        |                |              |                 |             |         | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                                                                                             | CCP2X          | CCP2Y          | CCP2M3       | CCP2M2          | CCP2M1      | CCP2M0  | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted                                                                                          |                |                |              |                 |             |         | _                        | _                                              |

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

5: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C63/R63, always maintain these bits clear.

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the individual enable bits for the peripheral interrupts.

Bit PEIE (INTCON<6>) must be set to Note: enable any peripheral interrupt.

# FIGURE 4-12: PIE1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 8Ch)

| RW-0     | R/W-0                                                                                                                                                  | U-0        | U-0         | R/W-0         | R/W-0  | R/W-0  | R/W-0  |                                                                                                                      |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------|--|--|

| _        | —                                                                                                                                                      |            | _           | SSPIE         | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                                                     |  |  |

| bit7     |                                                                                                                                                        |            |             |               |        |        | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |

| bit 7-6: | Reserved:                                                                                                                                              | Always ma  | intain thes | e bits clear. |        |        |        |                                                                                                                      |  |  |

| bit 5-4: | Unimplem                                                                                                                                               | ented: Rea | ıd as '0'   |               |        |        |        |                                                                                                                      |  |  |

| bit 3:   | <ul> <li>SSPIE: Synchronous Serial Port Interrupt Enable bit</li> <li>1 = Enables the SSP interrupt</li> <li>0 = Disables the SSP interrupt</li> </ul> |            |             |               |        |        |        |                                                                                                                      |  |  |

| bit 2:   | <b>CCP1IE</b> : C<br>1 = Enables<br>0 = Disable                                                                                                        | s the CCP1 | interrupt   | bit           |        |        |        |                                                                                                                      |  |  |

| bit 1:   | <b>TMR2IE</b> : TI<br>1 = Enables<br>0 = Disable                                                                                                       | s the TMR2 | to PR2 ma   | atch interru  | ot     |        |        |                                                                                                                      |  |  |

| bit 0:   | TMR1IE: TI<br>1 = Enables<br>0 = Disable                                                                                                               | s the TMR1 | overflow i  | nterrupt      | t      |        |        |                                                                                                                      |  |  |

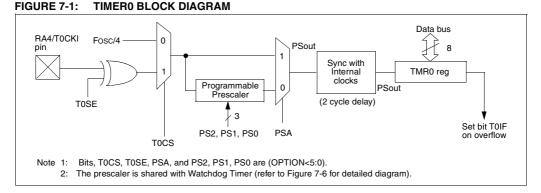

#### 7.0 TIMER0 MODULE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

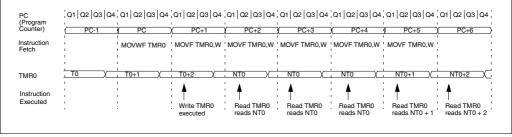

Timer mode is selected by clearing bit T0CS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 TMR0 Interrupt

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the TImer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

© 1997-2013 Microchip Technology Inc.

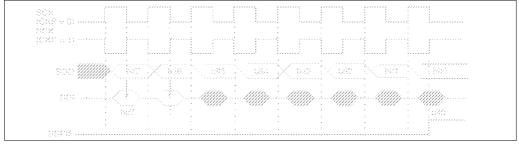

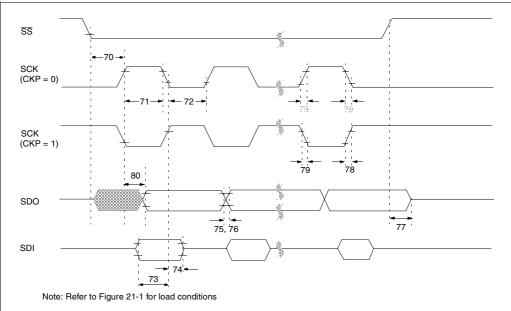

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

| TABLE 11-1: REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Name    | Bit 7                                                        | Bit 6                                                                                                                               | Bit 5                                                                                                                                                                                                                                | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                        | Value on:<br>POR,<br>BOR                                                                                                                                                                                                                                                                                                                                                                                            | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCON  | GIE                                                          | PEIE                                                                                                                                | TOIE                                                                                                                                                                                                                                 | INTE                                                                                                                                                                                                                                                                                                                                                                                                                                           | RBIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RBIF                                                                                                                                                                                                                                                                                                                                                                                                         | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIR1    | PSPIF <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIF <sup>(1)</sup>                                                                                                                                                                                                                  | TXIF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                            | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIE1    | PSPIE <sup>(2)</sup>                                         | (3)                                                                                                                                 | RCIE <sup>(1)</sup>                                                                                                                                                                                                                  | TXIE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                            | SSPIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CCP1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR1IE                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPBUF  | Synchrono                                                    | ous Serial                                                                                                                          | Port Rece                                                                                                                                                                                                                            | ive Buffer/                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                           | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SSPCON  | WCOL                                                         | SSPOV                                                                                                                               | SSPEN                                                                                                                                                                                                                                | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                            | SSPM3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPM0                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |