Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64at-04-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Г

# FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| _        | _                                                | RCIF                                                                                  | TXIF                                   | SSPIF         | CCP1IF                               | TMB2IF        | TMR1IF  | B = Beadable                                                | hit                      |

|----------|--------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|---------------|--------------------------------------|---------------|---------|-------------------------------------------------------------|--------------------------|

| bit7     |                                                  | 1101                                                                                  |                                        |               |                                      |               | bit0    | W = Writable<br>U = Unimpler<br>read as '<br>- n = Value at | bit<br>nented bit,<br>0' |

| bit 7-6: | Reserved:                                        | Always ma                                                                             | intain thes                            | e bits clear. |                                      |               |         |                                                             |                          |

| bit 5:   | <b>RCIF:</b> USA<br>1 = The US<br>0 = The US     | ART receiv                                                                            | e buffer is                            | full (cleared | I by reading                         | RCREG)        |         |                                                             |                          |

| bit 4:   | <b>TXIF:</b> USA<br>1 = The US<br>0 = The US     | ART transr                                                                            | nit buffer is                          | empty (cle    | ared by writi                        | ng to TXRE    | G)      |                                                             |                          |

| bit 3:   | <b>SSPIF</b> : Syr<br>1 = The tra<br>0 = Waiting | nsmission/ı                                                                           | eception is                            |               | ag bit<br>must be clea               | ared in softw | vare)   |                                                             |                          |

| bit 2:   | 0 = No TMI<br>Compare M                          | ode<br>1 register c<br>R1 register<br><u>Mode</u><br>1 register c<br>R1 register<br>2 | apture occi<br>capture oc<br>ompare ma | curred        | be cleared i<br>ed (must be c<br>red | ,             | ftware) |                                                             |                          |

| bit 1:   | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TM     | o PR2 mat                                                                             | ch occurred                            | d (must be o  | bit<br>cleared in so                 | ftware)       |         |                                                             |                          |

| bit 0:   | <b>TMR1IF</b> : T<br>1 = TMR1 1<br>0 = No TMI    | register ove                                                                          | rflow occur                            | red (must b   | e cleared in                         | software)     |         |                                                             |                          |

| globa    | 0 = No TMI                                       | R1 register                                                                           | overflow or                            | curred        | n occurs rega                        | ardless of th |         | corresponding e<br>rupt flag bits are                       |                          |

г

# FIGURE 4-19: PIR1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 0Ch)

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                | R-0                                                                                         | R-0           | R/W-0         | R/W-0                   | R/W-0         | R/W-0          |                                                                                                                                                |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------|---------------|-------------------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PSPIF<br>bit7 | —                                                                                                                                                                                                                                                                                                                                                                                                    | RCIF                                                                                        | TXIF          | SSPIF         | CCP1IF                  | TMR2IF        | TMR1IF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |  |  |  |

| bit 7:        |                                                                                                                                                                                                                                                                                                                                                                                                      | or a write o                                                                                | peration ha   | as taken pla  | ace (must be<br>ce      | cleared in s  | oftware)       |                                                                                                                                                |  |  |  |  |  |

| bit 6:        | Reserved:                                                                                                                                                                                                                                                                                                                                                                                            | 0 = No read or write operation has taken place<br>Reserved: Always maintain this bit clear. |               |               |                         |               |                |                                                                                                                                                |  |  |  |  |  |

| bit 5:        | <b>RCIF:</b> USA<br>1 = The US<br>0 = The US                                                                                                                                                                                                                                                                                                                                                         | SART receiv                                                                                 | /e buffer is  | full (cleared | d by reading            | RCREG)        |                |                                                                                                                                                |  |  |  |  |  |

| bit 4:        | <b>TXIF:</b> USA<br>1 = The US<br>0 = The US                                                                                                                                                                                                                                                                                                                                                         | SART trans                                                                                  | nit buffer is | empty (cle    | eared by writ           | ing to TXRE   | EG)            |                                                                                                                                                |  |  |  |  |  |

| bit 3:        |                                                                                                                                                                                                                                                                                                                                                                                                      | nsmission/                                                                                  | reception is  |               | ag bit<br>(must be clea | ared in softw | vare)          |                                                                                                                                                |  |  |  |  |  |

| bit 2:        | 0 = Waiting to transmit/receive<br>CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture Mode</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode</u><br>Unused in this mode |                                                                                             |               |               |                         |               |                |                                                                                                                                                |  |  |  |  |  |

| bit 1:        | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TMI                                                                                                                                                                                                                                                                                                                                                        | to PR2 mat                                                                                  | ch occurred   | d (must be    | bit<br>cleared in so    | ftware)       |                |                                                                                                                                                |  |  |  |  |  |

| bit 0:        | <b>TMR1IF</b> : T<br>1 = TMR1 1<br>0 = No TMI                                                                                                                                                                                                                                                                                                                                                        | register ove                                                                                | rflow occur   | red (must b   | be cleared in           | software)     |                |                                                                                                                                                |  |  |  |  |  |

| global        |                                                                                                                                                                                                                                                                                                                                                                                                      | GIE (INTC                                                                                   |               |               |                         |               |                | corresponding enable bit or the<br>rupt flag bits are clear prior to                                                                           |  |  |  |  |  |

# TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                       |

|------------|------|-------------|--------------------------------------------------------------------------------|

| RA0        | bit0 | TTL         | Input/output                                                                   |

| RA1        | bit1 | TTL         | Input/output                                                                   |

| RA2        | bit2 | TTL         | Input/output                                                                   |

| RA3        | bit3 | TTL         | Input/output                                                                   |

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0.<br>Output is open drain type. |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

# TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5                                        | Bit 4                                  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|----------------------------------------------|----------------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | —     | —     | RA5 <sup>(1)</sup>                           | RA5 <sup>(1)</sup> RA4 RA3 RA2 RA1 RA0 |       |       |       |       |                          | uu uuuu                   |

| 85h     | TRISA | —     | —     | PORTA Data Direction Register <sup>(1)</sup> |                                        |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

# 5.3 PORTC and TRISC Register

### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTC is an 8-bit wide bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

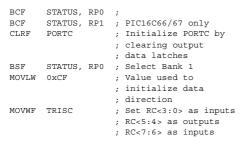

### EXAMPLE 5-3: INITIALIZING PORTC

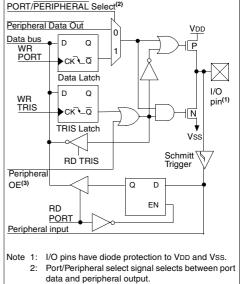

# FIGURE 5-6: PORTC BLOCK DIAGRAM

3: Peripheral OE (output enable) is only activated if peripheral select is active.

# TABLE 5-5: PORTC FUNCTIONS FOR PIC16C62/64

| Name            | Bit# | Buffer Type | Function                                                                    |

|-----------------|------|-------------|-----------------------------------------------------------------------------|

| RC0/T1OSI/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator input or Timer1 clock input      |

| RC1/T1OSO       | bit1 | ST          | Input/output port pin or Timer1 oscillator output                           |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).      |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                |

| RC6             | bit6 | ST          | Input/output port pin                                                       |

| RC7             | bit7 | ST          | Input/output port pin                                                       |

Legend: ST = Schmitt Trigger input

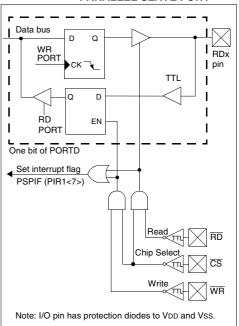

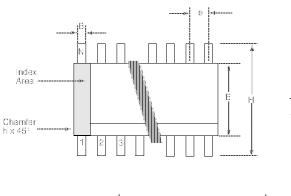

# 5.7 Parallel Slave Port

#### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD operates as an 8-bit wide parallel slave port (microprocessor port) when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input (RE0/ $\overline{\text{RD}}$ ) and  $\overline{\text{WR}}$  control input pin (RE1/ $\overline{\text{WR}}$ ).

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$  lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

### FIGURE 5-11: PORTD AND PORTE AS A PARALLEL SLAVE PORT

### 11.4.4 MULTI-MASTER

PIC16C6X

The  $I^2C$  protocol allows a system to have more than one master. This is called multi-master. When two or more masters try to transfer data at the same time, arbitration and synchronization occur.

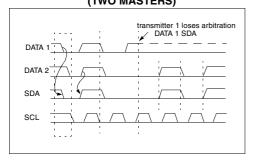

### 11.4.4.1 ARBITRATION

Arbitration takes place on the SDA line, while the SCL line is high. The master which transmits a high when the other master transmits a low loses arbitration (Figure 11-22), and turns off its data output stage. A master which lost arbitration can generate clock pulses until the end of the data byte where it lost arbitration. When the master devices are addressing the same device, arbitration continues into the data.

### FIGURE 11-22: MULTI-MASTER ARBITRATION (TWO MASTERS)

Masters that also incorporate the slave function, and have lost arbitration must immediately switch over to slave-receiver mode. This is because the winning master-transmitter may be addressing it.

Arbitration is not allowed between:

- A repeated START condition

- · A STOP condition and a data bit

- A repeated START condition and a STOP condition

Care needs to be taken to ensure that these conditions do not occur.

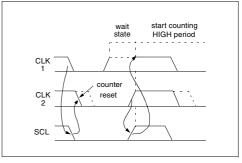

#### 11.2.4.2 Clock Synchronization

Clock synchronization occurs after the devices have started arbitration. This is performed using a wired-AND connection to the SCL line. A high to low transition on the SCL line causes the concerned devices to start counting off their low period. Once a device clock has gone low, it will hold the SCL line low until its SCL high state is reached. The low to high transition of this clock may not change the state of the SCL line, if another device clock is still within its low period. The SCL line is held low by the device with the longest low period. Devices with shorter low periods enter a high waitstate, until the SCL line comes high. When the SCL line comes high, all devices start counting off their high periods. The first device to complete its high period will pull the SCL line low. The SCL line high time is determined by the device with the shortest high period, Figure 11-23.

### FIGURE 11-23: CLOCK SYNCHRONIZATION

### 11.5.1 SLAVE MODE

PIC16C6X

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 11-4 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

#### 11.5.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The

address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 11-16). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT-2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### TABLE 11-4: DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>s Received |                    |                       | Set bit SSPIF                        |  |

|----|--------------------------|--------------------|-----------------------|--------------------------------------|--|

| BF | SSPOV                    | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |

| 0  | 0                        | Yes                | Yes                   | Yes                                  |  |

| 1  | 0                        | No                 | No                    | Yes                                  |  |

| 1  | 1                        | No                 | No                    | Yes                                  |  |

| 0  | 1                        | No                 | No                    | Yes                                  |  |

| Q2                                  | Q3Q4        | Q1 Q2 Q3 Q | 4Q1Q2       | Q3Q4Q1Q2         | 03040102    | 03040102    | 03040102    | 03 04 01 02 0         | 30401020         | 30401020         | 30401020304 |

|-------------------------------------|-------------|------------|-------------|------------------|-------------|-------------|-------------|-----------------------|------------------|------------------|-------------|

| C7/RX/DT pin                        | 1           |            | bit0        | bit1             | bit2        | bit3        | bit4        | , bit5                | bit6             | bit7             | 1           |

| C6/TX/CK pin –                      | 1<br>1<br>1 | Γ          |             |                  |             |             |             |                       |                  | <u> </u>         | 1           |

| Write to<br>bit SREN                |             |            | 1<br>1<br>1 | 1<br>1<br>1<br>1 |             |             |             | ,<br>,<br>,<br>,<br>, | 1<br>1<br>1<br>1 |                  |             |

| SREN bit -                          |             |            | 1           | 1<br>1<br>1      |             |             | 1           | 1                     | 1                |                  | 1           |

| CREN bit                            | '0'         |            | t<br>t      | 1<br>1<br>1      | 1           | 1           | 1           | 1                     | 1<br>1           | 1                | '0'         |

| RCIF bit<br>(interrupt) <sup></sup> |             |            | t<br>t<br>t | 1<br>1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1<br>1      | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 |             |

| Read<br>RXREG -                     | 1<br>1<br>1 |            | 1<br>1<br>1 | 1<br>1<br>1      | 1<br>1<br>1 | 1           | 1<br>1<br>1 | 1<br>1<br>1           | 1<br>1<br>1      | 1<br>1<br>1      |             |

# FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

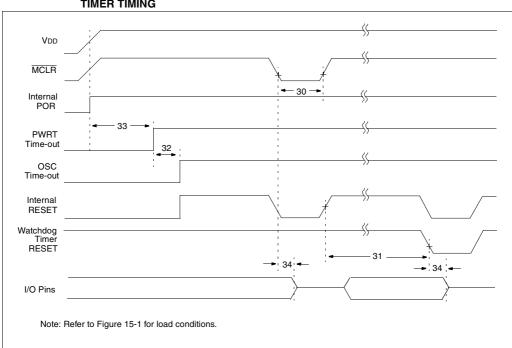

# FIGURE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                           | 200 | —        | —   | ns    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                |     | 1024Tosc | —   |       | TOSC = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low                   |     | —        | 100 | ns    |                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# 17.1 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial) PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial)

| DC CHAR               |                                                                   | Standard Operating Conditions (unless otherwise stated)           Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ $+85^{\circ}$ C for industrial and           0°C $\leq$ TA $\leq$ $+70^{\circ}$ C for commercial |             |                    |                |                |                                                                                                                                                                                                                                                                       |  |  |

|-----------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          | Characteristic                                                    | Sym                                                                                                                                                                                                                       | Min         | Тур†               | Max            | Units          | Conditions                                                                                                                                                                                                                                                            |  |  |

| D001<br>D001A         | Supply Voltage                                                    | Vdd                                                                                                                                                                                                                       | 4.0<br>4.5  | -                  | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                               |  |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                                                                                                                                                                                                                       | -           | 1.5                | -              | V              |                                                                                                                                                                                                                                                                       |  |  |

| D003                  | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                                                                                                                                                                                                                      | -           | Vss                | -              | V              | See section on Power-on Reset for details                                                                                                                                                                                                                             |  |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on<br>Reset signal      | SVDD                                                                                                                                                                                                                      | 0.05        | -                  | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                                                                                             |  |  |

| D010                  | Supply Current<br>(Note 2, 5)                                     | IDD                                                                                                                                                                                                                       | -           | 2.7                | 5.0            | mA             | XT, RC, osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                        |  |  |

| D013                  |                                                                   |                                                                                                                                                                                                                           | -           | 13.5               | 30             | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                     |  |  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3, 5)                                 | IPD                                                                                                                                                                                                                       | -<br>-<br>- | 10.5<br>1.5<br>1.5 | 42<br>21<br>24 | μΑ<br>μΑ<br>μΑ | $ \begin{array}{l} V\text{DD}=4.0V, WDT \mbox{ enabled}, -40^\circ C \mbox{ to } +85^\circ C \\ V\text{DD}=4.0V, WDT \mbox{ disabled}, -0^\circ C \mbox{ to } +70^\circ C \\ V\text{DD}=4.0V, WDT \mbox{ disabled}, -40^\circ C \mbox{ to } +85^\circ C \end{array} $ |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSs.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

| DC CHA       | RACTERISTICS                                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercialOperating voltage VDD range as described in DC spec Section 17.1and Section 17.2 |     |          |           |          |                                                                         |  |  |

|--------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------|----------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Characteristic                                                          | Sym                                                                                                                                                                                                                                                                        | Min | Тур<br>† | Max       | Units    | Conditions                                                              |  |  |

| D100         | Capacitive Loading Specs on Output<br>Pins<br>OSC2 pin                  | Cosc2                                                                                                                                                                                                                                                                      | -   | -        | 15        |          | In XT, HS and LP modes<br>when external clock is used to<br>drive OSC1. |  |  |

| D101<br>D102 | All I/O pins and OSC2 (in RC mode)<br>SCL, SDA in I <sup>2</sup> C mode | Cio<br>Cb                                                                                                                                                                                                                                                                  | -   | -        | 50<br>400 | pF<br>pF |                                                                         |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

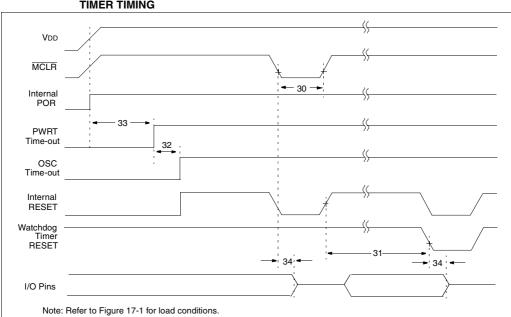

# FIGURE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                           | 100 | —        | —   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | -   | 1024Tosc | _   | -     | TOSC = OSC1 period       |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low                   | -   | —        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 20.2 DC Characteristics: PIC16LC63/65A-04 (Commercial, Industrial)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq Ta \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq Ta \leq +70^{\circ}$ C for commercial |                                                                  |               |      |      |     |       |                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|------|------|-----|-------|-----------------------------------------------------------------|--|

| Param<br>No.                                                                                                                                                                                                             | Characteristic                                                   | Sym           | Min  | Тур† | Max | Units | Conditions                                                      |  |

| D001                                                                                                                                                                                                                     | Supply Voltage                                                   | Vdd           | 2.5  | -    | 6.0 | V     | LP, XT, RC osc configuration (DC - 4 MHz)                       |  |

| D002*                                                                                                                                                                                                                    | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -    | 1.5  | -   | V     |                                                                 |  |

| D003                                                                                                                                                                                                                     | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -    | Vss  | -   | V     | See section on Power-on Reset for details                       |  |

| D004*                                                                                                                                                                                                                    | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD          | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details                       |  |

| D005                                                                                                                                                                                                                     | Brown-out Reset Voltage                                          | BVDD          | 3.7  | 4.0  | 4.3 | V     | BODEN configuration bit is enabled                              |  |

| D010                                                                                                                                                                                                                     | Supply Current (Note 2, 5)                                       | IDD           | -    | 2.0  | 3.8 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)   |  |

| D010A                                                                                                                                                                                                                    |                                                                  |               | -    | 22.5 | 48  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |  |

| D015*                                                                                                                                                                                                                    | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -    | 350  | 425 | μA    | BOR enabled, VDD = 5.0V                                         |  |

| D020                                                                                                                                                                                                                     | Power-down Current                                               | IPD           | -    | 7.5  | 30  | μA    | VDD = 3.0V, WDT enabled, -40°C to +85°C                         |  |

| D021                                                                                                                                                                                                                     | (Note 3, 5)                                                      |               | -    | 0.9  | 5   | μA    | VDD = 3.0V, WDT disabled, 0°C to +70°C                          |  |

| D021A                                                                                                                                                                                                                    |                                                                  |               | -    | 0.9  | 5   | μA    | VDD = 3.0V, WDT disabled, -40°C to +85°C                        |  |

| D023*                                                                                                                                                                                                                    | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -    | 350  | 425 | μA    | BOR enabled, VDD = 5.0V                                         |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# PIC16C6X

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

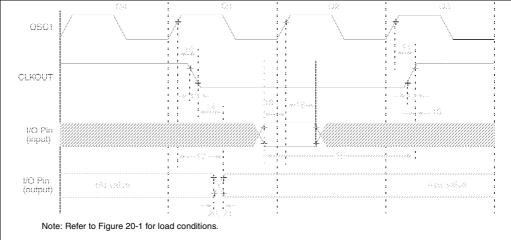

# FIGURE 20-3: CLKOUT AND I/O TIMING

| TABLE 20-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

| Parameter<br>No. | Sym      | Characteristic                                |                       | Min | Тур† | Max         | Units  | Conditions |

|------------------|----------|-----------------------------------------------|-----------------------|-----|------|-------------|--------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                              | _                     | 75  | 200  | ns          | Note 1 |            |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                              |                       | —   | 75   | 200         | ns     | Note 1     |

| 12*              | TckR     | CLKOUT rise time                              |                       | _   | 35   | 100         | ns     | Note 1     |

| 13*              | TckF     | CLKOUT fall time                              |                       | _   | 35   | 100         | ns     | Note 1     |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid         |                       | _   | _    | 0.5TCY + 20 | ns     | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOUT ↑                 | Tosc + 200            | _   | -    | ns          | Note 1 |            |

| 16*              | TckH2iol | Port in hold after CLKOUT $\uparrow$          | 0                     | _   | _    | ns          | Note 1 |            |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out val  | _                     | 50  | 150  | ns          |        |            |

| 18*              | TosH2iol | OSC1↑ (Q2 cycle) to Port input                | PIC16 <b>C</b> 63/65A | 100 | _    | _           | ns     |            |

|                  |          | invalid (I/O in hold time)                    | PIC16LC63/65A         | 200 | _    | _           | ns     |            |

| 19*              | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in | setup time)           | 0   | _    | _           | ns     |            |

| 20*              | TioR     | Port output rise time                         | PIC16 <b>C</b> 63/65A | _   | 10   | 40          | ns     |            |

|                  |          |                                               | PIC16LC63/65A         | _   | _    | 80          | ns     |            |

| 21*              | TioF     | Port output fall time                         | PIC16 <b>C</b> 63/65A | _   | 10   | 40          | ns     |            |

|                  |          | PIC16 <b>LC</b> 63/65/                        |                       | _   | _    | 80          | ns     |            |

| 22††*            | Tinp     | INT pin high or low time                      | 1                     | Тсү | _    | _           | ns     |            |

| 23††*            | Trbp     | RB7:RB4 change INT high or low                | / time                | Тсү | —    | _           | ns     |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

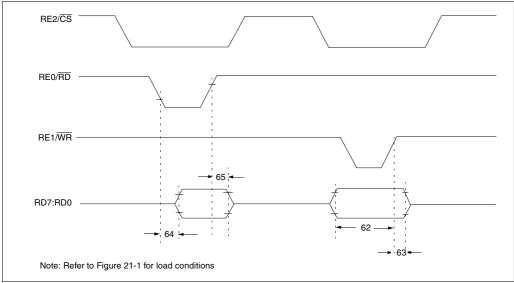

# FIGURE 21-8: PARALLEL SLAVE PORT TIMING (PIC16CR65)

# TABLE 21-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16CR65)

| Sym                                                                                        | Characteristic                                                                             | Min                                                                                                                                                              | Тур†                                                                                                                                                                                                     | Max                                                                                                                                                                                                 | Units                                                                                                                                                                                                                                                                                                                                                | Conditions                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TdtV2wrH                                                                                   | Data in valid before $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ (setup time) |                                                                                                                                                                  | 20                                                                                                                                                                                                       | _                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TwrH2dtI $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data–in invalid (hold |                                                                                            | PIC16 <b>CR</b> 65                                                                                                                                               | 20                                                                                                                                                                                                       | _                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| t                                                                                          | time)                                                                                      | PIC16 <b>LCR</b> 65                                                                                                                                              | 35                                                                                                                                                                                                       | —                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TrdL2dtV                                                                                   | $\overline{\text{RD}}\downarrow$ and $\overline{\text{CS}}\downarrow$ to data–out valid    |                                                                                                                                                                  | -                                                                                                                                                                                                        | —                                                                                                                                                                                                   | 80                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TrdH2dtl                                                                                   | $\overline{\text{RD}}$ for $\overline{\text{CS}}$ to data-out invalid                      |                                                                                                                                                                  | 10                                                                                                                                                                                                       | —                                                                                                                                                                                                   | 30                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                            | TdtV2wrH<br>TwrH2dtl<br>TrdL2dtV                                                           | TdtV2wrH     Data in valid before WR↑ or CS↑ (setu       TwrH2dtl     WR↑ or CS↑ to data–in invalid (hold time)       TrdL2dtV     RD↓ and CS↓ to data–out valid | TdtV2wrH     Data in valid before WR↑ or CS↑ (setup time)       TwrH2dtl     WR↑ or CS↑ to data-in invalid (hold time)       PIC16CR65       PIC16LCR65       TrdL2dtV     RD↓ and CS↓ to data-out valid | TdtV2wrH     Data in valid before WR↑ or CS↑ (setup time)     20       TwrH2dtl     WR↑ or CS↑ to data-in invalid (hold time)     PIC16CR65     20       TrdL2dtV     RD↓ and CS↓ to data-out valid | TdtV2wrH     Data in valid before $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ (setup time)     20        TwrH2dtl $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data-in invalid (hold time)     PIC16 <b>CR</b> 65     20        TrdL2dtV $\overline{RD}^{\downarrow}$ and $\overline{CS}^{\downarrow}$ to data-out valid | TdtV2wrH     Data in valid before $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ (seture time)     20        TwrH2dtl $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data-in invalid (hold time)     PIC16 <b>CR</b> 65     20        TrdL2dtV $\overline{RD}_{\downarrow}$ and $\overline{CS}_{\downarrow}$ to data-out valid      80 | TdtV2wrH       Data in valid before $\overline{WR}$ or $\overline{CS}$ (setup time)       20        ns         TwrH2dtl $\overline{WR}$ or $\overline{CS}$ to data-in invalid (hold time)       PIC16 <b>CR</b> 65       20        ns         TrdL2dtV $\overline{RD}$ and $\overline{CS}$ to data-out valid        ns       ns         TrdL2dtV $\overline{RD}$ and $\overline{CS}$ to data-out valid         ns |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

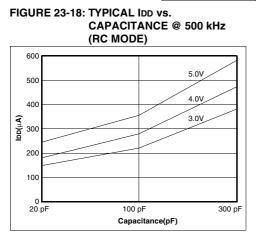

#### **TABLE 23-1: RC OSCILLATOR** FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |        |  |  |  |

|--------|------|----------------------------|--------|--|--|--|

| Cext   | nexi |                            |        |  |  |  |

| 22 pF  | 5k   | 4.12 MHz                   | ± 1.4% |  |  |  |

|        | 10k  | 2.35 MHz                   | ± 1.4% |  |  |  |

|        | 100k | 268 kHz                    | ± 1.1% |  |  |  |

| 100 pF | 3.3k | 1.80 MHz                   | ± 1.0% |  |  |  |

|        | 5k   | 1.27 MHz                   | ± 1.0% |  |  |  |

|        | 10k  | 688 kHz                    | ± 1.2% |  |  |  |

|        | 100k | 77.2 kHz                   | ± 1.0% |  |  |  |

| 300 pF | 3.3k | 707 kHz                    | ± 1.4% |  |  |  |

|        | 5k   | 501 kHz                    | ± 1.2% |  |  |  |

|        | 10k  | 269 kHz                    | ± 1.6% |  |  |  |

|        | 100k | 28.3 kHz                   | ± 1.1% |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

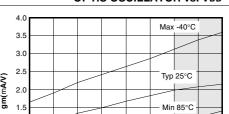

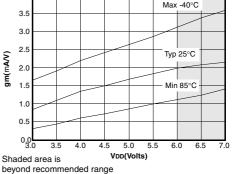

# FIGURE 23-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

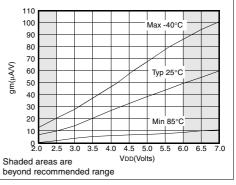

# FIGURE 23-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

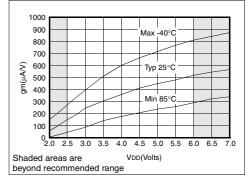

# FIGURE 23-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

# 24.4 18-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Plastic SOIC (SO) |             |           |        |       |           |  |  |  |  |

|--------|----------------------------------|-------------|-----------|--------|-------|-----------|--|--|--|--|

|        |                                  | Millimeters |           | Inches |       |           |  |  |  |  |

| Symbol | Min                              | Max         | Notes     | Min    | Max   | Notes     |  |  |  |  |

| α      | 0°                               | 8°          |           | 0°     | 8°    |           |  |  |  |  |

| А      | 2.362                            | 2.642       |           | 0.093  | 0.104 |           |  |  |  |  |

| A1     | 0.101                            | 0.300       |           | 0.004  | 0.012 |           |  |  |  |  |

| В      | 0.355                            | 0.483       |           | 0.014  | 0.019 |           |  |  |  |  |

| С      | 0.241                            | 0.318       |           | 0.009  | 0.013 |           |  |  |  |  |

| D      | 11.353                           | 11.735      |           | 0.447  | 0.462 |           |  |  |  |  |

| E      | 7.416                            | 7.595       |           | 0.292  | 0.299 |           |  |  |  |  |

| е      | 1.270                            | 1.270       | Reference | 0.050  | 0.050 | Reference |  |  |  |  |

| Н      | 10.007                           | 10.643      |           | 0.394  | 0.419 |           |  |  |  |  |

| h      | 0.381                            | 0.762       |           | 0.015  | 0.030 |           |  |  |  |  |

| L      | 0.406                            | 1.143       |           | 0.016  | 0.045 |           |  |  |  |  |

| N      | 18                               | 18          |           | 18     | 18    |           |  |  |  |  |

| CP     | _                                | 0.102       |           | -      | 0.004 |           |  |  |  |  |

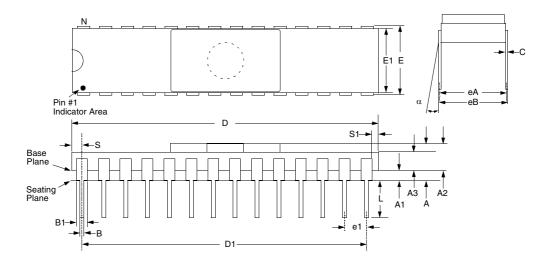

# 24.9 28-Lead Ceramic Side Brazed Dual In-Line with Window (300 mil) (JW)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic Side Brazed Dual In-Line (CER) |        |             |           |        |       |       |  |  |  |

|-------------------------------------------------------|--------|-------------|-----------|--------|-------|-------|--|--|--|

| 0 militad                                             |        | Millimeters |           | Inches |       |       |  |  |  |

| Symbol                                                | Min    | Мах         | Notes     | Min    | Max   | Notes |  |  |  |

| α                                                     | 0°     | 10°         |           | 0°     | 10°   |       |  |  |  |

| Α                                                     | 3.937  | 5.030       |           | 0.155  | 0.198 |       |  |  |  |

| A1                                                    | 1.016  | 1.524       |           | 0.040  | 0.060 |       |  |  |  |

| A2                                                    | 2.921  | 3.506       |           | 0.115  | 0.138 |       |  |  |  |

| A3                                                    | 1.930  | 2.388       |           | 0.076  | 0.094 |       |  |  |  |

| В                                                     | 0.406  | 0.508       |           | 0.016  | 0.020 |       |  |  |  |

| B1                                                    | 1.219  | 1.321       | Typical   | 0.048  | 0.052 |       |  |  |  |

| С                                                     | 0.228  | 0.305       | Typical   | 0.009  | 0.012 |       |  |  |  |

| D                                                     | 35.204 | 35.916      |           | 1.386  | 1.414 |       |  |  |  |

| D1                                                    | 32.893 | 33.147      | Reference | 1.295  | 1.305 |       |  |  |  |

| E                                                     | 7.620  | 8.128       |           | 0.300  | 0.320 |       |  |  |  |

| E1                                                    | 7.366  | 7.620       |           | 0.290  | 0.300 |       |  |  |  |