Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64at-04-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | DIP<br>Pin#     | SOIC<br>Pin#      | Pin Type | Buffer<br>Type                   | Description                                                                                                                                                                                                 |  |  |  |  |

|-------------------|-----------------|-------------------|----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OSC1/CLKIN        | 16              | 16                | I        | ST/CMOS(1)                       | Oscillator crystal input/external clock source input.                                                                                                                                                       |  |  |  |  |

| OSC2/CLKOUT       | 15              | 15                | 0        | _                                | Oscillator crystal output. Connects to crystal or resonator in crysta<br>oscillator mode. In RC mode, the pin outputs CLKOUT which has<br>1/4 the frequency of OSC1, and denotes the instruction cycle rate |  |  |  |  |

| MCLR/VPP          | 4               | 4                 | I/P      | ST                               | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                       |  |  |  |  |

|                   |                 |                   |          |                                  | PORTA is a bi-directional I/O port.                                                                                                                                                                         |  |  |  |  |

| RA0               | 17              | 17                | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RA1               | 18              | 18                | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RA2               | 1               | 1                 | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RA3               | 2               | 2                 | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RA4/T0CKI         | 3               | 3                 | I/O      | ST                               | RA4 can also be the clock input to the Timer0 timer/counter.<br>Output is open drain type.                                                                                                                  |  |  |  |  |

|                   |                 |                   |          |                                  | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                          |  |  |  |  |

| RB0/INT           | 6               | 6                 | I/O      | TTL/ST <sup>(2)</sup>            | RB0 can also be the external interrupt pin.                                                                                                                                                                 |  |  |  |  |

| RB1               | 7               | 7                 | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RB2               | 8               | 8                 | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RB3               | 9               | 9                 | I/O      | TTL                              |                                                                                                                                                                                                             |  |  |  |  |

| RB4               | 10              | 10                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                    |  |  |  |  |

| RB5               | 11              | 11                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                    |  |  |  |  |

| RB6               | 12              | 12                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming clock.                                                                                                                                                          |  |  |  |  |

| RB7               | 13              | 13                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming data.                                                                                                                                                           |  |  |  |  |

| Vss               | 5               | 5                 | Р        | -                                | Ground reference for logic and I/O pins.                                                                                                                                                                    |  |  |  |  |

| Vdd               | 14              | 14                | Р        | _                                | Positive supply for logic and I/O pins.                                                                                                                                                                     |  |  |  |  |

| Legend: I = input | 0 = ou<br>— = N | utput<br>lot used |          | ) = input/outpu<br>L = TTL input |                                                                                                                                                                                                             |  |  |  |  |

### **PIC16C61 PINOUT DESCRIPTION TABLE 3-1:**

Note

1:

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

2:

This buffer is a Schmitt Trigger input when configured as the external interrupt.

Configured as the external interrup

3: This buffer is a Schmitt Trigger input when used in serial programming mode.

### 4.0 MEMORY ORGANIZATION

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

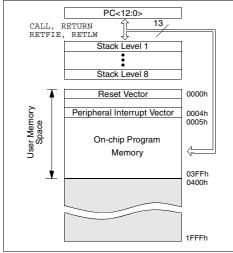

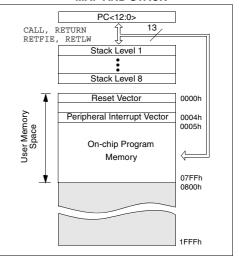

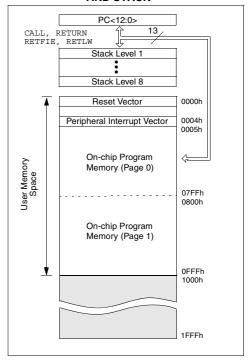

### 4.1 Program Memory Organization

The PIC16C6X family has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C61  | 1K x 14           | 0000h-03FFh   |

| PIC16C62  | 2K x 14           | 0000h-07FFh   |

| PIC16C62A | 2K x 14           | 0000h-07FFh   |

| PIC16CR62 | 2K x 14           | 0000h-07FFh   |

| PIC16C63  | 4K x 14           | 0000h-0FFFh   |

| PIC16CR63 | 4K x 14           | 0000h-0FFFh   |

| PIC16C64  | 2K x 14           | 0000h-07FFh   |

| PIC16C64A | 2K x 14           | 0000h-07FFh   |

| PIC16CR64 | 2K x 14           | 0000h-07FFh   |

| PIC16C65  | 4K x 14           | 0000h-0FFFh   |

| PIC16C65A | 4K x 14           | 0000h-0FFFh   |

| PIC16CR65 | 4K x 14           | 0000h-0FFFh   |

| PIC16C66  | 8K x 14           | 0000h-1FFFh   |

| PIC16C67  | 8K x 14           | 0000h-1FFFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 4-1: PIC16C61 PROGRAM MEMORY MAP AND STACK

### FIGURE 4-2: PIC16C62/62A/R62/64/64A/ R64 PROGRAM MEMORY MAP AND STACK

### FIGURE 4-3: PIC16C63/R63/65/65A/R65 PROGRAM MEMORY MAP AND STACK

### 4.2.2.1 STATUS REGISTER

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The STATUS register, shown in Figure 4-9, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0       | R-1 | R-1          | R/W-x        | R/W-x | R/W-x |                                                             |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|--------------|--------------|-------|-------|-------------------------------------------------------------|--|--|

| IRP      | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RP0         | TO  | PD           | Z            | DC    | С     | R = Readable bit                                            |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |     |              |              |       | bit0  | W = Writable bit<br>- n = Value at POR reset<br>x = unknown |  |  |

| bit 7:   | IRP: RegIster Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                                                                                                                                                                                                    |             |     |              |              |       |       |                                                             |  |  |

| bit 6-5: | <ul> <li>t 6-5: RP1:RP0: Register Bank Select bits (used for direct addressing)</li> <li>11 = Bank 3 (180h - 1FFh)</li> <li>10 = Bank 2 (100h - 17Fh)</li> <li>01 = Bank 1 (80h - FFh)</li> <li>00 = Bank 0 (00h - 7Fh)</li> <li>Each bank is 128 bytes.</li> </ul>                                                                                                                                                                                                                                         |             |     |              |              |       |       |                                                             |  |  |

| bit 4:   | <b>TO</b> : Time-or<br>1 = After points $0 = A WDT$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ower-up, CL |     | uction, or S | LEEP instruc | tion  |       |                                                             |  |  |

| bit 3:   | <b>PD</b> : Power-<br>1 = After po<br>0 = By exec                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ower-up or  |     |              | tion         |       |       |                                                             |  |  |

| bit 2:   | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                                                                                                                                                         |             |     |              |              |       |       |                                                             |  |  |

| bit 1:   | <b>DC</b> : Digit carry/borrow bit (for ADDWF, ADDLW, SUBLW, and SUBWF instructions) (For borrow the polarity is reversed).<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                                                                                                                                                                                                                                               |             |     |              |              |       |       |                                                             |  |  |

| bit 0:   | <ul> <li>C: Carry/borrow bit (for ADDWF, ADDLW, SUBLW, and SUBWF instructions)(For borrow the polarity is reversed).</li> <li>1 = A carry-out from the most significant bit of the result occurred</li> <li>0 = No carry-out from the most significant bit of the result</li> <li>Note: a subtraction is executed by adding the two's complement of the second operand.<br/>For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |             |     |              |              |       |       |                                                             |  |  |

### FIGURE 4-9: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

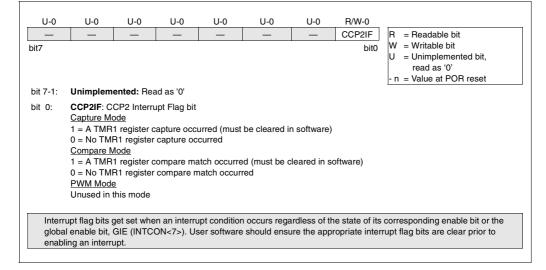

### 4.2.2.7 PIR2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 4-21: PIR2 REGISTER (ADDRESS 0Dh)

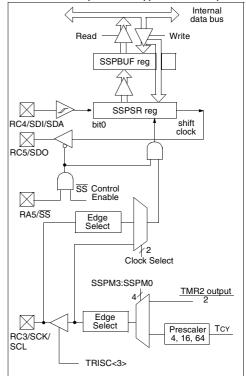

### 11.3.1 SSP MODULE IN SPI MODE FOR PIC16C66/67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS

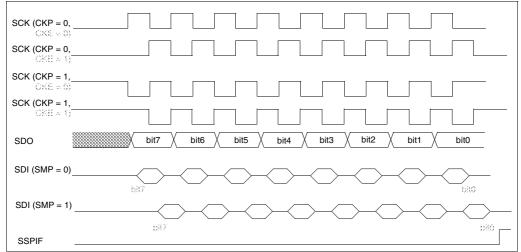

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device. MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

### EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C66/67)

| LOOP | BCF<br>BSF<br>BTFSS | STATUS,<br>STATUS,<br>SSPSTAT, | RP0 | ;Specify Bank 1<br>;<br>;Has data been<br>;received<br>;(transmit<br>;complete)? |

|------|---------------------|--------------------------------|-----|----------------------------------------------------------------------------------|

|      | GOTO                | LOOP                           |     | ;No                                                                              |

|      | BCF                 | STATUS,                        | RP0 | ;Specify Bank 0                                                                  |

|      | MOVF                | SSPBUF,                        | W   | ;W reg = contents<br>; of SSPBUF                                                 |

|      | MOVWF               | RXDATA                         |     | ;Save in user RAM                                                                |

|      | MOVF                | TXDATA,                        | W   | ;W reg = contents<br>; of TXDATA                                                 |

|      | MOVWF               | SSPBUF                         |     | ;New data to xmit                                                                |

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

### FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C66/67)

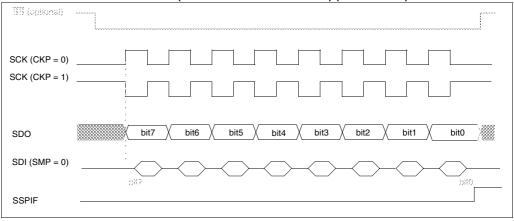

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

- Note: When the SPI is in Slave Mode with SS pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the SS pin is set to VDD.

- Note: If the SPI is used in Slave Mode with CKE = '1', then the SS pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

### FIGURE 11-11: SPI MODE TIMING, MASTER MODE (PIC16C66/67)

### FIGURE 11-12: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) (PIC16C66/67)

### 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0  | R/W-0                                                       | R/W-0                       | R/W-0        | U-0                     | R/W-0                        | R-1        | R/W-0       |                                                                                       |

|--------|-------------------------------------------------------------|-----------------------------|--------------|-------------------------|------------------------------|------------|-------------|---------------------------------------------------------------------------------------|

| CSRC   | TX9                                                         | TXEN                        | SYNC         | —                       | BRGH                         | TRMT       | TX9D        | R = Readable bit                                                                      |

| bit7   |                                                             |                             |              |                         |                              |            | bit0        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset  |

| bit 7: | CSRC: Clo                                                   | ck Source                   | Select bit   |                         |                              |            |             | <u>,</u>                                                                              |

|        | Asynchron<br>Don't care                                     | <u>ous mode</u>             |              |                         |                              |            |             |                                                                                       |

|        | Synchrono<br>1 = Master<br>0 = Slave n                      | mode (Clo                   |              |                         |                              | G)         |             |                                                                                       |

| bit 6: | <b>TX9</b> : 9-bit 1 = Selects 0 = Selects                  | 9-bit trans                 | smission     |                         |                              |            |             |                                                                                       |

| bit 5: | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SRE | iit enabled<br>iit disabled |              | EN in SYI               | NC mode.                     |            |             |                                                                                       |

| bit 4: | <b>SYNC</b> : US<br>1 = Synchr<br>0 = Asynch                | onous mod                   | le           |                         |                              |            |             |                                                                                       |

| bit 3: | Unimplem                                                    | ented: Re                   | ad as '0'    |                         |                              |            |             |                                                                                       |

| bit 2: | BRGH: Hig                                                   | h Baud Ra                   | ate Select b | it                      |                              |            |             |                                                                                       |

|        | Asynchron<br>1 = High sp                                    |                             |              |                         |                              |            |             |                                                                                       |

|        | Note:                                                       | experienc<br>higher ba      | e a high ra  | te of recei<br>n BRGH = | ive errors. I<br>= 0 can sup | t is recom | mended that | ed mode (BRGH = 1) may<br>BRGH = 0. If you desire a<br>e errata for additional infor- |

|        | 0 = Low sp                                                  | eed                         |              |                         |                              |            |             |                                                                                       |

|        | Synchrono<br>Unused in                                      |                             |              |                         |                              |            |             |                                                                                       |

| bit 1: | <b>TRMT</b> : Trai<br>1 = TSR er<br>0 = TSR fu              | npty                        | Register S   | tatus bit               |                              |            |             |                                                                                       |

| bit 0: | <b>TX9D</b> : 9th                                           | bit of trans                | mit data. C  | an be pari              | ty bit.                      |            |             |                                                                                       |

### 12.4 USART Synchronous Slave Mode

### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Synchronous Slave Mode differs from Master Mode in the fact that the shift clock is supplied externally at the CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit  $\mathsf{TXIE}.$

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, enable bit SREN is a don't care in slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing enable bit CREN.

### 13.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

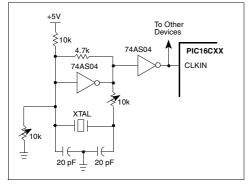

Figure 13-6 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 13-6: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

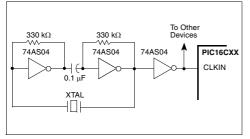

Figure 13-7 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 13-7: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

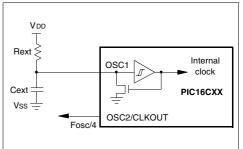

### 13.2.4 RC OSCILLATOR

For timing insensitive applications the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 13-8 shows how the RC combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-5 for waveform).

### FIGURE 13-8: RC OSCILLATOR MODE

## 14.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 14-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 14-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

### TABLE 14-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 14-2 lists the instructions recognized by the MPASM assembler.

Figure 14-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXX products, do not use the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 14-1: GENERAL FORMAT FOR INSTRUCTIONS

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                                                                                        | IORLW             | Inclusive OR Literal with W                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [label] INCFSZ f,d                                                                                                                                                                                                                                                                            | Syntax:           | [label] IORLW k                                                               |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                                                                                             | Operands:         | $0 \le k \le 255$                                                             |

|                   | d ∈ [0,1]                                                                                                                                                                                                                                                                                     | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                  |

| Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                    | Status Affected:  | Z                                                                             |

| Status Affected:  | None                                                                                                                                                                                                                                                                                          | Encoding:         | 11 1000 kkkk kkkk                                                             |

| Encoding:         | 00 1111 dfff ffff                                                                                                                                                                                                                                                                             | Description:      | The contents of the W register is                                             |

| Description:      | The contents of register 'f' are incre-                                                                                                                                                                                                                                                       |                   | OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Description.      | mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is                                                                                                                                                                                                      | Words:            | 1                                                                             |

|                   | placed back in register 'f'.<br>If the result is 1, the next instruction is                                                                                                                                                                                                                   | Cycles:           | 1                                                                             |

|                   | executed. If the result is 0, a NOP is exe-<br>cuted instead making it a 2TCY instruc-                                                                                                                                                                                                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

|                   | tion.                                                                                                                                                                                                                                                                                         |                   | Decode Read Process Write to<br>literal 'k' data W                            |

| Words:            | 1                                                                                                                                                                                                                                                                                             |                   |                                                                               |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                          | Example           | IORLW 0x35                                                                    |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                   | ·                 | Before Instruction                                                            |

|                   | Decode Read Process Write to<br>register 'f' data destination                                                                                                                                                                                                                                 |                   | W = 0x9A                                                                      |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                   |                   | After Instruction<br>W = 0xBF                                                 |

| ii enipi          | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |                   | Z = 1                                                                         |

|                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                                                                                              |                   |                                                                               |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•                                                                                                                                                                                                                                              |                   |                                                                               |

|                   | $\begin{array}{rcl} Before \mbox{ Instruction} & PC & = & \mbox{ address HERE} \\ After \mbox{ Instruction} & \\ CNT & = & CNT + 1 & \\ \mbox{ if } CNT = & 0, & \\ PC & = & \mbox{ address CONTINUE} & \\ \mbox{ if } CNT \neq & 0, & \\ PC & = & \mbox{ address HERE} + 1 & \\ \end{array}$ |                   |                                                                               |

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

NOTES:

# 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C62A/R62/64A/R64

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                   | 55°C to +125°C                                      |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Storage temperature                                                                                              | 65°C to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                               | 0.3V to (VDD + 0.3V)                                |

| Voltage on VDD with respect to VSS                                                                               | -0.3V to +7.5V                                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                     | 0V to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                               | 0V to +14V                                          |

| Total power dissipation (Note 1)                                                                                 | 1.0W                                                |

| Maximum current out of VSS pin                                                                                   |                                                     |

| Maximum current into VDD pin                                                                                     | 250 mA                                              |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                     | ±20 mA                                              |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                   | ±20 mA                                              |

| Maximum output current sunk by any I/O pin                                                                       | 25 mA                                               |

| Maximum output current sourced by any I/O pin                                                                    | 25 mA                                               |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined)                                                       | 200 mA                                              |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined)                                                    | 200 mA                                              |

| Maximum current sunk by PORTC and PORTD (combined)                                                               | 200 mA                                              |

| Maximum current sourced by PORTC and PORTD (combined)                                                            | 200 mA                                              |

| Note 1. Power dissipation is calculated as follows: $Pdis = Vpp \times (Ipp - \sum Ipu) + \sum (Vpp - \sum Ipu)$ | $(V_{OU}) \times (OU) + \Sigma(V_{OU} \times (OU))$ |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62A-04<br>PIC16CR62-04<br>PIC16C64A-04<br>PIC16CR64-04                                                | PIC16C62A-10<br>PIC16CR62-10<br>PIC16C64A-10<br>PIC16CR64-10                                | PIC16C62A-20<br>PIC16CR62-20<br>PIC16C64A-20<br>PIC16CR64-20                                  | PIC16LC62A-04<br>PIC16LCR62-04<br>PIC16LC64A-04<br>PIC16LCR64-04                                        | JW Devices                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                     | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                 |

| ХТ  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 µA max. at 3.0V<br>Freq: 4 MHz max.             | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| HS  | VpD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              |                                                                                             | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use<br>in HS mode                                                                   | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.           |

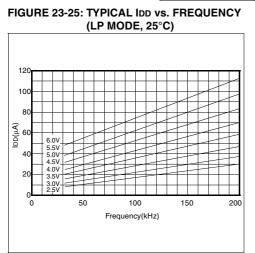

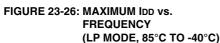

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                          | Not recommended for use in LP mode                                                            | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

<sup>© 1997-2013</sup> Microchip Technology Inc.

### 19.2 DC Characteristics: PIC16LC65-04 (Commercial, Industrial)

| $ \begin{array}{c} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{DC CHARACTERISTICS} \end{array} \begin{array}{c} \mbox{Standard Operating temperature} & -40^\circ C & \leq Ta \leq +85^\circ C \mbox{ for industrial and} \\ & 0^\circ C & \leq Ta \leq +70^\circ C \mbox{ for commercial} \end{array} \end{array}$ |                                                                  |      |      |      |     |       |                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|------|-----|-------|-----------------------------------------------------------------|

| Param<br>No.                                                                                                                                                                                                                                                                                                                                    | Characteristic                                                   | Sym  | Min  | Тур† | Max | Units | Conditions                                                      |

| D001                                                                                                                                                                                                                                                                                                                                            | Supply Voltage                                                   | Vdd  | 3.0  | -    | 6.0 | V     | LP, XT, RC osc configuration (DC - 4 MHz)                       |

| D002*                                                                                                                                                                                                                                                                                                                                           | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -    | 1.5  | -   | V     |                                                                 |

| D003                                                                                                                                                                                                                                                                                                                                            | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -    | Vss  | -   | V     | See section on Power-on Reset for details                       |

| D004*                                                                                                                                                                                                                                                                                                                                           | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd | 0.05 | -    | -   | V/ms  | See section on Power-on Reset for details                       |

| D010                                                                                                                                                                                                                                                                                                                                            | Supply Current (Note 2, 5)                                       | IDD  | -    | 2.0  | 3.8 | mA    | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 3.0V (Note 4)   |

| D010A                                                                                                                                                                                                                                                                                                                                           |                                                                  |      | -    | 22.5 | 105 | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 4.0V, WDT disabled |

| D020                                                                                                                                                                                                                                                                                                                                            | Power-down Current                                               | IPD  | -    | 7.5  | 800 | μA    | VDD = 3.0V, WDT enabled, -40°C to +85°C                         |

| D021                                                                                                                                                                                                                                                                                                                                            | (Note 3, 5)                                                      |      | -    | 0.9  | 800 | μA    | VDD = 3.0V, WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$        |

| D021A                                                                                                                                                                                                                                                                                                                                           |                                                                  |      | -    | 0.9  | 800 | μA    | VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

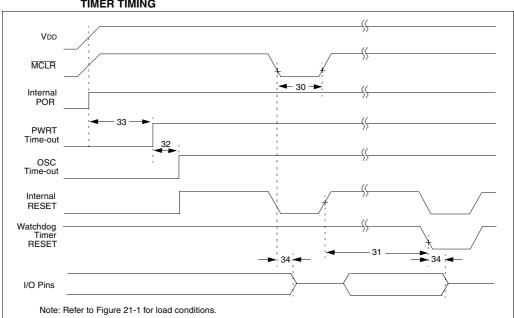

# FIGURE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

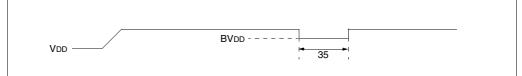

### FIGURE 21-5: BROWN-OUT RESET TIMING

# TABLE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†      | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2   | —         |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | —   | 1024 Tosc | I   | _     | TOSC = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or WDT reset      | —   | _         | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100 | —         | l   | μs    | $V$ DD $\leq$ BVDD (D005) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

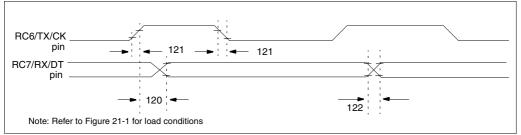

### FIGURE 21-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 21-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym                                     | Characteristic                   |                | Min | Тур† | Max | Units | Conditions |

|--------------|-----------------------------------------|----------------------------------|----------------|-----|------|-----|-------|------------|

| 120*         | TckH2dtV                                | SYNC XMIT (MASTER & SLAVE)       | PIC16CR63/R65  | —   | —    | 80  | ns    |            |

|              | Clock high to data out valid            |                                  | PIC16LCR63/R65 | —   | —    | 100 | ns    |            |

| 121*         | Tckrf Clock out rise time and fall time |                                  | PIC16CR63/R65  | _   | —    | 45  | ns    |            |

|              | (Master Mode)                           | PIC16LCR63/R65                   | —              | —   | 50   | ns  |       |            |

| 122*         | Tdtrf                                   | Data out rise time and fall time | PIC16CR63/R65  | _   | —    | 45  | ns    |            |

|              |                                         |                                  | PIC16LCR63/R65 | _   | —    | 50  | ns    |            |

\* These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

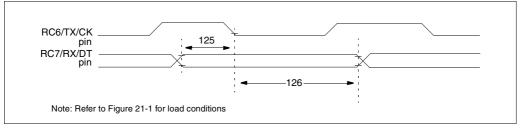

### FIGURE 21-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 21-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                      | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|---------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK ↓ (DT setup time) | 15  | I    |     | ns    |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                      | 15  | -    | _   | ns    |            |

These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C6X

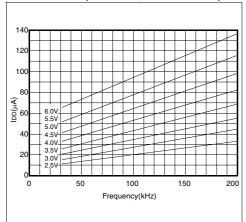

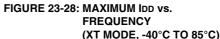

### FIGURE 23-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

# Data based on matrix samples. See first page of this section for details.

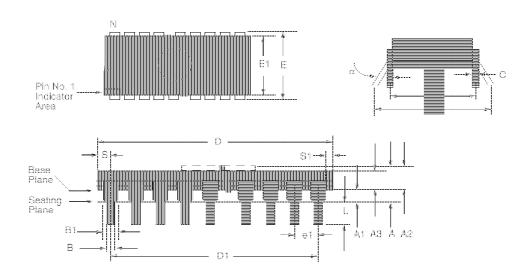

### 24.3 40-Lead Plastic Dual In-line (600 mil) (P)

| Package Group: Plastic Dual In-Line (PLA) |        |             |           |        |       |           |  |

|-------------------------------------------|--------|-------------|-----------|--------|-------|-----------|--|

|                                           |        | Millimeters |           | Inches |       |           |  |

| Symbol                                    | Min    | Max         | Notes     | Min    | Max   | Notes     |  |

| α                                         | 0°     | 10°         |           | 0°     | 10°   |           |  |

| А                                         | _      | 5.080       |           | _      | 0.200 |           |  |

| A1                                        | 0.381  | _           |           | 0.015  | _     |           |  |

| A2                                        | 3.175  | 4.064       |           | 0.125  | 0.160 |           |  |

| В                                         | 0.355  | 0.559       |           | 0.014  | 0.022 |           |  |

| B1                                        | 1.270  | 1.778       | Typical   | 0.050  | 0.070 | Typical   |  |

| С                                         | 0.203  | 0.381       | Typical   | 0.008  | 0.015 | Typical   |  |

| D                                         | 51.181 | 52.197      |           | 2.015  | 2.055 |           |  |

| D1                                        | 48.260 | 48.260      | Reference | 1.900  | 1.900 | Reference |  |

| E                                         | 15.240 | 15.875      |           | 0.600  | 0.625 |           |  |

| E1                                        | 13.462 | 13.970      |           | 0.530  | 0.550 |           |  |

| e1                                        | 2.489  | 2.591       | Typical   | 0.098  | 0.102 | Typical   |  |

| eA                                        | 15.240 | 15.240      | Reference | 0.600  | 0.600 | Reference |  |

| eB                                        | 15.240 | 17.272      |           | 0.600  | 0.680 |           |  |

| L                                         | 2.921  | 3.683       |           | 0.115  | 0.145 |           |  |

| N                                         | 40     | 40          |           | 40     | 40    |           |  |

| S                                         | 1.270  | -           |           | 0.050  | -     |           |  |

| S1                                        | 0.508  | -           |           | 0.020  | -     |           |  |

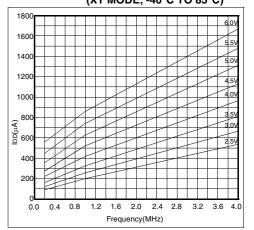

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |        |             |           |        |       |           |  |

|--------------------------------------------------|--------|-------------|-----------|--------|-------|-----------|--|