Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64at-04i-l |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

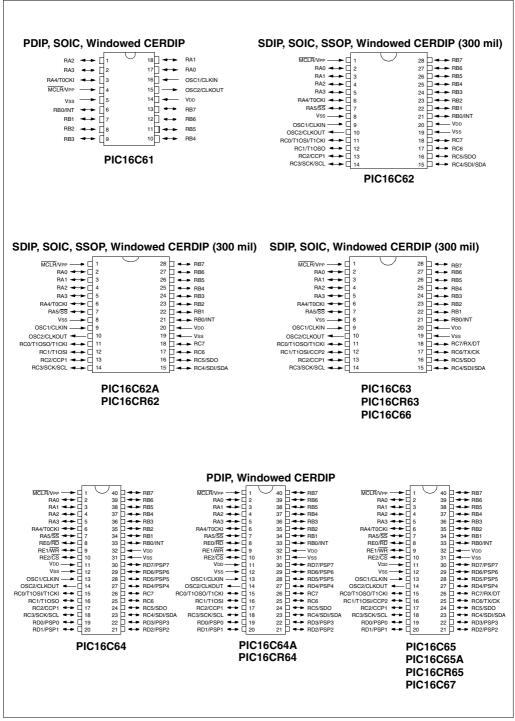

### **Pin Diagrams**

### FIGURE 4-15: PIE1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 8Ch)

| R/W-0  | R/W-0       | R/W-0     | R/W-0        | R/W-0        | R/W-0        | R/W-0  | R/W-0  |                          |

|--------|-------------|-----------|--------------|--------------|--------------|--------|--------|--------------------------|

| PSPIE  | —           | RCIE      | TXIE         | SSPIE        | CCP1IE       | TMR2IE | TMR1IE | R = Readable bit         |

| bit7   |             |           |              |              |              |        | bit0   | W = Writable bit         |

|        |             |           |              |              |              |        |        | U = Unimplemented bit,   |

|        |             |           |              |              |              |        |        | read as '0'              |

|        |             |           |              |              |              |        |        | - n = Value at POR reset |

| bit 7: | 1 = Enable  |           |              |              | upt Enable b | oit    |        |                          |

|        | 0 = Disable |           |              |              |              |        |        |                          |

| 1.1.0  |             |           |              | •            |              |        |        |                          |

| bit 6: | Reserved:   | Always ma | aintain this | oit clear.   |              |        |        |                          |

| bit 5: | RCIE: USA   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              | •            |              |        |        |                          |

| bit 4: | TXIE: USA   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              | •            |              |        |        |                          |

| bit 3: | SSPIE: Syr  |           |              | Interrupt Er | nable bit    |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           | •            |              |              |        |        |                          |

| bit 2: | CCP1IE: C   |           |              | bit          |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           | •            |              |              |        |        |                          |

| bit 1: | TMR2IE: T   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              |              | •            |        |        |                          |

| bit 0: | TMR1IE: T   |           |              |              | it           |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable | s the TMR | I OVERTION   | nterrupt     |              |        |        |                          |

|        |             |           |              |              |              |        |        |                          |

### TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                       |

|------------|------|-------------|--------------------------------------------------------------------------------|

| RA0        | bit0 | TTL         | Input/output                                                                   |

| RA1        | bit1 | TTL         | Input/output                                                                   |

| RA2        | bit2 | TTL         | Input/output                                                                   |

| RA3        | bit3 | TTL         | Input/output                                                                   |

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0.<br>Output is open drain type. |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

### TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5                                        | Bit 4                                  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|----------------------------------------------|----------------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | —     | —     | RA5 <sup>(1)</sup>                           | RA5 <sup>(1)</sup> RA4 RA3 RA2 RA1 RA0 |       |       |       |       |                          | uu uuuu                   |

| 85h     | TRISA | —     | —     | PORTA Data Direction Register <sup>(1)</sup> |                                        |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

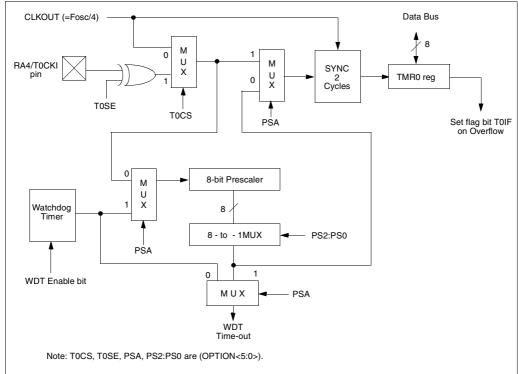

### 7.3 Prescaler

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF TMR0, MOVWF TMR0, BSF TMR0, bitx) will clear the prescaler count. When assigned to the Watchdog Timer, a CLRWDT instruction will clear the Watchdog Timer and the prescaler count. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

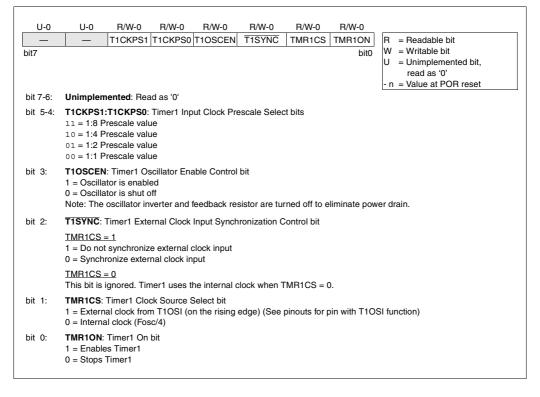

### 8.0 TIMER1 MODULE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

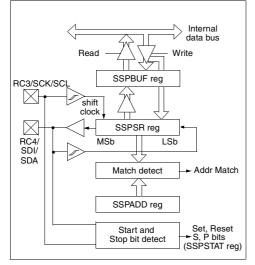

### 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in  $I^2C$  mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

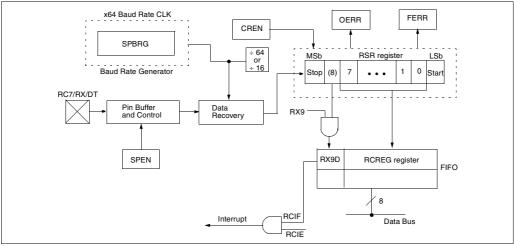

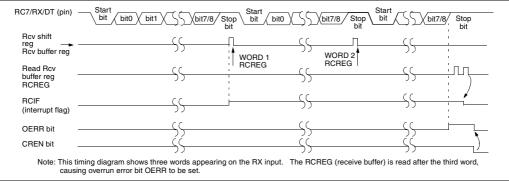

### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-10. The data comes in the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at FOSC.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is double buffered register, i.e., it is a two deep FIFO. It is

### FIGURE 12-10: USART RECEIVE BLOCK DIAGRAM

possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG is still full, then the overrun error bit, OERR (RCSTA<1>) will be set. The word in the RSR register will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear overrun bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Error bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG register will load bits RX9D and FERR with new values. Therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

### FIGURE 12-11: ASYNCHRONOUS RECEPTION

### 12.4 USART Synchronous Slave Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Synchronous Slave Mode differs from Master Mode in the fact that the shift clock is supplied externally at the CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit  $\mathsf{TXIE}.$

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, enable bit SREN is a don't care in slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing enable bit CREN.

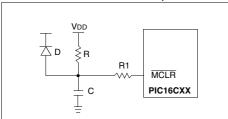

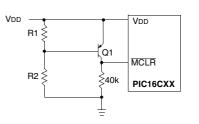

### FIGURE 13-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the devices electrical specifications.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrostatic Overstress (EOS).

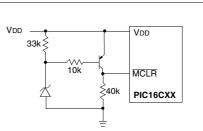

### FIGURE 13-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

### FIGURE 13-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

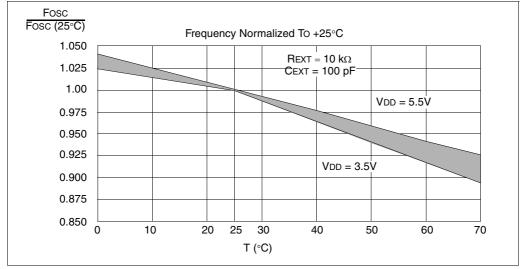

### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C61

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range. Note: The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean  $+3\sigma$ ) and (mean  $-3\sigma$ ) respectively where  $\sigma$  is standard deviation.

| Cext   | Rext | Ave<br>Fosc @ | rage<br>5V, 25°C |

|--------|------|---------------|------------------|

| 20 pF  | 4.7k | 4.52 MHz      | ± 17.35%         |

|        | 10k  | 2.47 MHz      | ± 10.10%         |

|        | 100k | 290.86 kHz    | ± 11.90%         |

| 100 pF | 3.3k | 1.92 MHz      | ± 9.43%          |

|        | 4.7k | 1.48 MHz      | ± 9.83%          |

|        | 10k  | 788.77 kHz    | ± 10.92%         |

|        | 100k | 88.11 kHz     | ± 16.03%         |

| 300 pF | 3.3k | 726.89 kHz    | ± 10.97%         |

|        | 4.7k | 573.95 kHz    | ± 10.14%         |

|        | 10k  | 307.31 kHz    | ± 10.43%         |

|        | 100k | 33.82 kHz     | ± 11.24%         |

TABLE 16-1: RC OSCILLATOR FREQUENCIES

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

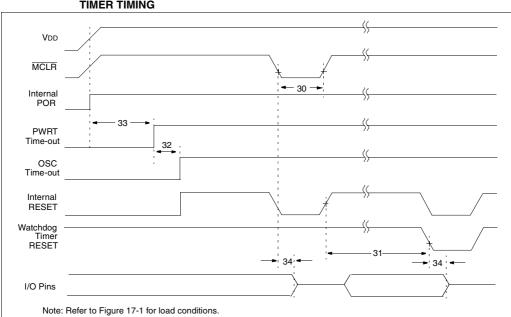

### FIGURE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

### TABLE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                           | 100 | —        | —   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | _   | 1024Tosc | _   | —     | TOSC = OSC1 period       |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low                   | _   | —        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 18.5 <u>Timing Diagrams and Specifications</u>

### FIGURE 18-2: EXTERNAL CLOCK TIMING

### TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| arameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|-----------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                 | Fosc  | External CLKIN Frequency         |     |      |        |       |                    |

|                 |       | (Note 1)                         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                 |       |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                 |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                 |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                 |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                 |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|                 |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                 |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                 |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1               | Tosc  | External CLKIN Period            | 250 | -    | —      | ns    | XT and RC osc mode |

|                 |       | (Note 1)                         | 250 | _    | —      | ns    | HS osc mode (-04)  |

|                 |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                 |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                 |       |                                  | 5   | _    | —      | μS    | LP osc mode        |

|                 |       | Oscillator Period                | 250 | _    | —      | ns    | RC osc mode        |

|                 |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                 |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                 |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                 |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                 |       |                                  | 5   | _    | —      | μs    | LP osc mode        |

| 2               | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3               | TosL, | External Clock in (OSC1) High or | 100 | —    | —      | ns    | XT oscillator      |

|                 | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|                 |       |                                  | 15  | _    | —      | ns    | HS oscillator      |

| 4               | TosR, | External Clock in (OSC1) Rise or | —   | -    | 25     | ns    | XT oscillator      |

|                 | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|                 |       |                                  | —   | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

## PIC16C6X

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

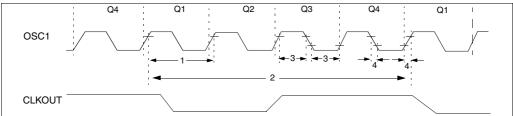

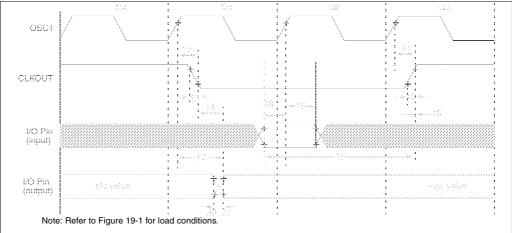

### FIGURE 19-3: CLKOUT AND I/O TIMING

| TABLE 19-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

| TADEE 13-0. |                                    |

| Parameter<br>No. | Sym      | Characteristic                             |                              | Min          | Тур† | Мах         | Units | Conditions |

|------------------|----------|--------------------------------------------|------------------------------|--------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                           |                              | -            | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>   |                              | —            | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                           |                              | _            | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                           |                              | _            | 35   | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid      |                              | —            | _    | 0.5TCY + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOUT 1              |                              | 0.25Tcy + 25 | _    | —           | ns    | Note 1     |

| 16*              | TckH2ioI | Port in hold after CLKOUT ↑                |                              | 0            | _    | —           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid         |                              | _            | 50   | 150         | ns    |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port       | PIC16 <b>C</b> 65            | 100          | _    | —           | ns    |            |

|                  |          | input invalid (I/O in hold time)           | PIC16 <b>LC</b> 65           | 200          | _    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O | in setup time)               | 0            | _    | —           | ns    |            |

| 20*              | TioR     | Port output rise time                      | PIC16 <b>C</b> 65            | —            | 10   | 25          | ns    |            |

|                  |          |                                            | PIC16 <b>LC</b> 65           | —            | _    | 60          | ns    |            |

| 21*              | TioF     | Port output fall time                      | PIC16 <b>C</b> 65            | —            | 10   | 25          | ns    |            |

|                  |          |                                            | PIC16 <b>LC</b> 65           | —            | _    | 60          | ns    |            |

| 22††*            | Tinp     | RB0/INT pin high or low time               | RB0/INT pin high or low time |              | —    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change int high or lo              | w time                       | Тсү          | _    | _           | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

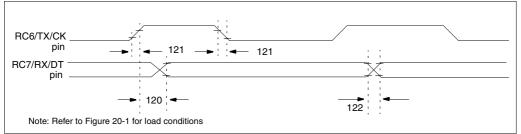

### FIGURE 20-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 20-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym                                          | Characteristic                   | stic                  |   | Тур† | Max | Units | Conditions |

|------------------|----------------------------------------------|----------------------------------|-----------------------|---|------|-----|-------|------------|

|                  |                                              | PIC16 <b>C</b> 63/65A            | _                     | — | 80   | ns  |       |            |

|                  | Clock high to data out valid                 | PIC16LC63/65A                    | _                     | — | 100  | ns  |       |            |

| 121*             | 121* Tckrf Clock out rise time and fall time |                                  | PIC16 <b>C</b> 63/65A | _ | —    | 45  | ns    |            |

|                  |                                              | (Master Mode)                    | PIC16LC63/65A         | _ | —    | 50  | ns    |            |

| 122*             | Tdtrf                                        | Data out rise time and fall time | PIC16 <b>C</b> 63/65A | _ | —    | 45  | ns    |            |

|                  |                                              |                                  | PIC16LC63/65A         | _ | —    | 50  | ns    |            |

These parameters are characterized but not tested.

**†**: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

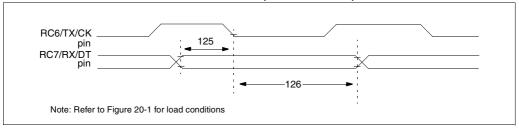

### FIGURE 20-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 20-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                            | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | $\frac{\text{SYNC RCV (MASTER \& SLAVE)}}{\text{Data setup before CK} \downarrow (\text{DT setup time})}$ | 15  | _    | _   | ns    |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                                            | 15  |      | _   | ns    |            |

These parameters are characterized but not tested.

**†**: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 21.3 DC Characteristics: PIC16CR63/R65-04 (Commercial, Industrial) PIC16CR63/R65-10 (Commercial, Industrial) PIC16CR63/R65-20 (Commercial, Industrial) PIC16LCR63/R65-04 (Commercial, Industrial)

|              |                                    |                                                                                                                                         | rd Operat |          |         |       | ss otherwise stated)<br>$A \le +85^{\circ}C$ for industrial and |  |  |

|--------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|---------|-------|-----------------------------------------------------------------|--|--|

| DC CHA       | RACTERISTICS                       | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial Operating voltage VDD range as described in DC spec Section 21.1 and Section 21.2 |           |          |         |       |                                                                 |  |  |

| Param<br>No. | Characteristic                     | Sym                                                                                                                                     | Min       | Тур<br>† | Мах     | Units | Conditions                                                      |  |  |

|              | Input Low Voltage                  |                                                                                                                                         |           |          |         |       |                                                                 |  |  |

|              | I/O ports                          | VIL                                                                                                                                     |           |          |         |       |                                                                 |  |  |

| D030         | with TTL buffer                    |                                                                                                                                         | Vss       | -        | 0.15Vdd | v     | For entire VDD range                                            |  |  |

| D030A        |                                    |                                                                                                                                         | Vss       | -        | 0.8V    | v     | $4.5V \le VDD \le 5.5V$                                         |  |  |

| D031         | with Schmitt Trigger buffer        |                                                                                                                                         | Vss       | -        | 0.2VDD  | v     |                                                                 |  |  |

| D032         | MCLR, OSC1 (in RC mode)            |                                                                                                                                         | Vss       | -        | 0.2VDD  | v     |                                                                 |  |  |

| D033         | OSC1 (in XT, HS and LP)            |                                                                                                                                         | Vss       | -        | 0.3VDD  | v     | Note1                                                           |  |  |

|              | Input High Voltage                 |                                                                                                                                         |           |          |         |       |                                                                 |  |  |

|              | I/O ports                          | Vін                                                                                                                                     |           | -        |         |       |                                                                 |  |  |

| D040         | with TTL buffer                    |                                                                                                                                         | 2.0       | -        | Vdd     | v     | $4.5V \le V$ DD $\le 5.5V$                                      |  |  |

| D040A        |                                    |                                                                                                                                         | 0.25VDD   | -        | Vdd     | v     | For entire VDD range                                            |  |  |

|              |                                    |                                                                                                                                         | + 0.8V    |          |         |       |                                                                 |  |  |

| D041         | with Schmitt Trigger buffer        |                                                                                                                                         | 0.8VDD    | -        | Vdd     | v     | For entire VDD range                                            |  |  |

| D042         | MCLR                               |                                                                                                                                         | 0.8VDD    | -        | Vdd     | V     |                                                                 |  |  |

| D042A        | OSC1 (XT, HS and LP)               |                                                                                                                                         | 0.7Vdd    | -        | Vdd     | V     | Note1                                                           |  |  |

| D043         | OSC1 (in RC mode)                  |                                                                                                                                         | 0.9Vdd    | -        | Vdd     | V     |                                                                 |  |  |

| D070         | PORTB weak pull-up current         | IPURB                                                                                                                                   | 50        | 250      | 400     | μΑ    | VDD = 5V, VPIN = VSS                                            |  |  |

|              | Input Leakage Current (Notes 2, 3) |                                                                                                                                         |           |          |         |       |                                                                 |  |  |

| D060         | I/O ports                          | lı∟                                                                                                                                     | -         | -        | ±1      | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance             |  |  |

| D061         | MCLR, RA4/T0CKI                    |                                                                                                                                         | -         | -        | ±5      | μA    | $Vss \le VPIN \le VDD$                                          |  |  |

| D063         | OSC1                               |                                                                                                                                         | -         | -        | ±5      | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and                          |  |  |

|              |                                    |                                                                                                                                         |           |          |         |       | LP osc configuration                                            |  |  |

|              | Output Low Voltage                 |                                                                                                                                         |           |          |         |       | -                                                               |  |  |

| D080         | I/O ports                          | Vol                                                                                                                                     | -         | -        | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                     |  |  |

| D083         | OSC2/CLKOUT (RC osc config)        |                                                                                                                                         | -         | -        | 0.6     | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                     |  |  |

|              | Output High Voltage                |                                                                                                                                         |           |          |         |       |                                                                 |  |  |

| D090         | I/O ports (Note 3)                 | Vон                                                                                                                                     | VDD-0.7   | -        | -       | v     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                    |  |  |

| D092         | OSC2/CLKOUT (RC osc config)        |                                                                                                                                         | VDD-0.7   | -        | -       | v     | IOH = -1.3  mA,  VDD = 4.5 V,<br>-40°C to +85°C                 |  |  |

| D150*        | Open-Drain High Voltage            | Vod                                                                                                                                     | -         | -        | 14      | V     | RA4 pin                                                         |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

### 24.10 28-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Plastic SSOP |             |        |           |        |       |           |

|-----------------------------|-------------|--------|-----------|--------|-------|-----------|

|                             | Millimeters |        |           | Inches |       |           |

| Symbol                      | Min         | Max    | Notes     | Min    | Max   | Notes     |

| α                           | 0°          | 8°     |           | 0°     | 8°    |           |

| А                           | 1.730       | 1.990  |           | 0.068  | 0.078 |           |

| A1                          | 0.050       | 0.210  |           | 0.002  | 0.008 |           |

| В                           | 0.250       | 0.380  |           | 0.010  | 0.015 |           |

| С                           | 0.130       | 0.220  |           | 0.005  | 0.009 |           |

| D                           | 10.070      | 10.330 |           | 0.396  | 0.407 |           |

| E                           | 5.200       | 5.380  |           | 0.205  | 0.212 |           |

| е                           | 0.650       | 0.650  | Reference | 0.026  | 0.026 | Reference |

| Н                           | 7.650       | 7.900  |           | 0.301  | 0.311 |           |

| L                           | 0.550       | 0.950  |           | 0.022  | 0.037 |           |

| Ν                           | 28          | 28     |           | 28     | 28    |           |

| CP                          | -           | 0.102  |           | -      | 0.004 |           |

-----

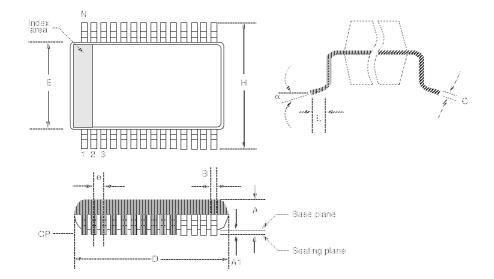

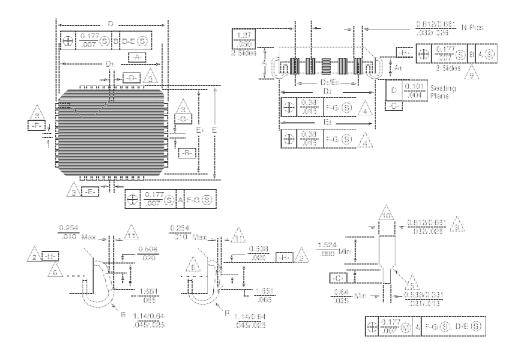

### 24.11 44-Lead Plastic Leaded Chip Carrier (Square) (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Plastic Leaded Chip Carrier (PLCC) |             |        |           |        |       |           |

|---------------------------------------------------|-------------|--------|-----------|--------|-------|-----------|

|                                                   | Millimeters |        |           | Inches |       |           |

| Symbol                                            | Min         | Max    | Notes     | Min    | Max   | Notes     |

| А                                                 | 4.191       | 4.572  |           | 0.165  | 0.180 |           |

| A1                                                | 2.413       | 2.921  |           | 0.095  | 0.115 |           |

| D                                                 | 17.399      | 17.653 |           | 0.685  | 0.695 |           |

| D1                                                | 16.510      | 16.663 |           | 0.650  | 0.656 |           |

| D2                                                | 15.494      | 16.002 |           | 0.610  | 0.630 |           |

| D3                                                | 12.700      | 12.700 | Reference | 0.500  | 0.500 | Reference |

| E                                                 | 17.399      | 17.653 |           | 0.685  | 0.695 |           |

| E1                                                | 16.510      | 16.663 |           | 0.650  | 0.656 |           |

| E2                                                | 15.494      | 16.002 |           | 0.610  | 0.630 |           |

| E3                                                | 12.700      | 12.700 | Reference | 0.500  | 0.500 | Reference |

| N                                                 | 44          | 44     |           | 44     | 44    |           |

| CP                                                | -           | 0.102  |           | _      | 0.004 |           |

| LT                                                | 0.203       | 0.381  |           | 0.008  | 0.015 |           |

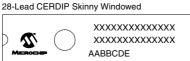

### Package Marking Information (Cont'd)

### 28-Lead SOIC

28-Lead Side Brazed Skinny Windowed

Example PIC16C66/JW  $\mathcal{D}$ 9517CAT

PIC16C62/JW

9517SBT

Example

Example

PIC16C62-20/S0111

5 9515SBA

### 40-Lead PDIP

Example

| Legend: | MMM                                                                                                                                                                                                          | Microchip part number information                                                                                           |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

|         | XXX                                                                                                                                                                                                          | Customer specific information*                                                                                              |  |

|         | AA                                                                                                                                                                                                           | Year code (last 2 digits of calender year)                                                                                  |  |

|         | BB                                                                                                                                                                                                           | Week code (week of January 1 is week '01')                                                                                  |  |

|         | С                                                                                                                                                                                                            | Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.   |  |

|         | D <sub>1</sub><br>E                                                                                                                                                                                          | Mask revision number for microcontroller<br>Assembly code of the plant or country of origin in which<br>part was assembled. |  |

| Note:   | In the event the full Microchip part number cannot be marked on one<br>line, it will be carried over to the next line thus limiting the number of<br>available characters for customer specific information. |                                                                                                                             |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# PIC16C6X

| Figure 11-2:                                                                                                                                                       | SSPCON: Sync Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                    | Control Register (Address 14h) 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 11-3:                                                                                                                                                       | SSP Block Diagram (SPI Mode) 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 11-4:                                                                                                                                                       | SPI Master/Slave Connection 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 11-5:                                                                                                                                                       | SPI Mode Timing, Master Mode or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                    | Slave Mode w/o SS Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 11-6:                                                                                                                                                       | SPI Mode Timing, Slave Mode with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                    | SS Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 11-7:                                                                                                                                                       | SSPSTAT: Sync Serial Port Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                    | Register (Address 94h)(PIC16C66/67) 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11-8:                                                                                                                                                       | SSPCON: Sync Serial Port Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 11 Or                                                                                                                                                       | Register (Address 14h)(PIC16C66/67) 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11-9:                                                                                                                                                       | SSP Block Diagram (SPI Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 11-10:                                                                                                                                                      | (PIC16C66/67)91<br>SPI Master/Slave Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 11-10.                                                                                                                                                      | (PIC16C66/67)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 11-11:                                                                                                                                                      | SPI Mode Timing, Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rigule 11-11.                                                                                                                                                      | (PIC16C66/67)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 11-12:                                                                                                                                                      | SPI Mode Timing (Slave Mode With                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| rigule 11-12.                                                                                                                                                      | CKE = 0) (PIC16C66/67)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11-13:                                                                                                                                                      | SPI Mode Timing (Slave Mode With                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| i iguio i i ioi                                                                                                                                                    | CKE = 1) (PIC16C66/67)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11-14:                                                                                                                                                      | Start and Stop Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 11-15:                                                                                                                                                      | 7-bit Address Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 11-16:                                                                                                                                                      | I <sup>2</sup> C 10-bit Address Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11-17:                                                                                                                                                      | Slave-receiver Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 11-18:                                                                                                                                                      | Data Transfer Wait State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 11-19:                                                                                                                                                      | Master-transmitter Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 11-20:                                                                                                                                                      | Master-receiver Sequence97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 11-21:                                                                                                                                                      | Combined Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 11-22:                                                                                                                                                      | Multi-master Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                    | (Two Masters)98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |