Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 33                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc64at-04i-pt |

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data may be fetched from the same memory using the same bus. Separating program and data busses further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C61 addresses 1K x 14 of program memory. The PIC16C62/62A/R62/64/64A/R64 address 2K x 14 of program memory, and the PIC16C63/R63/65/65A/R65 devices address 4K x 14 of program memory. The PIC16C66/67 address 8K x 14 program memory. All program memory is internal.

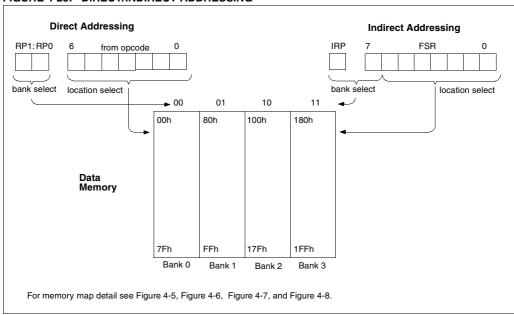

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of "special optimal situations" makes programming with the PIC16CXX simple yet efficient, thus significantly reducing the learning curve.

The PIC16CXX device contains an 8-bit ALU and working register (W). The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending upon the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. Bits C and DC operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67

| Address              | Name    | Bit 7                | Bit 6                                                    | Bit 5          | Bit 4           | Bit 3        | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------|----------------------------------------------------------|----------------|-----------------|--------------|-------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                      |                                                          |                |                 |              |             |               |           |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing           | this location                                            | uses conter    | ts of FSR to    | address data | memory (n   | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod           | lule's registe                                           | r              |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co           | ounter's (PC)                                            | Least Signi    | icant Byte      |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP                  | RP1                                                      | RP0            | TO              | PD           | Z           | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data        | ndirect data memory address pointer                      |                |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | _                    | PORTA Data Latch when written: PORTA pins when read      |                |                 |              |             |               |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat            | ta Latch whe                                             | n written: PC  | ORTB pins wh    | nen read     |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | PRTC Data Latch when written: PORTC pins when read       |                |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Date           | DRTD Data Latch when written: PORTD pins when read       |                |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _                                                        | _              | _               | _            | RE2         | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                    | Write Buffer for the upper 5 bits of the Program Counter |                |                 |              |             |               |           | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                  | PEIE                                                     | TOIE           | INTE            | RBIE         | TOIF        | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(6)</sup> | (4)                                                      | RCIF           | TXIF            | SSPIF        | CCP1IF      | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | _                    | _                                                        | _              | _               | _            | -           | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg          | ister for the I                                          | _east Signific | ant Byte of the | he 16-bit TM | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg          | ister for the I                                          | Most Signific  | ant Byte of th  | e 16-bit TMF | R1 register |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | _                    | _                                                        | T1CKPS1        | T1CKPS0         | T10SCEN      | T1SYNC      | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod           | lule's registe                                           | r              |                 |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                    | TOUTPS3                                                  | TOUTPS2        | TOUTPS1         | TOUTPS0      | TMR2ON      | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou           | ıs Serial Por                                            | t Receive Bu   | ffer/Transmit   | Register     |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                    | SSPEN          | CKP             | SSPM3        | SSPM2       | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWM                                                | 1 (LSB)        |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWM                                                | 1 (MSB)        |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                    | _                                                        | CCP1X          | CCP1Y           | CCP1M3       | CCP1M2      | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9                                                      | SREN           | CREN            | _            | FERR        | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra            | nsmit Data F                                             | legister       |                 |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red            | ceive Data R                                             | egister        |                 |              |             |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co           | mpare/PWM                                                | 2 (LSB)        |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co           | Capture/Compare/PWM2 (MSB)                               |                |                 |              |             |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | _                    | _                                                        | CCP2X          | CCP2Y           | ССР2М3       | CCP2M2      | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme            | nted                                                     |                |                 |              |             |               |           | _                        | _                                              |

|                      |         |                      |                                                          |                |                 |              |             |               |           |                          |                                                |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

- 5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

- 6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

#### 4.2.2.8 PCON REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control register (PCON) contains a flag bit to allow differentiation between a Power-on Reset to an external MCLR reset or WDT reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN

bit in the Configuration word).

#### FIGURE 4-22: PCON REGISTER FOR PIC16C62/64/65 (ADDRESS 8Eh)

R/W-0 R/W-q U-0 U-0 U-0 U-0 U-0 U-0 POR = Readable bit W = Writable bit bit7 hit0 = Unimplemented bit, read as '0' n = Value at POR reset = value depends on conditions Unimplemented: Read as '0' hit 7-2. bit 1: POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) bit 0: Reserved This bit should be set upon a Power-on Reset by user software and maintained as set. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.

### FIGURE 4-23: PCON REGISTER FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 (ADDRESS 8Eh)

| U-0                                                                                                                                                              | U-0                                         | U-0         | U-0         | U-0        | U-0         | R/W-0       | R/W-q       |                                                                                                              |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------|-------------|------------|-------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------|--|--|

| _                                                                                                                                                                | _                                           | _           | _           | -          | _           | POR         | BOR         | R = Readable bit                                                                                             |  |  |

| bit7                                                                                                                                                             |                                             |             |             |            |             |             | bit0        | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset q = value depends on conditions |  |  |

| bit 7-2:                                                                                                                                                         | Unimplem                                    | ented: Rea  | ıd as '0'   |            |             |             |             |                                                                                                              |  |  |

| bit 1:                                                                                                                                                           | <b>POR</b> : Power 1 = No Power 0 = A Power | ver-on Rese | et occurred | must be se | in software | after a Pow | er-on Reset | occurs)                                                                                                      |  |  |

| bit 0: BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred  0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |                                             |             |             |            |             |             |             |                                                                                                              |  |  |

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that the PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

```

ORG 0x500

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

BCF PCLATH,4 ;Only on >4K devices

CALL SUB1_P1 ;Call subroutine in

;;page 1 (800h-FFFh)

;

ORG 0x900

SUB1_P1: ;called subroutine

;;page 1 (800h-FFFh)

;

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

```

### 4.5 Indirect Addressing, INDF and FSR Registers

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-25.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

#### **EXAMPLE 4-2: INDIRECT ADDRESSING**

```

movlw 0x20

;initialize pointer

movwf FSR

; to RAM

NEXT

clrf

INDF

;clear INDF register

FSR,F

incf

;inc pointer

btfss FSR,4

;all done?

;NO, clear next

goto NEXT

CONTINUE

;YES, continue

```

### FIGURE 4-25: DIRECT/INDIRECT ADDRESSING

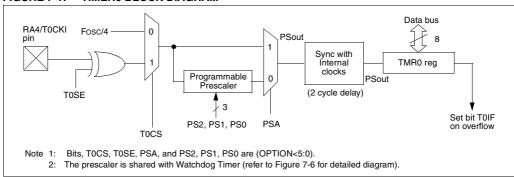

#### 7.0 TIMERO MODULE

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- · 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

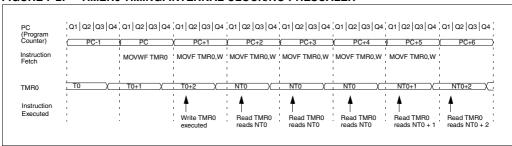

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE

(OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

### 7.1 TMR0 Interrupt

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the TImer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 7-4 displays the Timer0 interrupt timing.

#### FIGURE 7-1: TIMERO BLOCK DIAGRAM

### FIGURE 7-2: TIMERO TIMING: INTERNAL CLOCK/NO PRESCALER

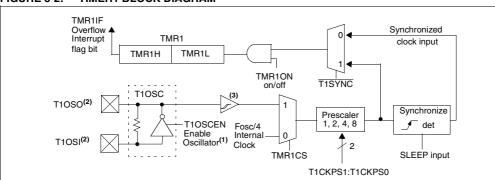

#### 8.1 <u>Timer1 Operation in Timer Mode</u>

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer mode is selected by clearing bit TMR1CS (T1CON<1>). In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

### 8.2 <u>Timer1 Operation in Synchronized</u> Counter Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on T1OSI when enable bit T1OSCEN is set or pin with T1CKI when bit T1OSCEN is cleared.

Note:

The T1OSI function is multiplexed to different pins, depending on the device. See the pinout descriptions to see which pin has the T1OSI function.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if an external clock is present, since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

### 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to appropriate electrical specification section, parameters 45, 46, and 47

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to applicable electrical specification section, parameters 40, 42, 45, 46, and 47.

#### FIGURE 8-2: TIMER1 BLOCK DIAGRAM

- Note 1: When enable bit T1OSCEN is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

- 2: See pinouts for pins with T1OSO and T1OSI functions.

- 3: For the PIC16C62/64/65, the Schmitt Trigger is not implemented in external clock mode.

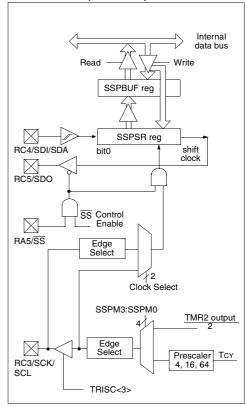

### 11.2.1 OPERATION OF SSP MODULE IN SPI MODE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- · Serial Data Out (SDO)

- · Serial Data In (SDI)

- · Serial Clock (SCK)

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>). These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- · Slave Mode (SCK is the clock input)

- Clock Polarity (Output/Input data on the Rising/ Falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full bit, BF (SSPSTAT<0>) and flag bit SSPIF are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>) will be set. User software must clear bit WCOL so that it can be determined if the following write(s) to the SSPBUF completed successfully. When the application software is expecting to receive valid data, the SSPBUF register should be read before the next byte of data to transfer is written to the SSPBUF register. The Buffer Full bit BF (SSPSTAT<0>) indicates when the SSPBUF register has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF register must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-1 shows the loading of the SSPBUF (SSPSR) register for data transmission. The shaded instruction is only required if the received data is meaningful.

### EXAMPLE 11-1: LOADING THE SSPBUF (SSPSR) REGISTER

|    |     | BSF   | STATUS,  | RP0 | ;Specify Bank 1   |

|----|-----|-------|----------|-----|-------------------|

| L( | OOP | BTFSS | SSPSTAT, | BF  | ;Has data been    |

|    |     |       |          |     | ;received         |

|    |     |       |          |     | ;(transmit        |

|    |     |       |          |     | ;complete)?       |

|    |     | GOTO  | LOOP     |     | ; No              |

|    |     | BCF   | STATUS,  | RP0 | ;Specify Bank 0   |

|    |     | MOVF  | SSPBUF,  | W   | ;W reg = contents |

|    |     |       |          |     | ;of SSPBUF        |

|    |     | MOVWF | RXDATA   |     | ;Save in user RAM |

|    |     | MOVF  | TXDATA,  | W   | ;W reg = contents |

|    |     |       |          |     | ; of TXDATA       |

|    |     | MOVWF | SSPBUF   |     | ;New data to xmit |

The block diagram of the SSP module, when in SPI mode (Figure 11-3), shows that the SSPSR register is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

### FIGURE 11-3: SSP BLOCK DIAGRAM (SPI MODE)

#### 12.4 <u>USART Synchronous Slave Mode</u>

#### **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Synchronous Slave Mode differs from Master Mode in the fact that the shift clock is supplied externally at the CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, enable bit SREN is a don't care in slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

### PIC16C6X

NOTES:

### 13.2 Oscillator Configurations

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 13.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power CrystalXT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

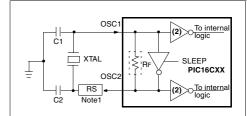

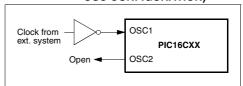

### 13.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In LP, XT, or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 13-4). The PIC16CXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in LP, XT, or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 13-5).

# FIGURE 13-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 13-1, Table 13-3, Table 13-2 and Table 13-4 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- For the PIC16C61 the buffer is on the OSC2 pin, all other devices have the buffer on the OSC1 pin.

## FIGURE 13-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

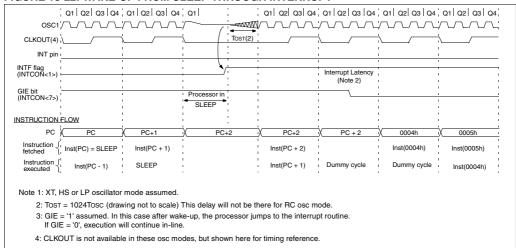

### FIGURE 13-22: WAKE-UP FROM SLEEP THROUGH INTERRUPT

### 13.9 Program Verification/Code Protection

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 13.10 ID Locations

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

### 13.11 <u>In-Circuit Serial Programming</u>

| Αp | Applicable Devices |     |     |    |     |    |     |     |    |     |     |    |    |

|----|--------------------|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

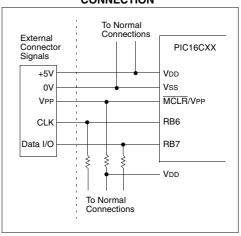

The PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding pins RB6 and RB7 low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device in program/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

FIGURE 13-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

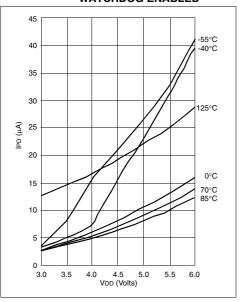

FIGURE 16-8: MAXIMUM IPD vs. VDD WATCHDOG ENABLED\*

\*IPD, with Watchdog Timer enabled, has two components: The leakage current which increases with higher temperature and the operating current of the Watchdog Timer logic which increases with lower temperature. At -40°C, the latter dominates explaining the apparently anomalous behavior.

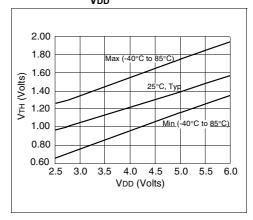

FIGURE 16-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs.

**DC Characteristics:**

18.1

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

TP -----

PIC16C62A/R62/64A/R64-04 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-10 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-20 (Commercial, Industrial, Extended)

|        | ·                                                                | Standar<br>Operatir |         |         |     |       | unless otherwise stated)<br>≤ TA ≤ +125°C for extended,     |

|--------|------------------------------------------------------------------|---------------------|---------|---------|-----|-------|-------------------------------------------------------------|

| DC CHA | RACTERISTICS                                                     | Oporatii            | ig tomp | oratare |     |       | ≤ TA ≤ +85°C for industrial and                             |

|        |                                                                  |                     |         |         | 0°0 |       | < TA < +70°C for commercial                                 |

| Param  | Characteristic                                                   | Sym                 | Min     | Turnst  |     | Units | Conditions                                                  |

| No.    | Characteristic                                                   | Sylli               | IVIIII  | Тур†    | wax | Units | Conditions                                                  |

| D001   | Supply Voltage                                                   | VDD                 | 4.0     | -       | 6.0 | V     | XT, RC and LP osc configuration                             |

| D001A  |                                                                  |                     | 4.5     | -       | 5.5 | V     | HS osc configuration                                        |

| D002*  | RAM Data Retention<br>Voltage (Note 1)                           | VDR                 | -       | 1.5     | -   | V     |                                                             |

| D003   | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                | -       | Vss     | -   | V     | See section on Power-on Reset for details                   |

| D004*  | VDD rise rate to ensure internal Power-on Reset signal           | SVDD                | 0.05    | -       | -   | V/ms  | See section on Power-on Reset for details                   |

| D005   | Brown-out Reset Voltage                                          | BVDD                | 3.7     | 4.0     | 4.3 | V     | BODEN bit in configuration word enabled                     |

|        |                                                                  |                     | 3.7     | 4.0     | 4.4 | V     | Extended Range Only                                         |

| D010   | Supply Current (Note 2, 5)                                       | IDD                 | -       | 2.7     | 5   | mA    | XT, RC, osc configuration Fosc = 4 MHz, VDD = 5.5V (Note 4) |

| D013   |                                                                  |                     | -       | 10      | 20  | mA    | HS osc configuration Fosc = 20 MHz,<br>VDD = 5.5V           |

| D015*  | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR       | -       | 350     | 425 | μА    | BOR enabled, VDD = 5.0V                                     |

| D020   | Power-down Current (Note                                         | IPD                 | -       | 10.5    | 42  | μА    | VDD = 4.0V, WDT enabled, -40°C to +85°C                     |

| D021   | 3, 5)                                                            |                     | -       | 1.5     | 16  | μA    | VDD = 4.0V, WDT disabled, -0°C to +70°C                     |

| D021A  |                                                                  |                     | -       | 1.5     | 19  | μΑ    | VDD = 4.0V, WDT disabled, -40°C to +85°C                    |

| D021B  |                                                                  |                     | -       | 2.5     | 19  | μА    | VDD = 4.0V, WDT disabled, -40°C to +125°C                   |

| D023*  | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR       | -       | 350     | 425 | μА    | BOR enabled, VDD = 5.0V                                     |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 18.5 <u>Timing Diagrams and Specifications</u>

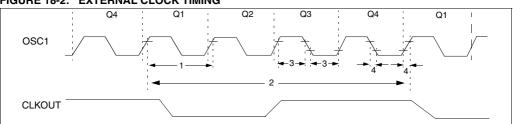

FIGURE 18-2: EXTERNAL CLOCK TIMING

TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         |     |      |        |       |                    |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2                | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  | _   |      | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

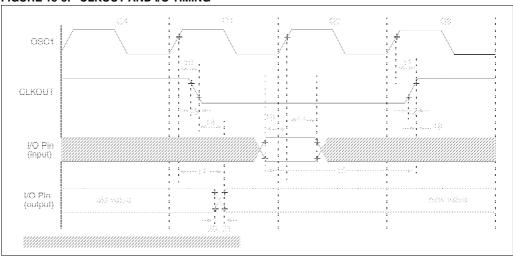

### FIGURE 18-3: CLKOUT AND I/O TIMING

TABLE 18-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameters | Sym      | Characteristic                                                        |                                     | Min        | Typ† | Max         | Units  | Conditions |

|------------|----------|-----------------------------------------------------------------------|-------------------------------------|------------|------|-------------|--------|------------|

| 10*        | TosH2ckL | OSC1↑ to CLKOUT↓                                                      |                                     | _          | 75   | 200         | ns     | Note 1     |

| 11*        | TosH2ckH | OSC1↑ to CLKOUT↑                                                      |                                     | _          | 75   | 200         | ns     | Note 1     |

| 12*        | TckR     | CLKOUT rise time                                                      |                                     | _          | 35   | 100         | ns     | Note 1     |

| 13*        | TckF     | CLKOUT fall time                                                      | _                                   | 35         | 100  | ns          | Note 1 |            |

| 14*        | TckL2ioV | CLKOUT ↓ to Port out valid                                            |                                     | _          | _    | 0.5Tcy + 20 | ns     | Note 1     |

| 15*        | TioV2ckH | Port in valid before CLKOUT ↑                                         |                                     | Tosc + 200 | _    | _           | ns     | Note 1     |

| 16*        | TckH2ioI | Port in hold after CLKOUT ↑                                           |                                     | 0          | -    |             | ns     | Note 1     |

| 17*        | TosH2ioV | OSC1↑ (Q1 cycle) to Port out va                                       | _                                   | 50         | 150  | ns          |        |            |

| 18*        | TosH2ioI | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | 100        |      |             | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | 200        | _    | _           | ns     |            |

| 19*        | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in                         | setup time)                         | 0          | _    | _           | ns     |            |

| 20*        | TioR     | Port output rise time                                                 | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | _          | 10   | 40          | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | _          | _    | 80          | ns     |            |

| 21*        | TioF     | Port output fall time                                                 | PIC16 <b>C</b> 62A/<br>R62/64A/R64  | _          | 10   | 40          | ns     |            |

|            |          |                                                                       | PIC16 <b>LC</b> 62A/<br>R62/64A/R64 | _          | -    | 80          | ns     |            |

| 22††*      | Tinp     | RB0/INT pin high or low time                                          | •                                   | Tcy        | _    | _           | ns     |            |

| 23††*      | Trbp     | RB7:RB4 change int high or low                                        | time                                | Tcy        | _    | _           | ns     |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x TOSC.

### PIC16C6X

1. TppS2ppS

Н

1

L

I<sup>2</sup>C only AA

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 21.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

|         | PPO                                   | 3. 100.81 | (1 C specifications only)              |

|---------|---------------------------------------|-----------|----------------------------------------|

| 2. TppS |                                       | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т       |                                       |           |                                        |

| F       | Frequency                             | Т         | Time                                   |

| Lowerc  | case letters (pp) and their meanings: |           |                                        |

| pp      |                                       |           |                                        |

| СС      | CCP1                                  | osc       | OSC1                                   |

| ck      | CLKOUT                                | rd        | RD                                     |

| cs      | CS                                    | rw        | RD or WR                               |

| di      | SDI                                   | sc        | SCK                                    |

| do      | SDO                                   | SS        | SS                                     |

| dt      | Data in                               | tO        | T0CKI                                  |

| io      | I/O port                              | t1        | T1CKI                                  |

| mc      | MCLR                                  | wr        | WR                                     |

| Upperd  | case letters and their meanings:      |           | ·                                      |

| S       |                                       |           |                                        |

| F       | Fall                                  | Р         | Period                                 |

R

٧

Ζ

High

Low

Rise

Valid

High

Low

Hi-impedance

3 Todist

(I<sup>2</sup>C specifications only)

| BUF    | Bus free                               |

|--------|----------------------------------------|

| Tcc:st | (I <sup>2</sup> C specifications only) |

output access

High

Low

Invalid (Hi-impedance)

| CC  |                 |     |                |

|-----|-----------------|-----|----------------|

| HD  | Hold            | SU  | Setup          |

| ST  |                 |     |                |

| DAT | DATA input hold | STO | STOP condition |

| STA | START condition |     |                |

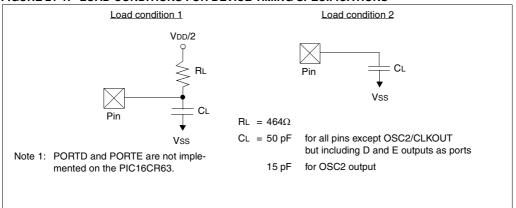

#### FIGURE 21-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

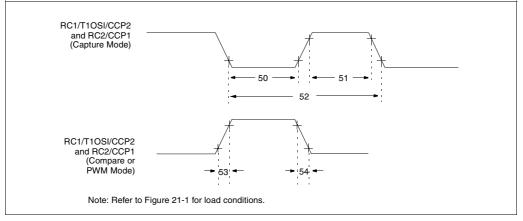

FIGURE 21-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 21-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym                                   | Characteristic                |                 |                         | Min            | Typ† | Max | Units | Conditions                         |

|--------------|---------------------------------------|-------------------------------|-----------------|-------------------------|----------------|------|-----|-------|------------------------------------|

| 50*          | TccL                                  | CCP1 and CCP2                 | No Prescaler    |                         | 0.5Tcy + 20    | _    | _   | ns    |                                    |

|              |                                       | input low time                | With Prescaler  | PIC16 <b>CR</b> 63/R65  | 10             | _    | _   | ns    |                                    |

|              |                                       |                               |                 | PIC16 <b>LCR</b> 63/R65 | 20             | _    | _   | ns    |                                    |

| 51*          | TccH                                  | CCP1 and CCP2 input high time | No Prescaler    |                         | 0.5TCY + 20    | _    | _   | ns    |                                    |

|              |                                       |                               | With Prescaler  | PIC16 <b>CR</b> 63/R65  | 10             | _    | _   | ns    |                                    |

|              |                                       |                               |                 | PIC16 <b>LCR</b> 63/R65 | 20             | _    | _   | ns    |                                    |

| 52*          | TccP                                  | CCP1 and CCP2 in              | put period      |                         | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR                                  | CCP1 and CCP2 of              | utput rise time | PIC16 <b>CR</b> 63/R65  | _              | 10   | 25  | ns    |                                    |

|              |                                       |                               |                 | PIC16 <b>LCR</b> 63/R65 | _              | 25   | 45  | ns    |                                    |

| 54*          | * TccF CCP1 and CCP2 output fall time |                               | utput fall time | PIC16 <b>CR</b> 63/R65  | _              | 10   | 25  | ns    |                                    |

|              |                                       |                               |                 | PIC16 <b>LCR</b> 63/R65 | _              | 25   | 45  | ns    |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

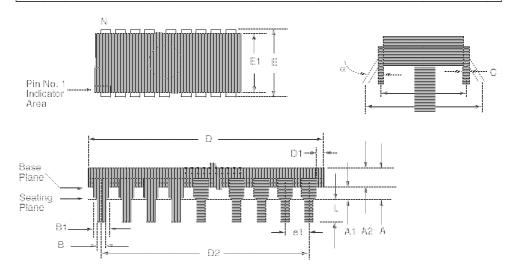

### 24.7 28-Lead Ceramic CERDIP Dual In-line with Window (300 mil)) (JW)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |       |           |        |       |           |  |

|--------------------------------------------------|-------------|-------|-----------|--------|-------|-----------|--|

|                                                  | Millimeters |       |           | Inches |       |           |  |

| Symbol                                           | Min         | Max   | Notes     | Min    | Max   | Notes     |  |

| α                                                | 0°          | 10°   |           | 0°     | 10°   |           |  |

| Α                                                | 3.30        | 5.84  |           | .130   | 0.230 |           |  |

| A1                                               | 0.38        | _     |           | 0.015  | _     |           |  |

| A2                                               | 2.92        | 4.95  |           | 0.115  | 0.195 |           |  |

| В                                                | 0.35        | 0.58  |           | 0.014  | 0.023 |           |  |

| B1                                               | 1.14        | 1.78  | Typical   | 0.045  | 0.070 | Typical   |  |

| С                                                | 0.20        | 0.38  | Typical   | 0.008  | 0.015 | Typical   |  |

| D                                                | 34.54       | 37.72 |           | 1.360  | 1.485 |           |  |

| D2                                               | 32.97       | 33.07 | Reference | 1.298  | 1.302 | Reference |  |

| Е                                                | 7.62        | 8.25  |           | 0.300  | 0.325 |           |  |

| E1                                               | 6.10        | 7.87  |           | 0.240  | 0.310 |           |  |

| е                                                | 2.54        | 2.54  | Typical   | 0.100  | 0.100 | Typical   |  |

| eA                                               | 7.62        | 7.62  | Reference | 0.300  | 0.300 | Reference |  |

| eB                                               | _           | 11.43 |           | _      | 0.450 |           |  |

| L                                                | 2.92        | 5.08  |           | 0.115  | 0.200 |           |  |

| N                                                | 28          | 28    |           | 28     | 28    |           |  |

| D1                                               | 0.13        | _     |           | 0.005  | _     |           |  |

### PIC16C6X

| OSC1/CLKIN                                              |                                                                                                                                                     |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | 16                                                                                                                                                  |

| OSC2/CLKOUT                                             |                                                                                                                                                     |

| PORTA                                                   |                                                                                                                                                     |

| PORTB                                                   |                                                                                                                                                     |

|                                                         |                                                                                                                                                     |

| PORTC                                                   |                                                                                                                                                     |

| PORTD                                                   |                                                                                                                                                     |

| PORTE                                                   | 59                                                                                                                                                  |

| RA4/T0CKI                                               | 16, 52                                                                                                                                              |

| RA5/SS                                                  | 16. 52                                                                                                                                              |

| RB0/INT                                                 |                                                                                                                                                     |

| RB6                                                     |                                                                                                                                                     |

|                                                         |                                                                                                                                                     |

| RB7                                                     |                                                                                                                                                     |

| RC0/T1OSI/T1CKI                                         |                                                                                                                                                     |

| RC0/T1OSO/T1CKI                                         | 16, 55                                                                                                                                              |

| RC1/T1OSI                                               | 55                                                                                                                                                  |

| RC1/T1OSI/CCP2                                          |                                                                                                                                                     |

| RC1/T1OSO                                               |                                                                                                                                                     |

|                                                         |                                                                                                                                                     |

| RC2/CCP1                                                | , ,                                                                                                                                                 |

| RC3/SCK/SCL                                             | 16, 55, 56                                                                                                                                          |

| RC4/SDI/SDA                                             | 16, 55, 56                                                                                                                                          |

| RC5/SDO                                                 | 16, 55, 56                                                                                                                                          |

| RC6/TX/CK                                               |                                                                                                                                                     |

| RC7/RX/DT                                               |                                                                                                                                                     |

|                                                         |                                                                                                                                                     |

| RD7/PSP7:RD0/PSP0                                       |                                                                                                                                                     |

| RE0/RD                                                  |                                                                                                                                                     |

| RE1/WR                                                  |                                                                                                                                                     |

| RE2/CS                                                  | 17, 59, 61                                                                                                                                          |

| SCK                                                     | 86–88                                                                                                                                               |

| SDI                                                     |                                                                                                                                                     |

|                                                         |                                                                                                                                                     |

| SDO                                                     |                                                                                                                                                     |

| SS                                                      |                                                                                                                                                     |

| VDD                                                     | 17                                                                                                                                                  |

| Vss                                                     | 17                                                                                                                                                  |

|                                                         |                                                                                                                                                     |

| PIR1                                                    |                                                                                                                                                     |

| PIR1                                                    | 24, 26, 28, 30, 32, 34                                                                                                                              |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34                                                                                                    |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48                                                                                              |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48<br>47, 131                                                                                   |

| POR Time-Out Sequence on Power                          | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48, 48<br>47, 131<br>er-Up134                                                                   |

| POR Time-Out Sequence on Power                          | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48, 48<br>47, 131<br>er-Up134                                                                   |

| PIR2POPPOR Time-Out Sequence on Power Port RB Interrupt | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>47, 131<br>er-Up134<br>53<br>24, 26, 28, 30, 32, 34, 51                                         |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>47, 131<br>er-Up                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>47, 131<br>er-Up                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48, 47, 131<br>er-Up134<br>53<br>24, 26, 28, 30, 32, 34, 51<br>24, 26, 28, 30, 32, 34, 53<br>38 |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>48, 47, 131<br>er-Up134<br>53<br>24, 26, 28, 30, 32, 34, 51<br>24, 26, 28, 30, 32, 34, 53<br>38 |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>47, 131<br>er-Up                                                                                |

| PIR2                                                    |                                                                                                                                                     |

| PIR2                                                    |                                                                                                                                                     |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>                                                                                                |

| PIR2                                                    | 24, 26, 28, 30, 32, 34<br>24, 26, 28, 30, 32, 34<br>47, 131<br>er-Up                                                                                |

| PIR2                                                    |                                                                                                                                                     |

| Мар                                          |         |

|----------------------------------------------|---------|

| Organization                                 |         |

| Paging                                       |         |

| Section                                      | 19      |

| Programming While In-circuit                 | 142     |

| PS2:PS0                                      |         |

| PSA                                          |         |

| PSPIE                                        | 30      |

|                                              |         |

| PSPIF                                        |         |

| Pull-ups                                     |         |

| PUSH                                         | 48      |

| PWM                                          |         |

| Block Diagram                                | 80      |

| Calculations                                 | 81      |

| Mode                                         | 80      |

| Output Timing                                |         |

| PWM Least Significant bits                   |         |

| WWW Least Significant bits                   | / C     |

| Q                                            |         |

| <del></del>                                  |         |

| Quadrature Clocks                            |         |

| Quick-Turnaround-Production                  | 7       |

| R                                            |         |

| · -                                          |         |