Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc65a-04-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2.2.3 INTCON REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INTCON Register is a readable and writable register which contains the various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts.

#### Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

# FIGURE 4-11: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh 18Bh)

| R/W-0<br>GIE | R/W-0<br>PEIE                                               | R/W-0<br>T0IE      | R/W-0<br>INTE                                | R/W-0<br>RBIE | R/W-0<br>T0IF            | R/W-0<br>INTF | R/W-x<br>RBIF | R = Readable bit                                                                                     |

|--------------|-------------------------------------------------------------|--------------------|----------------------------------------------|---------------|--------------------------|---------------|---------------|------------------------------------------------------------------------------------------------------|

| bit7         | 1 212                                                       | TOLE               | INTE                                         | TIDIL         | 1011                     |               | bit0          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset<br>x = unknown |

| bit 7:       | <b>GIE:</b> <sup>(1)</sup> Glo<br>1 = Enable<br>0 = Disable | s all un-ma        | sked interri                                 |               |                          |               |               |                                                                                                      |

| bit 6:       | PEIE: <sup>(2)</sup> Pe<br>1 = Enable<br>0 = Disable        | s all un-ma        | sked peripl                                  | neral interru | ipts                     |               |               |                                                                                                      |

| bit 5:       |                                                             | s the TMR          | Interrupt E<br>0 overflow ii<br>0 overflow i | nterrupt      |                          |               |               |                                                                                                      |

| bit 4:       | 1 = Enable                                                  | s the RB0/         | nal Interrup<br>INT externa<br>INT externa   |               |                          |               |               |                                                                                                      |

| bit 3:       |                                                             | s the RB p         | e Interrupt<br>ort change<br>ort change      | interrupt     |                          |               |               |                                                                                                      |

| bit 2:       | <b>TOIF:</b> TMR<br>1 = TMR0<br>0 = TMR0                    | register ove       | erflowed (m                                  | ust be clea   | red in softwa            | re)           |               |                                                                                                      |

| bit 1:       |                                                             | 30/INT exte        | rnal interru                                 |               | (must be cle<br>ccur     | ared in soft  | ware)         |                                                                                                      |

| bit 0:       |                                                             | t one of the       | RB7:RB4                                      |               | ed state (see<br>d state | Section 5.2   | to clear the  | interrupt)                                                                                           |

|              | be re-enab<br>description                                   | led by the 1<br>1. | RETFIE ins                                   | truction in t | he user's Inte           | errupt Servi  |               | red, the GIE bit may unintentionally<br>Refer to Section 13.5 for a detailed                         |

|              | The PEIE I                                                  | bit (bit6) is      |                                              |               | PIC16C61, r              |               |               |                                                                                                      |

| globa        |                                                             | GIE (INTC          |                                              |               |                          |               |               | corresponding enable bit or the<br>rupt flag bits are clear prior to                                 |

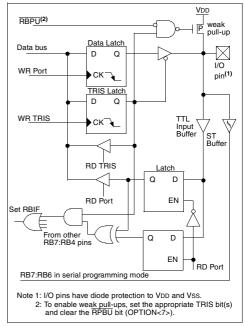

## 5.2 PORTB and TRISB Register

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

## EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are also disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB port change interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, Application Note, *"Implementing Wake-up on Key Stroke"* (AN552).

| Note: | For PIC16C61/62/64/65, if a change on the     |

|-------|-----------------------------------------------|

|       | I/O pin should occur when a read operation    |

|       | is being executed (start of the Q2 cycle),    |

|       | then interrupt flag bit RBIF may not get set. |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RB7:RB4 PINS FOR PIC16C61/62/64/65

## 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u>

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and generate an interrupt on overflow which will wake the processor. However, special precautions in software are needed to read-from or write-to the Timer1 register pair, TMR1L and TMR1H (Section 8.3.2).

In asynchronous counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements, as specified in timing parameters (45 - 47).

#### 8.3.2 READING AND WRITING TMR1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

## EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

| ; | All Int   | errupts  | are  | disabled                |

|---|-----------|----------|------|-------------------------|

|   | MOVF      | TMR1H,   | W    | ;Read high byte         |

|   | MOVWF     | TMPH     |      | ;                       |

|   | MOVF      | TMR1L,   | W    | ;Read low byte          |

|   | MOVWF     | TMPL     |      | ;                       |

|   | MOVF      | TMR1H,   | W    | ;Read high byte         |

|   | SUBWF     | TMPH,    | W    | ;Sub 1st read           |

|   |           |          |      | ;with 2nd read          |

|   | BTFSC     | STATUS   | , Z  | ;is result = 0          |

|   | GOTO      | CONTINU  | JE   | ;Good 16-bit read       |

| ; | TMR1L mag | y have r | olle | d over between the read |

| ; | of the h  | igh and  | low  | bytes. Reading the high |

| ; | and low   | bytes no | w w  | ill read a good value.  |

|   | MOVF      | TMR1H,   | W    | ;Read high byte         |

|   | MOVWF     | TMPH     |      | ;                       |

|   | MOVF      | TMR1L,   | W    | ;Read low byte          |

|   | MOVWF     | TMPL     |      | ;                       |

| ; | Re-enal   | ole Inte | rrup | ot (if required)        |

| C | ONTINUE   |          |      | ;Continue with          |

|   | :         |          |      | ;your code              |

|   |           |          |      |                         |

# 8.4 <u>Timer1 Oscillator</u>

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

A crystal oscillator circuit is built in-between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must allow a software time delay to ensure proper oscillator start-up.

## TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                   | Freq                                                                          | C1                                                 | C2                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| LP                                         | 32 kHz                                                                        | 33 pF                                              | 33 pF                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                                            | 100 kHz                                                                       | 15 pF                                              | 15 pF                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                                            | 200 kHz                                                                       | 15 pF                                              | 15 pF                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| These values are for design guidance only. |                                                                               |                                                    |                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Crystals Tested:                           |                                                                               |                                                    |                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 32.768 kHz                                 | Epson C-00                                                                    | 1R32.768K-A                                        | $\pm$ 20 PPM                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 100 kHz                                    | Epson C-2 1                                                                   | 00.00 KC-P                                         | $\pm$ 20 PPM                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 200 kHz                                    | STD XTL 20                                                                    | 0.000 kHz                                          | $\pm$ 20 PPM                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| of o<br>time<br>2: Sind<br>cha<br>reso     | scillator but al<br>b.<br>ce each reson<br>racteristics, th<br>onator/crystal | lso increases<br>ator/crystal ha<br>le user should | <ul> <li>Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropri-</li> </ul> |  |  |  |  |  |  |  |  |

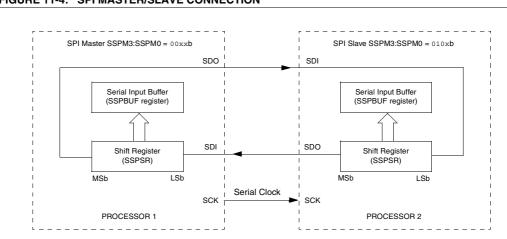

To enable the serial port, SSP enable bit SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear enable bit SSPEN, re-initialize SSPCON register, and then set enable bit SSPEN. This configures the SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if implemented)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

# FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the software protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5 and Figure 11-6 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

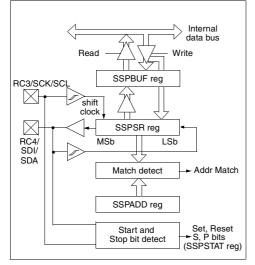

# 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in  $I^2C$  mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

## FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                 | Name                                   | Bit 7                | Bit 6              | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|-------------------------|----------------------------------------|----------------------|--------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                                 | GIE                  | PEIE               | TOIE                   | INTE       | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                     | PIR1                                   | PSPIF <sup>(1)</sup> | (2)                | RCIF                   | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                     | PIE1                                   | PSPIE <sup>(1)</sup> | (2)                | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                     | SSPBUF                                 | Synchrono            | us Serial          | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                     | SSPADD                                 | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                     | SSPCON                                 | WCOL                 | SSPOV              | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                     | SSPSTAT                                | SMP <sup>(3)</sup>   | CKE <sup>(3)</sup> | D/A                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                     | 7h TRISC PORTC Data Direction register |                      |                    |                        |            |            |          |        |        | 1111 1111               | 1111 1111                 |

## TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

3: The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'. NOTES:

-

# TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | e    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        | LSb    |      | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A  | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

|            | ĸ      |                              | · ·    | 11  | TOTO   | ĸĸĸĸ   | кккк | ~        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| SUBWF             | Subtract                                                                   | W from f                     |                                   |                      |

|-------------------|----------------------------------------------------------------------------|------------------------------|-----------------------------------|----------------------|

| Syntax:           | [ label ]                                                                  | SUBWF                        | f,d                               |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$ | ,                            |                                   |                      |

| Operation:        | (f) - (W) $\rightarrow$                                                    | (destina                     | tion)                             |                      |

| Status Affected:  | C, DC, Z                                                                   |                              |                                   |                      |

| Encoding:         | 00                                                                         | 0010                         | dfff                              | ffff                 |

| Description:      | Subtract (2'<br>ister from re<br>stored in the<br>result is sto            | egister 'f'. l<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the        |

| Words:            | 1                                                                          |                              |                                   |                      |

| Cycles:           | 1                                                                          |                              |                                   |                      |

| Q Cycle Activity: | Q1                                                                         | Q2                           | Q3                                | Q4                   |

|                   | Decode                                                                     | Read<br>register 'f'         | Process<br>data                   | Write to destination |

| Example 1:        | SUBWF                                                                      | reg1,1                       |                                   |                      |

|                   | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 3                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | Z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 1                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | nositive             |

|                   | z                                                                          | =                            | 0                                 | poolavo              |

| Example 2:        | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 2                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | Z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 0                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>1; result is                 | 7010                 |

|                   | z                                                                          | =                            | 1                                 | 2010                 |

| Example 3:        | Before Ins                                                                 | truction                     |                                   |                      |

|                   | REG1                                                                       | =                            | 1                                 |                      |

|                   | W<br>C                                                                     | =                            | 2<br>?                            |                      |

|                   | z                                                                          | =                            | ?                                 |                      |

|                   | After Instru                                                               | uction                       |                                   |                      |

|                   | REG1                                                                       | =                            | 0xFF                              |                      |

|                   | W<br>C                                                                     | =                            | 2<br>0; result is                 | negative             |

|                   | z                                                                          | =                            | 0                                 | guivo                |

|                   |                                                                            |                              |                                   |                      |

| SWAPF             | Swap Ni                           | bbles in                                                | f                             |                      |

|-------------------|-----------------------------------|---------------------------------------------------------|-------------------------------|----------------------|

| Syntax:           | [label]                           | SWAPF 1                                                 | ,d                            |                      |

| Operands:         | $0 \le f \le 12$<br>$d \in [0,1]$ | 27                                                      |                               |                      |

| Operation:        | · · ·                             | ightarrow (destin $ ightarrow$ (destin                  |                               |                      |

| Status Affected:  | None                              |                                                         |                               |                      |

| Encoding:         | 0 0                               | 1110                                                    | dfff                          | ffff                 |

| Description:      | 'f' are excl<br>placed in '       | r and lower<br>nanged. If<br>W register.<br>in register | 'd' is 0 the<br>If 'd' is 1 t | e result is          |

| Words:            | 1                                 |                                                         |                               |                      |

| Cycles:           | 1                                 |                                                         |                               |                      |

| Q Cycle Activity: | Q1                                | Q2                                                      | Q3                            | Q4                   |

|                   | Decode                            | Read<br>register 'f'                                    | Process<br>data               | Write to destination |

| Example           | SWAPF                             | REG,                                                    | 0                             |                      |

|                   | Before In                         | struction                                               |                               |                      |

|                   |                                   | REG1                                                    | = 0x/                         | A5                   |

|                   | After Inst                        | truction                                                |                               |                      |

|                   |                                   | REG1<br>W                                               | = 0x/<br>= 0x5                | .0                   |

| TRIS             | Load TR                                                                                                                                                                             | IS Regis  | ster    |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------|--|--|--|

| Syntax:          | [label]                                                                                                                                                                             | TRIS      | f       |      |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                   |           |         |      |  |  |  |

| Operation:       | $(W) \rightarrow TI$                                                                                                                                                                | RIS regis | ster f; |      |  |  |  |

| Status Affected: | None                                                                                                                                                                                |           |         |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                  | 0000      | 0110    | Offf |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |           |         |      |  |  |  |

| Words:           | 1                                                                                                                                                                                   |           |         |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |           |         |      |  |  |  |

| Example          |                                                                                                                                                                                     |           |         |      |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |           |         |      |  |  |  |

|                  |                                                                                                                                                                                     |           |         |      |  |  |  |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

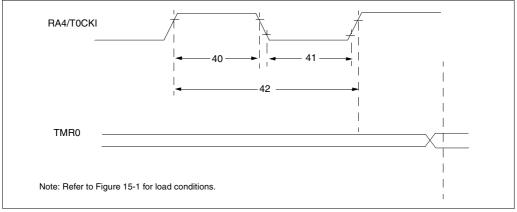

# FIGURE 15-5: TIMER0 EXTERNAL CLOCK TIMINGS

# TABLE 15-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                                             | Тур† | Max | Units | Conditions         |

|------------------|------|------------------------|----------------|-------------------------------------------------|------|-----|-------|--------------------|

| 40*              | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20                                     | _    | _   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | _   | ns    | parameter 42       |

| 41*              | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TCY + 20                                     | —    | —   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | —   | ns    | parameter 42       |

| 42*              | Tt0P | T0CKI Period           | No Prescaler   | TCY + 40                                        | _    | _   |       | N = prescale value |

|                  |      |                        | With Prescaler | Greater of:<br>20 ns or<br><u>Tcy + 40</u><br>N | _    | _   | ns    | (2, 4,, 256)       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

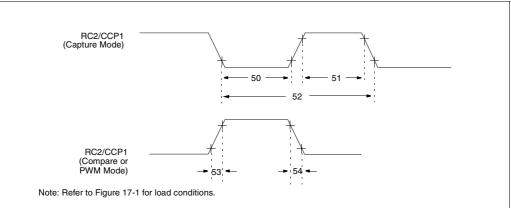

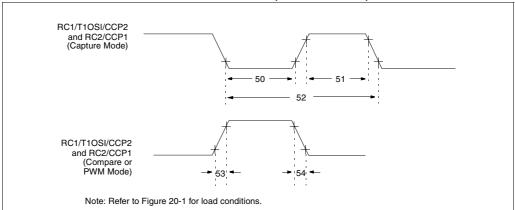

# TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Parameter<br>No. | Sym  | Characteristic        |                |                       | Min                   | Тур† | Max | Units | Conditions                        |

|------------------|------|-----------------------|----------------|-----------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*              | TccL | CCP1                  | No Prescaler   |                       | 0.5TCY + 20           | _    | -   | ns    |                                   |

|                  |      | input low time        | With Prescaler | PIC16 <b>C</b> 62/64  | 10                    | _    |     | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | 20                    | _    | _   | ns    |                                   |

| 51*              | TccH | CCP1                  | No Prescaler   |                       | 0.5Tcy + 20           | _    | _   | ns    |                                   |

|                  |      | input high time       | With Prescaler | PIC16 <b>C</b> 62/64  | 10                    | _    | _   | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | 20                    | _    | _   | ns    |                                   |

| 52*              | TccP | CCP1 input period     |                |                       | <u>3Tcy + 40</u><br>N | -    |     | ns    | N = prescale value<br>(1,4 or 16) |

| 53               | TccR | CCP1 output rise time | 9              | PIC16 <b>C</b> 62/64  | _                     | 10   | 25  | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | _                     | 25   | 45  | ns    |                                   |

| 54               | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 62/64  | _                     | 10   | 25  | ns    |                                   |

|                  |      |                       |                | PIC16LC62/64          | _                     | 25   | 45  | ns    |                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

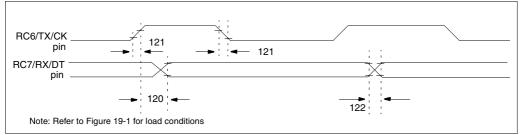

## FIGURE 19-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                    |                    | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------|--------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 65  |     | —    | 80  | ns    |            |

|                  |          | Clock high to data out valid      | PIC16 <b>LC</b> 65 | -   | —    | 100 | ns    |            |

| 121              | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 65  |     | —    | 45  | ns    |            |

|                  |          | (Master Mode)                     | PIC16 <b>LC</b> 65 | -   | —    | 50  | ns    |            |

| 122              | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 65  | _   | —    | 45  | ns    |            |

|                  |          |                                   | PIC16LC65          | _   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

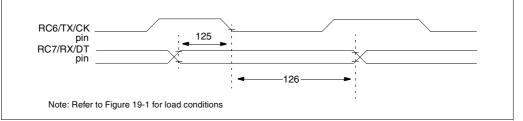

# FIGURE 19-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    |     | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Applicable Devices | 61 | 62 | 62A | <b>B62</b> | 63 | <b>B63</b> | 64 | 64A | <b>R64</b> | 65 | 65A | <b>B65</b> | 66 | 67 |

|--------------------|----|----|-----|------------|----|------------|----|-----|------------|----|-----|------------|----|----|

|                    |    |    |     |            |    |            |    |     |            |    |     |            |    |    |

|       |                                              | Standa              | rd Operat | ing C | ondition | s (unle | ss otherwise stated)                                                    |

|-------|----------------------------------------------|---------------------|-----------|-------|----------|---------|-------------------------------------------------------------------------|

|       |                                              | Operatir            | ng temper | ature | -40°     | Ć≤T     | $A \le +125^{\circ}C$ for extended,                                     |

|       | RACTERISTICS                                 |                     |           |       | -40°     | C ≤T    | $A \le +85^{\circ}C$ for industrial and                                 |

|       | RACIERISTICS                                 |                     |           |       | 0°C      | ≤ 1     | $A \le +70^{\circ}C$ for commercial                                     |

|       |                                              | Operatir<br>Section | • •       | Vdd   | range as | describ | ed in DC spec Section 20.1 and                                          |

| Param | Characteristic                               | Sym                 | Min       | Тур   | Max      | Units   | Conditions                                                              |

| No.   |                                              |                     |           | †     |          |         |                                                                         |

|       | Output High Voltage                          |                     |           |       |          |         |                                                                         |

| D090  | I/O ports (Note 3)                           | Vон                 | VDD-0.7   | -     | -        | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D090A |                                              |                     | VDD-0.7   | -     | -        | V       | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092  | OSC2/CLKOUT (RC osc config)                  |                     | VDD-0.7   | -     | -        | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D092A |                                              |                     | VDD-0.7   | -     | -        | V       | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D150* | Open-Drain High Voltage                      | Vod                 | -         | -     | 14       | V       | RA4 pin                                                                 |

|       | Capacitive Loading Specs on Out-<br>put Pins |                     |           |       |          |         |                                                                         |

| D100  | OSC2 pin                                     | Cosc <sub>2</sub>   | -         | -     | 15       | pF      | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101  | All I/O pins and OSC2 (in RC mode)           | Cio                 | -         | -     | 50       | pF      |                                                                         |

| D102  | SCL, SDA in I <sup>2</sup> C mode            | Cb                  | -         | -     | 400      | pF      |                                                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

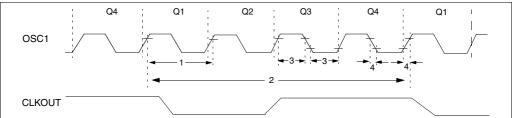

# 20.5 <u>Timing Diagrams and Specifications</u>

# FIGURE 20-2: EXTERNAL CLOCK TIMING

# TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|--------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKIN Frequency         | DC  | I    | 4      | MHz   | XT and RC osc mode |

|              |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|              |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|              |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|              |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|              |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|              |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|              |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|              |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1            | Tosc  | External CLKIN Period            | 250 |      | —      | ns    | XT and RC osc mode |

|              |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|              |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode        |

|              |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|              |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3*           | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|              | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|              |       |                                  | 15  | —    | —      | ns    | HS oscillator      |

| 4*           | TosR, | External Clock in (OSC1) Rise or | —   | _    | 25     | ns    | XT oscillator      |

|              | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|              |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

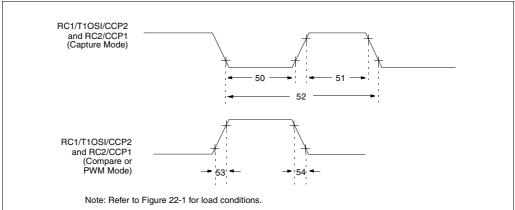

# FIGURE 20-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 20-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym  | Characteristic   |                 |                        | Min                   | Тур† | Max | Units | Conditions                         |

|------------------|------|------------------|-----------------|------------------------|-----------------------|------|-----|-------|------------------------------------|

| 50*              | TccL | CCP1 and CCP2    | No Prescaler    |                        | 0.5Tcy + 20           | _    | _   | ns    |                                    |

|                  |      | input low time   | With Prescaler  | PIC16 <b>C</b> 63/65A  | 10                    | —    |     | ns    |                                    |

|                  |      |                  |                 | PIC16LC63/65A          | 20                    | —    |     | ns    |                                    |

| 51*              | TccH | CCP1 and CCP2    | No Prescaler    |                        | 0.5TCY + 20           | -    |     | ns    |                                    |

|                  |      | input high time  | With Prescaler  | PIC16 <b>C</b> 63/65A  | 10                    | —    |     | ns    |                                    |

|                  |      |                  |                 | PIC16 <b>LC</b> 63/65A | 20                    | -    |     | ns    |                                    |

| 52*              | TccP | CCP1 and CCP2 ir | nput period     |                        | <u>3Tcy + 40</u><br>N |      |     | ns    | N = prescale value<br>(1,4, or 16) |

| 53*              | TccR | CCP1 and CCP2 of | utput rise time | PIC16 <b>C</b> 63/65A  | _                     | 10   | 25  | ns    |                                    |

|                  |      |                  |                 | PIC16 <b>LC</b> 63/65A | _                     | 25   | 45  | ns    |                                    |

| 54*              | TccF | CCP1 and CCP2 o  | utput fall time | PIC16 <b>C</b> 63/65A  | —                     | 10   | 25  | ns    |                                    |

|                  |      |                  |                 | PIC16 <b>LC</b> 63/65A | _                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# 21.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                     | 3. Tcc:st  | (I <sup>2</sup> C specifications only)                                    |

|-----------------------|----------------------------------------|------------|---------------------------------------------------------------------------|

| 2. TppS               |                                        | 4. Ts      | (I <sup>2</sup> C specifications only)                                    |

| т                     |                                        |            |                                                                           |

| F                     | Frequency                              | Т          | Time                                                                      |

| Lowerca               | ase letters (pp) and their meanings:   | L          |                                                                           |

| рр                    |                                        |            |                                                                           |

| сс                    | CCP1                                   | osc        | OSC1                                                                      |

| ck                    | CLKOUT                                 | rd         | RD                                                                        |

| cs                    | CS                                     | rw         | RD or WR                                                                  |

| di                    | SDI                                    | sc         | SCK                                                                       |

| do                    | SDO                                    | ss         | SS                                                                        |

| dt                    | Data in                                | tO         | TOCKI                                                                     |

| io                    | I/O port                               | t1         | T1CKI                                                                     |

| mc                    | MCLR                                   | wr         | WR                                                                        |

| Upperca               | ase letters and their meanings:        |            |                                                                           |

| S                     | -                                      |            |                                                                           |

| F                     | Fall                                   | Р          | Period                                                                    |

| н                     | High                                   | R          | Rise                                                                      |

| I                     | Invalid (Hi-impedance)                 | v          | Valid                                                                     |

| L                     | Low                                    | z          | Hi-impedance                                                              |

| I <sup>2</sup> C only |                                        |            |                                                                           |

| AA                    | output access                          | High       | High                                                                      |

| BUF                   | Bus free                               | Low        | Low                                                                       |

|                       | (I <sup>2</sup> C specifications only) | 2011       |                                                                           |

| CC                    |                                        |            |                                                                           |

| HD                    | Hold                                   | SU         | Setup                                                                     |

| ST                    | Tiold                                  | 30         | Selup                                                                     |

| DAT                   | DATA input hold                        | STO        | STOP condition                                                            |

| STA                   | START condition                        | 310        |                                                                           |

| 1                     |                                        |            |                                                                           |

| FIGURE 2              | 21-1: LOAD CONDITIONS FOR DEVIC        | E TIMING S | PECIFICATIONS                                                             |

|                       | Load condition 1                       |            | Load condition 2                                                          |

|                       | VDD/2                                  |            |                                                                           |

|                       | φ                                      | Γ          |                                                                           |

|                       | 2                                      |            |                                                                           |

|                       | $\geq$ RL                              | F          | Pin CL                                                                    |

|                       |                                        |            | •                                                                         |

|                       |                                        |            | Vss                                                                       |

|                       |                                        | RL = 464Ω  |                                                                           |

|                       | •                                      |            |                                                                           |

|                       | Vss                                    | •          | for all pins except OSC2/CLKOUT<br>but including D and E outputs as ports |

| Note 1:               | PORTD and PORTE are not imple-         |            |                                                                           |

|                       | mented on the PIC16CR63.               | 15 pF      | for OSC2 output                                                           |

|                       |                                        |            |                                                                           |

|                       |                                        |            |                                                                           |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# FIGURE 22-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 22-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym  | Characteristic   |                 |                      | Min                   | Тур† | Max | Units | Conditions                         |

|------------------|------|------------------|-----------------|----------------------|-----------------------|------|-----|-------|------------------------------------|

| 50*              | TccL | CCP1 and CCP2    | No Prescaler    |                      | 0.5TCY + 20           | —    | _   | ns    |                                    |

|                  |      | input low time   | With Prescaler  | PIC16 <b>C</b> 66/67 | 10                    | _    |     | ns    |                                    |

|                  |      |                  |                 | PIC16LC66/67         | 20                    | —    |     | ns    |                                    |

| 51*              | TccH | CCP1 and CCP2    | No Prescaler    |                      | 0.5TCY + 20           | -    |     | ns    |                                    |

|                  |      | input high time  | With Prescaler  | PIC16 <b>C</b> 66/67 | 10                    | —    |     | ns    |                                    |