Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc65a-04i-p |

# PIC16C6X

#### **Table Of Contents**

| 1.0 General Description                                                     | 5   |

|-----------------------------------------------------------------------------|-----|

| 2.0 PIC16C6X Device Varieties                                               | 7   |

| 3.0 Architectural Overview                                                  | c   |

| 4.0 Memory Organization                                                     |     |

| 5.0 I/O Ports                                                               | 51  |

| 6.0 Overview of Timer Modules                                               | 63  |

| 7.0 Timer0 Module                                                           | 65  |

| 8.0 Timer1 Module                                                           | 71  |

| 9.0 Timer2 Module                                                           | 75  |

| 10.0 Capture/Compare/PWM (CCP) Module(s)                                    | 77  |

| 11.0 Synchronous Serial Port (SSP) Module                                   | 83  |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | 105 |

| 13.0 Special Features of the CPU                                            | 123 |

| 14.0 Instruction Set Summary                                                | 143 |

| 15.0 Development Support                                                    | 159 |

| 16.0 Electrical Characteristics for PIC16C61                                | 163 |

| 17.0 DC and AC Characteristics Graphs and Tables for PIC16C61               | 173 |

| 18.0 Electrical Characteristics for PIC16C62/64                             | 183 |

| 19.0 Electrical Characteristics for PIC16C62A/R62/64A/R64                   | 199 |

| 20.0 Electrical Characteristics for PIC16C65                                | 215 |

| 21.0 Electrical Characteristics for PIC16C63/65A                            | 231 |

| 22.0 Electrical Characteristics for PIC16CR63/R65                           | 247 |

| 23.0 Electrical Characteristics for PIC16C66/67                             | 263 |

| 24.0 DC and AC Characteristics Graphs and Tables for:                       |     |

| PIC16C62, PIC16C62A, PIC16CR62, PIC16C63, PIC16C64, PIC16C64A, PIC16CR64,   |     |

| PIC16C65A, PIC16C66, PIC16C67                                               | 281 |

| 25.0 Packaging Information                                                  | 291 |

| Appendix A: Modifications                                                   | 307 |

| Appendix B: Compatibility                                                   |     |

| Appendix C: What's New                                                      |     |

| Appendix D: What's Changed                                                  | 308 |

| Appendix E: PIC16/17 Microcontrollers                                       |     |

| Pin Compatibility                                                           |     |

| Index                                                                       |     |

| List of Equation and Examples                                               |     |

| List of Figures                                                             |     |

| List of Tables                                                              |     |

| Reader Response                                                             |     |

| PIC16C6X Product Identification System                                      | 335 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. For example, the legend below shows that some features of only the PIC16C62A, PIC16CR62, PIC16C63, PIC16C64A, PIC16CR64, and PIC16C65A are described in this section.

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that the PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

# EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

```

ORG 0x500

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

BCF PCLATH,4 ;Only on >4K devices

CALL SUB1_P1 ;Call subroutine in

;;page 1 (800h-FFFh)

;

ORG 0x900

SUB1_P1: ;called subroutine

;;page 1 (800h-FFFh)

;

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

```

# 4.5 Indirect Addressing, INDF and FSR Registers

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

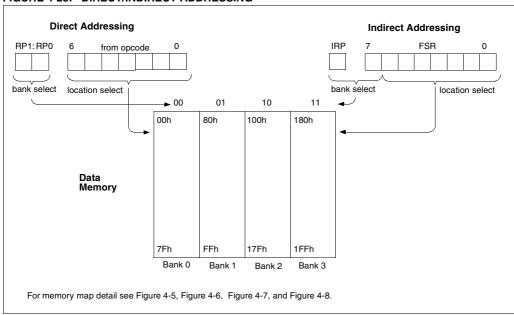

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-25.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

### **EXAMPLE 4-2: INDIRECT ADDRESSING**

```

movlw 0x20

;initialize pointer

movwf FSR

; to RAM

NEXT

clrf

INDF

;clear INDF register

FSR,F

incf

;inc pointer

btfss FSR,4

;all done?

;NO, clear next

goto NEXT

CONTINUE

;YES, continue

```

# FIGURE 4-25: DIRECT/INDIRECT ADDRESSING

# 5.3 PORTC and TRISC Register

# Applicable Devices 61|62|62A|R62|63|R63|64|64A|R64|65|65A|R65|66|67

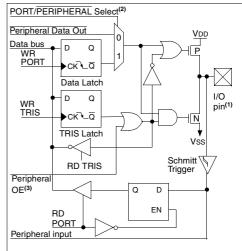

PORTC is an 8-bit wide bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### **EXAMPLE 5-3: INITIALIZING PORTC**

```

BCF

STATUS, RPO ;

BCF

STATUS, RP1 ; PIC16C66/67 only

; Initialize PORTC by

CLRE

PORTC

; clearing output

; data latches

BSF

STATUS, RPO ; Select Bank 1

; Value used to

MOVILW

0xCF

; initialize data

: direction

MOVWF TRISC

; Set RC<3:0> as inputs

; RC<5:4> as outputs

; RC<7:6> as inputs

```

## FIGURE 5-6: PORTC BLOCK DIAGRAM

- Note 1: I/O pins have diode protection to VDD and Vss.

- Port/Peripheral select signal selects between port data and peripheral output.

- Peripheral OE (output enable) is only activated if peripheral select is active.

TABLE 5-5: PORTC FUNCTIONS FOR PIC16C62/64

| Name            | Bit# | Buffer Type | Function                                                                              |

|-----------------|------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSI/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator input or Timer1 clock input                |

| RC1/T1OSO       | bit1 | ST          | Input/output port pin or Timer1 oscillator output                                     |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                   |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       |

| RC5/SDO         | bit5 | ST          | Input/output port pin or synchronous serial port data output                          |

| RC6             | bit6 | ST          | Input/output port pin                                                                 |

| RC7             | bit7 | ST          | Input/output port pin                                                                 |

Legend: ST = Schmitt Trigger input

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must

# **EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)**

be followed even if the WDT is disabled.

Lines 2 and 3 do NOT have to be included if the final desired prescale value is other than 1:1. If 1:1 is final desired value, then a temporary prescale value is set in lines 2 and 3 and the final prescale value will be set in lines 10 and 11.

```

1) BSF

STATUS, RPO

MOVLW b'xx0x0xxx'

;Select clock source and prescale value of

3) MOVWF OPTION REG

;other than 1:1

STATUS, RPO

BCF

;Bank 0

5)

;Clear TMR0 and prescaler

CLRF

TMR0

BSF

STATUS, RP1

;Bank 1

7)

MOVLW b'xxxx1xxx'

;Select WDT, do not change prescale value

8) MOVWF OPTION REG

9) CLRWDT

;Clears WDT and prescaler

10) MOVLW b'xxxx1xxx'

;Select new prescale value and WDT

11) MOVWF OPTION REG

STATUS, RPO

:Bank 0

12) BCF

```

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

### **EXAMPLE 7-2:** CHANGING PRESCALER (WDT→TIMER0)

```

CLRWDT ;Clear WDT and prescaler

BSF STATUS, RPO ;Bank 1

MOVLW b'xxxx0xxx';Select TMRO, new prescale value and clock source

MOVWF OPTION_REG ;

BCF STATUS, RPO ;Bank 0

```

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name   | Bit 7  | Bit 6               | Bit 5                                        | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|---------------------|----------------------------------------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h, 101h             | TMR0   | Timer0 | module's r          | egister                                      |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE <sup>(1)</sup> | TOIE                                         | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h, 181h             | OPTION | RBPU   | INTEDG              | T0CS                                         | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | _      | _                   | PORTA Data Direction Register <sup>(1)</sup> |       |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

Note 1: TRISA<5> and bit PEIE are not implemented on the PIC16C61, read as '0'.

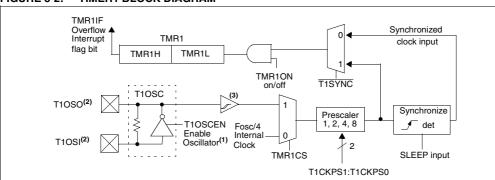

### 8.1 <u>Timer1 Operation in Timer Mode</u>

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer mode is selected by clearing bit TMR1CS (T1CON<1>). In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

# 8.2 <u>Timer1 Operation in Synchronized</u> Counter Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on T1OSI when enable bit T1OSCEN is set or pin with T1CKI when bit T1OSCEN is cleared.

Note:

The T1OSI function is multiplexed to different pins, depending on the device. See the pinout descriptions to see which pin has the T1OSI function.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if an external clock is present, since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

# 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to appropriate electrical specification section, parameters 45, 46, and 47

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to applicable electrical specification section, parameters 40, 42, 45, 46, and 47.

## FIGURE 8-2: TIMER1 BLOCK DIAGRAM

- Note 1: When enable bit T1OSCEN is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

- 2: See pinouts for pins with T1OSO and T1OSI functions.

- 3: For the PIC16C62/64/65, the Schmitt Trigger is not implemented in external clock mode.

# 9.0 TIMER2 MODULE

## **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

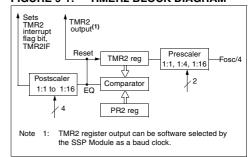

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

### 9.2 Output of TMR2

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

## FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

#### U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 = Readable bit W = Writable bit hit7 U = Unimplemented bit, read as '0' - n = Value at POR reset bit 7: Unimplemented: Read as '0' TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits 0000 = 1:1 postscale 0001 = 1:2 postscale 1111 = 1:16 postscale bit 2: TMR2ON: Timer2 On bit 1 = Timer2 is on 0 = Timer2 is off bit 1-0: T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits 00 = 1:1 prescale 01 = 1:4 prescale 1x = 1:16 prescale

# 12.1 USART Baud Rate Generator (BRG)

| Αp | pli | cable | e Dev | vice | es  |    |     |     |    |     |     |    |    |

|----|-----|-------|-------|------|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62  | 62A   | R62   | 63   | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

# EXAMPLE 12-1: CALCULATING BAUD RATE FRROR

Desired Baud rate = Fosc / (64 (X + 1))

9600 = 16000000 / (64 (X + 1)) $X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X+1)) equation can reduce the baud rate error in some cases.

Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------|-----------|-----------|-----------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9       | TXEN      | SYNC      | -     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9       | SREN      | CREN      | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| 99h     | SPBRG | Baud Rat | te Genera | 0000 0000 | 0000 0000 |       |       |       |       |                         |                                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

Steps to follow when setting up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                        | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>PO<br>BC | R,   | Valu<br>all o<br>Res |      |

|---------|-------|------------------------------|-----------|---------|-------|-------|--------|--------|--------|-------------------|------|----------------------|------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>         | (2)       | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000              | 0000 | 0000                 | 0000 |

| 18h     | RCSTA | SPEN                         | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000              | -00x | 0000                 | -00x |

| 1Ah     | RCREG | USART R                      | eceive Re | egister |       |       |        |        |        | 0000              | 0000 | 0000                 | 0000 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>         | (2)       | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000              | 0000 | 0000                 | 0000 |

| 98h     | TXSTA | CSRC                         | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000              | -010 | 0000                 | -010 |

| 99h     | SPBRG | Baud Rate Generator Register |           |         |       |       |        |        |        | 0000              | 0000 | 0000                 | 0000 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: PSPIE and PSPIF are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)                          | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9                          | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra            | ansmit Re                    | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)                          | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9                          | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |                         | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Master Transmission.

Note 1: PSPIE and PSPIF are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

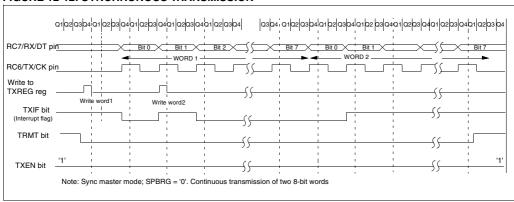

### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

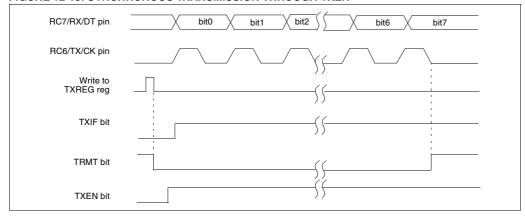

# FIGURE 12-13: SYNCHRONOUS TRANSMISSION THROUGH TXEN

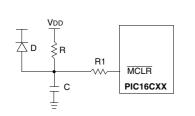

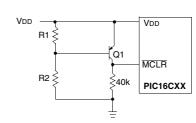

# FIGURE 13-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the devices electrical specifications.

- R1 = 100Ω to 1 kΩ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrostatic Overstress (EOS).

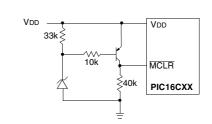

# FIGURE 13-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

# FIGURE 13-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- Internal brown-out detection on the PIC16C62A/R62/63/R63/64A/R64/65A/ R65/66/67 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistors.

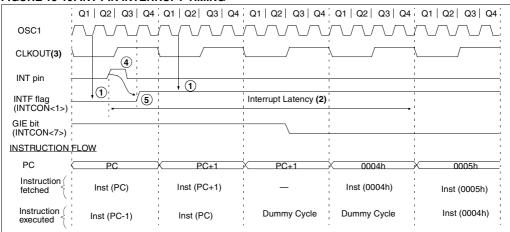

#### 13.5.1 INT INTERRUPT

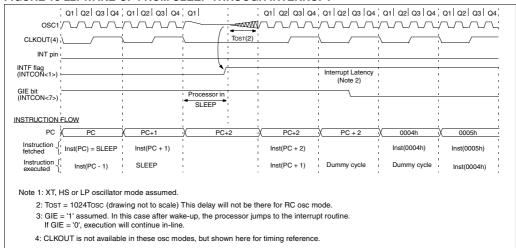

External interrupt on RB0/INT pin is edge triggered: either rising if edge select bit INTEDG (OPTION<6>) is set, or falling, if bit INTEDG is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP, if enable bit INTE was set prior to going into SLEEP. The status of global enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 13.8 for details on SLEEP mode.

#### 13.5.2 TMR0 INTERRUPT

Note:

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0).

#### 13.5.3 PORTB INTERRUPT ON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 5.2).

For the PIC16C61/62/64/65, if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then flag bit RBIF may not get set.

#### FIGURE 13-19: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3TCY for synchronous interrupt and 3-4TCY for asynchronous interrupt. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC oscillator mode.

- 4: For minimum width spec of INT pulse, refer to AC specs.

- 5: INTF can to be set anytime during the Q4-Q1 cycles.

# FIGURE 13-22: WAKE-UP FROM SLEEP THROUGH INTERRUPT

# 13.9 Program Verification/Code Protection

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

### 13.10 ID Locations

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

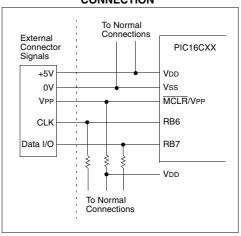

# 13.11 <u>In-Circuit Serial Programming</u>

| Αp | Applicable Devices |     |     |    |     |    |     |     |    |     |     |    |    |

|----|--------------------|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding pins RB6 and RB7 low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device in program/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

FIGURE 13-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

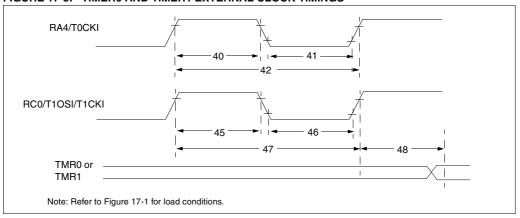

FIGURE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 17-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic        | Min               | Typ†               | Max                                | Units | Conditions |    |                                    |

|--------------|-----------|-----------------------|-------------------|--------------------|------------------------------------|-------|------------|----|------------------------------------|

|              |           |                       |                   | L                  |                                    |       |            |    |                                    |

| 40*          | Tt0H      | T0CKI High Pulse V    | Vidth             | No Prescaler       | 0.5Tcy + 20                        | _     | _          | ns | Must also meet                     |

|              |           |                       |                   | With Prescaler     | 10                                 | l —   | _          | ns | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse Width |                   | No Prescaler       | 0.5Tcy + 20                        | _     | _          | ns | Must also meet                     |

|              |           |                       |                   | With Prescaler     | 10                                 | _     | _          | ns | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period          |                   | No Prescaler       | Tcy + 40                           | _     | _          | ns |                                    |

|              |           |                       |                   | With Prescaler     |                                    | _     | _          | ns | N = prescale value                 |

|              |           |                       |                   |                    | 20 or TCY + 40                     |       |            |    | (2, 4,, 256)                       |

|              |           |                       |                   |                    | N                                  |       |            |    |                                    |

| 45*          | Tt1H      | T1CKI High Time       | Synchronous, P    |                    | 0.5Tcy + 20                        | _     | _          | ns | Must also meet                     |

|              |           |                       | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _     | _          | ns | parameter 47                       |

|              |           |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _     | _          | ns |                                    |

|              |           |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _     | _          | ns |                                    |

|              |           |                       |                   | PIC16 <b>LC</b> 6X | 50                                 | _     | _          | ns |                                    |

| 46*          | Tt1L      | T1CKI Low Time        | Synchronous, P    | rescaler = 1       | 0.5TCY + 20                        | _     | _          | ns | Must also meet                     |

|              |           |                       | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                 | _     | _          | ns | parameter 47                       |

|              |           |                       | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                 | _     |            | ns |                                    |

|              |           |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                 | _     | _          | ns |                                    |

|              |           |                       |                   | PIC16 <b>LC</b> 6X | 50                                 | _     | -          | ns |                                    |

| 47*          | Tt1P      | T1CKI input period    | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N | _     | _          | ns | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                       |                   | PIC16 <b>LC</b> 6X | Greater of:<br>50 OR TCY + 40<br>N |       |            |    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                       | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                 | _     | _          | ns |                                    |

|              |           |                       |                   | PIC16 <b>LC</b> 6X | 100                                | _     | _          | ns |                                    |

|              | Ft1       | Timer1 oscillator inp |                   | DC                 | _                                  | 200   | kHz        |    |                                    |

|              |           | (oscillator enabled b | , ,               |                    |                                    |       |            |    |                                    |

| 48           | TCKEZtmr1 | Delay from external   | •                 |                    | 2Tosc                              | _     | 7Tosc      | -  |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C62A/R62/64A/R64

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                     | 55°C to +125°C |

|--------------------------------------------------------------------|----------------|

| Storage temperature                                                | 65°C to +150°C |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) |                |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V  |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +14V     |

| Voltage on RA4 with respect to Vss                                 | 0V to +14V     |

| Total power dissipation (Note 1)                                   | 1.0W           |

| Maximum current out of Vss pin                                     |                |

| Maximum current into VDD pin                                       | 250 mA         |

| Input clamp current, IiK (VI < 0 or VI > VDD)                      | ±20 mA         |

| Output clamp current, loκ (Vo < 0 or Vo > VDD)                     | ±20 mA         |

| Maximum output current sunk by any I/O pin                         | 25 mA          |

| Maximum output current sourced by any I/O pin                      | 25 mA          |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined)         | 200 mA         |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined)      | 200 mA         |

| Maximum current sunk by PORTC and PORTD (combined)                 | 200 mA         |

| Maximum current sourced by PORTC and PORTD (combined)              | 200 mA         |

Note 1: Power dissipation is calculated as follows: Pdis = VDD  $x \{IDD - \sum IOH\} + \sum \{(VDD-VOH) \ x \ IOH\} + \sum (VOI \ x \ IOL) \}$

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62A-04<br>PIC16CR62-04<br>PIC16C64A-04<br>PIC16CR64-04                                                | PIC16C62A-10<br>PIC16CR62-10<br>PIC16C64A-10<br>PIC16CR64-10                            | PIC16C62A-20<br>PIC16CR62-20<br>PIC16C64A-20<br>PIC16CR64-20                                  | PIC16LC62A-04<br>PIC16LCR62-04<br>PIC16LC64A-04<br>PIC16LCR64-04                                        | JW Devices                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                     | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max. | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max.       | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 µA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                 |

| XT  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max. | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 $\mu$ A typ. at 4V Freq: 4 MHz max.       | VDD: 2.5V to 6.0V IDD: 3.8 mA max. at 3.0V IPD: $5 \mu A$ max. at 3.0V Freq: 4 MHz max.                 | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              |                                                                                         | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use in HS mode                                                                      | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.           |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                      | Not recommended for use in LP mode                                                            | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

DC CHARACTERISTICS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

20.3 DC Characteristics: PIC16C63/65A-04 (Commercial, Industrial, Extended)

PIC16C63/65A-10 (Commercial, Industrial, Extended)

PIC16C63/65A-20 (Commercial, Industrial, Extended)

PIC16LC63/65A-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for extended,

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C < TA < +70°C for commercial

Operating voltage VDD range as described in DC spec Section 20.1 and

Section 20.2

| Section 20.2                            |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                                      |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Characteristic                          | Sym                                                                                                                                                                                                                                                                                                                                                                               | Min                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | Max                                  | Units                                  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                         | †                          |                                      |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Input Low Voltage                       |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                                      |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| I/O ports                               | VIL                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                                      |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| with TTL buffer                         |                                                                                                                                                                                                                                                                                                                                                                                   | Vss                                                                                                                                                                                                                                                                                                                                                                                                                     | -                          | 0.15VDD                              | V                                      | For entire VDD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                   | Vss                                                                                                                                                                                                                                                                                                                                                                                                                     | -                          | V8.0                                 | V                                      | $4.5V \le V_{DD} \le 5.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| with Schmitt Trigger buffer             |                                                                                                                                                                                                                                                                                                                                                                                   | Vss                                                                                                                                                                                                                                                                                                                                                                                                                     | -                          | 0.2VDD                               | V                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| MCLR, OSC1 (in RC mode)                 |                                                                                                                                                                                                                                                                                                                                                                                   | Vss                                                                                                                                                                                                                                                                                                                                                                                                                     | -                          | 0.2VDD                               | V                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |