Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc65a-04i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

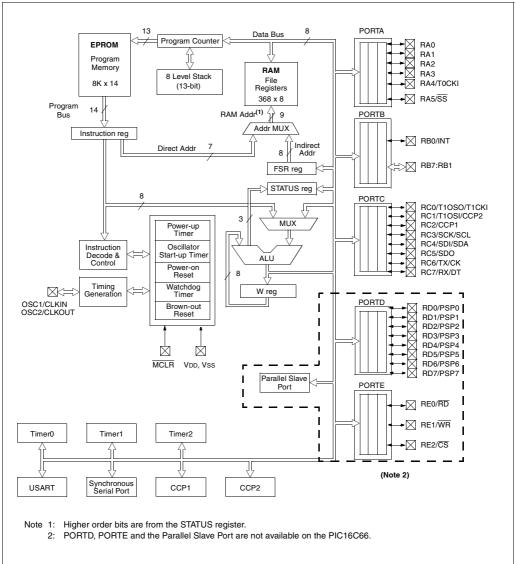

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data may be fetched from the same memory using the same bus. Separating program and data busses further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C61 addresses 1K x 14 of program memory. The PIC16C62/62A/R62/64/64A/R64 address 2K x 14 of program memory, and the PIC16C63/R63/65/65A/R65 devices address 4K x 14 of program memory. The PIC16C66/67 address 8K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of "special optimal situations" makes programming with the PIC16CXX simple yet efficient, thus significantly reducing the learning curve. The PIC16CXX device contains an 8-bit ALU and working register (W). The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending upon the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. Bits C and DC operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

FIGURE 3-4: PIC16C66/67 BLOCK DIAGRAM

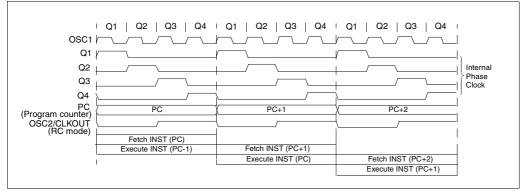

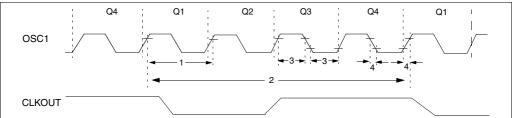

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

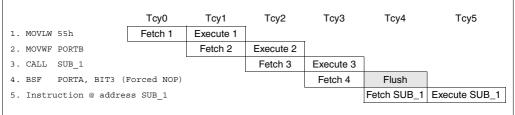

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.2.2.5 PIR1 REGISTER

| Applicable Devices |     |     |    |     |      |             |       |     |       |     |      |     |     |

|--------------------|-----|-----|----|-----|------|-------------|-------|-----|-------|-----|------|-----|-----|

| 61 62              | 62A | R62 | 63 | R63 | 64   | 64 <i>F</i> | R64   | 65  | 65A   | R65 | 5 66 | 67  |     |

| This<br>periph     | 0   |     |    |     | IS 1 | the         | indiv | idu | al fl | ag  | bits | for | the |

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-16: PIR1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 0Ch)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0        | U-0          | R/W-0         | R/W-0  | R/W-0  | R/W-0  |                                                                                       |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|---------------|--------|--------|--------|---------------------------------------------------------------------------------------|--|--|--|

| _        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _          | _            | SSPIF         | CCP1IF | TMR2IF | TMR1IF | R = Readable bit                                                                      |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |              |               |        |        | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |

| bit 7-6: | Reserved:                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Always ma  | aintain thes | e bits clear. |        |        |        | LI                                                                                    |  |  |  |

| bit 5-4: | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ented: Rea | ad as '0'    |               |        |        |        |                                                                                       |  |  |  |

| bit 3:   | <ul> <li>SSPIF: Synchronous Serial Port Interrupt Flag bit</li> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>                                                                                                                                                                                                                                                                       |            |              |               |        |        |        |                                                                                       |  |  |  |

| bit 2:   | CCP1IF: CCP1 Interrupt Flag bit         Capture Mode         1 = A TMR1 register capture occurred (must be cleared in software)         0 = No TMR1 register capture occurred         Compare Mode         1 = A TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred         PWM Mode         Unused in this mode |            |              |               |        |        |        |                                                                                       |  |  |  |

| bit 1:   | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                                                                                                      |            |              |               |        |        |        |                                                                                       |  |  |  |

| bit 0:   | TMR1IF: TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflow occurred (must be cleared in software)<br>0 = No TMR1 register overflow occurred                                                                                                                                                                                                                                                                                                                |            |              |               |        |        |        |                                                                                       |  |  |  |

| globa    | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.                                                                                                                                                                                            |            |              |               |        |        |        |                                                                                       |  |  |  |

#### SWITCHING PRESCALER ASSIGNMENT 7.3.1

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

| Note: | To avoid an unintended device RESET, the |

|-------|------------------------------------------|

|       | following instruction sequence (shown in |

|       | Example 7-1) must be executed when       |

|       | changing the prescaler assignment from   |

|       | Timer0 to the WDT. This precaution must  |

|       | be followed even if the WDT is disabled. |

#### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

|                                                                   | 1)  | BSF    | STATUS, RPO | ;Bank 1                                    |

|-------------------------------------------------------------------|-----|--------|-------------|--------------------------------------------|

| Lines 2 and 3 do NOT have to                                      | 2)  | MOVLW  | b'xx0x0xxx' | ;Select clock source and prescale value of |

| be included if the final desired                                  | 3)  | MOVWF  | OPTION_REG  | ;other than 1:1                            |

| prescale value is other than 1:1.                                 | 4)  | BCF    | STATUS, RPO | ;Bank 0                                    |

| If 1:1 is final desired value, then a temporary prescale value is | 5)  | CLRF   | TMR0        | ;Clear TMR0 and prescaler                  |

| set in lines 2 and 3 and the final                                | 6)  | BSF    | STATUS, RP1 | ;Bank 1                                    |

| prescale value will be set in lines                               | 7)  | MOVLW  | b'xxxx1xxx' | ;Select WDT, do not change prescale value  |

| 10 and 11.                                                        | 8)  | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 9)  | CLRWDT |             | ;Clears WDT and prescaler                  |

|                                                                   | 10) | MOVLW  | b'xxxx1xxx' | ;Select new prescale value and WDT         |

|                                                                   | 11) | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 12) | BCF    | STATUS, RPO | ;Bank 0                                    |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT → TIMER0)

CLRWDT ;Clear WDT and prescaler BSF STATUS, RP0 ;Bank 1 MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and clock source MOVWF OPTION REG ; BCF STATUS, RPO ;Bank 0

#### TABLE 7-1: **REGISTERS ASSOCIATED WITH TIMER0**

| Address               | Name   | Bit 7  | Bit 6               | Bit 5                                        | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|---------------------|----------------------------------------------|-------|-------|-------|-------|---------|--------------------------|---------------------------|

| 01h, 101h             | TMR0   | Timer0 | module's r          | egister                                      |       |       |       |       |         | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE <sup>(1)</sup> | TOIE                                         | INTE  | RBIE  | TOIF  | INTF  | RBIF    | 0000 000x                | 0000 000u                 |

| 81h, 181h             | OPTION | RBPU   | INTEDG              | T0CS                                         | T0SE  | PSA   | PS2   | PS1   | PS0     | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | —      | _                   | PORTA Data Direction Register <sup>(1)</sup> |       |       |       |       | 11 1111 | 11 1111                  |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0 R/W-0 R            | /W-0 R/W-0         | R/W-0        | R/W-0         | R/W-0        |                                       |

|----------|------------------------|--------------------|--------------|---------------|--------------|---------------------------------------|

| —        | - CCPxX CC             | CPxY CCPxM3        | CCPxM2       | CCPxM1        | CCPxM0       | R = Readable bit                      |

| bit7     |                        |                    |              |               | bit0         | W = Writable bit                      |

|          |                        |                    |              |               |              | U = Unimplemented bit, read<br>as '0' |

|          |                        |                    |              |               |              | - n =Value at POR reset               |

| bit 7-6: | Unimplemented: F       | Poad as '0'        |              |               |              |                                       |

|          | •                      |                    |              |               |              |                                       |

| bit 5-4: | CCPxX:CCPxY: PV        | VM Least Significa | ant bits     |               |              |                                       |

|          | Capture Mode<br>Unused |                    |              |               |              |                                       |

|          | Compare Mode           |                    |              |               |              |                                       |

|          | Unused                 |                    |              |               |              |                                       |

|          | PWM Mode               |                    |              |               |              |                                       |

|          | These bits are the t   | wo LSbs of the P   | NM duty cy   | cle. The eig  | ht MSbs are  | found in CCPRxL.                      |

| bit 3-0: | CCPxM3:CCPxM0          | : CCPx Mode Sele   | ect bits     |               |              |                                       |

|          | 0000 = Capture/Co      | •                  |              | k module)     |              |                                       |

|          | 0100 = Capture mo      |                    | •            |               |              |                                       |

|          | 0101 = Capture mo      |                    | •            |               |              |                                       |

|          | 0110 = Capture mo      | · ·                | 0 0          |               |              |                                       |

|          | 1000 = Compare m       | · ·                | • •          | CCPxIF is     | set)         |                                       |

|          | 1001 = Compare m       |                    | •            |               | ,            |                                       |

|          | •                      |                    | •            |               | ,            | is set, CCPx pin is unaffected)       |

|          | •                      |                    | al event (CC | PxIF bit is s | et; CCP1 res | ets TMR1; CCP2 resets TMR1)           |

|          | 11xx = PWM mode        | 9                  |              |               |              |                                       |

|          |                        |                    |              |               |              |                                       |

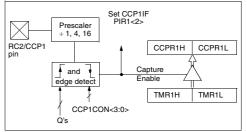

#### 10.1 Capture Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an   |

|-------|-------------------------------------------|

|       | output, a write to PORTC can cause a cap- |

|       | ture condition.                           |

### FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work consistently.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture event is changed, a false capture interrupt may be generated. The user should clear enable bit CCP1IE (PIE1<2>) to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

| TABLE 13-9: | STATUS BITS AND THEIR SIGNIFICANCE FOR     |

|-------------|--------------------------------------------|

|             | PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67 |

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |

| 0   | x   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

Legend: x = unknown, u = unchanged

#### TABLE 13-10: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C61/62/64/65

|                                    | Program Counter       | STATUS    | PCON <sup>(2)</sup> |

|------------------------------------|-----------------------|-----------|---------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0 -                 |

| MCLR reset during normal operation | 000h                  | 000u uuuu | u-                  |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | u-                  |

| WDT Reset                          | 000h                  | 0000 luuu | u-                  |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | u-                  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu | u-                  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

2: The PCON register is not implemented on the PIC16C61.

#### TABLE 13-11: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

|                                    | Program Counter       | STATUS    | PCON |

|------------------------------------|-----------------------|-----------|------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0x   |

| MCLR reset during normal operation | 000h                  | 000u uuuu | uu   |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | uu   |

| WDT Reset                          | 000h                  | 0000 luuu | uu   |

| Brown-out Reset                    | 000h                  | 0001 luuu | u0   |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | uu   |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | uu   |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

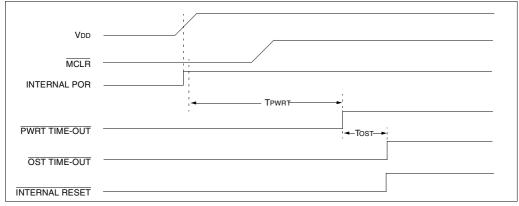

#### FIGURE 13-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

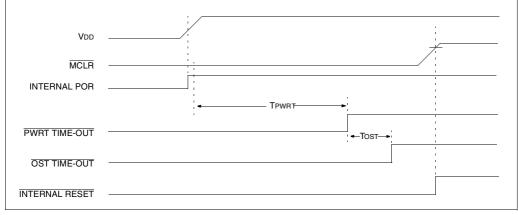

#### FIGURE 13-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

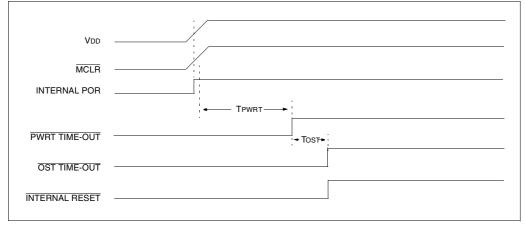

#### FIGURE 13-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

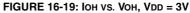

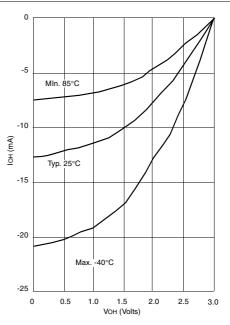

FIGURE 16-20: IOH VS. VOH, VDD = 5V

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

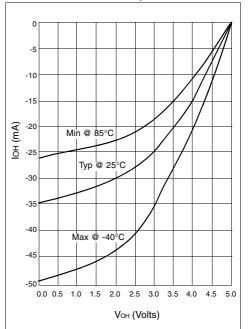

#### TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Parameter<br>No. | Sym  | Characteristic        |                |                       | Min                   | Тур† | Max | Units | Conditions                        |

|------------------|------|-----------------------|----------------|-----------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*              |      |                       | No Prescaler   |                       | 0.5TCY + 20           | _    | -   | ns    |                                   |

|                  |      | input low time        | With Prescaler | PIC16 <b>C</b> 62/64  | 10                    | _    |     | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | 20                    | _    | _   | ns    |                                   |

| 51*              | TccH | CCP1                  | No Prescaler   |                       | 0.5Tcy + 20           | _    | _   | ns    |                                   |

|                  |      | input high time       | With Prescaler | PIC16 <b>C</b> 62/64  | 10                    | _    | _   | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | 20                    | _    | _   | ns    |                                   |

| 52*              | TccP | CCP1 input period     |                |                       | <u>3Tcy + 40</u><br>N | -    | -   | ns    | N = prescale value<br>(1,4 or 16) |

| 53               | TccR | CCP1 output rise time | 9              | PIC16 <b>C</b> 62/64  | _                     | 10   | 25  | ns    |                                   |

|                  |      |                       |                | PIC16 <b>LC</b> 62/64 | _                     | 25   | 45  | ns    |                                   |

| 54               | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 62/64  | _                     | 10   | 25  | ns    |                                   |

|                  |      |                       |                | PIC16LC62/64          | _                     | 25   | 45  | ns    |                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

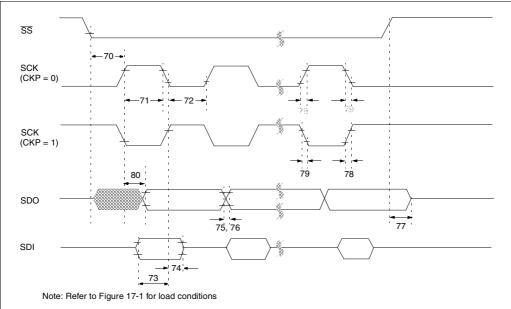

#### TABLE 17-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input  | Тсү      | —    | —   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | —    | —   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | —   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                |          | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                |          | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)       |          | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)       | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 18.3 DC Characteristics: PIC16C62A/R62/64A/R64-04 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-10 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-20 (Commercial, Industrial, Extended) PIC16LC62A/R62/64A/R64-04 (Commercial, Industrial)

| DC CH        | ARACTERISTICS                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |          |         |       |                                                 |  |  |  |

|--------------|------------------------------------|------------------------------------------------------|---------|----------|---------|-------|-------------------------------------------------|--|--|--|

| Param<br>No. | Characteristic                     | Sym                                                  | Min     | тур<br>† | Мах     | Units | Conditions                                      |  |  |  |

| 110.         | Input Low Voltage                  |                                                      |         |          |         |       |                                                 |  |  |  |

|              | I/O ports                          | VIL                                                  |         |          |         |       |                                                 |  |  |  |

| D030         | with TTL buffer                    | VIL                                                  | Vss     | -        | 0.15VDD | v     | For entire VDD range                            |  |  |  |

| D030A        |                                    |                                                      | VSS     | _        | 0.13VDD | v     | $4.5V \le VDD \le 5.5V$                         |  |  |  |

| D031         | with Schmitt Trigger buffer        |                                                      | Vss     | -        | 0.2VDD  | v     |                                                 |  |  |  |

| D032         | MCLR, OSC1 (in RC mode)            |                                                      | Vss     | -        | 0.2VDD  | v     |                                                 |  |  |  |

| D033         | OSC1 (in XT, HS and LP)            |                                                      | Vss     | -        | 0.3VDD  | v     | Note1                                           |  |  |  |

|              | Input High Voltage                 |                                                      |         |          |         | -     |                                                 |  |  |  |

|              | I/O ports                          | Viн                                                  |         | -        |         |       |                                                 |  |  |  |

| D040         | with TTL buffer                    |                                                      | 2.0     | -        | VDD     | v     | $4.5V \leq VDD \leq 5.5V$                       |  |  |  |

| D040A        |                                    |                                                      | 0.25VDD | -        | Vdd     | V     | For entire VDD range                            |  |  |  |

|              |                                    |                                                      | + 0.8V  |          |         |       | , , , , , , , , , , , , , , , , , , ,           |  |  |  |

| D041         | with Schmitt Trigger buffer        |                                                      | 0.8VDD  | -        | Vdd     | v     | For entire VDD range                            |  |  |  |

| D042         | MCLR                               |                                                      | 0.8VDD  | -        | Vdd     | V     |                                                 |  |  |  |

| D042A        | OSC1 (XT, HS and LP)               |                                                      | 0.7Vdd  | -        | Vdd     | V     | Note1                                           |  |  |  |

| D043         | OSC1 (in RC mode)                  |                                                      | 0.9Vdd  | -        | Vdd     | V     |                                                 |  |  |  |

| D070         | PORTB weak pull-up current         | <b>I</b> PURB                                        | 50      | 250      | 400     | μA    | VDD = 5V, VPIN = VSS                            |  |  |  |

|              | Input Leakage Current (Notes 2, 3) |                                                      |         |          |         |       |                                                 |  |  |  |

| D060         | I/O ports                          | lı∟                                                  | -       | -        | ±1      | μA    | $Vss \leq VPIN \leq VDD, Pin at hi-impedance$   |  |  |  |

| D061         | MCLR, RA4/T0CKI                    |                                                      | -       | -        | ±5      | μA    | $Vss \leq VPIN \leq VDD$                        |  |  |  |

| D063         | OSC1                               |                                                      | -       | -        | ±5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP       |  |  |  |

|              |                                    |                                                      |         |          |         |       | osc configuration                               |  |  |  |

|              | Output Low Voltage                 |                                                      |         |          |         |       |                                                 |  |  |  |

| D080         | I/O ports                          | Vol                                                  | -       | -        | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C     |  |  |  |

| D080A        |                                    |                                                      | -       | -        | 0.6     | v     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C    |  |  |  |

| D083         | OSC2/CLKOUT (RC osc config)        |                                                      | -       | -        | 0.6     | v     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C     |  |  |  |

| D083A        |                                    |                                                      | -       | -        | 0.6     | v     | IOL = 1.2  mA,  VDD = 4.5 V,<br>-40°C to +125°C |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

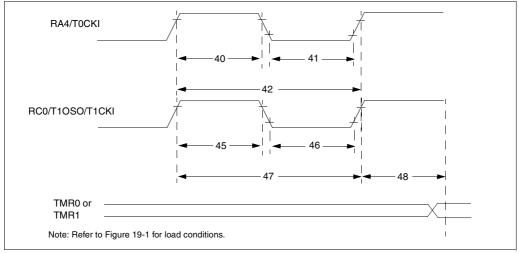

#### FIGURE 19-5: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TABLE 19-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                 |                      |                    | Min                                              | Typ† | Max   | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|----------------------|--------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse V                             | Vidth                | No Prescaler       | 0.5TCY + 20                                      | _    |       | ns    | Must also meet                     |

|              |           |                                                |                      | With Prescaler     | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth                | No Prescaler       | 0.5TCY + 20                                      | _    | —     | ns    | Must also meet                     |

|              |           |                                                |                      | With Prescaler     | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                      | No Prescaler       | TCY + 40                                         | —    | —     | ns    |                                    |

|              |           |                                                |                      | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, F       | Prescaler = 1      | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |

|              |           | 0                                              | Synchronous,         | PIC16 <b>C</b> 6X  | 15                                               | _    | _     | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 6X | 25                                               | -    | —     | ns    | -                                  |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 30                                               | —    | -     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 50                                               | —    | -     | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, F       | Prescaler = 1      | 0.5TCY + 20                                      | _    | —     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,         | PIC16 <b>C</b> 6X  | 15                                               | —    | —     | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 6X | 25                                               | -    | —     | ns    |                                    |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 30                                               | _    | —     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 50                                               | -    | —     | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous          | PIC16 <b>C</b> 6X  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 60                                               | _    | —     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 100                                              | -    | —     | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                      |                    | DC                                               | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                            | clock edge to tir    | ner increment      | 2Tosc                                            | —    | 7Tosc | —     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Applicable Devices | 61 | 62 | 62A | <b>B62</b> | 63 | <b>B63</b> | 64 | 64A | <b>R64</b> | 65 | 65A | <b>B65</b> | 66 | 67 |

|--------------------|----|----|-----|------------|----|------------|----|-----|------------|----|-----|------------|----|----|

|                    |    |    |     |            |    |            |    |     |            |    |     |            |    |    |

|       |                                              | Standa                                                                            | rd Operat | ing C | ondition | s (unle | ss otherwise stated)                                                    |  |  |  |

|-------|----------------------------------------------|-----------------------------------------------------------------------------------|-----------|-------|----------|---------|-------------------------------------------------------------------------|--|--|--|

|       |                                              | Operatir                                                                          | ng temper | ature | -40°     | Ć≤T     | $A \le +125^{\circ}C$ for extended,                                     |  |  |  |

|       | RACTERISTICS                                 |                                                                                   |           |       | -40°     | C ≤T    | $A \le +85^{\circ}C$ for industrial and                                 |  |  |  |

|       | RACIERISTICS                                 |                                                                                   |           |       | 0°C      | ≤ 1     | $A \le +70^{\circ}C$ for commercial                                     |  |  |  |

|       |                                              | Operating voltage VDD range as described in DC spec Section 20.1 and Section 20.2 |           |       |          |         |                                                                         |  |  |  |

| Param | Characteristic                               | Sym                                                                               | Min       | Тур   | Max      | Units   | Conditions                                                              |  |  |  |

| No.   |                                              |                                                                                   |           | †     |          |         |                                                                         |  |  |  |

|       | Output High Voltage                          |                                                                                   |           |       |          |         |                                                                         |  |  |  |

| D090  | I/O ports (Note 3)                           | Vон                                                                               | VDD-0.7   | -     | -        | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D090A |                                              |                                                                                   | VDD-0.7   | -     | -        | V       | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)                  |                                                                                   | VDD-0.7   | -     | -        | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D092A |                                              |                                                                                   | VDD-0.7   | -     | -        | V       | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D150* | Open-Drain High Voltage                      | Vod                                                                               | -         | -     | 14       | V       | RA4 pin                                                                 |  |  |  |

|       | Capacitive Loading Specs on Out-<br>put Pins |                                                                                   |           |       |          |         |                                                                         |  |  |  |

| D100  | OSC2 pin                                     | Cosc <sub>2</sub>                                                                 | -         | -     | 15       | pF      | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101  | All I/O pins and OSC2 (in RC mode)           | Cio                                                                               | -         | -     | 50       | pF      |                                                                         |  |  |  |

| D102  | SCL, SDA in I <sup>2</sup> C mode            | Cb                                                                                | -         | -     | 400      | pF      |                                                                         |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 20.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 20-2: EXTERNAL CLOCK TIMING

#### TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|--------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKIN Frequency         | DC  | I    | 4      | MHz   | XT and RC osc mode |

|              |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|              |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|              |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|              |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|              |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|              |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|              |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|              |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1            | Tosc  | External CLKIN Period            | 250 |      | —      | ns    | XT and RC osc mode |

|              |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|              |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode        |

|              |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|              |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3*           | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|              | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|              |       |                                  | 15  | —    | —      | ns    | HS oscillator      |

| 4*           | TosR, | External Clock in (OSC1) Rise or | —   | _    | 25     | ns    | XT oscillator      |

|              | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|              |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 21.0 ELECTRICAL CHARACTERISTICS FOR PIC16CR63/R65

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                                                                                                | 55°C to +125°C         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Ambient temperature under bias<br>Storage temperature                                                                                                                         | 65°C to +150°C         |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                                                            |                        |

| Voltage on VDD with respect to VSS                                                                                                                                            | -0.3V to +7.5V         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                  | 0V to +14V             |

| Voltage on RA4 with respect to Vss                                                                                                                                            | 0V to +14V             |

| Total power dissipation (Note 1)                                                                                                                                              |                        |

| Maximum current out of Vss pin                                                                                                                                                |                        |

| Maximum current into VDD pin                                                                                                                                                  |                        |

| Maximum current into VDD pin<br>Input clamp current, Iiκ (VI < 0 or VI > VDD)<br>Output clamp current, Ioκ (VO < 0 or VO > VDD)<br>Maximum output current sunk by any I/O pin | ±20 mA                 |

| Output clamp current, Iok (Vo < 0 or Vo > VDD)                                                                                                                                | ±20 mA                 |

| Maximum output current sunk by any I/O pin                                                                                                                                    |                        |

| Maximum output current sourced by any I/O pin                                                                                                                                 |                        |

| Maximum current sunk by PORTA, PORTB, and PORTE (Note 3) (combined)                                                                                                           |                        |

| Maximum current sourced by PORTA, PORTB, and PORTE (Note 3) (combined)                                                                                                        |                        |

| Maximum current sunk by PORTC and PORTD (Note 3) (combined)                                                                                                                   | $\sim 200 \mathrm{mA}$ |

| Maximum current sourced by PORTC and PORTD (Note 3) (combined)                                                                                                                |                        |

| Note 1. Dever discipation is calculated as follows: Ddia VDD x (100 X 100)                                                                                                    |                        |

- **Note 1:** Power dissipation is calculated as follows: Pdis =  $VDx \{IDD \SigmaIOH\} + \Sigma (VDD VOH) \times IOH\} + \Sigma (VOI \times IOL)$

- Note 2: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "fow" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE not available on the P(C16CR63.

† NOTICE: Stresses above those listed under "Absolute Maximum Patings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 21-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16CR63-04<br>PIC16CR65-04                                                                                | PIC16CR63-10<br>PIC16CR65-10                                                                | PIC16CR63-20<br>PIC16CR65-20                                                                | PIC16LCR63-04<br>PIC16LCR65-04                                                                          | JW Devices                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  |                                                                                                             | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IRD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 3.0V to 5.5V<br>IDD: 3.8 mA max. at 3V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| ХТ  | VDD: 4.0V to 5:5V<br>IDP: -5 mA max. at 5.5V<br>IPD: -16 µA max. at 4V<br>Freq: 4 MHz max                   | Vod: 4.5V to 5.5V<br>Idd: 2.7 mA typ. at 5.5V<br>IPd: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 3.0V to 5.5V<br>IDD: 3.8 mA max. at 3V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at<br>5.5V                                                           | VDD: 4.5V to 5.5V<br>IDD: 10 mA max. at 5.5V                                                | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V                                                | Not recommended for use in HS mode                                                                      | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at<br>5.5V                                                         |

|     | IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.                                                                | IPD 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max.                                                | IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.                                               |                                                                                                         | IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.                                                           |

| LP  | VDD: 4.0V to 5.5V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for<br>use in LP mode                                                       | Not recommended for<br>use in LP mode                                                       | VDD: 3.0V to 5.5V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 5.5V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

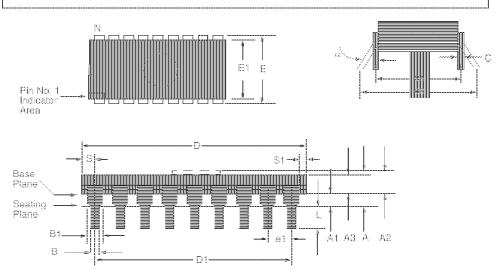

#### 24.6 18-Lead Ceramic CERDIP Dual In-line with Window (300 mil) (JW)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Pa     | ckage Group: ( | Ceramic CERDIP | Dual In-Line (C | DP)   |           |  |  |

|--------|--------|----------------|----------------|-----------------|-------|-----------|--|--|

|        |        | Millimeters    |                | Inches          |       |           |  |  |

| Symbol | Min    | Max            | Notes          | Min             | Max   | Notes     |  |  |

| α      | 0°     | 10°            |                | 0°              | 10°   |           |  |  |

| А      | _      | 5.080          |                | _               | 0.200 |           |  |  |

| A1     | 0.381  | 1.778          |                | 0.015           | 0.070 |           |  |  |

| A2     | 3.810  | 4.699          |                | 0.150           | 0.185 |           |  |  |

| A3     | 3.810  | 4.445          |                | 0.150           | 0.175 |           |  |  |

| В      | 0.355  | 0.585          |                | 0.014           | 0.023 |           |  |  |

| B1     | 1.270  | 1.651          | Typical        | 0.050           | 0.065 | Typical   |  |  |

| С      | 0.203  | 0.381          | Typical        | 0.008           | 0.015 | Typical   |  |  |

| D      | 22.352 | 23.622         |                | 0.880           | 0.930 |           |  |  |

| D1     | 20.320 | 20.320         | Reference      | 0.800           | 0.800 | Reference |  |  |

| E      | 7.620  | 8.382          |                | 0.300           | 0.330 |           |  |  |

| E1     | 5.588  | 7.874          |                | 0.220           | 0.310 |           |  |  |

| e1     | 2.540  | 2.540          | Reference      | 0.100           | 0.100 | Reference |  |  |

| eA     | 7.366  | 8.128          | Typical        | 0.290           | 0.320 | Typical   |  |  |

| eB     | 7.620  | 10.160         |                | 0.300           | 0.400 |           |  |  |

| L      | 3.175  | 3.810          |                | 0.125           | 0.150 |           |  |  |

| Ν      | 18     | 18             |                | 18              | 18    |           |  |  |

| S      | 0.508  | 1.397          |                | 0.020           | 0.055 |           |  |  |

| S1     | 0.381  | 1.270          |                | 0.015           | 0.050 |           |  |  |

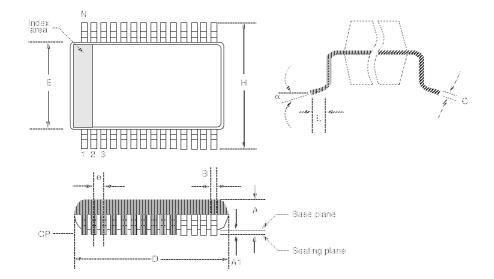

### 24.10 28-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        |        | Packag      | e Group: Plasti | c SSOP |        |           |

|--------|--------|-------------|-----------------|--------|--------|-----------|

|        |        | Millimeters |                 |        | Inches |           |

| Symbol | Min    | Max         | Notes           | Min    | Max    | Notes     |

| α      | 0°     | 8°          |                 | 0°     | 8°     |           |

| А      | 1.730  | 1.990       |                 | 0.068  | 0.078  |           |

| A1     | 0.050  | 0.210       |                 | 0.002  | 0.008  |           |

| В      | 0.250  | 0.380       |                 | 0.010  | 0.015  |           |

| С      | 0.130  | 0.220       |                 | 0.005  | 0.009  |           |

| D      | 10.070 | 10.330      |                 | 0.396  | 0.407  |           |

| E      | 5.200  | 5.380       |                 | 0.205  | 0.212  |           |

| е      | 0.650  | 0.650       | Reference       | 0.026  | 0.026  | Reference |

| Н      | 7.650  | 7.900       |                 | 0.301  | 0.311  |           |

| L      | 0.550  | 0.950       |                 | 0.022  | 0.037  |           |

| Ν      | 28     | 28          |                 | 28     | 28     |           |

| CP     | -      | 0.102       |                 | -      | 0.004  |           |

-----

### APPENDIX F: PIC16/17 MICROCONTROLLERS

#### F.1 PIC12CXXX Family of Devices

|            |                                         | PIC12C508       | PIC12C509       | PIC12C671       | PIC12C672       |

|------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|

| lock       | Maximum Frequency<br>of Operation (MHz) | 4               | 4               | 4               | 4               |

| emory      | EPROM Program Memory                    | 512 x 12        | 1024 x 12       | 1024 x 14       | 2048 x 14       |

| emory      | Data Memory (bytes)                     | 25              | 41              | 128             | 128             |

|            | Timer Module(s)                         | TMR0            | TMR0            | TMR0            | TMR0            |

| eripherals | A/D Converter (8-bit) Channels          |                 | _               | 4               | 4               |

|            | Wake-up from SLEEP on<br>pin change     | Yes             | Yes             | Yes             | Yes             |

|            | I/O Pins                                | 5               | 5               | 5               | 5               |

|            | Input Pins                              | 1               | 1               | 1               | 1               |

| atures     | Internal Pull-ups                       | Yes             | Yes             | Yes             | Yes             |

|            | Voltage Range (Volts)                   | 2.5-5.5         | 2.5-5.5         | 2.5-5.5         | 2.5-5.5         |

|            | In-Circuit Serial Programming           | Yes             | Yes             | Yes             | Yes             |

|            | Number of Instructions                  | 33              | 33              | 35              | 35              |

|            | Packages                                | 8-pin DIP, SOIC | 8-pin DIP, SOIC | 8-pin DIP, SOIC | 8-pin DIP, SOIC |

All PIC12C5XX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC12C5XX devices use serial programming with data pin GP1 and clock pin GP0.

#### F.2 PIC14C000 Family of Devices

|             |                                                 | PIC14C000                                                                                                                                                                       |

|-------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                                                                                                                                                              |

| Memory      | EPROM Program Memory (x14 words)                | 4K                                                                                                                                                                              |

|             | Data Memory (bytes)                             | 192                                                                                                                                                                             |

|             | Timer Module(s)                                 | TMR0<br>ADTMR                                                                                                                                                                   |

| Peripherals | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | I <sup>2</sup> C with SMBus<br>Support                                                                                                                                          |

| Features    | Slope A/D Converter Channels                    | 8 External; 6 Internal                                                                                                                                                          |

|             | Interrupt Sources                               | 11                                                                                                                                                                              |

|             | I/O Pins                                        | 22                                                                                                                                                                              |

|             | Voltage Range (Volts)                           | 2.7-6.0                                                                                                                                                                         |

|             | In-Circuit Serial Programming                   | Yes                                                                                                                                                                             |

|             | Additional On-chip Features                     | Internal 4MHz Oscillator, Bandgap Reference,Temperature Sensor,<br>Calibration Factors, Low Voltage Detector, SLEEP, HIBERNATE,<br>Comparators with Programmable References (2) |

|             | Packages                                        | 28-pin DIP (.300 mil), SOIC, SSOP                                                                                                                                               |

### Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tei: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068