Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc65at-04-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams PDIP, SOIC, Windowed CERDIP SDIP, SOIC, SSOP, Windowed CERDIP (300 mil) 18 → RA1 MCI R/Vpp RA3 ← 2 RA4/T0CKI ← 3 RA0 ← □ 2 27 ☐ → RB6 26 ☐ → RB5 17 → RA0 RA1 **←** ► □ 3 16 → OSC1/CLKIN 25 □ → RB4 MCLR/VPP → 4 15 → OSC2/CLKOUT RA3 **→** □ 5 24 ☐ → RB3 Vss --- □ 5 RA4/T0CKI ← □ 6 23 ☐ → RB2 RA5/SS → □ 7 Vss → □ 8 22 ☐ → RB1 21 ☐ → RB0/INT 13 ←→ RB7 RB0/INT ← 6 RB1 **→** 7 12 ←→ RB6 20 - VDD 19 - VSS RB2 → □ 8 11 → RB5 RC0/T1OSI/T1CKI ← ☐ 11 RC1/T1OSO ← ☐ 12 RC2/CCP1 ← ☐ 13 RB3 **→** 9 RB4 16 ☐ ←→ RC5/SDO PIC16C61 RC3/SCK/SCL ← ► □ 14 15 ☐ ←→ RC4/SDI/SDA **PIC16C62** SDIP, SOIC, SSOP, Windowed CERDIP (300 mil) SDIP, SOIC, Windowed CERDIP (300 mil) R/VPP - C RA0 - C RA1 - C RA2 - C MCI B/Vpp -28 ☐ ←→ RB7 MCI B/Vpp -□ ←→ RB6 □ - RB6 RA1 → □ 3 26 ☐ ←→ RB5 26 ☐ ←→ RB5 RA2 <del>▼ ►</del> □ 4 25 ☐ ←→ RB4 4 25 ☐ ←→ RB4 RA3 **→** 5 RA4/T0CKI **→** 6 24 ☐ → RB3 23 ☐ → RB2 24 ☐ → RB3 23 ☐ → RB2 RA5/SS → □ 7 22 ☐ **← ►** RB1 Vss — **-** □ 8 21 □ - RB0/INT OSC1/CLKIN → 9 OSC2/CLKOUT ← 10 10 10 19 ☐ **→** Vss RC0/T1OSO/T1CKI - 11 RC1/T1OSI - 12 RC2/CCP1 - 13 RC0/T1OS0/T1CKI ← □ RC1/T1OSI/CCP2 ← □ 18 ☐ ← ► RC7/RX/DT 17 ☐ → RC6 12 17 ☐ → RC6/TX/CK RC2/CCP1 → ► 16 → BC5/SDO 13 16 - RC5/SDO RC3/SCK/SCL ← ► RC3/SCK/SCL → □ 14 15 T → RC4/SDI/SDA 15 RC4/SDI/SDA PIC16C62A PIC16C63 PIC16CR62 PIC16CR63 **PIC16C66** PDIP, Windowed CERDIP MCLR/Vpp → □ 1 40 1 → BR7 MCLB/Vpp → 1 40 1 → BB7 40 → RB7 39 → RB6 38 → RB5 37 → RB4 39 ☐ <del>< ►</del> RB6 38 ☐ <del>< ►</del> RB5 RA0 <del>▼ ►</del> □ 2 RA1 → □ 3 RA2 <del>▼ ►</del> □ 4 36 ☐ <del>< ►</del> RB3 35 ☐ <del>< ►</del> RB2 BA3 <del>▼ ►</del> □ 5 RA4/T0CKI → □ 6 RA5/SS → □ 7 33 ☐ → ► RB0/INT RE0/RD → □ 8 RE1/WR → □ 9 RE2/CS → □ 10 26 → RC7/RX/DT PIC16C64A PIC16C64 **PIC16C65** PIC16CR64 PIC16C65A

PIC16CR65 PIC16C67

NOTES:

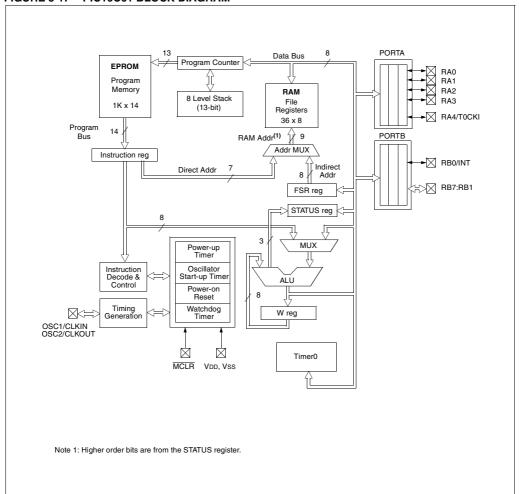

FIGURE 3-1: PIC16C61 BLOCK DIAGRAM

**TABLE 3-3:** PIC16C64/64A/R64/65/65A/R65/67 PINOUT DESCRIPTION

| Pin Name                                      | DIP<br>Pin# | PLCC<br>Pin# | TQFP<br>MQFP<br>Pin# | Pin<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|-----------------------------------------------|-------------|--------------|----------------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN                                    | 13          | 14           | 30                   | ı           | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT                                   | 14          | 15           | 31                   | 0           | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the pin outputs CLK-OUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP                                      | 1           | 2            | 18                   | I/P         | ST                     | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                    |

|                                               |             |              |                      |             |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0                                           | 2           | 3            | 19                   | I/O         | TTL                    |                                                                                                                                                                                                          |

| RA1                                           | 3           | 4            | 20                   | I/O         | TTL                    |                                                                                                                                                                                                          |

| RA2                                           | 4           | 5            | 21                   | I/O         | TTL                    |                                                                                                                                                                                                          |

| RA3                                           | 5           | 6            | 22                   | I/O         | TTL                    |                                                                                                                                                                                                          |

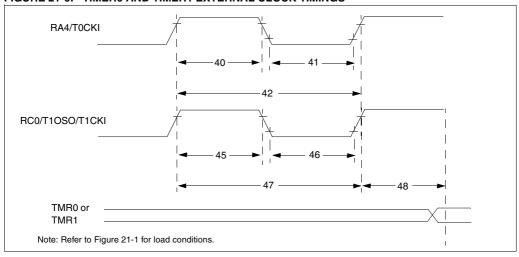

| RA4/T0CKI                                     | 6           | 7            | 23                   | I/O         | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                  |

| RA5/SS                                        | 7           | 8            | 24                   | I/O         | TTL                    | RA5 can also be the slave select for the synchronous serial port.                                                                                                                                        |

|                                               |             |              |                      |             |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT                                       | 33          | 36           | 8                    | I/O         | TTL/ST <sup>(4)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1                                           | 34          | 37           | 9                    | I/O         | TTL                    |                                                                                                                                                                                                          |

| RB2                                           | 35          | 38           | 10                   | I/O         | TTL                    |                                                                                                                                                                                                          |

| RB3                                           | 36          | 39           | 11                   | I/O         | TTL                    |                                                                                                                                                                                                          |

| RB4                                           | 37          | 41           | 14                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB5                                           | 38          | 42           | 15                   | I/O         | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB6                                           | 39          | 43           | 16                   | I/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7                                           | 40          | 44           | 17                   | I/O         | TTL/ST <sup>(5)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

|                                               |             |              |                      |             |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                      |

| RC0/T10SO <sup>(1)</sup> /T1CKI               | 15          | 16           | 32                   | I/O         | ST                     | RC0 can also be the Timer1 oscillator output <sup>(1)</sup> or Timer1 clock input.                                                                                                                       |

| RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> | 16          | 18           | 35                   | I/O         | ST                     | RC1 can also be the Timer1 oscillator input <sup>(1)</sup> or Capture2 input/Compare2 output/PWM2 output <sup>(2)</sup> .                                                                                |

| RC2/CCP1                                      | 17          | 19           | 36                   | I/O         | ST                     | RC2 can also be the Capture1 input/Compare1 out-<br>put/PWM1 output.                                                                                                                                     |

| RC3/SCK/SCL                                   | 18          | 20           | 37                   | I/O         | ST                     | RC3 can also be the synchronous serial clock input/out-<br>put for both SPI and I <sup>2</sup> C modes.                                                                                                  |

| RC4/SDI/SDA                                   | 23          | 25           | 42                   | I/O         | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                          |

| RC5/SDO                                       | 24          | 26           | 43                   | I/O         | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                             |

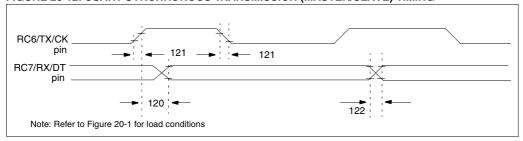

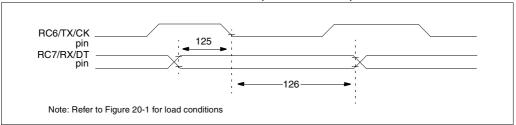

| RC6/TX/CK <sup>(2)</sup>                      | 25          | 27           | 44                   | I/O         | ST                     | RC6 can also be the USART Asynchronous Transmit <sup>(2)</sup> or Synchronous Clock <sup>(2)</sup> .                                                                                                     |

| RC7/RX/DT <sup>(2)</sup>                      | 26          | 29           | 1                    | I/O         | ST                     | RC7 can also be the USART Asynchronous Receive <sup>(2)</sup> or Synchronous Data <sup>(2)</sup> .                                                                                                       |

Legend: I = input O = output - = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: Pin functions T1OSO and T1OSI are reversed on the PIC16C64.

- 2: CCP2 and the USART are not available on the PIC16C64/64A/R64.

- 3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

- 4: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 5: This buffer is a Schmitt Trigger input when used in serial programming mode.

- 6: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

TABLE 4-2: SPECIAL FUNCTION REGISTERS FOR THE PIC16C62/62A/R62 (Cont.'d)

| Address              | Name    | Bit 7              | Bit 6                                      | Bit 5                     | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |  |

|----------------------|---------|--------------------|--------------------------------------------|---------------------------|----------------|--------------|-----------------|---------------|--------------------|--------------------------|------------------------------------------------|--|

| Bank 1               |         |                    |                                            |                           |                |              |                 |               |                    |                          |                                                |  |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location                              | uses conter               | nts of FSR to  | address data | a memory (n     | ot a physical | register)          | 0000 0000                | 0000 0000                                      |  |

| 81h                  | OPTION  | RBPU               | INTEDG                                     | T0CS                      | T0SE           | PSA          | PS2             | PS1           | PS0                | 1111 1111                | 1111 1111                                      |  |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                              |                           | 0000 0000      | 0000 0000    |                 |               |                    |                          |                                                |  |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                         | RP0                       | TO             | PD           | 0001 1xxx       | 000q quuu     |                    |                          |                                                |  |

| 84h <sup>(1)</sup>   | FSR     | Indirect dat       | direct data memory address pointer xxxx xx |                           |                |              |                 |               |                    |                          |                                                |  |

| 85h                  | TRISA   | _                  | _                                          | PORTA Dat                 | ta Direction R | egister      |                 |               |                    | 11 1111                  | 11 1111                                        |  |

| 86h                  | TRISB   | PORTB Da           | ta Direction F                             | Register                  |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |  |

| 87h                  | TRISC   | PORTC Da           | ORTC Data Direction Register               |                           |                |              |                 |               |                    |                          | 1111 1111                                      |  |

| 88h                  | _       | Unimpleme          | Unimplemented                              |                           |                |              |                 |               |                    |                          | _                                              |  |

| 89h                  | _       | Unimplemented      |                                            |                           |                |              |                 |               |                    | _                        | _                                              |  |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                                          | _                         | Write Buffer   | for the uppe | r 5 bits of the | Program C     | ounter             | 0 0000                   | 0 0000                                         |  |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                       | TOIE                      | INTE           | RBIE         | TOIF            | INTF          | RBIF               | 0000 000x                | 0000 000u                                      |  |

| 8Ch                  | PIE1    | (6)                | (6)                                        | _                         | _              | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE             | 00 0000                  | 00 0000                                        |  |

| 8Dh                  | _       | Unimpleme          | nted                                       |                           |                |              |                 |               |                    | _                        | _                                              |  |

| 8Eh                  | PCON    | _                  | _                                          | _                         | _              | _            | _               | POR           | BOR <sup>(4)</sup> | qq                       | uu                                             |  |

| 8Fh                  | _       | Unimpleme          | nted                                       |                           |                |              | •               |               |                    | _                        | _                                              |  |

| 90h                  | _       | Unimpleme          | nted                                       |                           |                |              |                 |               |                    | _                        | _                                              |  |

| 91h                  | _       | Unimpleme          | nted                                       |                           |                |              |                 |               |                    | _                        | _                                              |  |

| 92h                  | PR2     | Timer2 Peri        | iod Register                               |                           |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |  |

| 93h                  | SSPADD  | Synchronou         | us Serial Port                             | t (I <sup>2</sup> C mode) | Address Reg    | jister       |                 |               |                    | 0000 0000                | 0000 0000                                      |  |

| 94h                  | SSPSTAT | _                  | _                                          | D/Ā                       | Р              | S            | R/W             | UA            | BF                 | 00 0000                  | 00 0000                                        |  |

| 95h-9Fh              | _       | Unimpleme          | nted                                       |                           |                |              |                 |               |                    | _                        | _                                              |  |

|                      |         |                    |                                            |                           |                |              |                 |               |                    |                          |                                                |  |

$\begin{tabular}{ll} Legend: & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented location read as '0'. \\ & Shaded locations are unimplemented, read as '0'. \\ \end{tabular}$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The BOR bit is reserved on the PIC16C62, always maintain this bit set.

- 5: The IRP and RP1 bits are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

- 6: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

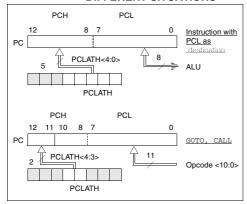

#### 4.3 PCL and PCLATH

**Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-24 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-24: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or a POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no status bits to indicate stack overflows or stack underflow conditions

Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address

## 4.4 Program Memory Paging

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PIC16C6X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C6X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

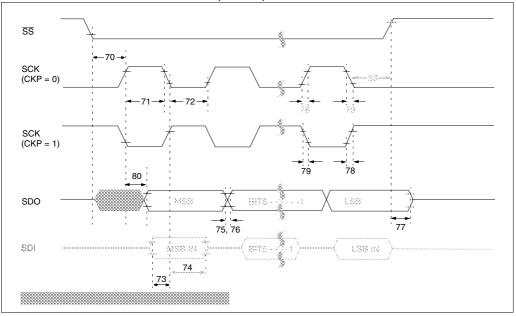

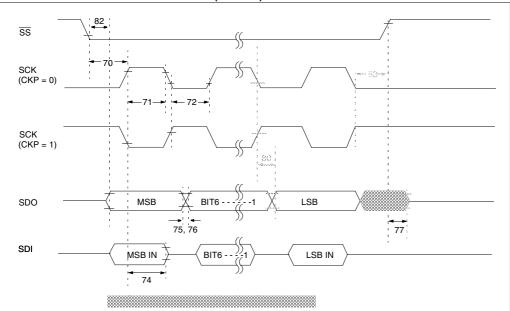

#### 11.3 SPI Mode for PIC16C66/67

This section contains register definitions and operational characterisitics of the SPI module on the PIC16C66 and PIC16C67 only.

### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C66/67)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0  |

|-------|-------|-----|-----|-----|-----|-----|------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF   |

| bit7  |       |     |     |     |     |     | bit0 |

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'- n = Value at POR reset

bit 7: SMP: SPI data input sample phase

**SPI Master Mode**

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

SPI Slave Mode

SMP must be cleared when SPI is used in slave mode

bit 6: CKE: SPI Clock Edge Select (Figure 11-11, Figure 11-12, and Figure 11-13)

CKP = 0

- 1 = Data transmitted on rising edge of SCK

- 0 = Data transmitted on falling edge of SCK

CKP = 1

- 1 = Data transmitted on falling edge of SCK

- 0 = Data transmitted on rising edge of SCK

- bit 5: D/A: Data/Address bit (I<sup>2</sup>C mode only)

- 1 = Indicates that the last byte received or transmitted was data

- 0 = Indicates that the last byte received or transmitted was address

- bit 4: **P**: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Start bit is detected last, SSPEN is cleared)

- 1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)

- 0 = Stop bit was not detected last

- bit 3: Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Stop bit is detected last, SSPEN is cleared)

- 1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)

- 0 = Start bit was not detected last

- bit 2: **R/W**: Read/Write bit information (I<sup>2</sup>C mode only)

This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or  $\overline{ACK}$  bit.

- 1 = Read

- 0 = Write

- bit 1: **UA**: Update Address (10-bit I<sup>2</sup>C mode only)

- 1 = Indicates that the user needs to update the address in the SSPADD register

- 0 = Address does not need to be updated

- bit 0: **BF**: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes)

- 1 = Receive complete, SSPBUF is full

- 0 = Receive not complete. SSPBUF is empty

Transmit (I<sup>2</sup>C mode only)

- 1 = Transmit in progress, SSPBUF is full

- 0 = Transmit complete, SSPBUF is empty

## 12.1 USART Baud Rate Generator (BRG)

| Αp | pli | cable | e Dev | vice | es  |    |     |     |    |     |     |    |    |

|----|-----|-------|-------|------|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62  | 62A   | R62   | 63   | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

# EXAMPLE 12-1: CALCULATING BAUD RATE FRROR

Desired Baud rate = Fosc / (64 (X + 1))

9600 = 16000000 / (64 (X + 1)) $X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X+1)) equation can reduce the baud rate error in some cases.

Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name                               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 98h     | TXSTA                              | CSRC  | TX9   | TXEN  | SYNC  | -     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| 18h     | RCSTA                              | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| 99h     | SPBRG Baud Rate Generator Register |       |       |       |       |       |       |       |       |                         | 0000 0000                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

| XORLW                          | Exclusive OR Literal with W                                                                                       | XORWF                         | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                        | [label] XORLW k                                                                                                   | Syntax:                       | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Operands:                      | $0 \le k \le 255$                                                                                                 | Operands:                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Operation:<br>Status Affected: | (W) .XOR. $k \rightarrow (W)$<br>Z                                                                                | Operation:                    | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Encoding:                      | 11 1010 kkkk kkkk                                                                                                 | Status Affected:<br>Encoding: | Z 00 0110 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Description:                   | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. | Description:                  | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Words:                         | 1                                                                                                                 | Words:                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:<br>Q Cycle Activity:   | 1<br>Q1 Q2 Q3 Q4                                                                                                  | Cycles:                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                | Decode Read Ilteral 'k' Process Write to data W                                                                   | Q Cycle Activity:             | Q1 Q2 Q3 Q4    Decode   Read register r |  |  |  |  |

| Example:                       | XORLW 0xAF                                                                                                        |                               | · '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                | Before Instruction                                                                                                | Example                       | XORWF REG 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                | W = 0xB5                                                                                                          |                               | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                | After Instruction  W = 0x1A                                                                                       |                               | $ \begin{array}{rcl} REG &=& 0xAF \\ W &=& 0xB5 \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                | OKIN                                                                                                              |                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                |                                                                                                                   |                               | REG = 0x1A  W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 15.4 **Timing Parameter Symbology**

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                   | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|--------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                      |           |                                        |

| F                     | Frequency                            | Т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings: |           |                                        |

| pp                    |                                      |           |                                        |

| СС                    | CCP1                                 | osc       | OSC1                                   |

| ck                    | CLKOUT                               | rd        | RD                                     |

| cs                    | CS                                   | rw        | RD or WR                               |

| di                    | SDI                                  | sc        | SCK                                    |

| do                    | SDO                                  | SS        | SS                                     |

| dt                    | Data in                              | tO        | T0CKI                                  |

| io                    | I/O port                             | t1        | T1CKI                                  |

| mc                    | MCLR                                 | wr        | WR                                     |

| Upperca               | ase letters and their meanings:      | ·         |                                        |

| S                     |                                      |           |                                        |

| F                     | Fall                                 | Р         | Period                                 |

| Н                     | High                                 | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)               | V         | Valid                                  |

| L                     | Low                                  | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                      |           |                                        |

Bus free Tcc:st (I<sup>2</sup>C specifications only)

output access

AA

BUF

| CC  |                 |     |                |  |

|-----|-----------------|-----|----------------|--|

| HD  | Hold            | SU  | Setup          |  |

| ST  |                 |     |                |  |

| DAT | DATA input hold | STO | STOP condition |  |

| STA | START condition |     |                |  |

High

Low

High

Low

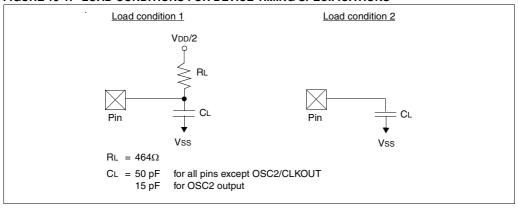

### FIGURE 15-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

**DC Characteristics:**

18.1

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

TP -----

PIC16C62A/R62/64A/R64-04 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-10 (Commercial, Industrial, Extended) PIC16C62A/R62/64A/R64-20 (Commercial, Industrial, Extended)

|        | ·                                                                | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended, |         |         |     |       |                                                             |  |  |  |

|--------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-----|-------|-------------------------------------------------------------|--|--|--|

| DC CHA | RACTERISTICS                                                     | Oporatii                                                                                                                             | ig tomp | oratare |     |       | ≤ TA ≤ +85°C for industrial and                             |  |  |  |

|        |                                                                  | 0°C ≤ TA ≤ +70°C for commercial                                                                                                      |         |         |     |       |                                                             |  |  |  |

| Param  | Characteristic                                                   | Sym                                                                                                                                  | Min     | Turnst  |     | Units | Conditions                                                  |  |  |  |

| No.    | Characteristic                                                   | Sylli                                                                                                                                | IVIIII  | Тур†    | wax | Units | Conditions                                                  |  |  |  |

| D001   | Supply Voltage                                                   | VDD                                                                                                                                  | 4.0     | -       | 6.0 | V     | XT, RC and LP osc configuration                             |  |  |  |

| D001A  |                                                                  |                                                                                                                                      | 4.5     | -       | 5.5 | V     | HS osc configuration                                        |  |  |  |

| D002*  | RAM Data Retention<br>Voltage (Note 1)                           | VDR                                                                                                                                  | -       | 1.5     | -   | V     |                                                             |  |  |  |

| D003   | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                                                                                                                                 | -       | Vss     | -   | V     | See section on Power-on Reset for details                   |  |  |  |

| D004*  | VDD rise rate to ensure internal Power-on Reset signal           | SVDD                                                                                                                                 | 0.05    | -       | -   | V/ms  | See section on Power-on Reset for details                   |  |  |  |

| D005   | Brown-out Reset Voltage                                          | BVDD                                                                                                                                 | 3.7     | 4.0     | 4.3 | V     | BODEN bit in configuration word enabled                     |  |  |  |

|        |                                                                  |                                                                                                                                      | 3.7     | 4.0     | 4.4 | V     | Extended Range Only                                         |  |  |  |

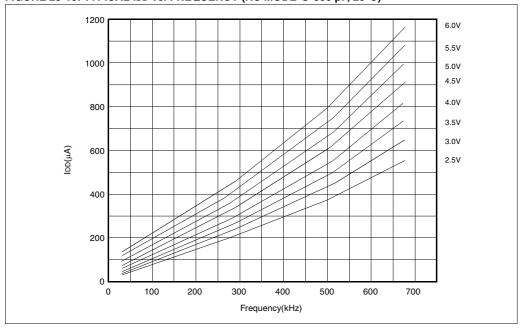

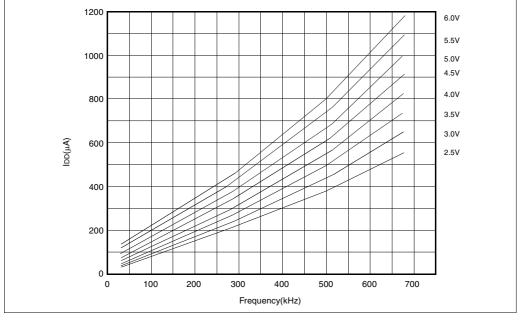

| D010   | Supply Current (Note 2, 5)                                       | IDD                                                                                                                                  | -       | 2.7     | 5   | mA    | XT, RC, osc configuration Fosc = 4 MHz, VDD = 5.5V (Note 4) |  |  |  |

| D013   |                                                                  |                                                                                                                                      | -       | 10      | 20  | mA    | HS osc configuration Fosc = 20 MHz,<br>VDD = 5.5V           |  |  |  |

| D015*  | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR                                                                                                                        | -       | 350     | 425 | μА    | BOR enabled, VDD = 5.0V                                     |  |  |  |

| D020   | Power-down Current (Note                                         | IPD                                                                                                                                  | -       | 10.5    | 42  | μА    | VDD = 4.0V, WDT enabled, -40°C to +85°C                     |  |  |  |

| D021   | 3, 5)                                                            |                                                                                                                                      | -       | 1.5     | 16  | μA    | VDD = 4.0V, WDT disabled, -0°C to +70°C                     |  |  |  |

| D021A  |                                                                  |                                                                                                                                      | -       | 1.5     | 19  | μΑ    | VDD = 4.0V, WDT disabled, -40°C to +85°C                    |  |  |  |

| D021B  |                                                                  |                                                                                                                                      | -       | 2.5     | 19  | μА    | VDD = 4.0V, WDT disabled, -40°C to +125°C                   |  |  |  |

| D023*  | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR                                                                                                                        | -       | 350     | 425 | μА    | BOR enabled, VDD = 5.0V                                     |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.