Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc65at-04-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 4-15: PIE1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 8Ch)

| R/W-0  | R/W-0       | R/W-0     | R/W-0        | R/W-0        | R/W-0        | R/W-0  | R/W-0  |                          |

|--------|-------------|-----------|--------------|--------------|--------------|--------|--------|--------------------------|

| PSPIE  | —           | RCIE      | TXIE         | SSPIE        | CCP1IE       | TMR2IE | TMR1IE | R = Readable bit         |

| bit7   |             |           |              |              |              |        | bit0   | W = Writable bit         |

|        |             |           |              |              |              |        |        | U = Unimplemented bit,   |

|        |             |           |              |              |              |        |        | read as '0'              |

|        |             |           |              |              |              |        |        | - n = Value at POR reset |

| bit 7: | 1 = Enable  |           |              |              | upt Enable b | bit    |        |                          |

|        | 0 = Disable |           |              |              |              |        |        |                          |

| 1.1.0  |             |           |              | •            |              |        |        |                          |

| bit 6: | Reserved:   | Always ma | aintain this | oit clear.   |              |        |        |                          |

| bit 5: | RCIE: USA   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              | •            |              |        |        |                          |

| bit 4: | TXIE: USA   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              | •            |              |        |        |                          |

| bit 3: | SSPIE: Syr  |           |              | Interrupt Er | nable bit    |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           | •            |              |              |        |        |                          |

| bit 2: | CCP1IE: C   |           |              | bit          |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           | •            |              |              |        |        |                          |

| bit 1: | TMR2IE: T   |           |              |              |              |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable |           |              |              | •            |        |        |                          |

| bit 0: | TMR1IE: T   |           |              |              | it           |        |        |                          |

|        | 1 = Enable  |           |              |              |              |        |        |                          |

|        | 0 = Disable | s the TMR | I OVERTION   | nterrupt     |              |        |        |                          |

|        |             |           |              |              |              |        |        |                          |

NOTES:

-

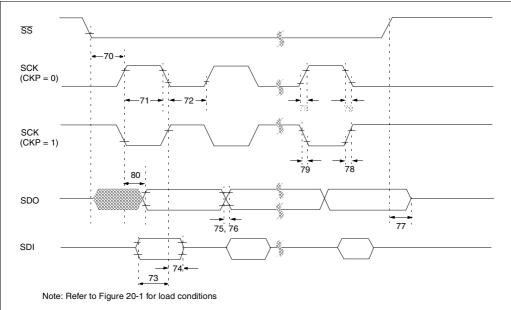

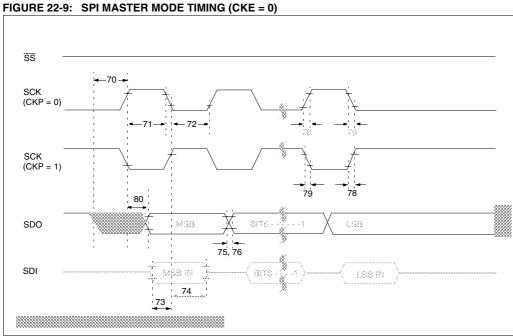

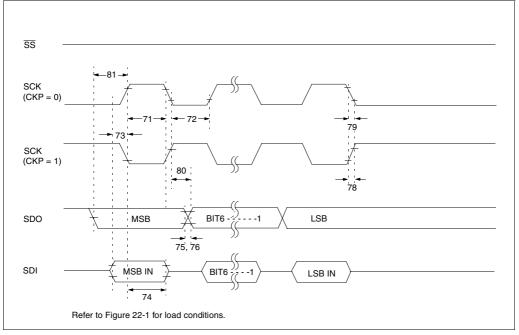

#### 11.2.1 OPERATION OF SSP MODULE IN SPI MODE

Applicable Devices 61 62 624 R62 63 R63 64 644 R64 65 654 R65 66 67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

Serial Data Out (SDO)

PIC16C6X

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- · Slave Mode (SCK is the clock input)

- Clock Polarity (Output/Input data on the Rising/ Falling edge of SCK)

- · Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full bit, BF (SSPSTAT<0>) and flag bit SSPIF are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>) will be set. User software must clear bit WCOL so that it can be determined if the following write(s) to the SSPBUF completed successfully. When the application software is expecting to receive valid data, the SSPBUF register should be read before the next byte of data to transfer is written to the SSPBUF register. The Buffer Full bit BF (SSPSTAT<0>) indicates when the SSPBUF register has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF register must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-1 shows the loading of the SSPBUF (SSPSR) register for data transmission. The shaded instruction is only required if the received data is meaningful.

#### EXAMPLE 11-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      |       | •       | ,    |                   |

|------|-------|---------|------|-------------------|

|      | BSF   | STATUS, | RP0  | ;Specify Bank 1   |

| LOOP | BTFSS | SSPSTAT | , BF | ;Has data been    |

|      |       |         |      | ;received         |

|      |       |         |      | ;(transmit        |

|      |       |         |      | ;complete)?       |

|      | GOTO  | LOOP    |      | ;No               |

|      | BCF   | STATUS, | RP0  | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, | W    | ;W reg = contents |

|      |       |         |      | ; of SSPBUF       |

|      | MOVWF | RXDATA  |      | ;Save in user RAM |

|      | MOVF  | TXDATA, | W    | ;W reg = contents |

|      |       |         |      | ; of TXDATA       |

|      | MOVWF | SSPBUF  |      | ;New data to xmit |

|      |       |         |      |                   |

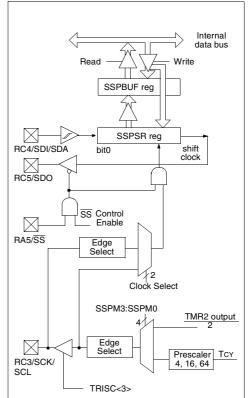

The block diagram of the SSP module, when in SPI mode (Figure 11-3), shows that the SSPSR register is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

#### FIGURE 11-3: SSP BLOCK DIAGRAM (SPI MODE)

#### 11.5.1.2 RECEPTION

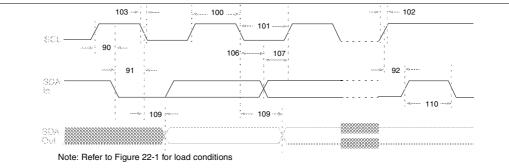

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

### FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W=0         Receiving Data         ACK         Receiving Data         ACK           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | F 7<br>I I<br>I I<br>/ I PI<br>- A   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>) Cleared in software BF (SSPSTAT<0>) SSPBUF register is read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bus Master<br>terminates<br>transfer |

| SSPOV (SSPCON<6>)<br>Bit SSPOV is set because the SSPBUF register is still full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |

| ACK is not sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |

Г

### FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                | R/W-0                       | R/W-0          | U-0         | R-0          | R-0          | R-x         |                    |                                                                                                                               |

|--------|----------------------------------------------------------------------|-----------------------------|----------------|-------------|--------------|--------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                  | SREN                        | CREN           | —           | FERR         | OERR         | RX9D        | R                  | = Readable bit                                                                                                                |

| bit7   |                                                                      |                             |                |             |              |              | bitO        | W<br>U<br>- n<br>x | <ul> <li>Writable bit</li> <li>Unimplemented</li> <li>bit, read as '0'</li> <li>Value at POR rese</li> <li>unknown</li> </ul> |

| bit 7: | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p             | s RC7/RX/l                  | DT and RC<br>d | 6/TX/CK     | pins as seri | al port pins | s when bits | TRIS               | C<7:6> are set)                                                                                                               |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion          |             |              |              |             |                    |                                                                                                                               |

| bit 5: | SREN: Sing                                                           | gle Receiv                  | e Enable bi    | t           |              |              |             |                    |                                                                                                                               |

|        | Asynchrone<br>Don't care                                             | ous mode                    |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{Synchronof}{1 = Enables}$ $0 = Disables$ This bit is c        | s single ree<br>s single re | ceive<br>ceive | is comple   | ete.         |              |             |                    |                                                                                                                               |

|        | Synchrono<br>Unused in t                                             |                             | <u>slave</u>   |             |              |              |             |                    |                                                                                                                               |

| bit 4: | CREN: Cor                                                            | ntinuous R                  | eceive Ena     | ble bit     |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Asynchrono}}{1 = \text{Enable}}$ $0 = \text{Disable}$   | s continuo                  |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Synchronor}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                | until enabl | le bit CREN  | l is cleared | (CREN ov    | erride             | s SREN)                                                                                                                       |

| bit 3: | Unimplem                                                             | ented: Rea                  | ad as '0'      |             |              |              |             |                    |                                                                                                                               |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                | ed by rea   | ding RCRE    | G register   | and receive | e next             | valid byte)                                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                | d by clea   | ring bit CRI | EN)          |             |                    |                                                                                                                               |

| bit 0: | <b>RX9D</b> : 9th                                                    |                             |                |             |              |              |             |                    |                                                                                                                               |

NOTES:

-

| COMF                                                                                    | Complement f                                                                                                                                                                                                                                                                                                                                                                                       | DECFSZ            | Decrement f, Skip if 0                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                 | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                                                                                                                          | Syntax:           | [label] DECFSZ f,d                                                                                                                                                                                                                                                 |

| Operands:                                                                               | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                        | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                    |

| Operation:                                                                              | $(\bar{f}) \rightarrow (destination)$                                                                                                                                                                                                                                                                                                                                                              | Operation:        | (f) - 1 $\rightarrow$ (destination);                                                                                                                                                                                                                               |

| Status Affected:                                                                        | Z                                                                                                                                                                                                                                                                                                                                                                                                  |                   | skip if result = 0                                                                                                                                                                                                                                                 |

| Encoding:                                                                               | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                  | Status Affected:  | None                                                                                                                                                                                                                                                               |

| Description:                                                                            | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in                                                                                                                                                                                                                                                                                                            | Encoding:         | 00 1011 dfff ffff                                                                                                                                                                                                                                                  |

| Words:<br>Cycles:                                                                       | W. If 'd' is 1 the result is stored back in<br>register 'f'.<br>1                                                                                                                                                                                                                                                                                                                                  | Description:      | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is |

| Q Cycle Activity:                                                                       | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                        |                   | executed instead making it a 2TCY instruc-<br>tion.                                                                                                                                                                                                                |

| , ,                                                                                     | Decode Read Process Write to                                                                                                                                                                                                                                                                                                                                                                       | Words:            | 1                                                                                                                                                                                                                                                                  |

|                                                                                         | register data destination                                                                                                                                                                                                                                                                                                                                                                          | Cycles:           | 1(2)                                                                                                                                                                                                                                                               |

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                    | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                        |

| Example                                                                                 | COMF REG1, 0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                 | , ,               | Decode Read Process Write to register 'f' data destination                                                                                                                                                                                                         |

|                                                                                         | $\begin{array}{rcl} REG1 &=& 0x13\\ After Instruction & \\ REG1 &=& 0x13\\ W &=& 0xEC \end{array}$                                                                                                                                                                                                                                                                                                 | lf Skip:          | Q1         Q2         Q3         Q4           No-<br>Operation         Operation         Operation         Operation                                                                                                                                               |

| DECF                                                                                    | Decrement f                                                                                                                                                                                                                                                                                                                                                                                        |                   |                                                                                                                                                                                                                                                                    |

| Syntax:                                                                                 | [ <i>label</i> ] DECF f,d                                                                                                                                                                                                                                                                                                                                                                          | Example           | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                    |

| Operands:                                                                               | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                  |                   | CONTINUE •                                                                                                                                                                                                                                                         |

|                                                                                         | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                          |                   | •                                                                                                                                                                                                                                                                  |

| Operation:                                                                              | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                               |                   | •<br>Before Instruction                                                                                                                                                                                                                                            |

| Operation:<br>Status Affected:                                                          |                                                                                                                                                                                                                                                                                                                                                                                                    |                   | •<br>Before Instruction<br>PC = address HERE                                                                                                                                                                                                                       |

| •                                                                                       | (f) - 1 $\rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                                                |                   | PC = address HERE<br>After Instruction                                                                                                                                                                                                                             |

| Status Affected:                                                                        | (f) - 1 → (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is                                                                                                                                                                                                                                                      |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE                                                                                                                                                                    |

| Status Affected:<br>Encoding:                                                           | (f) - 1 → (destination)<br>Z<br>00 0011 dfff ffff                                                                                                                                                                                                                                                                                                                                                  |                   | $\begin{array}{rcl} PC &=& address {}_{HERE}\\ \textbf{After Instruction}\\ & CNT &=& CNT-1\\ & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                            |

| Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | (f) - 1 $\rightarrow$ (destination)<br>Z<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                                                                                                                                                                                                               |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE                                                                                                                                                                    |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | (f) - 1 $\rightarrow$ (destination)<br>Z<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                                                                                                                                                                                                               |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1                                                                                                                                                                                |                   | $\begin{array}{rcl} PC &=& address \mbox{ HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \mbox{ continue} \\ \mbox{if CNT} &\neq& 0, \\ \end{array}$                                                               |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00 0011 dfff ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination                                                                                                             |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $ \begin{array}{c c} (f) - 1 \rightarrow (destination) \\ \hline Z \\ \hline 00 & 0011 & dfff & ffff \\ \hline Decrement register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. \\ 1 & & \\ 1 & & \\ Q1 & Q2 & Q3 & Q4 \\ \hline \hline Decode & Read & Process & Write to destination \\ \hline & & \\ f'' & & \\ \end{array} $ |                   | $\begin{array}{rcl} PC &=& address {}_{HERE}\\ \textbf{After Instruction}\\ & CNT &=& CNT-1\\ & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                            |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00  0011  dfff  ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>2<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01                                                       |                   | PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT ≠ 0,                                                                                                                                                     |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 → (destination)<br>Z<br>00 0011 dfff fff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>1<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>register data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01<br>Z = 0                                                     |                   | $\begin{array}{rcl} PC &=& address \mbox{ HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \mbox{ CONTINUE} \\ \mbox{if CNT} &\neq& 0, \\ \end{array}$                                                               |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | (f) - 1 $\rightarrow$ (destination)<br>Z<br>00  0011  dfff  ffff<br>Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.<br>1<br>2<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>data destination<br>DECF CNT, 1<br>Before Instruction<br>CNT = 0x01                                                       |                   | $\begin{array}{rcl} PC &=& address \mbox{ HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \mbox{ continue} \\ \mbox{if CNT} &\neq& 0, \\ \end{array}$                                                               |

| SUBWF             | Subtract                                                                   | W from f                                                                                                                                                                             |                   |                      |  |  |  |

|-------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|--|--|--|

| Syntax:           | [ label ]                                                                  | SUBWF                                                                                                                                                                                | f,d               |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$ | ,                                                                                                                                                                                    |                   |                      |  |  |  |

| Operation:        | (f) - (W) $\rightarrow$                                                    | (destina                                                                                                                                                                             | tion)             |                      |  |  |  |

| Status Affected:  | C, DC, Z                                                                   |                                                                                                                                                                                      |                   |                      |  |  |  |

| Encoding:         | 00                                                                         | 0010                                                                                                                                                                                 | dfff              | ffff                 |  |  |  |

| Description:      | ister from re<br>stored in the                                             | Subtract (2's complement method) W reg-<br>ister from register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                   |                      |  |  |  |

| Words:            | 1                                                                          |                                                                                                                                                                                      |                   |                      |  |  |  |

| Cycles:           | 1                                                                          |                                                                                                                                                                                      |                   |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                         | Q2                                                                                                                                                                                   | Q3                | Q4                   |  |  |  |

|                   | Decode                                                                     | Read<br>register 'f'                                                                                                                                                                 | Process<br>data   | Write to destination |  |  |  |

| Example 1:        | SUBWF                                                                      | reg1,1                                                                                                                                                                               |                   |                      |  |  |  |

|                   | Before Ins                                                                 | truction                                                                                                                                                                             |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 3                 |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>?            |                      |  |  |  |

|                   | Z                                                                          | =                                                                                                                                                                                    | ?                 |                      |  |  |  |

|                   | After Instru                                                               | uction                                                                                                                                                                               |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 1                 |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>1; result is | nositive             |  |  |  |

|                   | z                                                                          | =                                                                                                                                                                                    | 0                 | poolavo              |  |  |  |

| Example 2:        | Before Ins                                                                 | truction                                                                                                                                                                             |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 2                 |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>?            |                      |  |  |  |

|                   | Z                                                                          | =                                                                                                                                                                                    | ?                 |                      |  |  |  |

|                   | After Instru                                                               | uction                                                                                                                                                                               |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 0                 |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>1; result is | 7010                 |  |  |  |

|                   | z                                                                          | =                                                                                                                                                                                    | 1                 | 2010                 |  |  |  |

| Example 3:        | Before Ins                                                                 | truction                                                                                                                                                                             |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 1                 |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>?            |                      |  |  |  |

|                   | z                                                                          | =                                                                                                                                                                                    | ?                 |                      |  |  |  |

|                   | After Instru                                                               | uction                                                                                                                                                                               |                   |                      |  |  |  |

|                   | REG1                                                                       | =                                                                                                                                                                                    | 0xFF              |                      |  |  |  |

|                   | W<br>C                                                                     | =                                                                                                                                                                                    | 2<br>0; result is | negative             |  |  |  |

|                   | z                                                                          | =                                                                                                                                                                                    | 0                 | guivo                |  |  |  |

|                   |                                                                            |                                                                                                                                                                                      |                   |                      |  |  |  |

| SWAPF             | Swap Ni                                                                                                                                                               | bbles in                                                                                | f               |                      |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|--|

| Syntax:           | [label]                                                                                                                                                               | SWAPF 1                                                                                 | ,d              |                      |  |  |  |  |

| Operands:         | $0 \le f \le 12$<br>$d \in [0,1]$                                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                         |                 |                      |  |  |  |  |

| Operation:        | · · ·                                                                                                                                                                 | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$ |                 |                      |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                  | None                                                                                    |                 |                      |  |  |  |  |

| Encoding:         | 0 0                                                                                                                                                                   | 1110                                                                                    | dfff            | ffff                 |  |  |  |  |

| Description:      | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |                                                                                         |                 |                      |  |  |  |  |

| Words:            | 1                                                                                                                                                                     |                                                                                         |                 |                      |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                     |                                                                                         |                 |                      |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                    | Q2                                                                                      | Q3              | Q4                   |  |  |  |  |

|                   | Decode                                                                                                                                                                | Read<br>register 'f'                                                                    | Process<br>data | Write to destination |  |  |  |  |

| Example           | SWAPF                                                                                                                                                                 | REG,                                                                                    | 0               |                      |  |  |  |  |

|                   | Before In                                                                                                                                                             | struction                                                                               |                 |                      |  |  |  |  |

|                   |                                                                                                                                                                       | REG1                                                                                    | = 0x/           | A5                   |  |  |  |  |

|                   | After Inst                                                                                                                                                            | truction                                                                                |                 |                      |  |  |  |  |

|                   |                                                                                                                                                                       | REG1<br>W                                                                               | = 0x/<br>= 0x5  | .0                   |  |  |  |  |

| TRIS             | Load TR                                                                                                                                                                             | IS Regis  | ster    |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------|--|

| Syntax:          | [label]                                                                                                                                                                             | TRIS      | f       |      |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                   |           |         |      |  |

| Operation:       | $(W) \rightarrow TI$                                                                                                                                                                | RIS regis | ster f; |      |  |

| Status Affected: | None                                                                                                                                                                                |           |         |      |  |

| Encoding:        | 00                                                                                                                                                                                  | 0000      | 0110    | Offf |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |           |         |      |  |

| Words:           | 1                                                                                                                                                                                   |           |         |      |  |

| Cycles:          | 1                                                                                                                                                                                   |           |         |      |  |

| Example          |                                                                                                                                                                                     |           |         |      |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |           |         |      |  |

|                  |                                                                                                                                                                                     |           |         |      |  |

| XORLW             | Exclusive OR Literal with W                                                                                                  |                     |                 |               |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ]                                                                                                             | XORLV               | Vk              |               |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                              | $0 \le k \le 255$   |                 |               |  |  |  |  |  |

| Operation:        | (W) .XO                                                                                                                      | $R. k \to (N$       | N)              |               |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                            |                     |                 |               |  |  |  |  |  |

| Encoding:         | 11                                                                                                                           | 1010                | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |                     |                 |               |  |  |  |  |  |

| Words:            | 1                                                                                                                            |                     |                 |               |  |  |  |  |  |

| Cycles:           | 1                                                                                                                            |                     |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                           | Q2                  | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                                                                                                       | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example:          | XORLW                                                                                                                        | 0xAF                |                 |               |  |  |  |  |  |

|                   | Before Ir                                                                                                                    | nstruction          | n               |               |  |  |  |  |  |

|                   |                                                                                                                              | W =                 | 0xB5            |               |  |  |  |  |  |

|                   | After Ins                                                                                                                    | truction            |                 |               |  |  |  |  |  |

|                   |                                                                                                                              | W =                 | 0x1A            |               |  |  |  |  |  |

|                   |                                                                                                                              |                     |                 |               |  |  |  |  |  |

| XORWF             | Exclusiv                                                                                                                                                                           | e OR W                  | with f          |                      |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [label]                                                                                                                                                                            | XORWF                   | f,d             |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                                     | 27                      |                 |                      |  |  |  |

| Operation:        | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                          |                         |                 |                      |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                  |                         |                 |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                                 | 0110                    | dfff            | ffff                 |  |  |  |

| Description:      | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |                         |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                                  |                         |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                                  |                         |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                 | Q2                      | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                             | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |

| Example           | XORWF                                                                                                                                                                              | REG                     | 1               |                      |  |  |  |

|                   | Before In                                                                                                                                                                          | struction               | I               |                      |  |  |  |

|                   |                                                                                                                                                                                    | REG<br>W                | 0/1             | AF<br>B5             |  |  |  |

|                   | After Inst                                                                                                                                                                         | ruction                 |                 |                      |  |  |  |

|                   |                                                                                                                                                                                    | REG<br>W                | 0/1             | 1A<br>B5             |  |  |  |

=

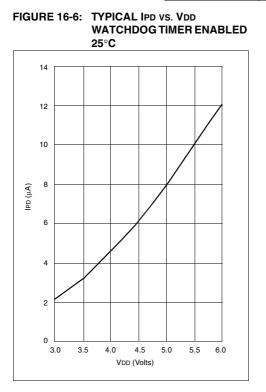

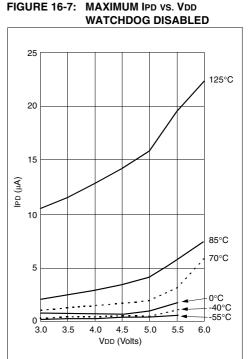

Data based on matrix samples. See first page of this section for details.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

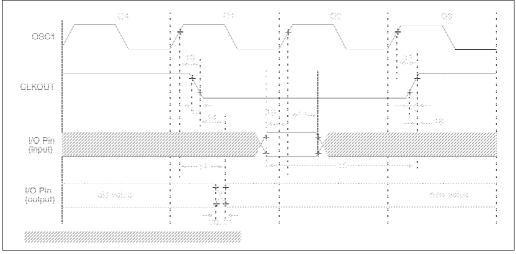

### FIGURE 17-3: CLKOUT AND I/O TIMING

### TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameters | Sym                                   | Characteristic                                   |                      | Min | Typ†        | Max | Units  | Conditions |

|------------|---------------------------------------|--------------------------------------------------|----------------------|-----|-------------|-----|--------|------------|

| 10*        | TosH2ckL                              | OSC1↑ to CLKOUT↓                                 |                      | -   | 75          | 200 | ns     | Note 1     |

| 11*        | TosH2ckH                              | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>         |                      | _   | 75          | 200 | ns     | Note 1     |