Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| - · ·                      |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc66-04i-sp |

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

| Address               | Name   | Bit 7         | Bit 6                                                                                         | Bit 5         | Bit 4         | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|-----------------------|--------|---------------|-----------------------------------------------------------------------------------------------|---------------|---------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 2                | •      |               |                                                                                               |               |               | •            |                 |               |           |                          |                                                |

| 100h <sup>(1)</sup>   | INDF   | Addressing    | ddressing this location uses contents of FSR to address data memory (not a physical register) |               |               |              |                 |               |           |                          |                                                |

| 101h                  | TMR0   | Timer0 mo     | dule's registe                                                                                | r             |               |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 102h <sup>(1)</sup>   | PCL    | Program C     | ounter's (PC)                                                                                 | Least Signi   | ficant Byte   |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 103h <sup>(1)</sup>   | STATUS | IRP           | RP1                                                                                           | RP0           | TO            | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 104h <sup>(1)</sup>   | FSR    | Indirect dat  | a memory ac                                                                                   | Idress pointe | er            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 105h                  | _      | Unimpleme     | ented                                                                                         |               |               |              |                 |               |           | _                        | _                                              |

| 106h                  | PORTB  | PORTB Da      | ta Latch whe                                                                                  | n written: PO | ORTB pins wh  | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 107h                  | _      | Unimpleme     | ented                                                                                         |               |               |              |                 |               |           | _                        | _                                              |

| 108h                  | _      | Unimpleme     | nted                                                                                          |               |               |              |                 |               |           | _                        | _                                              |

| 109h                  | _      | Unimpleme     | nted                                                                                          |               |               |              |                 |               |           | _                        | _                                              |

| 10Ah <sup>(1,2)</sup> | PCLATH | _             | _                                                                                             | 1             | Write Buffer  | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 10Bh <sup>(1)</sup>   | INTCON | GIE           | PEIE                                                                                          | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 10Ch-<br>10Fh         | _      | Unimpleme     | ented                                                                                         |               |               |              |                 |               |           | _                        | _                                              |

| Bank 3                |        |               |                                                                                               |               |               |              |                 |               |           |                          |                                                |

| 180h <sup>(1)</sup>   | INDF   | Addressing    | this location                                                                                 | uses conter   | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 181h                  | OPTION | RBPU          | INTEDG                                                                                        | T0CS          | T0SE          | PSA          | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 182h <sup>(1)</sup>   | PCL    | Program C     | ounter's (PC)                                                                                 | Least Sigr    | nificant Byte |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 183h <sup>(1)</sup>   | STATUS | IRP           | RP1                                                                                           | RP0           | TO            | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 184h <sup>(1)</sup>   | FSR    | Indirect dat  | a memory ac                                                                                   | Idress pointe | er            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 185h                  | _      | Unimpleme     | ented                                                                                         |               |               |              |                 |               |           | _                        | _                                              |

| 186h                  | TRISB  | PORTB Da      | ta Direction F                                                                                | Register      |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 187h                  | _      | Unimpleme     | Unimplemented                                                                                 |               |               |              |                 |               |           | _                        | _                                              |

| 188h                  | _      | Unimplemented |                                                                                               |               |               |              |                 |               | _         | _                        |                                                |

| 189h                  | _      | Unimpleme     | nted                                                                                          |               |               |              |                 |               |           | _                        | _                                              |

| 18Ah <sup>(1,2)</sup> | PCLATH | _             | _                                                                                             | -             | Write Buffer  | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 18Bh <sup>(1)</sup>   | INTCON | GIE           | PEIE                                                                                          | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 18Ch-<br>19Fh         | _      | Unimpleme     |                                                                                               |               | anands on     |              |                 |               |           | _                        | _                                              |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'.

Shaded locations are unimplemented, read as '0'.

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

- 5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

- 6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

Note 1: These registers can be addressed from any bank.

<sup>2:</sup> The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that the PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

# EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

```

ORG 0x500

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

BCF PCLATH,4 ;Only on >4K devices

CALL SUB1_P1 ;Call subroutine in

;;page 1 (800h-FFFh)

;

ORG 0x900

SUB1_P1: ;called subroutine

;;page 1 (800h-FFFh)

;

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

```

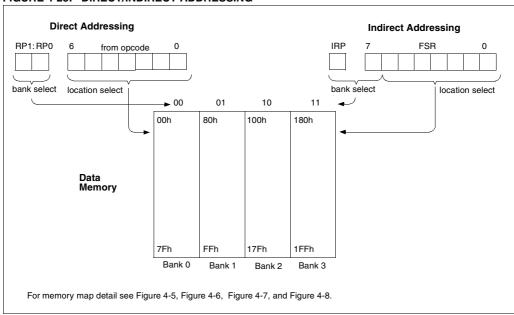

# 4.5 Indirect Addressing, INDF and FSR Registers

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-25.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

## **EXAMPLE 4-2: INDIRECT ADDRESSING**

```

movlw 0x20

;initialize pointer

movwf FSR

; to RAM

NEXT

clrf

INDF

;clear INDF register

FSR,F

incf

;inc pointer

btfss FSR,4

;all done?

;NO, clear next

goto NEXT

CONTINUE

;YES, continue

```

## FIGURE 4-25: DIRECT/INDIRECT ADDRESSING

# **5.0 I/O PORTS**

# Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Some pins for these I/O ports are multiplexed with an alternate function(s) for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

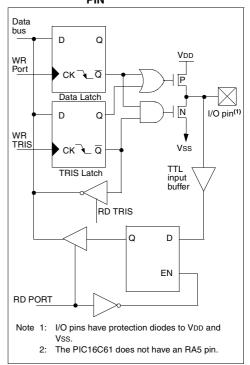

## 5.1 PORTA and TRISA Register

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

All devices have a 6-bit wide PORTA, except for the PIC16C61 which has a 5-bit wide PORTA.

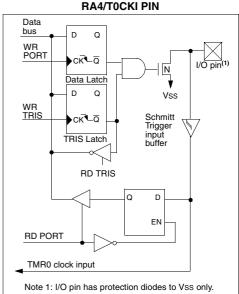

Pin RA4/T0CKI is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a bit in the TRISA register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch

Pin RA4 is multiplexed with Timer0 module clock input to become the RA4/T0CKI pin.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

```

BCF

STATUS, RP0

BCF

STATUS, RP1 ; PIC16C66/67 only

; Initialize PORTA by

CLRE

PORTA

: clearing output

; data latches

BSF

STATUS, RPO ; Select Bank 1

; Value used to

MOVLW

0xCF

: initialize data

: direction

MOVWF TRISA

; Set RA<3:0> as inputs

; RA<5:4> as outputs

; TRISA<7:6> are always

; read as '0'.

```

# FIGURE 5-1: BLOCK DIAGRAM OF THE RA3:RA0 PINS AND THE RA5 PIN

# FIGURE 5-2: BLOCK DIAGRAM OF THE

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recomended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

```

CLRF CCP1CON ; Turn CCP module off

MOVLW NEW_CAPT_PS; Load the W reg with

; the new prescaler

; mode value and CCP ON

MOVWF CCP1CON ; Load CCP1CON with

; this value

```

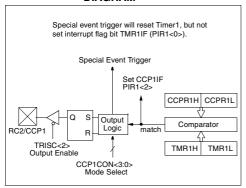

## 10.2 Compare Mode

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · Driven High

- · Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time interrupt flag bit CCP1IF is set.

# FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the data latch.

#### 10.2.1 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 10.2.2 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 10.2.3 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 and CCP2 resets the TMR1 register pair. This allows the CCPR1H:CCPR1L and CCPR2H:CCPR2L registers to effectively be 16-bit programmable period register(s) for Timer1.

For compatibility issues, the special event trigger output of CCP1 (<u>PIC16C72</u>) and CCP2 (all other PIC16C7X devices) also starts an A/D conversion.

Note: The "special event trigger" from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

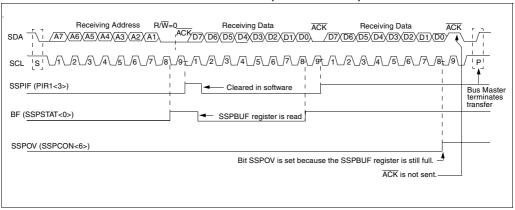

#### 11.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

## 12.4 <u>USART Synchronous Slave Mode</u>

## **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Synchronous Slave Mode differs from Master Mode in the fact that the shift clock is supplied externally at the CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

# 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

# 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, enable bit SREN is a don't care in slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

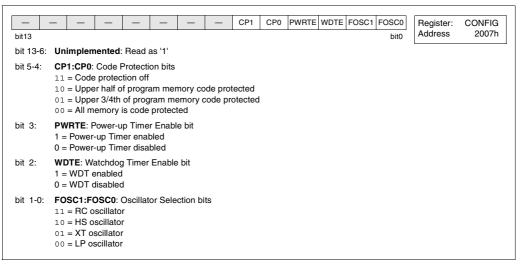

#### FIGURE 13-2: CONFIGURATION WORD FOR PIC16C62/64/65

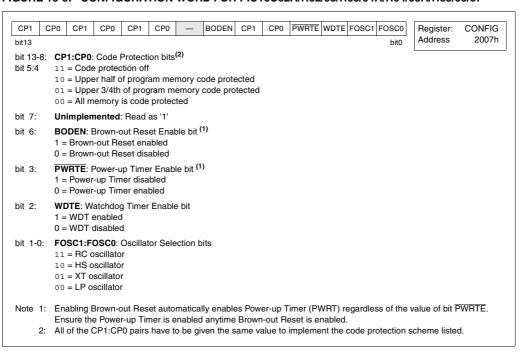

## FIGURE 13-3: CONFIGURATION WORD FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

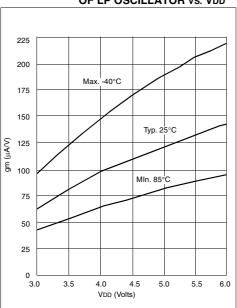

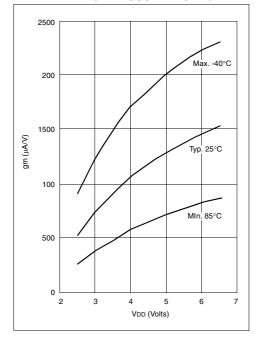

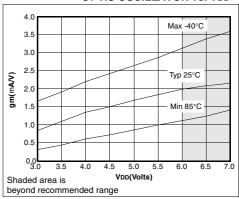

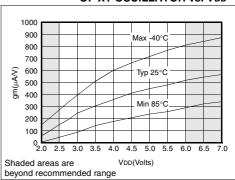

FIGURE 16-17: TRANSCONDUCTANCE (gm)

OF LP OSCILLATOR vs. VDD

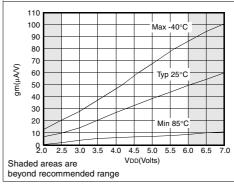

FIGURE 16-18: TRANSCONDUCTANCE (gm)

OF XT OSCILLATOR vs. VDD

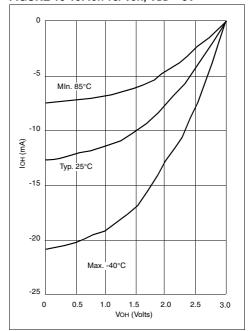

FIGURE 16-19: IOH VS. VOH, VDD = 3V

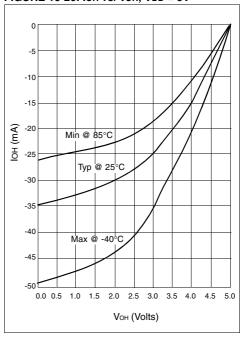

FIGURE 16-20: IOH VS. VOH, VDD = 5V

# PIC16C6X

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

17.1 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial)

> PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) DC CHARACTERISTICS Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$  for industrial and

|                       |                                                                   | •    |            |                    | 0°0            | 2 ≤                                    | TA ≤ +70°C for commercial                                                                                                |

|-----------------------|-------------------------------------------------------------------|------|------------|--------------------|----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                    | Sym  | Min        | Тур†               | Max            | Units                                  | Conditions                                                                                                               |

| D001<br>D001A         | Supply Voltage                                                    | VDD  | 4.0<br>4.5 | -                  | 6.0<br>5.5     | V<br>V                                 | XT, RC and LP osc configuration<br>HS osc configuration                                                                  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                            | VDR  | -          | 1.5                |                | ٧                                      |                                                                                                                          |

| D003                  | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR | -          | Vss                |                | V                                      | See section on Power-on Reset for details                                                                                |

| D004*                 | VDD rise rate to ensure internal Power-on Reset signal            | SVDD | 0.05       | -                  |                | V/ms                                   | See section on Power-on Reset for details                                                                                |

| D010                  | Supply Current (Note 2, 5)                                        | IDD  | -          | 2.7                | 5.0            | mA                                     | XT, RC, osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                           |

| D013                  |                                                                   |      | -          | 13.5               | 30             | mA                                     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                        |

| D020<br>D021<br>D021A | Power-down Current (Note 3, 5)                                    | IPD  | -          | 10.5<br>1.5<br>1.5 | 42<br>21<br>24 | μ <b>Α</b><br>μ <b>Α</b><br>μ <b>Α</b> | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C |

- These parameters are characterized but not tested.

- Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSs.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

DC CHARACTERISTICS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

17.3 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial)

> PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial) PIC16LC62/64-04 (Commercial, Industrial)

> > Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C  $\leq$  TA  $\leq$  +85°C for industrial and

0°C

$\leq$  TA  $\leq$  +70°C for commercial Operating voltage VDD range as described in DC spec Section 17.1

|              |                                    | and Sed | ction 17.2        |          | -       |       | ·                                                                                              |

|--------------|------------------------------------|---------|-------------------|----------|---------|-------|------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                     | Sym     | Min               | Typ<br>† | Max     | Units | Conditions                                                                                     |

|              | Input Low Voltage                  |         |                   |          |         |       |                                                                                                |

|              | I/O ports                          | VIL     |                   |          |         |       |                                                                                                |

| D030         | with TTL buffer                    |         | Vss               | -        | 0.15VDD | V     | For entire VDD range                                                                           |

| D030A        |                                    |         | Vss               | -        | V8.0    | V     | $4.5V \le VDD \le 5.5V$                                                                        |

| D031         | with Schmitt Trigger buffer        |         | Vss               | -        | 0.2VDD  | V     |                                                                                                |

| D032         | MCLR, OSC1 (in RC mode)            |         | Vss               | -        | 0.2VDD  | V     |                                                                                                |

| D033         | OSC1 (in XT, HS and LP)            |         | Vss               | -        | 0.3VDD  | V     | Note1                                                                                          |

|              | Input High Voltage                 |         |                   |          |         |       |                                                                                                |

|              | I/O ports                          | VIH     |                   |          |         |       |                                                                                                |

| D040         | with TTL buffer                    |         | 2.0               | -        | VDD     | V     | $4.5V \le V_{DD} \le 5.5V$                                                                     |

| D040A        |                                    |         | 0.25VDD<br>+ 0.8V | -        | VDD     | V     | For entire VDD range                                                                           |

| D041         | with Schmitt Trigger buffer        |         | 0.8VDD            | -        | VDD     |       | For entire VDD range                                                                           |

| D042         | MCLR                               |         | 0.8VDD            | -        | VDD     | V     |                                                                                                |

| D042A        | OSC1 (XT, HS and LP)               |         | 0.7VDD            | -        | VDD     | V     | Note1                                                                                          |

| D043         | OSC1 (in RC mode)                  |         | 0.9VDD            | -        | VDD     | V     |                                                                                                |

| D070         | PORTB weak pull-up current         | IPURB   | 50                | 200      | 400     | μΑ    | VDD = 5V, VPIN = VSS                                                                           |

|              | Input Leakage Current (Notes 2, 3) |         |                   |          |         |       |                                                                                                |

| D060         | I/O ports                          | lı∟     | -                 | -        | ±1      | μА    | $Vss \leq VPIN \leq VDD, Pin at hi-impedance$                                                  |

| D061         | MCLR, RA4/T0CKI                    |         | -                 | -        | ±5      | μΑ    | $Vss \le VPIN \le VDD$                                                                         |

| D063         | OSC1                               |         | -                 | -        | ±5      | μА    | $Vss \leq VPIN \leq VDD, \ XT, \ HS \ and \\ LP \ osc \ configuration$                         |

|              | Output Low Voltage                 |         |                   |          |         |       |                                                                                                |

| D080         | I/O ports                          | VOL     | -                 | -        | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                    |

| D083         | OSC2/CLKOUT (RC osc config)        |         | -                 | -        | 0.6     | V     | IOL = $1.6 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

|              | Output High Voltage                |         |                   |          |         |       |                                                                                                |

| D090         | I/O ports (Note 3)                 | Vон     | VDD-0.7           | -        | -       | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                           |

| D092         | OSC2/CLKOUT (RC osc config)        |         | VDD-0.7           | -        | -       | V     | IOH = $-1.3$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                           |

| D150*        | Open-Drain High Voltage            | Vod     | -                 | -        | 14      | V     | RA4 pin                                                                                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

# 18.5 <u>Timing Diagrams and Specifications</u>

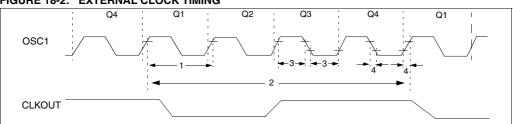

FIGURE 18-2: EXTERNAL CLOCK TIMING

TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         |     |      |        |       |                    |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2                | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# PIC16C6X

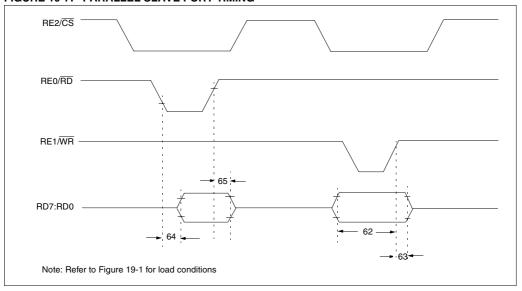

FIGURE 19-7: PARALLEL SLAVE PORT TIMING

TABLE 19-7: PARALLEL SLAVE PORT REQUIREMENTS

| Parameter No. | Sym      | Characteristic                               |                    |    | Тур† | Max | Units | Conditions |

|---------------|----------|----------------------------------------------|--------------------|----|------|-----|-------|------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS↑ (setup time) |                    | 20 | _    | _   | ns    |            |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data–in invalid (hold          | PIC16 <b>C</b> 65  | 20 | _    | _   | ns    |            |

|               |          | time)                                        | PIC16 <b>LC</b> 65 | 35 | _    | _   | ns    |            |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid                |                    | _  | _    | 80  | ns    |            |

| 65            | TrdH2dtl | RD↑ or CS↑ to data–out invalid               |                    | 10 | _    | 30  | ns    |            |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

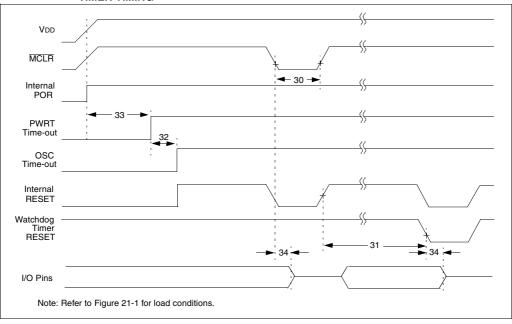

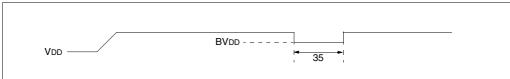

FIGURE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

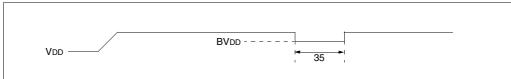

FIGURE 21-5: BROWN-OUT RESET TIMING

TABLE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                | Min | Typ†      | Max | Units | Conditions                |

|---------------|-------|-----------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                        | 2   | _         |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32            | Tost  | Oscillation Start-up Timer Period             |     | 1024 Tosc |     | _     | TOSC = OSC1 period        |

| 33*           | Tpwrt | Power-up Timer Period                         | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34            | Tıoz  | I/O Hi-impedance from MCLR Low or WDT reset   | _   | _         | 2.1 | μs    |                           |

| 35            | TBOR  | Brown-out Reset Pulse Width                   | 100 | _         | _   | μs    | VDD ≤ BVDD (D005)         |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

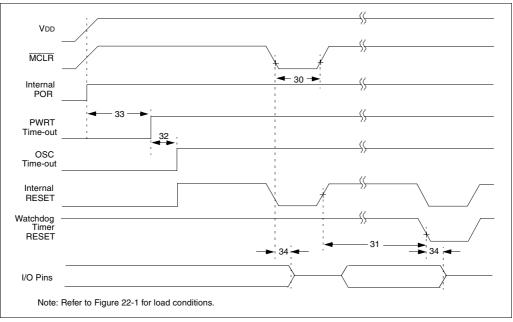

FIGURE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

FIGURE 22-5: BROWN-OUT RESET TIMING

TABLE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                | Min | Typ†      | Max | Units | Conditions                |

|------------------|-------|-----------------------------------------------|-----|-----------|-----|-------|---------------------------|

|                  |       |                                               |     |           |     |       |                           |

| 30               | TmcL  | MCLR Pulse Width (low)                        | 2   | _         | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period             |     | 1024 Tosc | _   | _     | TOSC = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                         | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or WDT reset   | -   | _         | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset Pulse Width                   | 100 | -         | _   | μs    | VDD ≤ BVDD (D005)         |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

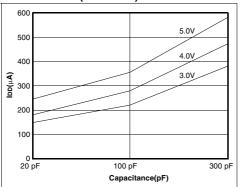

FIGURE 23-18: TYPICAL IDD vs.

CAPACITANCE @ 500 kHz

(RC MODE)

TABLE 23-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average    |        |  |  |  |

|--------|------|------------|--------|--|--|--|

| Cext   | next | Fosc @ 5V, | 25°C   |  |  |  |

| 22 pF  | 5k   | 4.12 MHz   | ± 1.4% |  |  |  |

|        | 10k  | 2.35 MHz   | ± 1.4% |  |  |  |

|        | 100k | 268 kHz    | ± 1.1% |  |  |  |

| 100 pF | 3.3k | 1.80 MHz   | ± 1.0% |  |  |  |

|        | 5k   | 1.27 MHz   | ± 1.0% |  |  |  |

|        | 10k  | 688 kHz    | ± 1.2% |  |  |  |

|        | 100k | 77.2 kHz   | ± 1.0% |  |  |  |

| 300 pF | 3.3k | 707 kHz    | ± 1.4% |  |  |  |

|        | 5k   | 501 kHz    | ± 1.2% |  |  |  |

|        | 10k  | 269 kHz    | ± 1.6% |  |  |  |

|        | 100k | 28.3 kHz   | ± 1.1% |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

FIGURE 23-19: TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

FIGURE 23-20: TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

# FIGURE 23-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

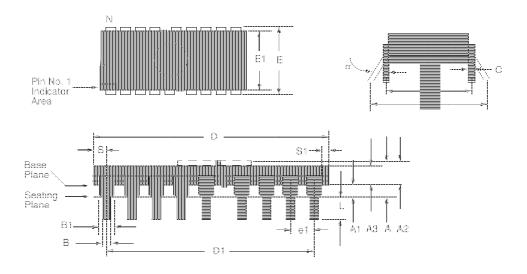

# 24.8 40-Lead Ceramic CERDIP Dual In-line with Window (600 mil) (JW)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |           |       |        |           |  |  |  |  |

|--------|--------------------------------------------------|-------------|-----------|-------|--------|-----------|--|--|--|--|

|        |                                                  | Millimeters |           |       | Inches | hes       |  |  |  |  |

| Symbol | Min                                              | Max         | Notes     | Min   | Max    | Notes     |  |  |  |  |

| α      | 0°                                               | 10°         |           | 0°    | 10°    |           |  |  |  |  |

| Α      | 4.318                                            | 5.715       |           | 0.170 | 0.225  |           |  |  |  |  |

| A1     | 0.381                                            | 1.778       |           | 0.015 | 0.070  |           |  |  |  |  |

| A2     | 3.810                                            | 4.699       |           | 0.150 | 0.185  |           |  |  |  |  |

| А3     | 3.810                                            | 4.445       |           | 0.150 | 0.175  |           |  |  |  |  |

| В      | 0.355                                            | 0.585       |           | 0.014 | 0.023  |           |  |  |  |  |

| B1     | 1.270                                            | 1.651       | Typical   | 0.050 | 0.065  | Typical   |  |  |  |  |

| С      | 0.203                                            | 0.381       | Typical   | 0.008 | 0.015  | Typical   |  |  |  |  |

| D      | 51.435                                           | 52.705      |           | 2.025 | 2.075  |           |  |  |  |  |

| D1     | 48.260                                           | 48.260      | Reference | 1.900 | 1.900  | Reference |  |  |  |  |

| E      | 15.240                                           | 15.875      |           | 0.600 | 0.625  |           |  |  |  |  |

| E1     | 12.954                                           | 15.240      |           | 0.510 | 0.600  |           |  |  |  |  |

| e1     | 2.540                                            | 2.540       | Reference | 0.100 | 0.100  | Reference |  |  |  |  |

| eA     | 14.986                                           | 16.002      | Typical   | 0.590 | 0.630  | Typical   |  |  |  |  |

| eB     | 15.240                                           | 18.034      |           | 0.600 | 0.710  |           |  |  |  |  |

| L      | 3.175                                            | 3.810       |           | 0.125 | 0.150  |           |  |  |  |  |

| N      | 40                                               | 40          |           | 40    | 40     |           |  |  |  |  |

| S      | 1.016                                            | 2.286       |           | 0.040 | 0.090  |           |  |  |  |  |

| S1     | 0.381                                            | 1.778       |           | 0.015 | 0.070  |           |  |  |  |  |

### **APPENDIX A: MODIFICATIONS**

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits.

This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- Data memory paging is redefined slightly. STA-TUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- OPTION and TRIS registers are made addressable.

- Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- Wake-up from SLEEP through interrupt is added

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT), are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. Timer0 pin is also a port pin (RA4/T0CKI) now.

- 14. FSR is made a full 8-bit register.

- "In-circuit programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, VPP, RB6 (clock) and RB7 (data in/out).

- Power Control register (PCON) is added with a Power-on Reset status bit (POR). (Not on the PIC16C61).

- Brown-out Reset has been added to the following devices:

PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67.

## APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO

- Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- Eliminate any data memory page switching. Redefine data variables to reallocate them.

- Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

## **APPENDIX C: WHAT'S NEW**

Added PIC16CR63 and PIC16CR65 devices.

Added PIC16C66 and PIC16C67 devices. The PIC16C66/67 devices have 368 bytes of data memory distributed in 4 banks and 8K of program memory in 4 pages. These two devices have an enhanced SPI that supports both clock phase and polarity. The USART has been enhanced.

When upgrading to the PIC16C66/67 please note that the upper 16 bytes of data memory in banks 1,2, and 3 are mapped into bank 0. This may require relocation of data memory usage in the user application code.

Q-cycles for instruction execution were added to Section 14.0 Instruction Set Summary.

# **APPENDIX D: WHAT'S CHANGED**

Minor changes, spelling and grammatical changes.

Divided SPI section into SPI for the PIC16C66/67 (Section 11.3) and SPI for all other devices (Section 11.2).

Added the following note for the USART. This applies to all devices except the PIC16C66 and PIC16C67.

For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

# APPENDIX E: REVISION E

January 2013 - Added a note to each package drawing.

NOTES:

# PIC16C6X

| Table 18-1:  | Cross Reference of Device Specs             | Table 20-12: | USART Synchronous Receive                     |      |

|--------------|---------------------------------------------|--------------|-----------------------------------------------|------|

|              | for Oscillator Configurations and           |              | Requirements                                  | 230  |

|              | Frequencies of Operation                    | Table 21-1:  | Cross Reference of Device                     |      |

|              | (Commercial Devices)183                     |              | Specs for Oscillator Configurations           |      |

| Table 18-2:  | External Clock Timing                       |              | and Frequencies of Operation                  |      |

|              | Requirements189                             |              | (Commercial Devices)                          | 231  |

| Table 18-3:  | CLKOUT and I/O Timing                       | Table 21-2:  | External Clock Timing                         |      |

|              | Requirements190                             |              | Requirements                                  | 237  |

| Table 18-4:  | Reset, Watchdog Timer,                      | Table 21-3:  | CLKOUT and I/O Timing                         |      |

|              | Oscillator Start-up Timer and               |              | Requirements                                  | 238  |

|              | Power-up Timer Requirements191              | Table 21-4:  | Reset, Watchdog Timer, Oscillator             |      |

| Table 18-5:  | Timer0 and Timer1 External                  |              | Start-up Timer, Power-up Timer, and           |      |

|              | Clock Requirements                          |              | Brown-out Reset Requirements                  | 239  |

| Table 18-6:  | Capture/Compare/PWM                         | Table 21-5:  | Timer0 and Timer1 External                    |      |

|              | Requirements (CCP1)                         |              | Clock Requirements                            | 240  |

| Table 18-7:  | Parallel Slave Port Requirements (PIC16C64) | Table 21-6:  | Capture/Compare/PWM                           |      |

|              | 194                                         |              | Requirements (CCP1 and CCP2)                  | 241  |

| Table 18-8:  | SPI Mode Requirements195                    | Table 21-7:  | Parallel Slave Port Requirements              |      |

| Table 18-9:  | I <sup>2</sup> C Bus Start/Stop Bits        |              | (PIC16C65A)                                   | 242  |

|              | Requirements                                | Table 21-8:  | SPI Mode Requirements                         |      |

| Table 18-10: | I <sup>2</sup> C Bus Data Requirements197   | Table 21-9:  | I <sup>2</sup> C Bus Start/Stop Bits          | 2 10 |

| Table 19-1:  | Cross Reference of Device Specs             |              | Requirements                                  | 244  |

| 10010 10 1.  | for Oscillator Configurations and           | Table 21-10: | I <sup>2</sup> C Bus Data Requirements        |      |

|              | Frequencies of Operation                    | Table 21-11: | USART Synchronous                             | 2 10 |

|              | (Commercial Devices)199                     | Table 21 11. | Transmission Requirements                     | 246  |

| Table 19-2:  | External Clock Timing                       | Table 21-12: | USART Synchronous Receive                     | 240  |

| Table 13-2.  | Requirements205                             | Table 21-12. | Requirements                                  | 246  |

| Table 19-3:  | CLKOUT and I/O Timing                       | Table 22-1:  | Cross Reference of Device Specs               | 240  |

| Table 13-3.  | Requirements206                             | Table 22-1.  | for Oscillator Configurations and             |      |

| Table 19-4:  | Reset, Watchdog Timer,                      |              | Frequencies of Operation                      |      |

| Table 13-4.  | Oscillator Start-up Timer,                  |              | (Commercial Devices)                          | 247  |

|              | Power-up Timer, and Brown-out               | Table 22-2:  | External Clock Timing                         | 241  |

|              | ·                                           | Table 22-2.  | ğ .                                           | 050  |

| Toble 10 Fr  | Reset Requirements                          | Table 00 0   | Requirements CLKOUT and I/O Timing            | 253  |

| Table 19-5:  | Timer0 and Timer1 External                  | Table 22-3:  | ě .                                           | 054  |

| T-bl- 10 C   | Clock Requirements                          | T-bl- 00 4:  | Requirements                                  | 254  |

| Table 19-6:  | Capture/Compare/PWM                         | Table 22-4:  | Reset, Watchdog Timer,                        |      |

| Table 10.7   | Requirements (CCP1)                         |              | Oscillator Start-up Timer,                    |      |

| Table 19-7:  | Parallel Slave Port Requirements            |              | Power-up Timer, and Brown-out                 | OFF  |

| Table 19-8:  | (PIC16C64A/R64)210                          | Table 22-5:  | Reset Requirements Timer0 and Timer1 External | 255  |

|              | SPI Mode Requirements211                    | Table 22-5.  |                                               | 056  |

| Table 19-9:  | I <sup>2</sup> C Bus Start/Stop Bits        | T-bl- 00 C   | Clock Requirements                            | 256  |

| T-bl- 10 10. | Requirements                                | Table 22-6:  | Capture/Compare/PWM                           | 057  |

| Table 19-10: | I <sup>2</sup> C Bus Data Requirements      | T-bl- 00 7.  | Requirements (CCP1 and CCP2)                  | 257  |

| Table 20-1:  | Cross Reference of Device Specs             | Table 22-7:  | Parallel Slave Port Requirements              | 050  |

|              | for Oscillator Configurations and           | T-bl- 00 0.  | (PIC16CR65)                                   |      |

|              | Frequencies of Operation                    | Table 22-8:  | SPI Mode Requirements                         | 259  |

| T-1-1- 00 0  | (Commercial Devices)                        | Table 22-9:  | I <sup>2</sup> C Bus Start/Stop Bits          | 000  |

| Table 20-2:  | External Clock Timing                       | T-1-1- 00 40 | Requirements                                  |      |

| <b>T</b>     | Requirements                                | Table 22-10: | I <sup>2</sup> C Bus Data Requirements        | 261  |

| Table 20-3:  | CLKOUT and I/O Timing                       | Table 22-11: | USART Synchronous Transmission                |      |

| T            | Requirements                                | T 11 00 10   | Requirements                                  | 262  |

| Table 20-4:  | Reset, Watchdog Timer,                      | Table 22-12: | USART Synchronous Receive                     |      |

|              | Oscillator Start-up Timer and               | T            | Requirements                                  | 262  |

| T            | Power-up Timer Requirements223              | Table 23-1:  | Cross Reference of Device Specs               |      |

| Table 20-5:  | Timer0 and Timer1 External                  |              | for Oscillator Configurations and             |      |

|              | Clock Requirements                          |              | Frequencies of Operation                      |      |

| Table 20-6:  | Capture/Compare/PWM                         |              | (Commercial Devices)                          | 263  |

|              | Requirements (CCP1 and CCP2)225             | Table 23-2:  | External Clock Timing                         |      |

| Table 20-7:  | Parallel Slave Port Requirements226         |              | Requirements                                  | 269  |

| Table 20-8:  | SPI Mode Requirements227                    | Table 23-3:  | CLKOUT and I/O Timing                         |      |

| Table 20-9:  | I <sup>2</sup> C Bus Start/Stop Bits        | _ ,          | Requirements                                  | 270  |

|              | Requirements                                | Table 23-4:  | Reset, Watchdog Timer,                        |      |

| Table 20-10: | i <sup>2</sup> C Bus Data Requirements229   |              | Oscillator Start-up Timer,                    |      |

| Table 20-11: | USART Synchronous Transmission              |              | Power-up Timer, and Brown-out                 |      |

|              | Requirements230                             |              | Reset Requirements                            | 271  |