Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc67-04-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7                                                    | Bit 6              | Bit 5          | Bit 4          | Bit 3         | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|----------------------------------------------------------|--------------------|----------------|----------------|---------------|-----------------|--------------|-------------|--------------------------|------------------------------------------------|

| Bank 0               |         |                                                          |                    |                |                |               |                 |              |             |                          |                                                |

| 00h <sup>(1)</sup>   | INDF    | Addressing                                               | this location      | uses conten    | ts of FSR to   | address data  | a memory (n     | ot a physica | l register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod                                               | lule's registe     |                | xxxx xxxx      | uuuu uuuu     |                 |              |             |                          |                                                |

| 02h <sup>(1)</sup>   | PCL     | Program Co                                               | ounter's (PC)      |                | 0000 0000      | 0000 0000     |                 |              |             |                          |                                                |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>                                       | RP1 <sup>(5)</sup> | RP0            | TO             | PD            | Z               | DC           | С           | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                                            | a memory ad        |                | xxxx xxxx      | uuuu uuuu     |                 |              |             |                          |                                                |

| 05h                  | PORTA   | —                                                        | —                  |                | xx xxxx        | uu uuuu       |                 |              |             |                          |                                                |

| 06h                  | PORTB   | PORTB Dat                                                | ta Latch whe       | n written: PC  | ORTB pins wi   | nen read      |                 |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat                                                | ta Latch whe       | n written: PC  | ORTC pins w    | hen read      |                 |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  |         | Unimpleme                                                | Unimplemented      |                |                |               |                 |              |             |                          |                                                |

| 09h                  |         | Unimplemented                                            |                    |                |                |               |                 |              |             |                          | _                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                                                        | _                  | _              | Write Buffer   | for the uppe  | r 5 bits of the | e Program C  | ounter      | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                                      | PEIE               | TOIE           | INTE           | RBIE          | TOIF            | INTF         | RBIF        | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | (6)                                                      | (6)                | _              | 1              | SSPIF         | CCP1IF          | TMR2IF       | TMR1IF      | 00 0000                  | 00 0000                                        |

| 0Dh                  |         | Unimpleme                                                | nted               |                |                |               |                 |              |             | _                        | _                                              |

| 0Eh                  | TMR1L   | Holding reg                                              | ister for the L    | east Signific  | ant Byte of t  | he 16-bit TM  | R1 register     |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg                                              | ister for the M    | /lost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                                                        | —                  | T1CKPS1        | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS       | TMR10N      | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod                                               | lule's registe     | r              |                |               |                 |              |             | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | —                                                        | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1      | T2CKPS0     | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |                    |                |                |               |                 |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                                                     | SSPOV              | SSPM0          | 0000 0000      | 0000 0000     |                 |              |             |                          |                                                |

| 15h                  | CCPR1L  | Capture/Compare/PWM1 (LSB)                               |                    |                |                |               |                 |              |             | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Compare/PWM1 (MSB)                               |                    |                |                |               |                 |              |             |                          | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                                                        | —                  | CCP1M0         | 00 0000        | 00 0000       |                 |              |             |                          |                                                |

| 18h-1Fh              | _       | Unimpleme                                                | nted               |                |                |               |                 |              |             | _                        | _                                              |

#### TABLE 4-2: SPECIAL FUNCTION REGISTERS FOR THE PIC16C62/62A/R62

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C62, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

6: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

| Address              | Name    | Bit 7                        | Bit 6                                              | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|------------------------------|----------------------------------------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                              |                                                    |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing                   | this location                                      | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod                   | lule's registe                                     | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co                   | ounter's (PC)                                      | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>           | RP1 <sup>(5)</sup>                                 | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                | a memory ad                                        | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   |                              | _                                                  | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat                    | ta Latch whe                                       | n written: PC | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat                    | ORTC Data Latch when written: PORTC pins when read |               |                |               |                 |               |           |                          | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat                    | ORTD Data Latch when written: PORTD pins when read |               |                |               |                 |               |           |                          | uuuu uuuu                                      |

| 09h                  | PORTE   |                              | RE2 RE1 RE0                                        |               |                |               |                 |               |           |                          | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                            | —                                                  | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                          | PEIE                                               | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF                        | (6)                                                | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                              | _                                                  | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg                  | ister for the L                                    | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg                  | ister for the M                                    | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                              | _                                                  | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod                   | lule's registe                                     | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                            | TOUTPS3                                            | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou                   | is Serial Port                                     | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                         | SSPOV                                              | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co                   | mpare/PWM                                          | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co                   | mpare/PWM                                          | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                            | —                                                  | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                         | RX9                                                | SREN          | CREN           | —             | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Transmit Data Register |                                                    |               |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Receive Data Register  |                                                    |               |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co                   | Capture/Compare/PWM2 (LSB)                         |               |                |               |                 |               |           |                          | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  |                              |                                                    |               |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                            | —                                                  | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme                    | nted                                               |               |                |               |                 |               |           | —                        | _                                              |

#### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

| TABLE                | 4-6:    | SPECIA                       |                | TION RE                   | GISTERS        | S FOR T      | HE PIC1          | 6C66/67       | (Cont.'c  | I)                       |                                                |

|----------------------|---------|------------------------------|----------------|---------------------------|----------------|--------------|------------------|---------------|-----------|--------------------------|------------------------------------------------|

| Address              | Name    | Bit 7                        | Bit 6          | Bit 5                     | Bit 4          | Bit 3        | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

| Bank 1               |         |                              |                |                           |                |              |                  |               |           |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing                   | this location  | uses conte                | nts of FSR to  | address dat  | a memory (n      | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU                         | INTEDG         | TOCS                      | T0SE           | PSA          | PS2              | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co                   | ounter's (PC)  | Least Sig                 | nificant Byte  |              |                  |               |           | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP                          | RP1            | RP0                       | TO             | PD           | Z                | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data                | a memory ad    | dress point               | er             |              |                  |               | 1         | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                            | _              | PORTA Da                  | ta Direction R | legister     |                  |               |           | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat                    | ta Direction I | Register                  |                |              |                  |               |           | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Dat                    | ta Direction   | Register                  |                |              |                  |               |           | 1111 1111                | 1111 1111                                      |

| 88h <sup>(5)</sup>   | TRISD   | PORTD Dat                    | ta Direction   | Register                  |                |              |                  |               |           | 1111 1111                | 1111 1111                                      |

| 89h <sup>(5)</sup>   | TRISE   | IBF                          | OBF            | Bits                      | 0000 -111      | 0000 -111    |                  |               |           |                          |                                                |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                            | —              | —                         | Write Buffer   | for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                          | PEIE           | TOIE                      | INTE           | RBIE         | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | PSPIE <sup>(6)</sup>         | (4)            | RCIE                      | TXIE           | SSPIE        | CCP1IE           | TMR2IE        | TMR1IE    | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                            | _              | _                         | _              | —            | _                | _             | CCP2IE    | 0                        | 0                                              |

| 8Eh                  | PCON    | —                            | —              | —                         | -              | _            | _                | POR           | BOR       | dd                       | uu                                             |

| 8Fh                  | -       | Unimpleme                    | nted           |                           |                |              | •                |               |           | -                        | _                                              |

| 90h                  |         | Unimpleme                    | nted           |                           |                |              |                  |               |           | _                        | _                                              |

| 91h                  | -       | Unimpleme                    | nted           |                           |                |              |                  |               |           | -                        | —                                              |

| 92h                  | PR2     | Timer2 Peri                  | od Register    |                           |                |              |                  |               |           | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou                   | us Serial Por  | t (I <sup>2</sup> C mode) | Address Reg    | gister       |                  |               |           | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | SMP                          | CKE            | D/A                       | Р              | S            | R/W              | UA            | BF        | 0000 0000                | 0000 0000                                      |

| 95h                  | -       | Unimpleme                    | nted           |                           |                |              |                  |               |           | _                        | —                                              |

| 96h                  | -       | Unimpleme                    | nted           |                           |                |              |                  |               |           | _                        | —                                              |

| 97h                  | -       | Unimpleme                    | nted           |                           |                |              |                  |               |           | _                        | —                                              |

| 98h                  | TXSTA   | CSRC                         | TX9            | TXEN                      | SYNC           | —            | BRGH             | TRMT          | TX9D      | 0000 -010                | 0000 -010                                      |

| 99h                  | SPBRG   | Baud Rate Generator Register |                |                           |                |              |                  |               |           |                          | 0000 0000                                      |

| 9Ah                  | -       | Unimplemented                |                |                           |                |              |                  |               |           |                          | _                                              |

| 9Bh                  | _       | Unimpleme                    | nted           |                           | -              | —            |                  |               |           |                          |                                                |

| 9Ch                  | _       | Unimpleme                    | nted           |                           |                |              |                  |               |           | —                        | _                                              |

| 9Dh                  | —       | Unimpleme                    |                | —                         | —              |              |                  |               |           |                          |                                                |

| 9Eh                  | _       | Unimpleme                    | nted           |                           |                |              |                  |               |           | —                        | —                                              |

| 9Fh                  | -       | Unimpleme                    | nted           |                           |                |              |                  |               |           | -                        | -                                              |

TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

#### 4.2.2.5 PIR1 REGISTER

| Appli          | cable | e Dev | vice | es  |      |             |       |     |       |     |      |     |     |

|----------------|-------|-------|------|-----|------|-------------|-------|-----|-------|-----|------|-----|-----|

| 61 62          | 62A   | R62   | 63   | R63 | 64   | 64 <i>F</i> | R64   | 65  | 65A   | R65 | 5 66 | 67  |     |

| This<br>periph | 0     |       |      |     | IS 1 | the         | indiv | idu | al fl | ag  | bits | for | the |

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-16: PIR1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 0Ch)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                           | U-0          | U-0          | R/W-0                       | R/W-0                   | R/W-0         | R/W-0  |                                                                                       |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------------------------|-------------------------|---------------|--------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| _        | -                                                                                                                                                                                                                                                                                                                                                                               | _            | _            | SSPIF                       | CCP1IF                  | TMR2IF        | TMR1IF | R = Readable bit                                                                      |  |  |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                 |              |              |                             |                         |               | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |  |  |

| bit 7-6: | Reserved:                                                                                                                                                                                                                                                                                                                                                                       | Always ma    | aintain thes | e bits clear.               |                         |               |        | LI                                                                                    |  |  |  |  |  |

| bit 5-4: | Unimplem                                                                                                                                                                                                                                                                                                                                                                        | ented: Rea   | ad as '0'    |                             |                         |               |        |                                                                                       |  |  |  |  |  |

| bit 3:   | 1 = The tra                                                                                                                                                                                                                                                                                                                                                                     | nsmission/   | reception is | Interrupt Fla<br>complete ( | ag bit<br>(must be clea | ared in softw | vare)  |                                                                                       |  |  |  |  |  |

| bit 2:   | 0 = Waiting to transmit/receive<br>CCP1IF: CCP1 Interrupt Flag bit<br>Capture Mode<br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br>Compare Mode<br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br>PWM Mode<br>Unused in this mode |              |              |                             |                         |               |        |                                                                                       |  |  |  |  |  |

| bit 1:   |                                                                                                                                                                                                                                                                                                                                                                                 | to PR2 mat   | tch occurre  | •                           | bit<br>cleared in so    | ftware)       |        |                                                                                       |  |  |  |  |  |

| bit 0:   | <b>TMR1IF</b> : T<br>1 = TMR1<br>0 = No TM                                                                                                                                                                                                                                                                                                                                      | register ove | erflow occu  | rred (must b                | be cleared in           | software)     |        |                                                                                       |  |  |  |  |  |

| globa    |                                                                                                                                                                                                                                                                                                                                                                                 | GIE (INTC    |              |                             |                         |               |        | corresponding enable bit or the rupt flag bits are clear prior to                     |  |  |  |  |  |

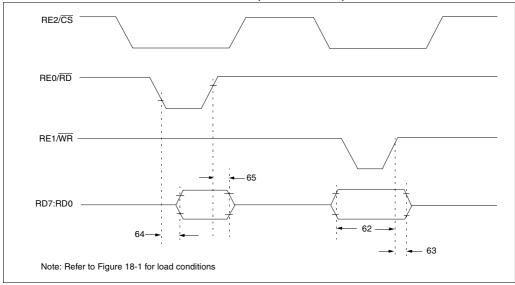

#### 5.4 PORTD and TRISD Register

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

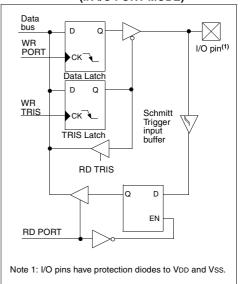

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

#### TABLE 5-9: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port mode.

#### TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7   | Bit 6      | Bit 5          | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|------------|----------------|---------|-------|----------|--------------|-----------|--------------------------|---------------------------|

| 08h     | PORTD | RD7     | RD6        | RD5            | RD4     | RD3   | RD2      | RD1          | RD0       | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORTD I | Data Direc | ction Register |         |       |          |              |           | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF     | OBF        | IBOV           | PSPMODE | _     | PORTE Da | ata Directio | 0000 -111 | 0000 -111                |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

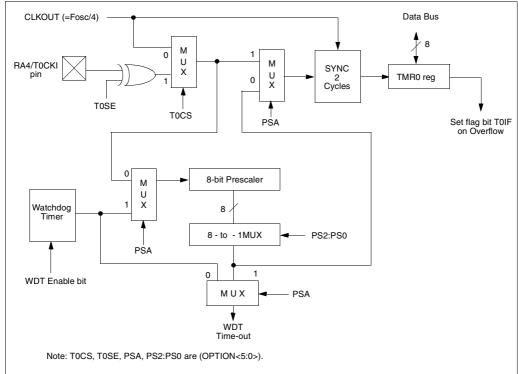

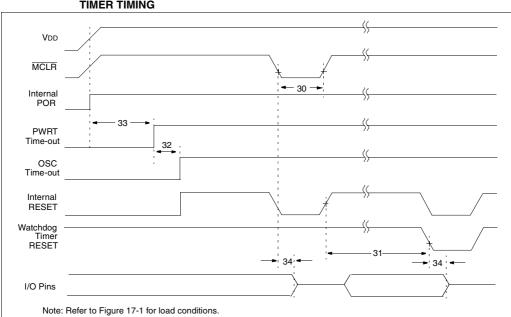

#### 7.3 Prescaler

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF TMR0, MOVWF TMR0, BSF TMR0, bitx) will clear the prescaler count. When assigned to the Watchdog Timer, a CLRWDT instruction will clear the Watchdog Timer and the prescaler count. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

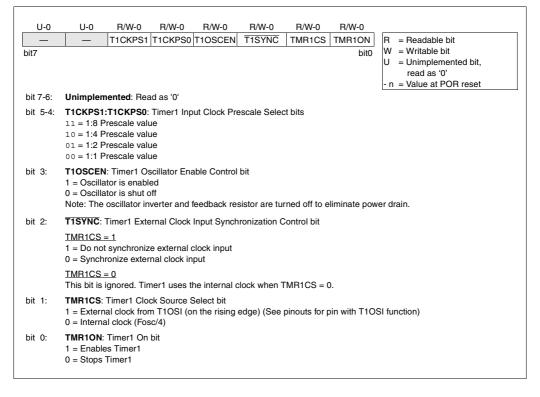

## 8.0 TIMER1 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

#### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

#### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0 R/W-0 R            | /W-0 R/W-0         | R/W-0        | R/W-0         | R/W-0        |                                       |

|----------|------------------------|--------------------|--------------|---------------|--------------|---------------------------------------|

| —        | - CCPxX CC             | CPxY CCPxM3        | CCPxM2       | CCPxM1        | CCPxM0       | R = Readable bit                      |

| bit7     |                        |                    |              |               | bit0         | W = Writable bit                      |

|          |                        |                    |              |               |              | U = Unimplemented bit, read<br>as '0' |

|          |                        |                    |              |               |              | - n =Value at POR reset               |

| bit 7-6: | Unimplemented: F       | Poad as '0'        |              |               |              |                                       |

|          | •                      |                    |              |               |              |                                       |

| bit 5-4: | CCPxX:CCPxY: PV        | VM Least Significa | ant bits     |               |              |                                       |

|          | Capture Mode<br>Unused |                    |              |               |              |                                       |

|          | Compare Mode           |                    |              |               |              |                                       |

|          | Unused                 |                    |              |               |              |                                       |

|          | PWM Mode               |                    |              |               |              |                                       |

|          | These bits are the t   | wo LSbs of the P   | NM duty cy   | cle. The eig  | ht MSbs are  | found in CCPRxL.                      |

| bit 3-0: | CCPxM3:CCPxM0          | : CCPx Mode Sele   | ect bits     |               |              |                                       |

|          | 0000 = Capture/Co      | •                  |              | k module)     |              |                                       |

|          | 0100 = Capture mo      |                    | •            |               |              |                                       |

|          | 0101 = Capture mo      |                    | •            |               |              |                                       |

|          | 0110 = Capture mo      | · ·                | 0 0          |               |              |                                       |

|          | 1000 = Compare m       | · ·                | • •          | CCPxIF is     | set)         |                                       |

|          | 1001 = Compare m       |                    | •            |               | ,            |                                       |

|          | •                      |                    | •            |               | ,            | is set, CCPx pin is unaffected)       |

|          | •                      |                    | al event (CC | PxIF bit is s | et; CCP1 res | ets TMR1; CCP2 resets TMR1)           |

|          | 11xx = PWM mode        | 9                  |              |               |              |                                       |

|          |                        |                    |              |               |              |                                       |

#### 10.1 Capture Mode

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

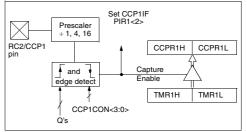

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1 (Figure 10-2). An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an   |

|-------|-------------------------------------------|

|       | output, a write to PORTC can cause a cap- |

|       | ture condition.                           |

# FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work consistently.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture event is changed, a false capture interrupt may be generated. The user should clear enable bit CCP1IE (PIE1<2>) to avoid false interrupts and should clear flag bit CCP1IF following any such change in operating mode.

#### EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 78.125 kHz, Fosc = 20 MHz TMR2 prescale = 1

$1/78.125 \text{ kHz} = [(PR2) + 1] \cdot 4 \cdot 1/20 \text{ MHz} \cdot 1$   $12.8 \ \mu s = [(PR2) + 1] \cdot 4 \cdot 50 \text{ ns} \cdot 1$ PR2 = 63

Find the maximum resolution of the duty cycle that can be used with a 78.125 kHz frequency and 20 MHz oscillator:

| 1/78.125 kHz | = $2^{\text{PWM RESOLUTION}} \cdot 1/20 \text{ MHz} \cdot 1$  |

|--------------|---------------------------------------------------------------|

| 12.8 µs      | = $2^{\text{PWM RESOLUTION}} \bullet 50 \text{ ns} \bullet 1$ |

| 256          | $= 2^{\text{PWM RESOLUTION}}$                                 |

| log(256)     | = (PWM Resolution) • $log(2)$                                 |

| 8.0          | = PWM Resolution                                              |

|              |                                                               |

At most, an 8-bit resolution duty cycle can be obtained from a 78.125 kHz frequency and a 20 MHz oscillator, i.e.,  $0 \leq$  CCPR1L:CCP1CON<5:4>  $\leq$  255. Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-3 lists example PWM frequencies and resolutions for Fosc = 20 MHz. The TMR2 prescaler and PR2 values are also shown.

10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 10-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 10-4: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Add                  | Name    | Bit 7                      | Bit 6                         | Bit 5               | Bit 4               | Bit 3                    | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|----------------------|---------|----------------------------|-------------------------------|---------------------|---------------------|--------------------------|------------|------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                        | PEIE                          | TOIE                | INTE                | RBIE                     | T0IF       | INTF       | RBIF   |      |                    | 0000  |                       |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup>       | (3)                           | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF                    | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 0Dh <sup>(4)</sup>   | PIR2    | —                          | _                             | _                   | _                   | -                        | -          | -          | CCP2IF |      | 0                  |       | 0                     |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup>       | (3)                           | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE                    | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 8Dh <sup>(4)</sup>   | PIE2    | —                          | _                             | _                   | _                   |                          | —          |            | CCP2IE |      | 0                  |       | 0                     |

| 87h                  | TRISC   | PORTC D                    | PORTC Data Direction register |                     |                     |                          |            |            |        |      |                    | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding re                 | egister for                   | the Least           | Significant         | Byte of the              | 16-bit TMF | R1 registe | r      | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding re                 | egister for                   | the Most S          | Significant I       | Byte of the <sup>·</sup> | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h                  | T1CON   | _                          | _                             | T1CKPS1             | T1CKPS0             | T1OSCEN                  | T1SYNC     | TMR1CS     | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/C                  | Compare/                      | PWM1 (LS            | B)                  |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture/C                  | Compare/                      | PWM1 (MS            | SB)                 |                          |            |            |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                  | CCP1CON | —                          | _                             | CCP1X               | CCP1Y               | CCP1M3                   | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00    | 0000                  |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/Compare/PWM2 (LSB) |                               |                     |                     |                          |            |            |        |      | xxxx               | uuuu  | uuuu                  |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/C                  |                               | xxxx                | xxxx                | uuuu                     | uuuu       |            |        |      |                    |       |                       |

| 1Dh <sup>(4)</sup>   | CCP2CON | —                          | _                             | CCP2X               | CCP2Y               | CCP2M3                   | CCP2M2     | CCP2M1     | CCP2M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

#### 11.3 SPI Mode for PIC16C66/67

This section contains register definitions and operational characterisitics of the SPI module on the PIC16C66 and PIC16C67 only.

#### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C66/67)

| R/W-0  | R/W-0                                                            | R-0                                                      | R-0                                          | R-0                                                                                 | R-0                                            | R-0          | R-0          |                                                                                      |

|--------|------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------|

| SMP    | CKE                                                              | D/A                                                      | Р                                            | S                                                                                   | R/W                                            | UA           | BF           | R = Readable bit                                                                     |

| bit7   |                                                                  |                                                          |                                              |                                                                                     |                                                |              | bit0         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| bit 7: | <u>SPI Mas</u><br>1 = Inpu<br>0 = Inpu<br><u>SPI Slav</u>        | <u>ster Mod</u><br>it data sa<br>it data sa<br>ve Mode   | ampled at e<br>ampled at r                   | end of data<br>niddle of da                                                         | output time<br>ata output tir<br>ed in slave m |              |              |                                                                                      |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$ | <u>)</u><br>a transm<br>a transm<br><u>1</u><br>a transm | itted on ris<br>itted on fal<br>itted on fal | ct (Figure <sup>-</sup><br>ing edge of<br>ling edge o<br>ling edge o<br>ing edge of | f SCK<br>f SCK                                 | e 11-12, an  | d Figure 11- | 13)                                                                                  |

| bit 5: | 1 = India                                                        | cates that                                               | at the last b                                |                                                                                     | )<br>ed or transmi<br>ed or transmi            |              |              |                                                                                      |

| bit 4: | detected<br>1 = India                                            | d last, SS<br>cates tha                                  | SPEN is cle                                  | eared)<br>t has been                                                                | cleared whe<br>detected las                    |              |              | isabled, or when the Start bit is<br>T)                                              |

| bit 3: | detected<br>1 = India                                            | d last, SS<br>cates tha                                  | SPEN is cle                                  | eared)<br>t has been                                                                | cleared whe                                    |              |              | lisabled, or when the Stop bit is                                                    |

| bit 2: | This bit                                                         | holds th<br>match to<br>d                                | ne R/W bit                                   |                                                                                     |                                                |              | Iress match  | . This bit is only valid from the                                                    |

| bit 1: | 1 = India                                                        | cates that                                               | at the user                                  | it I <sup>2</sup> C mode<br>needs to up<br>I to be upda                             | pdate the ad                                   | dress in the | e SSPADD r   | egister                                                                              |

| bit 0: | BF: Buff                                                         | fer Full S                                               | status bit                                   |                                                                                     |                                                |              |              |                                                                                      |

|        | 1 = Rec<br>0 = Rec                                               | eive com<br>eive not                                     | complete,                                    | es)<br>PBUF is full<br>SSPBUF is                                                    |                                                |              |              |                                                                                      |

|        | 1 = Tran                                                         | ismit in p                                               |                                              | SPBUF is f<br>PBUF is en                                                            |                                                |              |              |                                                                                      |

### 11.4 <u>I<sup>2</sup>C<sup>™</sup> Overview</u>

This section provides an overview of the Inter-Integrated Circuit (I<sup>2</sup>C) bus, with Section 11.5 discussing the operation of the SSP module in  $I^2C$  mode.

The  $I^2C$  bus is a two-wire serial interface developed by the Philips<sup>®</sup> Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. The enhanced specification (fast mode) is also supported. This device will communicate with both standard and fast mode devices if attached to the same bus. The clock will determine the data rate.

The I<sup>2</sup>C interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXX software. Table 11-3 defines some of the I<sup>2</sup>C bus terminology. For additional information on the I<sup>2</sup>C interface specification, refer to the Philips document "*The I<sup>2</sup>C bus and how to use it.*"#939839340011, which can be obtained from the Philips Corporation.

In the  $I^2C$  interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- · Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the  $I^2C$  bus is limited only by the maximum bus loading specification of 400 pF.

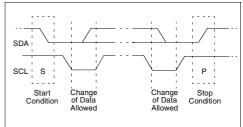

# 11.4.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions. The master generates these conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### FIGURE 11-14: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

#### TABLE 11-3: I<sup>2</sup>C BUS TERMINOLOGY

# FIGURE 11-27: OPERATION OF THE I<sup>2</sup>C MODULE IN IDLE\_MODE, RCV\_MODE OR XMIT\_MODE

| DLE_MODE (7-bit):                             | ,                                                                                                                             | 0                                                                                                                                                                    |                                                                                                    |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| if (Addr_match)                               | {                                                                                                                             | Set interrupt;                                                                                                                                                       |                                                                                                    |

|                                               |                                                                                                                               | if (R/W = 1)                                                                                                                                                         | { Send $\overline{ACK} = 0$ ;                                                                      |

|                                               |                                                                                                                               |                                                                                                                                                                      | set XMIT_MODE;                                                                                     |

|                                               |                                                                                                                               |                                                                                                                                                                      | }                                                                                                  |

|                                               |                                                                                                                               | else if (R/W =                                                                                                                                                       | 0) set RCV_MODE;                                                                                   |

|                                               | }                                                                                                                             |                                                                                                                                                                      |                                                                                                    |

| RCV_MODE:                                     | ,                                                                                                                             |                                                                                                                                                                      |                                                                                                    |

| if ((SSPBUF=Full) OR (SSI                     | POV – 1))                                                                                                                     |                                                                                                                                                                      |                                                                                                    |

|                                               |                                                                                                                               |                                                                                                                                                                      |                                                                                                    |

| •                                             |                                                                                                                               |                                                                                                                                                                      |                                                                                                    |

|                                               | acknowledge;                                                                                                                  |                                                                                                                                                                      |                                                                                                    |

| }                                             |                                                                                                                               |                                                                                                                                                                      |                                                                                                    |

|                                               | $r SSPSR \rightarrow SSI$                                                                                                     | PBOF;                                                                                                                                                                |                                                                                                    |

| send AC                                       | CK = 0;                                                                                                                       |                                                                                                                                                                      |                                                                                                    |

| }                                             |                                                                                                                               |                                                                                                                                                                      |                                                                                                    |