Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

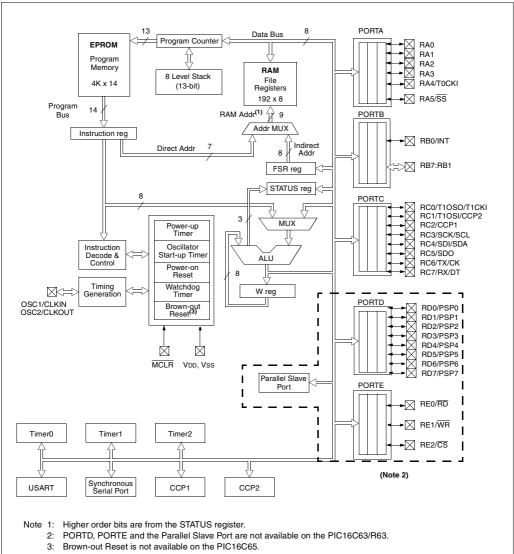

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc67t-04-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7              | Bit 6              | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|----------------|----------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               | 1       | 1                  | 1                  | 1              |                | 1            | 1               | 1             | 1         | 1                        | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter    | its of FSR to  | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | dule's registe     | r              |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif   | icant Byte     |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0            | TO             | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac        | Idress pointe  | er             |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | —                  | —                  | PORTA Dat      | a Latch wher   | written: PO  | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe       | n written: PC  | ORTB pins wh   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe       | n written: PC  | ORTC pins wi   | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | _       | Unimpleme          | nted               |                |                |              |                 |               |           | —                        | _                                              |

| 09h                  | —       | Unimpleme          | nted               |                |                |              |                 |               |           | —                        | —                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                  | _              | Write Buffer   | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE           | INTE           | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | (5)                | (5)                | RCIF           | TXIF           | SSPIF        | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    | _                  | _                  | _              | _              | —            | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the I    | _east Signific | ant Byte of t  | ne 16-bit TM | R1 register     |               | 1         | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the I    | Most Signific  | ant Byte of th | e 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | —                  | —                  | T1CKPS1        | T1CKPS0        | T1OSCEN      | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | dule's registe     | r              |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | _                  | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | us Serial Por      | t Receive Bu   | ffer/Transmit  | Register     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN          | CKP            | SSPM3        | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                  | _                  | CCP1X          | CCP1Y          | CCP1M3       | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                | SREN           | CREN           | —            | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Tra          | nsmit Data F       | legister       |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re           | ceive Data R       | egister        |                |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM          | 2 (LSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM          | 2 (MSB)        |                |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                  | CCP2X          | CCP2Y          | CCP2M3       | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted               |                |                |              |                 |               |           | _                        | _                                              |

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

5: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C63/R63, always maintain these bits clear.

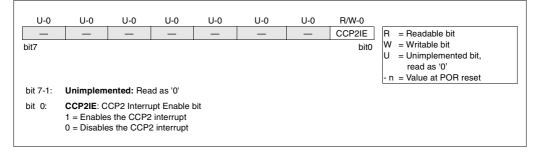

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the individual enable bits for the peripheral interrupts.

Bit PEIE (INTCON<6>) must be set to Note: enable any peripheral interrupt.

#### FIGURE 4-12: PIE1 REGISTER FOR PIC16C62/62A/R62 (ADDRESS 8Ch)

| RW-0     | R/W-0                                                                                                                                                                                    | U-0        | U-0         | R/W-0         | R/W-0  | R/W-0  | R/W-0  |                                                                                                                      |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------|--|

| _        | _                                                                                                                                                                                        |            | _           | SSPIE         | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                                                     |  |

| bit7     |                                                                                                                                                                                          |            |             |               |        |        | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |

| bit 7-6: | Reserved:                                                                                                                                                                                | Always ma  | intain thes | e bits clear. |        |        |        |                                                                                                                      |  |

| bit 5-4: | Unimplem                                                                                                                                                                                 | ented: Rea | ıd as '0'   |               |        |        |        |                                                                                                                      |  |

| bit 3:   | SSPIE: Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                                                                   |            |             |               |        |        |        |                                                                                                                      |  |

| bit 2:   | <b>CCP1IE</b> : C<br>1 = Enables<br>0 = Disable                                                                                                                                          | s the CCP1 | interrupt   | bit           |        |        |        |                                                                                                                      |  |

| bit 1:   | 0 = Disables the CCP1 interrupt<br><b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |            |             |               |        |        |        |                                                                                                                      |  |

| bit 0:   | TMR1IE: TI<br>1 = Enables<br>0 = Disable                                                                                                                                                 | s the TMR1 | overflow i  | nterrupt      | t      |        |        |                                                                                                                      |  |

#### 4.2.2.6 PIE2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt enable bit.

#### FIGURE 4-20: PIE2 REGISTER (ADDRESS 8Dh)

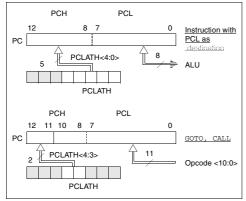

#### 4.3 PCL and PCLATH

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-24 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure in shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-24: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or a POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflows or stack underflow conditions.

- Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address

#### 4.4 Program Memory Paging

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PIC16C6X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C6X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### 11.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 11.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SSP module in  $l^2$ C mode works the same in all PIC16C6X devices that have an SSP module. However the SSP Module in SPI mode has differences between the PIC16C66/67 and the other PIC16C6X devices.

The register definitions and operational description of SPI mode has been split into two sections because of the differences between the PIC16C66/67 and the other PIC16C6X devices. The default reset values of both the SPI modules is the same regardless of the device:

| 11.2 SPI Mode for PIC16C62/62A/R62/63/R63/64/ |  |

|-----------------------------------------------|--|

| 64A/R64/65/65A/R6584                          |  |

| 11.3 SPI Mode for PIC16C66/67 89              |  |

| 11.4 I <sup>2</sup> C <sup>™</sup> Overview95 |  |

| 11.5 SSP I <sup>2</sup> C Operation           |  |

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

#### 12.3 USART Synchronous Master Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Synchronous Master mode the data is transmitted in a half-duplex manner i.e., transmission and reception do not occur at the same time. When transmitting data the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6 and RC7 I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR register is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG register is empty and interrupt flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the status of enable bit TXIE and cannot be cleared in software. It will clear only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR register is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in reset when bits TXEN. CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG register. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hi-impedance. If, during a transmission, either bit CREN or bit SREN is set the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however, is not reset although it is disconnected from the pins. In order to reset the transmitter, the user has to clear enable bit TXEN. If enable bit SREN is set (to interrupt an on going transmission and receive a single word), then after the single word is received, enable bit SREN will be cleared, and the serial port will revert back to transmitting since enable bit TXEN is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, enable bit TXEN should be cleared.

In order to select 9-bit transmission, bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR register was empty and the TXREG register was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{TXIE}}$  .

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

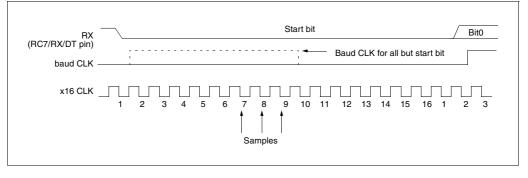

#### 13.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 13-6 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 13-6: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

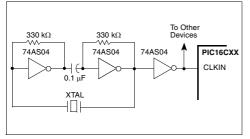

Figure 13-7 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 13-7: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

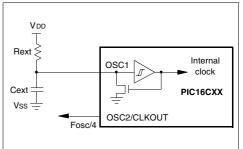

#### 13.2.4 RC OSCILLATOR

For timing insensitive applications the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 13-8 shows how the RC combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-5 for waveform).

#### FIGURE 13-8: RC OSCILLATOR MODE

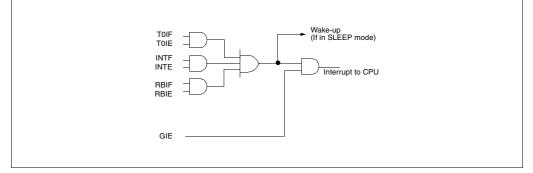

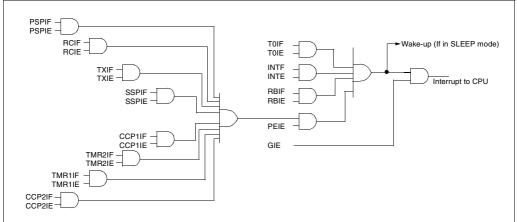

#### FIGURE 13-17: INTERRUPT LOGIC FOR PIC16C61

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|-------|--------|--------|--------|--------|

| PIC16C62  | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C62A | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16CR62 | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C63  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR63 | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64A | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C65  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C65A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR65 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C66  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C67  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

### 15.0 ELECTRICAL CHARACTERISTICS FOR PIC16C61

#### Absolute Maximum Ratings †

this pin directly to Vss.

| Ambient temperature under bias                                                                             | -55°C to +125°C                    |

|------------------------------------------------------------------------------------------------------------|------------------------------------|

| •                                                                                                          |                                    |

| Storage temperature                                                                                        | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                         | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to VSS                                                                         | -0.3V to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                               | 0V to +14V                         |

| Voltage on RA4 pin with respect to Vss                                                                     | 0V to +14V                         |

| Total power dissipation (Note 1)                                                                           | 800 mW                             |

| Maximum current out of Vss pin                                                                             | 150 mA                             |

| Maximum current into VDD pin                                                                               | 100 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                               | ± 20 mA                            |

| Output clamp current, Iок (Vo < 0 or Vo > VDD)                                                             | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                 | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                              | 20 mA                              |

| Maximum current sunk by PORTA                                                                              | 80 mA                              |

| Maximum current sourced by PORTA                                                                           | 50 mA                              |

| Maximum current sunk by PORTB                                                                              | 150 mA                             |

| Maximum current sourced by PORTB                                                                           | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD- | VOH) x IOH} + $\Sigma$ (VOI x IOL) |

**Note 2:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 15-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C61-04                | PIC16C61-20              | PIC16LC61-04               | JW Devices                 |

|-----|----------------------------|--------------------------|----------------------------|----------------------------|

| RC  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| XT  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| HS  | VDD: 4.5V to 5.5V          | VDD: 4.5V to 5.5V        |                            | VDD: 4.5V to 5.5V          |

|     | IDD: 13.5 mA typ. at 5.5V  | IDD: 30 mA max. at 5.5V  | Not recommended for use in | IDD: 30 mA max. at 5.5V    |

|     | IPD: 1.0 μA typ. at 4.5V   | IPD: 1.0 μA typ. at 4.5V | HS mode                    | IPD: 1.0 μA typ. at 4.5V   |

|     | Freq: 4 MHz max.           | Freq: 20 MHz max.        |                            | Freq: 20 MHz max.          |

| LP  | VDD: 4.0V to 6.0V          |                          | VDD: 3.0V to 6.0V          | VDD: 3.0V to 6.0V          |

|     | IDD: 15 μA typ. at 32 kHz, | Not recommended for      | IDD: 32 μA max. at 32 kHz, | IDD: 32 μA max. at 32 kHz, |

|     | 4.0V                       | use in LP mode           | 3.0V                       | 3.0V                       |

|     | IPD: 0.6 μA typ. at 4.0V   | use in LP mode           | IPD: 9 μA max. at 3.0V     | IPD: 9 μA max. at 3.0V     |

|     | Freq: 200 kHz max.         |                          | Freq: 200 kHz max.         | Freq: 200 kHz max.         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 15.3 DC Characteristics: PIC16C61-04 (Commercial, Industrial, Extended) PIC16C61-20 (Commercial, Industrial, Extended) PIC16LC61-04 (Commercial, Industrial)

| DC CH4        | ARACTERISTICS                      | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |                   |      |                 |        |                                                             |  |  |

|---------------|------------------------------------|-------------------------------------------------------|-------------------|------|-----------------|--------|-------------------------------------------------------------|--|--|

| Param<br>No.  | Characteristic                     | Section                                               | 15.2.<br>Min      | Тур† | Max             | Units  | Conditions                                                  |  |  |

|               | Input Low Voltage                  |                                                       |                   |      |                 |        |                                                             |  |  |

|               | I/O ports                          | VIL                                                   |                   |      |                 |        |                                                             |  |  |

| D030<br>D030A | with TTL buffer                    |                                                       | Vss<br>Vss        | -    | 0.15VDD<br>0.8V | V<br>V | For entire VDD range<br>4.5V ≤ VDD ≤ 5.5V                   |  |  |

| D031          | with Schmitt Trigger buffer        |                                                       | Vss               | -    | 0.2VDD          | v      |                                                             |  |  |

| D032          | MCLR, OSC1 (in RC mode)            |                                                       | Vss               | -    | 0.2VDD          | v      |                                                             |  |  |

| D033          | OSC1 (in XT, HS and LP)            |                                                       | Vss               | -    | 0.3VDD          | v      | Note1                                                       |  |  |

|               | Input High Voltage                 |                                                       |                   |      |                 |        |                                                             |  |  |

|               | I/O ports                          | VIH                                                   |                   | -    |                 |        |                                                             |  |  |

| D040          | with TTL buffer                    |                                                       | 2.0               | -    | VDD             | v      | $4.5V \le VDD \le 5.5V$                                     |  |  |

| D040A         |                                    |                                                       | 0.25Vdd<br>+ 0.8V | -    | Vdd             | V      | For entire VDD range                                        |  |  |

| D041          | with Schmitt Trigger buffer        |                                                       | 0.85Vdd           | -    | Vdd             | v      | For entire VDD range                                        |  |  |

| D042          | MCLR                               |                                                       | 0.85VDD           | -    | Vdd             | V      |                                                             |  |  |

| D042A         | OSC1 (XT, HS and LP)               |                                                       | 0.7Vdd            | -    | Vdd             | V      | Note1                                                       |  |  |

| D043          | OSC1 (in RC mode)                  |                                                       | 0.9Vdd            | -    | Vdd             | V      |                                                             |  |  |

| D070          | PORTB weak pull-up current         | IPURB                                                 | 50                | 250  | † 400           | μA     | VDD = 5V, VPIN = VSS                                        |  |  |

|               | Input Leakage Current (Notes 2, 3) |                                                       |                   |      |                 |        |                                                             |  |  |

| D060          | I/O ports                          | lı∟                                                   | -                 | -    | ±1              | μA     | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-impedance             |  |  |

| D061          | MCLR, RA4/T0CKI                    |                                                       | -                 | -    | ±5              | μA     | $Vss \leq V PIN \leq V DD$                                  |  |  |

| D063          | OSC1                               |                                                       | -                 | -    | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

| 1             | Output Low Voltage                 |                                                       |                   |      |                 |        |                                                             |  |  |

| D080          | I/O ports                          | Vol                                                   | -                 | -    | 0.6             | V      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                 |  |  |

| D080A         |                                    |                                                       | -                 | -    | 0.6             | V      | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                |  |  |

| D083          | OSC2/CLKOUT (RC osc config)        |                                                       | -                 | -    | 0.6             | V      | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                 |  |  |

| D083A         |                                    |                                                       | -                 | -    | 0.6             | V      | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                |  |  |

The parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

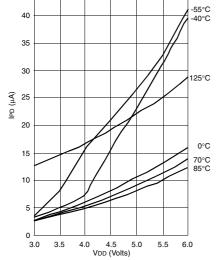

# FIGURE 16-8: MAXIMUM IPD vs. VDD WATCHDOG ENABLED\*

\*IPD, with Watchdog Timer enabled, has two components: The leakage current which increases with higher temperature and the operating current of the Watchdog Timer logic which increases with lower temperature. At -40°C, the latter dominates explaining the apparently anomalous behavior.

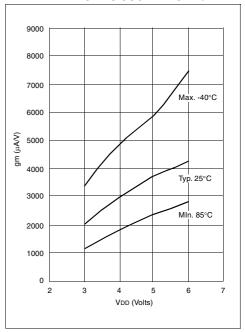

FIGURE 16-16: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

#### 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C62A/R62/64A/R64

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                   | 55°C to +125°C                                      |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Storage temperature                                                                                              | 65°C to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                               | 0.3V to (VDD + 0.3V)                                |

| Voltage on VDD with respect to VSS                                                                               | -0.3V to +7.5V                                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                     | 0V to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                               | 0V to +14V                                          |

| Total power dissipation (Note 1)                                                                                 | 1.0W                                                |

| Maximum current out of VSS pin                                                                                   |                                                     |

| Maximum current into VDD pin                                                                                     | 250 mA                                              |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                     | ±20 mA                                              |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                   | ±20 mA                                              |

| Maximum output current sunk by any I/O pin                                                                       | 25 mA                                               |

| Maximum output current sourced by any I/O pin                                                                    | 25 mA                                               |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined)                                                       | 200 mA                                              |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined)                                                    | 200 mA                                              |

| Maximum current sunk by PORTC and PORTD (combined)                                                               | 200 mA                                              |

| Maximum current sourced by PORTC and PORTD (combined)                                                            | 200 mA                                              |

| Note 1. Power dissipation is calculated as follows: $Pdis = Vpp \times (Ipp - \sum Ipu) + \sum (Vpp - \sum Ipu)$ | $(V_{OU}) \times (OU) + \Sigma(V_{OU} \times (OU))$ |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62A-04<br>PIC16CR62-04<br>PIC16C64A-04<br>PIC16CR64-04                                                | PIC16C62A-10<br>PIC16CR62-10<br>PIC16C64A-10<br>PIC16CR64-10                                | PIC16C62A-20<br>PIC16CR62-20<br>PIC16C64A-20<br>PIC16CR64-20                                  | PIC16LC62A-04<br>PIC16LCR62-04<br>PIC16LC64A-04<br>PIC16LCR64-04                                        | JW Devices                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                     | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                 |

| ХТ  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 µA max. at 3.0V<br>Freq: 4 MHz max.             | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| HS  | VpD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              |                                                                                             | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use<br>in HS mode                                                                   | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.           |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                          | Not recommended for use in LP mode                                                            | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

<sup>© 1997-2013</sup> Microchip Technology Inc.

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

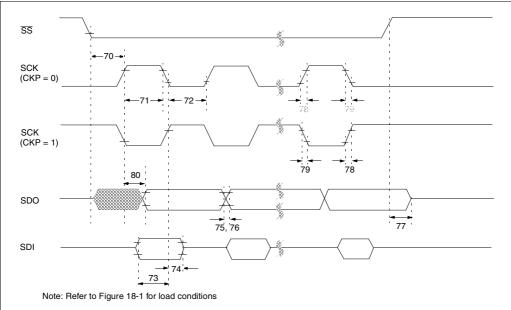

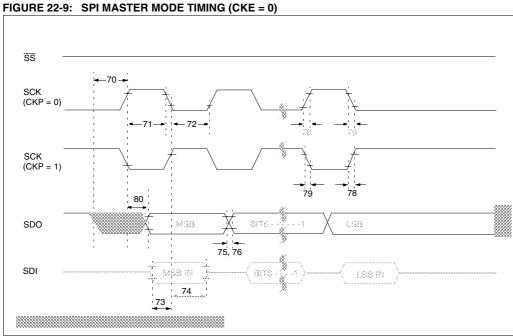

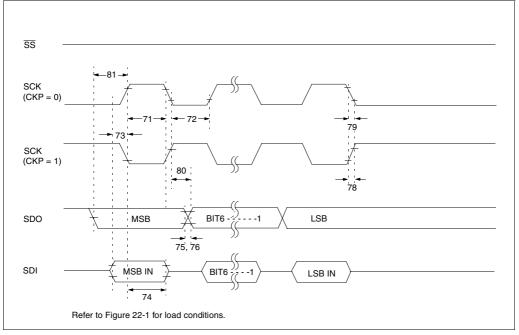

#### TABLE 18-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input  | Тсү      | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)         | TCY + 20 | —    |     | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)          | TCY + 20 | —    |     | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                |          | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | —    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)       |          | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

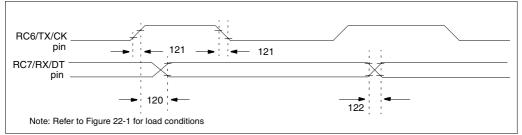

#### FIGURE 22-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 22-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                    |                       | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-----------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120*             | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 66/67  |     | —    | 80  | ns    |            |

|                  |          | Clock high to data out valid      | PIC16 <b>LC</b> 66/67 | -   | —    | 100 | ns    |            |

| 121*             | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 66/67  |     | —    | 45  | ns    |            |

|                  |          | (Master Mode)                     | PIC16LC66/67          |     | —    | 50  | ns    |            |

| 122*             | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 66/67  | _   | —    | 45  | ns    |            |

|                  |          |                                   | PIC16LC66/67          | _   | —    | 50  | ns    |            |

\* These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

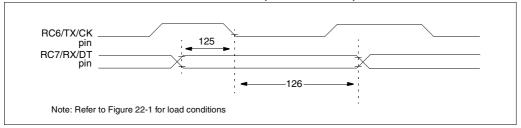

#### FIGURE 22-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 22-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup time) | 15  | _    |     | ns    |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    | -   | ns    |            |

These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

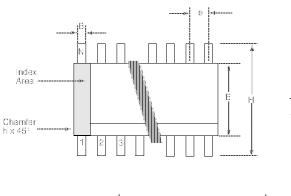

#### 24.4 18-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|        | Package Group: Plastic SOIC (SO) |             |           |        |       |           |

|--------|----------------------------------|-------------|-----------|--------|-------|-----------|

|        |                                  | Millimeters |           | Inches |       |           |

| Symbol | Min                              | Max         | Notes     | Min    | Max   | Notes     |

| α      | 0°                               | 8°          |           | 0°     | 8°    |           |

| А      | 2.362                            | 2.642       |           | 0.093  | 0.104 |           |

| A1     | 0.101                            | 0.300       |           | 0.004  | 0.012 |           |

| В      | 0.355                            | 0.483       |           | 0.014  | 0.019 |           |

| С      | 0.241                            | 0.318       |           | 0.009  | 0.013 |           |

| D      | 11.353                           | 11.735      |           | 0.447  | 0.462 |           |

| E      | 7.416                            | 7.595       |           | 0.292  | 0.299 |           |

| е      | 1.270                            | 1.270       | Reference | 0.050  | 0.050 | Reference |

| Н      | 10.007                           | 10.643      |           | 0.394  | 0.419 |           |

| h      | 0.381                            | 0.762       |           | 0.015  | 0.030 |           |

| L      | 0.406                            | 1.143       |           | 0.016  | 0.045 |           |

| N      | 18                               | 18          |           | 18     | 18    |           |

| CP     | -                                | 0.102       |           | -      | 0.004 |           |

| Figure 23-12:                  | SPI Slave Mode Timing (CKE = 1)                                    |

|--------------------------------|--------------------------------------------------------------------|

| Figure 23-13:                  | I <sup>2</sup> C Bus Start/Stop Bits Timing278                     |

| Figure 23-14:<br>Figure 23-15: | I <sup>2</sup> C Bus Data Timing                                   |

| Figure 23-15.                  | USART Synchronous Transmission<br>(Master/Slave) Timing            |

| Figure 23-16:                  | USART Synchronous Receive                                          |

| 1 iguro 20 101                 | (Master/Slave) Timing                                              |

| Figure 24-1:                   | Typical IPD vs. VDD                                                |

|                                | (WDT Disabled, RC Mode)                                            |

| Figure 24-2:                   | Maximum IPD vs. VDD                                                |

|                                | (WDT Disabled, RC Mode) 281                                        |

| Figure 24-3:                   | Typical IPD vs. VDD @ 25°C                                         |

| <b>-</b> :                     | (WDT Enabled, RC Mode)282                                          |

| Figure 24-4:                   | Maximum IPD vs. VDD                                                |

| Figure 04 Fr                   | (WDT Enabled, RC Mode)                                             |

| Figure 24-5:                   | Typical RC Oscillator<br>Frequency vs. VDD                         |

| Figure 24-6:                   | Typical RC Oscillator                                              |

| riguie 24 0.                   | Frequency vs. VDD                                                  |

| Figure 24-7:                   | Typical RC Oscillator                                              |

| 5                              | Frequency vs. VDD                                                  |

| Figure 24-8:                   | Typical IPD vs. VDD Brown-out                                      |

|                                | Detect Enabled (RC Mode)283                                        |

| Figure 24-9:                   | Maximum IPD vs. VDD Brown-out                                      |

|                                | Detect Enabled                                                     |

|                                | (85°C to -40°C, RC Mode)                                           |

| Figure 24-10:                  | Typical IPD vs. Timer1 Enabled                                     |

|                                | (32 kHz, RC0/RC1 = 33 pF/33 pF,                                    |

| Figure 24-11:                  | RC Mode)                                                           |

| 1 igule 24-11.                 | (32  kHz, RC0/RC1 = 33  pF/33  pF,                                 |

|                                | 85°C to -40°C, RC Mode)                                            |

| Figure 24-12:                  | Typical IDD vs. Frequency                                          |

| 0                              | (RC Mode @ 22 pF, 25°C)                                            |

| Figure 24-13:                  | Maximum IDD vs. Frequency                                          |

|                                | (RC Mode @ 22 pF, -40°C to 85°C)                                   |

| Figure 24-14:                  | Typical IDD vs. Frequency                                          |

|                                | (RC Mode @ 100 pF, 25°C)                                           |

| Figure 24-15:                  | Maximum IDD vs. Frequency                                          |

| Figure 24-16:                  | (RC Mode @ 100 pF, -40°C to 85°C) 285<br>Typical IDD vs. Frequency |

| Figure 24-10.                  | (RC Mode @ 300 pF, 25°C)                                           |

| Figure 24-17:                  | Maximum IDD vs. Frequency                                          |

| guio 2 i i i i                 | (RC Mode @ 300 pF, -40°C to 85°C) 286                              |

| Figure 24-18:                  | Typical IDD vs. Capacitance @ 500 kHz                              |

|                                | (RC Mode)                                                          |

| Figure 24-19:                  | Transconductance(gm) of HS                                         |

|                                | Oscillator vs. VDD287                                              |

| Figure 24-20:                  | Transconductance(gm) of LP                                         |

|                                | Oscillator vs. VDD                                                 |

| Figure 24-21:                  | Transconductance(gm) of XT                                         |

| <b>Figure 04 00</b>            | Oscillator vs. VDD                                                 |

| Figure 24-22:                  | (LP Mode, 25°C)                                                    |

| Figure 24-23:                  |                                                                    |

| 1 iguio 21 20.                 | (HS Mode, 25°C)                                                    |

| Figure 24-24:                  | Typical XTAL Startup Time vs. VDD                                  |

| 5                              | (XT Mode, 25°C)                                                    |

| Figure 24-25:                  | Typical Idd vs. Frequency                                          |

| -                              | (LP Mode, 25°C)                                                    |

| Figure 24-26:                  | Maximum IDD vs. Frequency                                          |

|                                | (LP Mode, 85°C to -40°C)289                                        |

| Figure 24-27:                  | Typical IDD vs. Frequency                                          |

| <b>Figure 04.00</b>            | (XT Mode, 25°C)                                                    |

| Figure 24-28:                  | Maximum IDD vs. Frequency<br>(XT Mode, -40°C to 85°C)289           |

|                                | (AT MODE, -40 C 10 63 C)                                           |

|                                |                                                                    |

| Figure 24-29: | Typical IDD vs. Frequency    |

|---------------|------------------------------|

|               | (HS Mode, 25°C) 290          |

| Figure 24-30: | Maximum IDD vs. Frequency    |

|               | (HS Mode, -40°C to 85°C) 290 |