Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc67t-04i-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

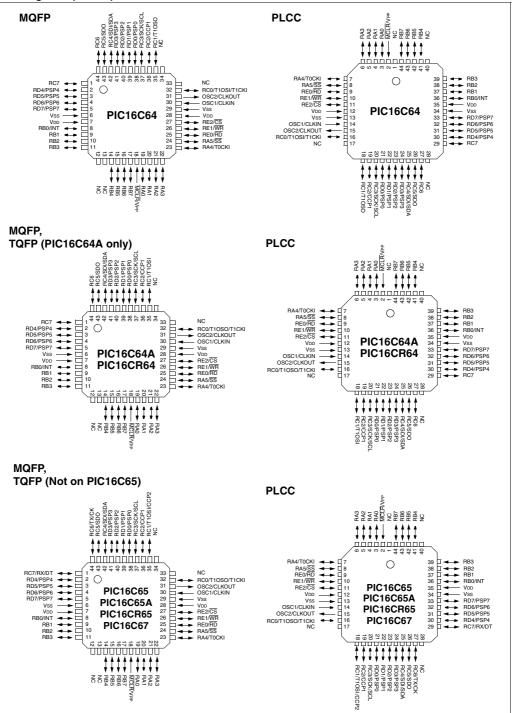

#### Pin Diagrams (Cont.'d)

### 2.0 PIC16C6X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C6X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C6X family of devices, there are four device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**64. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC64. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**64. These devices have ROM program memory and operate over the standard voltage range.

- 4. LCR, as in PIC16LCR64. These devices have ROM program memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C6X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

ROM devices do not allow serialization information in the program memory space. The user may have this information programmed in the data memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

#### FIGURE 4-8: PIC16C66/67 DATA MEMORY MAP

| ndirect addr.(*)                           | 00h       | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 180 |

|--------------------------------------------|-----------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----|

| TMR0                                       | 01h       | OPTION                                     | 81h        | TMR0                                       | 101h         | OPTION                                     | 181 |

| PCL                                        | 02h       | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182 |

| STATUS                                     | 03h       | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183 |

| FSR                                        | 04h       | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184 |

| PORTA                                      | 05h       | TRISA                                      | 85h        |                                            | 105h         | 1011                                       | 185 |

| PORTB                                      | 06h       | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186 |

| PORTC                                      | 07h       | TRISC                                      | 87h        |                                            | 107h         |                                            | 187 |

| PORTD (1)                                  | 08h       | TRISD (1)                                  | 88h        |                                            | 108h         |                                            | 188 |

| PORTE (1)                                  | 09h       | TRISE (1)                                  | 89h        |                                            | 109h         |                                            | 189 |

| PCLATH                                     | 0Ah       | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 184 |

| INTCON                                     | 0Bh       | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18E |

| PIR1                                       | 0Ch       | PIE1                                       | 8Ch        |                                            | 10Ch         |                                            | 180 |

| PIR2                                       | 0Dh       | PIE2                                       | 8Dh        |                                            | 10Dh         |                                            | 180 |

| TMR1L                                      | 0Eh       | PCON                                       | 8Eh        |                                            | 10Eh         |                                            | 18  |

| TMR1H                                      | 0Fh       | TOON                                       | 8Fh        |                                            | 10Fh         |                                            | 18F |

| T1CON                                      | 10h       |                                            | 90h        |                                            | 110h         |                                            | 190 |

| TMR2                                       | 11h       |                                            | 91h        |                                            | 111h         |                                            | 191 |

| T2CON                                      | 12h       | PR2                                        | 92h        |                                            | 112h         |                                            | 192 |

| SSPBUF                                     | 13h       | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193 |

| SSPCON                                     | 14h       | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194 |

| CCPR1L                                     | 15h       | 30F 5TAT                                   | 95h        |                                            | 115h         |                                            | 195 |

| CCPR1H                                     | 16h       |                                            | 96h        |                                            | 116h         |                                            | 196 |

| CCP1CON                                    | 17h       |                                            | 97h        | General                                    | 117h         | General                                    | 197 |

| RCSTA                                      | 18h       | TXSTA                                      | 98h        | Purpose                                    | 118h         | Purpose                                    | 198 |

| TXREG                                      | 19h       | SPBRG                                      | 99h        | Register<br>16 Bytes                       | 119h         | Register<br>16 Bytes                       | 199 |

| RCREG                                      | 1Ah       | SEDITO                                     | 9Ah        | TO Bytes                                   | 11Ah         | TO Dytes                                   | 194 |

| CCPR2L                                     | 1Bh       |                                            | 9Bh        |                                            | 11Bh         |                                            | 19E |

| CCPR2H                                     | 1Ch       |                                            | 9Ch        |                                            | 11Ch         |                                            | 190 |

| CCP2CON                                    | 1Dh       |                                            | 9Dh        |                                            | 11Dh         |                                            | 190 |

| 0012001                                    | 1Eh       |                                            | 9Eh        |                                            | 11Eh         |                                            | 19E |

|                                            | 1Fh       |                                            | 9Fh        |                                            | 11Fh         |                                            | 19F |

|                                            | 20h       |                                            | -          |                                            | 120h         |                                            | -   |

|                                            | 2011      |                                            | A0h        |                                            | 12011        |                                            | 1A0 |

| General<br>Purpose<br>Register<br>96 Bytes |           | General<br>Purpose<br>Register<br>80 Bytes | EFh        | General<br>Purpose<br>Register<br>80 Bytes | 16Fh         | General<br>Purpose<br>Register<br>80 Bytes | 1EF |

|                                            | 7Fh       | accesses<br>70h-7Fh<br>in Bank 0           | F0h<br>FFh | accesses<br>70h-7Fh<br>in Bank 0           | 170h<br>17Fh | accesses<br>70h-7Fh<br>in Bank 0           | 1FC |

| Bank 0                                     |           | Bank 1                                     |            | Bank 2                                     |              | Bank 3                                     |     |

| Not a physical                             | register. | mory locations, read                       |            |                                            |              |                                            |     |

|                                            |           | ytes of data memo                          |            | nks 1, 2, and 3 are                        |              |                                            |     |

| IADLE                | 4-2:    | SPECIA             |                    | ION RE                    | GISTER         |              |                 | 5002/02/      | 4/H02 ((           | Jont.a)                  |                                                |

|----------------------|---------|--------------------|--------------------|---------------------------|----------------|--------------|-----------------|---------------|--------------------|--------------------------|------------------------------------------------|

| Address              | Name    | Bit 7              | Bit 6              | Bit 5                     | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

| Bank 1               |         |                    |                    |                           |                |              |                 |               |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter               | nts of FSR to  | address data | a memory (n     | ot a physical | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU               | INTEDG             | TOCS                      | T0SE           | PSA          | PS2             | PS1           | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Sigr                | nificant Byte  |              |                 |               |                    | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0                       | TO             | PD           | Z               | DC            | С                  | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ac        | Idress pointe             | er             |              |                 |               |                    | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | —                  | _                  | PORTA Da                  | ta Direction R | legister     |                 |               |                    | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat          | ta Direction F     | Register                  |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da           | ta Direction F     | Register                  |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | —       | Unimpleme          | nted               |                           |                |              |                 |               |                    | —                        | -                                              |

| 89h                  | _       | Unimpleme          | nted               |                           |                |              |                 |               |                    | —                        | —                                              |

| 8Ah <sup>(1,2)</sup> | PCLATH  | —                  | -                  | —                         | Write Buffer   | for the uppe | r 5 bits of the | e Program C   | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | T0IE                      | INTE           | RBIE         | TOIF            | INTF          | RBIF               | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | (6)                | (6)                | -                         | —              | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE             | 00 0000                  | 00 0000                                        |

| 8Dh                  | -       | Unimpleme          | nted               |                           |                |              |                 |               |                    | _                        | _                                              |

| 8Eh                  | PCON    | —                  | -                  | —                         | —              | —            | —               | POR           | BOR <sup>(4)</sup> | qq                       | uu                                             |

| 8Fh                  | -       | Unimpleme          | nted               |                           |                |              |                 | •             |                    | —                        | -                                              |

| 90h                  | -       | Unimpleme          | nted               |                           |                |              |                 |               |                    | -                        | -                                              |

| 91h                  | -       | Unimpleme          | nted               |                           |                |              |                 |               |                    | -                        | -                                              |

| 92h                  | PR2     | Timer2 Peri        | iod Register       |                           |                |              |                 |               |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou         | us Serial Port     | t (I <sup>2</sup> C mode) | ) Address Reg  | gister       |                 |               |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | _                  | _                  | D/A                       | Р              | S            | R/W             | UA            | BF                 | 00 0000                  | 00 0000                                        |

| 95h-9Fh              | -       | Unimpleme          | nted               |                           |                |              |                 |               |                    | -                        | _                                              |

|                      |         |                    |                    |                           |                |              |                 |               |                    |                          |                                                |

| TABLE 4-2: | SPECIAL FUNCTION REGISTERS FOR THE PIC16C62/62A/R62 | (Cont.'d) |

|------------|-----------------------------------------------------|-----------|

|            |                                                     |           |

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C62, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

6: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C62/62A/R62, always maintain these bits clear.

| Address              | Name    | Bit 7              | Bit 6              | Bit 5          | Bit 4          | Bit 3         | Bit 2           | Bit 1        | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|----------------|----------------|---------------|-----------------|--------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                    |                |                |               |                 |              |           |                          | ·                                              |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter    | ts of FSR to   | address data  | a memory (n     | ot a physica | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r              |                |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif   | icant Byte     |               |                 |              |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0            | TO             | PD            | Z               | DC           | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad        | dress pointe   | r              |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   | -                  | _                  | PORTA Dat      | a Latch wher   | n written: PO | RTA pins wh     | en read      |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat          | ta Latch whe       | n written: PC  | ORTB pins wi   | nen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe       | n written: PC  | ORTC pins w    | hen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat          | ta Latch whe       | n written: PC  | ORTD pins w    | hen read      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                    | —                  | _              | _              | —             | RE2             | RE1          | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  |                    | _                  | _              | Write Buffer   | for the uppe  | r 5 bits of the | e Program C  | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE           | INTE           | RBIE          | TOIF            | INTF         | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                | _              | 1              | SSPIF         | CCP1IF          | TMR2IF       | TMR1IF    | 00 0000                  | 00 0000                                        |

| 0Dh                  | _       | Unimpleme          | nted               |                |                |               |                 |              |           | —                        | _                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L    | east Signific  | ant Byte of t  | he 16-bit TM  | R1 register     |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the M    | /lost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   | -                  | _                  | T1CKPS1        | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS       | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r              |                |               |                 |              |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   |                    | TOUTPS3            | TOUTPS2        | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1      | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | us Serial Port     | Receive Bu     | ffer/Transmit  | Register      |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN          | СКР            | SSPM3         | SSPM2           | SSPM1        | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)        |                |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)        |                |               |                 |              |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | —                  | —                  | CCP1X          | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1       | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h-1Fh              | _       | Unimpleme          | nted               |                |                |               |                 |              |           | _                        |                                                |

#### TABLE 4-4: SPECIAL FUNCTION REGISTERS FOR THE PIC16C64/64A/R64

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C64, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C64/64A/R64, always maintain these bits clear.

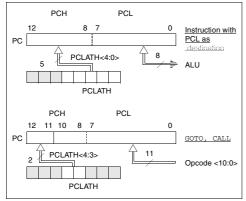

#### 4.3 PCL and PCLATH

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-24 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure in shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-24: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or a POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflows or stack underflow conditions.

- Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address

#### 4.4 Program Memory Paging

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PIC16C6X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C6X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### TABLE 5-11: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                                           |

|--------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Read control input in parallel slave port mode.<br>RD<br>1 = Not a read operation<br>0 = Read operation. The system reads the PORTD register (if<br>chip selected)        |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Write control input in parallel slave port mode.<br>WR<br>1 = Not a write operation<br>0 = Write operation. The system writes to the PORTD register (if<br>chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Chip select control input in parallel slave port<br>mode.<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                   |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port (PSP) mode.

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|----------|--------------|-------|--------------------------|---------------------------|

| 09h     | PORTE |       | —     | _     | —       |       | RE2      | RE1          | RE0   | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Da | ta Direction | Bits  | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells not used by PORTE.

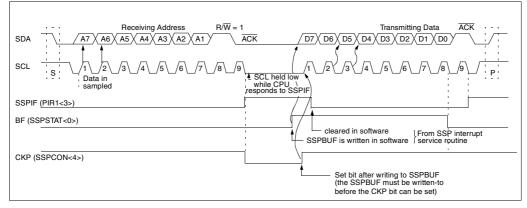

#### 11.5.1.3 TRANSMISSION

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

Г

### FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                | R/W-0                       | R/W-0          | U-0         | R-0          | R-0          | R-x         |                    |                                                                                                                               |

|--------|----------------------------------------------------------------------|-----------------------------|----------------|-------------|--------------|--------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                  | SREN                        | CREN           | —           | FERR         | OERR         | RX9D        | R                  | = Readable bit                                                                                                                |

| bit7   |                                                                      |                             |                |             |              |              | bitO        | W<br>U<br>- n<br>x | <ul> <li>Writable bit</li> <li>Unimplemented</li> <li>bit, read as '0'</li> <li>Value at POR rese</li> <li>unknown</li> </ul> |

| bit 7: | SPEN: Ser<br>(Configures<br>1 = Serial p<br>0 = Serial p             | s RC7/RX/l                  | DT and RC<br>d | 6/TX/CK     | pins as seri | al port pins | s when bits | TRIS               | C<7:6> are set)                                                                                                               |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                   | 9-bit rece                  | otion          |             |              |              |             |                    |                                                                                                                               |

| bit 5: | SREN: Sing                                                           | gle Receiv                  | e Enable bi    | t           |              |              |             |                    |                                                                                                                               |

|        | Asynchrone<br>Don't care                                             | ous mode                    |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{Synchronof}{1 = Enables}$ $0 = Disables$ This bit is c        | s single ree<br>s single re | ceive<br>ceive | is comple   | ete.         |              |             |                    |                                                                                                                               |

|        | Synchrono<br>Unused in t                                             |                             | <u>slave</u>   |             |              |              |             |                    |                                                                                                                               |

| bit 4: | CREN: Cor                                                            | ntinuous R                  | eceive Ena     | ble bit     |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Asynchrono}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                |             |              |              |             |                    |                                                                                                                               |

|        | $\frac{\text{Synchronor}}{1 = \text{Enables}}$ $0 = \text{Disables}$ | s continuo                  |                | until enabl | le bit CREN  | l is cleared | (CREN ov    | erride             | s SREN)                                                                                                                       |

| bit 3: | Unimplem                                                             | ented: Rea                  | ad as '0'      |             |              |              |             |                    |                                                                                                                               |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                             | g error (Ca                 |                | ed by rea   | ding RCRE    | G register   | and receive | e next             | valid byte)                                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrun<br>0 = No ove                       | n error (Ca                 |                | d by clea   | ring bit CRI | EN)          |             |                    |                                                                                                                               |

| bit 0: | <b>RX9D</b> : 9th                                                    |                             |                |             |              |              |             |                    |                                                                                                                               |

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, then set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

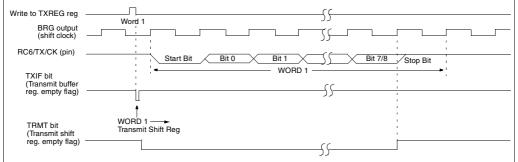

## FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN       | CREN  | —     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h     | TXREG | USART Tra            | ansmit R | egister    |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | General  | or Registe | er    |       |        |        |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

| NOP               | No Oper   | ation            |                  |                  |

|-------------------|-----------|------------------|------------------|------------------|

| Syntax:           | [ label ] | NOP              |                  |                  |

| Operands:         | None      |                  |                  |                  |

| Operation:        | No opera  | ition            |                  |                  |

| Status Affected:  | None      |                  |                  |                  |

| Encoding:         | 00        | 0000             | 0xx0             | 0000             |

| Description:      | No operat | ion.             |                  |                  |

| Words:            | 1         |                  |                  |                  |

| Cycles:           | 1         |                  |                  |                  |

| Q Cycle Activity: | Q1        | Q2               | Q3               | Q4               |

|                   | Decode    | No-<br>Operation | No-<br>Operation | No-<br>Operation |

| Example           | NOP       |                  |                  |                  |

| RETFIE                       | Return fi                                                             | rom Inter                     | rupt                                         |                       |

|------------------------------|-----------------------------------------------------------------------|-------------------------------|----------------------------------------------|-----------------------|

| Syntax:                      | [ label ]                                                             | RETFIE                        |                                              |                       |

| Operands:                    | None                                                                  |                               |                                              |                       |

| Operation:                   | $\begin{array}{l} TOS \rightarrow F \\ 1 \rightarrow GIE \end{array}$ | PC,                           |                                              |                       |

| Status Affected:             | None                                                                  |                               |                                              |                       |

| Encoding:                    | 00                                                                    | 0000                          | 0000                                         | 1001                  |

|                              | PC. Interru                                                           | inte ara ar                   | ablad by a                                   | otting                |

|                              | Global Inte<br>(INTCON<<br>instruction                                | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |

| Words:                       | Global Inte<br>(INTCON<                                               | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |

| Words:<br>Cycles:            | Global Inte<br>(INTCON<<br>instruction                                | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |

|                              | Global Inte<br>(INTCON<<br>instruction                                | ,<br>errupt Ena<br><7>). This | ble bit, ĠIE                                 | Ē                     |

| Cycles:                      | Global Inte<br>(INTCON<<br>instruction<br>1<br>2                      | errupt Ena<br>(7>). This      | ble bit, GIE<br>is a two cy                  | E<br>cle              |

| Cycles:<br>Q Cycle Activity: | Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1                | Q2<br>No-                     | ble bit, GIE<br>is a two cy<br>Q3<br>Set the | cle<br>Q4<br>Pop from |

After Interrupt PC = TOS GIE = 1

| OPTION                            | Load Option Register                                                                                                                                                                                                                                    |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [label] OPTION                                                                                                                                                                                                                                          |

| Operands:                         | None                                                                                                                                                                                                                                                    |

| Operation:                        | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                |

| Status Affected:                  | None                                                                                                                                                                                                                                                    |

| Encoding:                         | 00 0000 0110 0010                                                                                                                                                                                                                                       |

| Description:<br>Words:<br>Cycles: | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it.<br>1 |

| Example                           | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                      |

#### SLEEP

| Syntax:           | [ label ]                                                                                                | SLEEP                                               |                                                                                          |                     |

|-------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|

| Operands:         | None                                                                                                     |                                                     |                                                                                          |                     |

| Operation:        | $\begin{array}{c} 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$ | VDT,<br>T presca                                    | ler,                                                                                     |                     |

| Status Affected:  | TO, PD                                                                                                   |                                                     |                                                                                          |                     |

| Encoding:         | 0.0                                                                                                      | 0000                                                | 0110                                                                                     | 0011                |

| Description:      | cleared. T<br>set. Watc<br>caler are<br>The proce<br>mode with                                           | Time-out si<br>hdog Time<br>cleared.<br>essor is pu | atus bit, Pi<br>tatus bit, T<br>er and its p<br>at into SLE<br>ator stopp<br>re details. | O is<br>ores-<br>EP |

| Words:            | 1                                                                                                        |                                                     |                                                                                          |                     |

| Cycles:           | 1                                                                                                        |                                                     |                                                                                          |                     |

| Q Cycle Activity: | Q1                                                                                                       | Q2                                                  | Q3                                                                                       | Q4                  |

|                   | Decode                                                                                                   | No-<br>Operation                                    | No-<br>Operation                                                                         | Go to<br>Sleep      |

| Example:          | SLEEP                                                                                                    |                                                     |                                                                                          |                     |

|                   |                                                                                                          |                                                     |                                                                                          |                     |

| SUBLW             | Subtract              | W from              | _iteral                                      |              |

|-------------------|-----------------------|---------------------|----------------------------------------------|--------------|

| Syntax:           | [ label ]             | SUBLW               | k                                            |              |

| Operands:         | $0 \le k \le 25$      | 5                   |                                              |              |

| Operation:        | k - (W) $\rightarrow$ | (W)                 |                                              |              |

| Status Affected:  | C, DC, Z              |                     |                                              |              |

| Encoding:         | 11                    | 110x                | kkkk                                         | kkkk         |

| Description:      | ment meth             | od) from th         | otracted (2's<br>ne eight bit<br>n the W reg | literal 'k'. |

| Words:            | 1                     |                     |                                              |              |

| Cycles:           | 1                     |                     |                                              |              |

| Q Cycle Activity: | Q1                    | Q2                  | Q3                                           | Q4           |

|                   | Decode                | Read<br>literal 'k' | Process<br>data                              | Write to W   |

| Example 1:        | SUBLW                 | 0x02                |                                              |              |

|                   | Before Ins            | struction           |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 1<br>?<br>?                                  |              |

|                   | After Instr           | ruction             |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 1<br>1; result is<br>0                       | positive     |

| Example 2:        | Before Ins            | struction           |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 2<br>?<br>?                                  |              |

|                   | After Instr           | ruction             |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 0<br>1; result i<br>1                        | s zero       |

| Example 3:        | Before Ins            | struction           |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 3<br>?<br>?                                  |              |

|                   | After Inst            | ruction             |                                              |              |

|                   |                       | W =<br>C =<br>Z =   | 0xFF<br>0; result is<br>0                    | negative     |

-

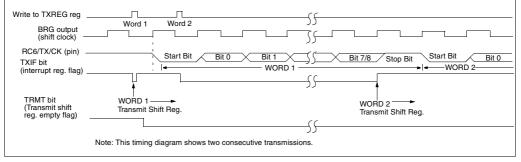

## FIGURE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                           | 200 | —        | —   | ns    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                |     | 1024Tosc | —   |       | TOSC = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low                   |     | —        | 100 | ns    |                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C62A/R62/64A/R64

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                   | 55°C to +125°C                                      |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Storage temperature                                                                                              | 65°C to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                               | 0.3V to (VDD + 0.3V)                                |

| Voltage on VDD with respect to VSS                                                                               | -0.3V to +7.5V                                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                     | 0V to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                               | 0V to +14V                                          |

| Total power dissipation (Note 1)                                                                                 | 1.0W                                                |

| Maximum current out of VSS pin                                                                                   |                                                     |

| Maximum current into VDD pin                                                                                     | 250 mA                                              |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                     | ±20 mA                                              |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                   | ±20 mA                                              |

| Maximum output current sunk by any I/O pin                                                                       | 25 mA                                               |

| Maximum output current sourced by any I/O pin                                                                    | 25 mA                                               |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined)                                                       | 200 mA                                              |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined)                                                    | 200 mA                                              |

| Maximum current sunk by PORTC and PORTD (combined)                                                               | 200 mA                                              |

| Maximum current sourced by PORTC and PORTD (combined)                                                            | 200 mA                                              |

| Note 1. Power dissipation is calculated as follows: $Pdis = Vpp \times (Ipp - \sum Ipu) + \sum (Vpp - \sum Ipu)$ | $(V_{OU}) \times (OU) + \Sigma(V_{OU} \times (OU))$ |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62A-04<br>PIC16CR62-04<br>PIC16C64A-04<br>PIC16CR64-04                                                | PIC16C62A-10<br>PIC16CR62-10<br>PIC16C64A-10<br>PIC16CR64-10                                | PIC16C62A-20<br>PIC16CR62-20<br>PIC16C64A-20<br>PIC16CR64-20                                  | PIC16LC62A-04<br>PIC16LCR62-04<br>PIC16LC64A-04<br>PIC16LCR64-04                                        | JW Devices                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                     | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq:4 MHz max.                 |

| ХТ  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 µA max. at 3.0V<br>Freq: 4 MHz max.             | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                |

| HS  | VpD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              |                                                                                             | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use<br>in HS mode                                                                   | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.           |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                          | Not recommended for use in LP mode                                                            | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at 32<br>kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 5 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

<sup>© 1997-2013</sup> Microchip Technology Inc.

#### 18.2 DC Characteristics: PIC16LC62A/R62/64A/R64-04 (Commercial, Industrial)

|              |                                                                  | Standa        | rd Ope  | rating   | Condi | tions (u | Inless otherwise stated)                                        |

|--------------|------------------------------------------------------------------|---------------|---------|----------|-------|----------|-----------------------------------------------------------------|

| DC CHA       | RACTERISTICS                                                     | Operatir      | ng temp | perature |       |          | $TA \leq +85^{\circ}C$ for industrial and                       |

|              | 1                                                                |               |         |          | 0°C   |          | $TA \le +70^{\circ}C$ for commercial                            |

| Param<br>No. | Characteristic                                                   | Sym           | Min     | Тур†     | Мах   | Units    | Conditions                                                      |

| D001         | Supply Voltage                                                   | Vdd           | 2.5     | -        | 6.0   | V        | LP, XT, RC osc configuration (DC - 4 MHz)                       |

| D002*        | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr           | -       | 1.5      | -     | V        |                                                                 |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -       | Vss      | -     | V        | See section on Power-on Reset for details                       |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD          | 0.05    | -        | -     | V/ms     | See section on Power-on Reset for details                       |

| D005         | Brown-out Reset Voltage                                          | Bvdd          | 3.7     | 4.0      | 4.3   | V        | BODEN bit in configuration word enabled                         |

| D010         | Supply Current (Note 2, 5)                                       | IDD           | -       | 2.0      | 3.8   | mA       | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)   |

| D010A        |                                                                  |               | -       | 22.5     | 48    | μA       | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |

| D015*        | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -       | 350      | 425   | μA       | BOR enabled, VDD = 5.0V                                         |

| D020         | Power-down Current                                               | IPD           | -       | 7.5      | 30    | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                         |

| D021         | (Note 3, 5)                                                      |               | -       | 0.9      | 5     | μA       | VDD = 3.0V, WDT disabled, 0°C to +70°C                          |

| D021A        |                                                                  |               | -       | 0.9      | 5     | μA       | $V_{DD} = 3.0V$ , WDT disabled, -40°C to +85°C                  |

| D023*        | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -       | 350      | 425   | μA       | BOR enabled, VDD = 5.0V                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

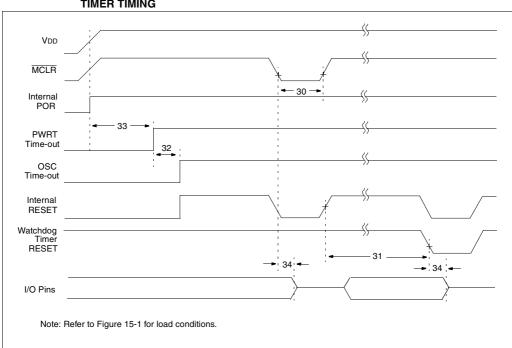

#### TABLE 18-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|----------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү      | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)                                      | TCY + 20 | —    |     | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)                                       | TCY + 20 | —    |     | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 50       | _    | _   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 50       | _    | _   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                                             | _        | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                                             |          | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10       | —    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)                                    |          | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | _        | _    | 50  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

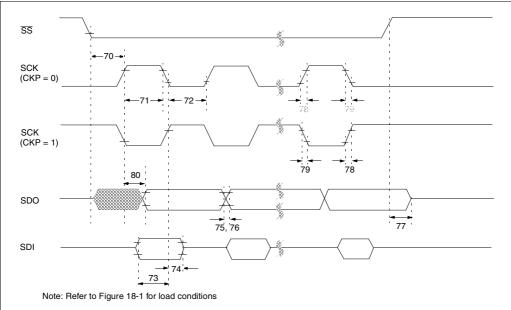

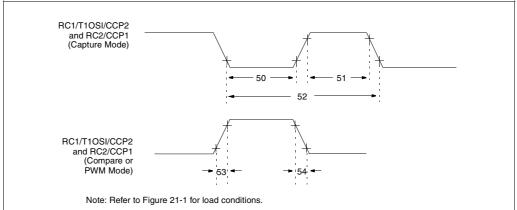

### FIGURE 21-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 21-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym  | Characteristic   |                 |                        | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|------|------------------|-----------------|------------------------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL | CCP1 and CCP2    | No Prescaler    |                        | 0.5TCY + 20           | —    | _   | ns    |                                    |

|              |      | input low time   | With Prescaler  | PIC16CR63/R65          | 10                    | —    | —   | ns    |                                    |