Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc67t-04i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

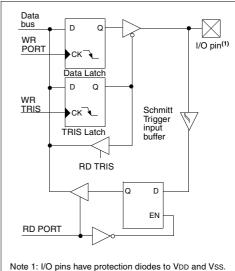

#### 5.4 **PORTD and TRISD Register**

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

Note 1: I/O pins have protection diodes to VDD and Vss.

**TABLE 5-9:** PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                          |  |

|----------|------|-----------------------|---------------------------------------------------|--|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |  |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |  |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |  |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |  |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |  |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |  |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |  |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |  |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port mode.

TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7   | Bit 6                         | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------------------------|-------|---------|-------|----------|--------------|--------|--------------------------|---------------------------|

| 08h     | PORTD | RD7     | RD6                           | RD5   | RD4     | RD3   | RD2      | RD1          | RD0    | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORTD I | PORTD Data Direction Register |       |         |       |          |              |        | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF     | OBF                           | IBOV  | PSPMODE | _     | PORTE Da | ata Directio | n Bits | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

# 10.0 CAPTURE/COMPARE/PWM (CCP) MODULE(s)

| Applicable Devices |    |    |     |     |    |     |    |     |     |    |     |     |    |    |      |

|--------------------|----|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|------|

|                    | 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP1 |

|                    | 61 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 | CCP2 |

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM master/slave duty cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP modules(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

### CCP1 module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

### CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the *Embedded Control Handbook*, "Using the CCP Modules" (AN594).

TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

### 12.4 <u>USART Synchronous Slave Mode</u>

### **Applicable Devices**

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Synchronous Slave Mode differs from Master Mode in the fact that the shift clock is supplied externally at the CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

## 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

# 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, enable bit SREN is a don't care in slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN, and clearing bit CSRC.

- If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

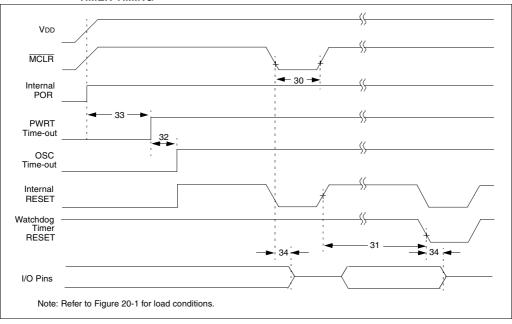

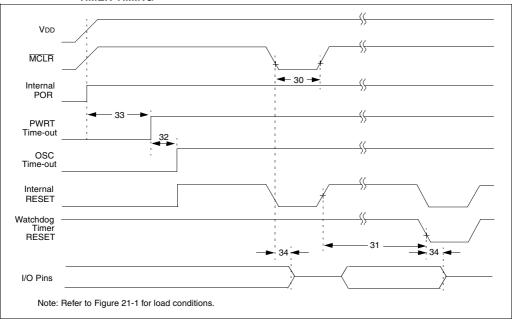

#### 13.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First a PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode, with the PWRT disabled, there will be no time-out at all. Figure 13-11, Figure 13-12, and Figure 13-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if the MCLR/VPP pin is kept low long enough, the time-outs will expire. Then bringing the MCLR/VPP pin high will begin execution immediately (Figure 13-14). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 13-10 and Table 13-11 show the reset conditions for some special function registers, while Table 13-12 shows the reset conditions for all the registers.

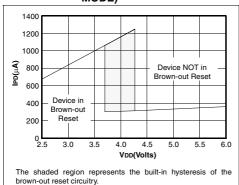

# 13.4.6 POWER CONTROL/STATUS REGISTER (PCON)

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C62/64/65.

Bit0 is  $\overline{BOR}$  (Brown-out Reset Status bit).  $\overline{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{BOR}$  cleared, indicating that a brown-out has occurred. The  $\overline{BOR}$  status bit is a "Don't Care" and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 13-5: TIME-OUT IN VARIOUS SITUATIONS, PIC16C61/62/64/65

| Oscillator Configuration | Power            | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | _                  | _         |

TABLE 13-6: TIME-OUT IN VARIOUS SITUATIONS, PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

| Ossillator Configur | Oscillator Configuration | Power-           | -up       | Brown-out        | Wake up from |

|---------------------|--------------------------|------------------|-----------|------------------|--------------|

|                     | Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Blowii-out       | SLEEP        |

|                     | XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024 Tosc    |

|                     | RC                       | 72 ms            | _         | 72 ms            | _            |

TABLE 13-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C61

| TO | PD |                                                         |

|----|----|---------------------------------------------------------|

| 1  | 1  | Power-on Reset or MCLR reset during normal operation    |

| 0  | 1  | WDT Reset                                               |

| 0  | 0  | WDT Wake-up                                             |

| 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |

TABLE 13-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C62/64/65

| POR | TO | PD |                                                         |  |

|-----|----|----|---------------------------------------------------------|--|

| 0   | 1  | 1  | Power-on Reset                                          |  |

| 0   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |  |

| 0   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |  |

| 1   | 0  | 1  | WDT Reset                                               |  |

| 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | u  | u  | MCLR reset during normal operation                      |  |

| 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |  |

Legend: x = unknown, u = unchanged

TABLE 13-9: STATUS BITS AND THEIR SIGNIFICANCE FOR PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

| POR | BOR | TO | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | Illegal, TO is set on a Power-on Reset                  |  |

| 0   | x   | x  | 0  | Illegal, PD is set on a Power-on Reset                  |  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR reset during SLEEP or interrupt wake-up from SLEEP |  |

Legend: x = unknown, u = unchanged

TABLE 13-10: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C61/62/64/65

|                                    | Program Counter       | STATUS    | PCON <sup>(2)</sup> |

|------------------------------------|-----------------------|-----------|---------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0 -                 |

| MCLR reset during normal operation | 000h                  | 000u uuuu | u-                  |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | u-                  |

| WDT Reset                          | 000h                  | 0000 luuu | u-                  |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | u-                  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | u-                  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

2: The PCON register is not implemented on the PIC16C61.

TABLE 13-11: RESET CONDITION FOR SPECIAL REGISTERS ON PIC16C62A/R62/63/R63/64A/R64/65A/R65/66/67

|                                    | Program Counter       | STATUS    | PCON |

|------------------------------------|-----------------------|-----------|------|

| Power-on Reset                     | 000h                  | 0001 1xxx | 0x   |

| MCLR reset during normal operation | 000h                  | 000u uuuu | uu   |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu | uu   |

| WDT Reset                          | 000h                  | 0000 luuu | uu   |

| Brown-out Reset                    | 000h                  | 0001 1uuu | u0   |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu | uu   |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu | uu   |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

# PIC16C6X

| IORWF             | Inclusive                                                   | OR W                         | with f           |                      |  |  |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------|------------------|----------------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                   | IORWF                        | f,d              |                      |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                              | 27                           |                  |                      |  |  |  |  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ (destination)                    |                              |                  |                      |  |  |  |  |  |

| Status Affected:  | Z                                                           |                              |                  |                      |  |  |  |  |  |

| Encoding:         | 0.0                                                         | 0100                         | dfff             | ffff                 |  |  |  |  |  |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg | is 0 the re<br>: If 'd' is 1 | sult is plac     | ced in the           |  |  |  |  |  |

| Words:            | 1                                                           |                              |                  |                      |  |  |  |  |  |

| Cycles:           | 1                                                           |                              |                  |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                          | Q2                           | Q3               | Q4                   |  |  |  |  |  |

|                   | Decode                                                      | Read<br>register<br>'f'      | Process<br>data  | Write to destination |  |  |  |  |  |

| Example           | IORWF                                                       |                              | RESULT,          | 0                    |  |  |  |  |  |

|                   | Before In                                                   |                              |                  |                      |  |  |  |  |  |

|                   |                                                             | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |  |  |  |  |  |

|                   | After Inst                                                  | • •                          | _ 0.891          |                      |  |  |  |  |  |

|                   |                                                             | RESULT                       | = 0x13           | 3                    |  |  |  |  |  |

0x93

| MOVLW             | Move Lit        | eral to V           | V                            |               |

|-------------------|-----------------|---------------------|------------------------------|---------------|

| Syntax:           | [ label ]       | MOVLW               | / k                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                              |               |

| Operation:        | $k\to(W)$       |                     |                              |               |

| Status Affected:  | None            |                     |                              |               |

| Encoding:         | 11              | 00xx                | kkkk                         | kkkk          |

| Description:      |                 |                     | k' is loaded<br>ares will as |               |

| Words:            | 1               |                     |                              |               |

| Cycles:           | 1               |                     |                              |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                           | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data              | Write to<br>W |

| Example           | MOVLW           | 0x5A                |                              |               |

|                   | After Inst      |                     |                              |               |

|                   |                 | W =                 | 0x5A                         |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

| MOVF                                    | Move f                                                                                                                                                                                                                                                  |                         |                 |                      |  |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:                                 | [ label ]                                                                                                                                                                                                                                               | MOVF                    | f,d             |                      |  |  |  |  |  |

| Operands:                               | $\begin{aligned} 0 &\leq f \leq 127 \\ d &\in [0,1] \end{aligned}$                                                                                                                                                                                      |                         |                 |                      |  |  |  |  |  |

| Operation:                              | $(f) \rightarrow (destination)$                                                                                                                                                                                                                         |                         |                 |                      |  |  |  |  |  |

| Status Affected:                        | Z                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |  |  |

| Encoding:                               | 00                                                                                                                                                                                                                                                      | 1000                    | dfff            | ffff                 |  |  |  |  |  |

| Description:                            | The contents of register f is moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flaq Z is affected. |                         |                 |                      |  |  |  |  |  |

| Words:                                  | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |  |  |

| Cycles:                                 | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |  |  |

| Q Cycle Activity:                       | Q1                                                                                                                                                                                                                                                      | Q2                      | Q3              | Q4                   |  |  |  |  |  |

|                                         | Decode                                                                                                                                                                                                                                                  | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |  |  |

| Example                                 | MOVF                                                                                                                                                                                                                                                    | FSR,                    | 0               |                      |  |  |  |  |  |

| After Instruction W = value in FSR regi |                                                                                                                                                                                                                                                         |                         |                 |                      |  |  |  |  |  |

Z = 1

| MOVWF             | Move W                                      | to f                    |                 |                       |  |  |  |  |

|-------------------|---------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [ label ]                                   | MOVWI                   | F f             |                       |  |  |  |  |

| Operands:         | $0 \leq f \leq 127$                         |                         |                 |                       |  |  |  |  |

| Operation:        | $(W) \rightarrow (f)$                       |                         |                 |                       |  |  |  |  |

| Status Affected:  | None                                        |                         |                 |                       |  |  |  |  |

| Encoding:         | 00                                          | 0000                    | 1fff            | ffff                  |  |  |  |  |

| Description:      | Move data                                   | from W r                | egister to      | register              |  |  |  |  |

| Words:            | 1                                           |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                                           |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                          | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode                                      | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | MOVWF                                       | OPTIC                   | ON_REG          |                       |  |  |  |  |

|                   | Before Instruction  OPTION = 0xFF  W = 0x4F |                         |                 |                       |  |  |  |  |

|                   | After Inst                                  | ruction<br>OPTION       | = 0x4F          | =                     |  |  |  |  |

W = 0x4F

SLEEP Syntax:

[ label ] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

$0 \rightarrow WDT$  prescaler,

$1 \rightarrow \overline{10}$  $0 \rightarrow \overline{PD}$

TO, PD Status Affected:

Encoding:

0000 0110 0011

Description: The power-down status bit, PD is

cleared. Time-out status bit,  $\overline{\text{TO}}$  is set. Watchdog Timer and its pres-

caler are cleared.

The processor is put into SLEEP mode with the oscillator stopped. See

Section 13.8 for more details.

Words:

Cycles:

Q Cycle Activity: Q1 Q2 Q3 Q4

Decode No-No-Go to Operation Operation Sleep

Example: SLEEP **SUBLW** Subtract W from Literal

Syntax: [ label ] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$

C. DC. Z Status Affected:

Encoding: 110x kkkk kkkk

The W register is subtracted (2's comple-Description: ment method) from the eight bit literal 'k'.

The result is placed in the W register.

Words:

Cycles:

Q1 Q2 Q4 Q Cycle Activity: Q3 Decode Read Process Write to W

Example 1: SUBLW 0x02

Before Instruction

W С ? ?

literal 'k'

After Instruction

W

С 1; result is positive

data

Ζ

Example 2: Before Instruction

> 2 W С ? =

Z

After Instruction

W

С 1; result is zero

z

Example 3: Before Instruction

> W 3 С ? = ?

After Instruction

W 0xFF

С 0; result is negative

z

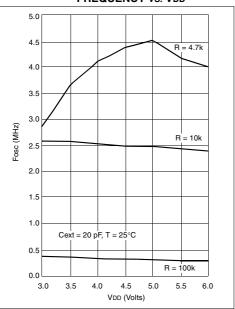

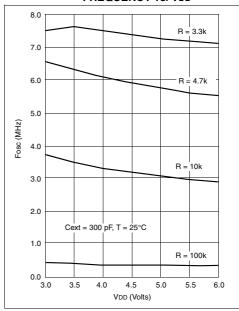

FIGURE 16-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

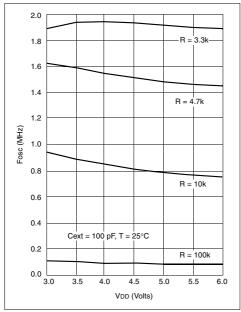

FIGURE 16-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

FIGURE 16-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

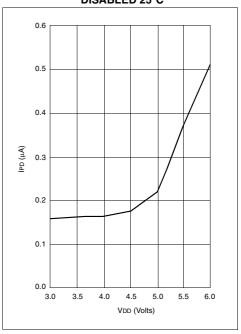

FIGURE 16-5: TYPICAL IPD VS. VDD WATCHDOG TIMER DISABLED 25°C

DC CHARACTERISTICS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

17.3 DC Characteristics: PIC16C62/64-04 (Commercial, Industrial)

> PIC16C62/64-10 (Commercial, Industrial) PIC16C62/64-20 (Commercial, Industrial) PIC16LC62/64-04 (Commercial, Industrial)

> > Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C  $\leq$  TA  $\leq$  +85°C for industrial and

0°C

$\leq$  TA  $\leq$  +70°C for commercial Operating voltage VDD range as described in DC spec Section 17.1

|              |                                    | and Sed | ction 17.2        |          | -       |       | •                                                                                              |

|--------------|------------------------------------|---------|-------------------|----------|---------|-------|------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                     | Sym     | Min               | Typ<br>† | Max     | Units | Conditions                                                                                     |

|              | Input Low Voltage                  |         |                   |          |         |       |                                                                                                |

|              | I/O ports                          | VIL     |                   |          |         |       |                                                                                                |

| D030         | with TTL buffer                    |         | Vss               | -        | 0.15VDD | V     | For entire VDD range                                                                           |

| D030A        |                                    |         | Vss               | -        | V8.0    | V     | $4.5V \le V_{DD} \le 5.5V$                                                                     |

| D031         | with Schmitt Trigger buffer        |         | Vss               | -        | 0.2VDD  | V     |                                                                                                |

| D032         | MCLR, OSC1 (in RC mode)            |         | Vss               | -        | 0.2VDD  | V     |                                                                                                |

| D033         | OSC1 (in XT, HS and LP)            |         | Vss               | -        | 0.3VDD  | V     | Note1                                                                                          |

|              | Input High Voltage                 |         |                   |          |         |       |                                                                                                |

|              | I/O ports                          | VIH     |                   |          |         |       |                                                                                                |

| D040         | with TTL buffer                    |         | 2.0               | -        | VDD     | V     | $4.5V \le V$ DD $\le 5.5V$                                                                     |

| D040A        |                                    |         | 0.25VDD<br>+ 0.8V | -        | VDD     | V     | For entire VDD range                                                                           |

| D041         | with Schmitt Trigger buffer        |         | 0.8VDD            | -        | VDD     |       | For entire VDD range                                                                           |

| D042         | MCLR                               |         | 0.8VDD            | -        | VDD     | V     |                                                                                                |

| D042A        | OSC1 (XT, HS and LP)               |         | 0.7VDD            | -        | VDD     | V     | Note1                                                                                          |

| D043         | OSC1 (in RC mode)                  |         | 0.9VDD            | -        | VDD     | V     |                                                                                                |

| D070         | PORTB weak pull-up current         | IPURB   | 50                | 200      | 400     | μΑ    | VDD = 5V, VPIN = VSS                                                                           |

|              | Input Leakage Current (Notes 2, 3) |         |                   |          |         |       |                                                                                                |

| D060         | I/O ports                          | lı∟     | -                 | -        | ±1      | μА    | $Vss \leq VPIN \leq VDD, \ Pin \ at \ hi-impedance$                                            |

| D061         | MCLR, RA4/T0CKI                    |         | -                 | -        | ±5      | μΑ    | $Vss \le VPIN \le VDD$                                                                         |

| D063         | OSC1                               |         | -                 | -        | ±5      | μА    | $\label{eq:VSS} Vss \leq VPIN \leq VDD, \ XT, \ HS \ and \\ LP \ osc \ configuration$          |

|              | Output Low Voltage                 |         |                   |          |         |       |                                                                                                |

| D080         | I/O ports                          | VOL     | -                 | -        | 0.6     | V     | IOL = $8.5 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| D083         | OSC2/CLKOUT (RC osc config)        |         | -                 | -        | 0.6     | V     | IOL = $1.6 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

|              | Output High Voltage                |         |                   |          |         |       |                                                                                                |

| D090         | I/O ports (Note 3)                 | Vон     | VDD-0.7           | -        | -       | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                           |

| D092         | OSC2/CLKOUT (RC osc config)        |         | VDD-0.7           | -        | -       | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +85°C                                                   |

| D150*        | Open-Drain High Voltage            | Vod     | -                 | -        | 14      | V     | RA4 pin                                                                                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

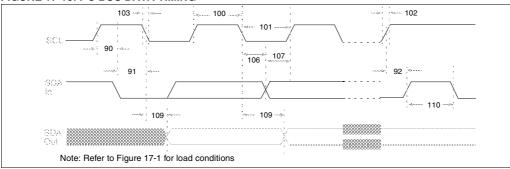

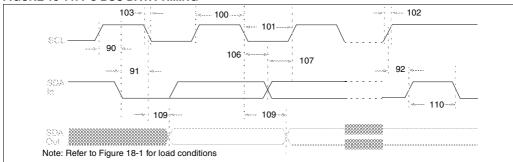

### FIGURE 17-10: I<sup>2</sup>C BUS DATA TIMING

TABLE 17-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|---------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100           | THIGH   | Clock high time        | 100 kHz mode | 4.0        | _    | μS    | Device must operate at a minimum of 1.5 MHz      |

|               |         |                        | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a mini-<br>mum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 101           | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a mini-<br>mum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a mini-<br>mum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102           | TR      | SDA and SCL rise       | 100 kHz mode | -          | 1000 | ns    |                                                  |

|               |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10 to 400 pF          |

| 103           | TF      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                                  |

|               |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10 to 400 pF          |

| 90            | Tsu:sta | START condition        | 100 kHz mode | 4.7        | _    | μS    | Only relevant for repeated                       |

|               |         | setup time             | 400 kHz mode | 0.6        | _    | μS    | START condition                                  |

| 91            | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μS    | After this period the first clock                |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μs    | pulse is generated                               |

| 106           | THD:DAT | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                                  |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107           | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | _    | ns    | Note 2                                           |

|               |         |                        | 400 kHz mode | 100        | _    | ns    |                                                  |

| 92            | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | _    | μs    |                                                  |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μs    |                                                  |

| 109           | TAA     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|               |         | clock                  | 400 kHz mode | _          | _    | ns    |                                                  |

| 110           | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                        |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | before a new transmission can start              |

|               | Cb      | Bus capacitive loading |              | _          | 400  | pF    | defined region (min. 300 ns) of                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

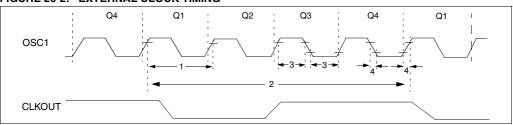

### 18.5 <u>Timing Diagrams and Specifications</u>

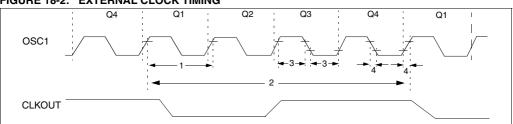

FIGURE 18-2: EXTERNAL CLOCK TIMING

TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         |     |      |        |       |                    |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2                | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

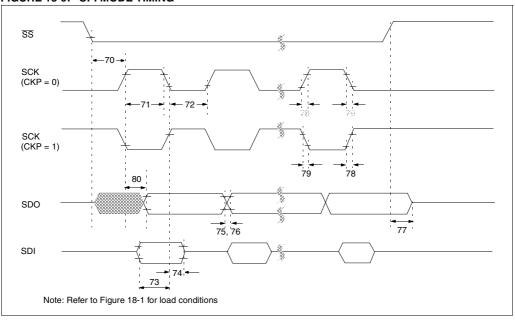

FIGURE 18-9: SPI MODE TIMING

**TABLE 18-8: SPI MODE REQUIREMENTS**

| Parameter No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|---------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71*           | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72*           | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75*           | TdoR                  | SDO data output rise time                | 1        | 10   | 25  | ns    |            |

| 76*           | TdoF                  | SDO data output fall time                | I        | 10   | 25  | ns    |            |

| 77*           | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78*           | TscR                  | SCK output rise time (master mode)       | I        | 10   | 25  | ns    |            |

| 79*           | TscF                  | SCK output fall time (master mode)       | ı        | 10   | 25  | ns    |            |

| 80*           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## FIGURE 18-11: I<sup>2</sup>C BUS DATA TIMING

### TABLE 18-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                  |

|---------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | THIGH   | Clock high time        | 100 kHz mode | 4.0        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| 101*          | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| 102*          | TR      | SDA and SCL rise       | 100 kHz mode | _          | 1000 | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF        |

| 103*          | TF      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                             |

|               |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF        |

| 90*           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | _    | μS    | Only relevant for repeated                  |

|               |         | setup time             | 400 kHz mode | 0.6        | _    | μS    | START condition                             |

| 91*           | THD:STA | START condition hold   | 100 kHz mode | 4.0        |      | μS    | After this period the first clock           |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μS    | pulse is generated                          |

| 106*          | THD:DAT | Data input hold time   | 100 kHz mode | 0          |      | ns    |                                             |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| 107*          | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | _    | ns    | Note 2                                      |

|               |         |                        | 400 kHz mode | 100        | _    | ns    |                                             |

| 92*           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | _    | μS    |                                             |

|               |         | time                   | 400 kHz mode | 0.6        | _    | μS    |                                             |

| 109*          | TAA     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                      |

|               |         | clock                  | 400 kHz mode | _          | _    | ns    |                                             |

| 110*          | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | before a new transmission can start         |

|               | Cb      | Bus capacitive loading |              | _          | 400  | pF    |                                             |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

**DC CHARACTERISTICS**

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

19.3 DC Characteristics: PIC16C65-04 (Commercial, Industrial)

PIC16C65-10 (Commercial, Industrial) PIC16C65-20 (Commercial, Industrial) PIC16LC65-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C ≤ TA ≤ +85°C for industrial and

0°C ≤ TA ≤ +70°C for commercial

Operating voltage VDD range as described in DC spec Section 19.1 and

|              |                             | Operating voltage VDD range as described in DC spec Section 19.1 and Section 19.2 |                  |          |         |       |                                                                                                |

|--------------|-----------------------------|-----------------------------------------------------------------------------------|------------------|----------|---------|-------|------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic              | Sym                                                                               | Min              | Typ<br>† | Max     | Units | Conditions                                                                                     |

| NO.          | Input Low Voltage           |                                                                                   |                  |          |         |       |                                                                                                |

|              | I/O ports                   | VIL                                                                               |                  |          |         |       |                                                                                                |

| D030         | with TTL buffer             | V                                                                                 | Vss              | _        | 0.15Vpp | V     | For entire VDD range                                                                           |

| D030A        |                             |                                                                                   | Vss              | _        | 0.8V    | ٧     | 4.5V ≤ VDD ≤ 5.5V                                                                              |

| D031         | with Schmitt Trigger buffer |                                                                                   | Vss              | -        | 0.2VDD  | V     |                                                                                                |

| D032         | MCLR, OSC1(in RC mode)      |                                                                                   | Vss              | -        | 0.2VDD  | V     |                                                                                                |

| D033         | OSC1 (in XT, HS and LP)     |                                                                                   | Vss              | -        | 0.3VDD  | ٧     | Note1                                                                                          |

|              | Input High Voltage          |                                                                                   |                  |          |         |       |                                                                                                |

|              | I/O ports                   | VIH                                                                               |                  | -        |         |       |                                                                                                |

| D040         | with TTL buffer             |                                                                                   | 2.0              | -        | VDD     | V     | $4.5V \leq V_{DD} \leq 5.5V$                                                                   |

| D040A        |                             |                                                                                   | 0.25VDD+<br>0.8V | -        | VDD     | V     | For entire VDD range                                                                           |

| D041         | with Schmitt Trigger buffer |                                                                                   | 0.8Vpp           | _        | Vpp     |       | For entire VDD range                                                                           |

| D042         | MCLR                        |                                                                                   | 0.8VDD           | _        | VDD     | V     | To online VEE range                                                                            |

| D042A        | OSC1 (XT, HS and LP)        |                                                                                   | 0.7 VDD          | _        | VDD     | ٧     | Note1                                                                                          |

| D043         | OSC1 (in RC mode)           |                                                                                   | 0.9VDD           | _        | VDD     | V     |                                                                                                |

| D070         | PORTB weak pull-up current  | IPURB                                                                             | 50               | 250      | 400     | μА    | VDD = 5V, VPIN = VSS                                                                           |

|              | Input Leakage Current       |                                                                                   |                  |          |         |       |                                                                                                |

|              | (Notes 2, 3)                |                                                                                   |                  |          |         |       |                                                                                                |

| D060         | I/O ports                   | Iı∟                                                                               | -                | -        | ±1      | μΑ    | $Vss \leq VPIN \leq VDD, \ Pin \ at \ hiimpedance$                                             |

| D061         | MCLR, RA4/T0CKI             |                                                                                   | -                | -        | ±5      | μΑ    | $Vss \leq VPIN \leq VDD$                                                                       |

| D063         | OSC1                        |                                                                                   | -                | -        | ±5      | μА    | $Vss \leq VPIN \leq VDD, \ XT, \ HS, \ and \ LP \ osc \ configuration$                         |

|              | Output Low Voltage          |                                                                                   |                  |          |         |       |                                                                                                |

| D080         | I/O ports                   | VOL                                                                               | -                | -        | 0.6     | V     | IOL = $8.5 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| D083         | OSC2/CLKOUT (RC osc config) |                                                                                   | -                | -        | 0.6     | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                                                    |

|              | Output High Voltage         |                                                                                   |                  |          |         |       |                                                                                                |

| D090         | I/O ports (Note 3)          | Vон                                                                               | VDD-0.7          | -        | -       | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                           |

| D092         | OSC2/CLKOUT (RC osc config) |                                                                                   | VDD-0.7          | -        | -       | V     | IOH = -1.3 mA, VDD = $4.5V$ , $-40^{\circ}$ C to $+85^{\circ}$ C                               |

| D150*        | Open-Drain High Voltage     | VOD                                                                               | -                | -        | 14      | V     | RA4 pin                                                                                        |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

### 20.5 Timing Diagrams and Specifications

FIGURE 20-2: EXTERNAL CLOCK TIMING

TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param | Sym   | Characteristic                   | Min | Typ† | Max    | Units | Conditions         |

|-------|-------|----------------------------------|-----|------|--------|-------|--------------------|

| No.   |       |                                  |     |      |        |       |                    |

|       | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|       |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|       |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|       |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|       |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|       |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|       |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|       |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|       |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1     | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|       |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|       |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|       |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|       |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|       |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|       |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|       |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|       |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|       |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|       |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2     | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3*    | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|       | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|       |       |                                  | 15  |      |        | ns    | HS oscillator      |

| 4*    | TosR, | External Clock in (OSC1) Rise or | _   |      | 25     | ns    | XT oscillator      |

|       | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|       |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

FIGURE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

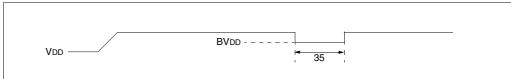

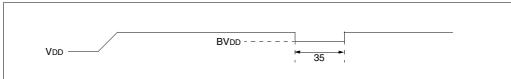

FIGURE 20-5: BROWN-OUT RESET TIMING

TABLE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                | Min | Тур†      | Max | Units | Conditions                |

|---------------|-------|-----------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                        | 2   | _         |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32            | Tost  | Oscillation Start-up Timer Period             |     | 1024 Tosc |     | _     | TOSC = OSC1 period        |

| 33*           | Tpwrt | Power-up Timer Period                         | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34            | Tioz  | I/O Hi-impedance from MCLR Low or WDT reset   | -   | _         | 2.1 | μs    |                           |

| 35            | TBOR  | Brown-out Reset Pulse Width                   | 100 | _         | _   | μs    | VDD ≤ BVDD (D005)         |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

FIGURE 21-5: BROWN-OUT RESET TIMING

TABLE 21-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                | Min | Typ†      | Max | Units | Conditions                |

|---------------|-------|-----------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                        | 2   | _         |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32            | Tost  | Oscillation Start-up Timer Period             |     | 1024 Tosc |     | _     | TOSC = OSC1 period        |

| 33*           | Tpwrt | Power-up Timer Period                         | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34            | Tıoz  | I/O Hi-impedance from MCLR Low or WDT reset   | _   | _         | 2.1 | μs    |                           |

| 35            | TBOR  | Brown-out Reset Pulse Width                   | 100 | _         | _   | μs    | VDD ≤ BVDD (D005)         |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

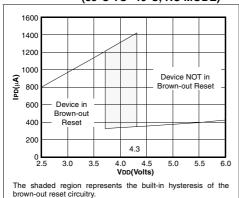

FIGURE 23-8: TYPICAL IPD vs. VDD BROWN-OUT DETECT ENABLED (RC MODE)

FIGURE 23-9: MAXIMUM IPD vs. VDD BROWN-OUT DETECT ENABLED (85°C TO -40°C, RC MODE)

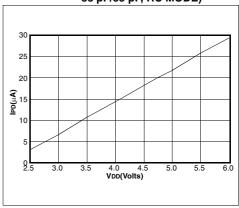

FIGURE 23-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

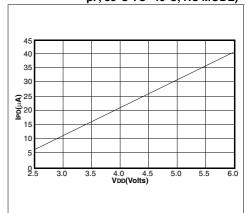

FIGURE 23-11: MAXIMUM IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, 85°C TO -40°C, RC MODE)

### PIN COMPATIBILITY

Devices that have the same package type and VDD, VSS and  $\overline{\text{MCLR}}$  pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PlC16C56 and PlC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PlC16C62 is compatible with the PlC16C63, but not the PlC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

TABLE F-1: PIN COMPATIBLE DEVICES

| Pin Compatible Devices                                                                                                                                                                                                                                                                                                                                                                       | Package           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PIC12C508, PIC12C509, PIC12C671, PIC12C672                                                                                                                                                                                                                                                                                                                                                   | 8-pin             |

| PIC16C154, PIC16CR154, PIC16C156, PIC16CR156, PIC16CR156, PIC16CS2, PIC16C54, PIC16CS4A, PIC16CS54A, PIC16CS54A, PIC16CS6, PIC16CS6, PIC16CS6A, PIC16CS6A, PIC16CS5A, PIC16CS5A, PIC16CS54, PIC16CS54, PIC16CS56, PIC16CS58 PIC16C620, PIC16C621, PIC16C622 PIC16C641, PIC16C642, PIC16C661, PIC16C661, PIC16C6710, PIC16C71, PIC16C711, PIC16C715 PIC16F83, PIC16CR83, PIC16F84A, PIC16CR84 | 18-pin,<br>20-pin |

| PIC16C55, PIC16C57, PIC16CR57B                                                                                                                                                                                                                                                                                                                                                               | 28-pin            |

| PIC16CR62, PIC16C62A, PIC16C63, PIC16CR63, PIC16C66, PIC16C72, PIC16C73A, PIC16C76                                                                                                                                                                                                                                                                                                           | 28-pin            |