Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 784                                                           |

| Number of Logic Elements/Cells | 1862                                                          |

| Total RAM Bits                 | 25088                                                         |

| Number of I/O                  | 113                                                           |

| Number of Gates                | 20000                                                         |

| Voltage - Supply               | 3V ~ 3.6V                                                     |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 144-LQFP Exposed Pad                                          |

| Supplier Device Package        | 144-TQFP (20x20)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xillinx/xc4020xl-2ht144c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Set/Reset

An asynchronous storage element input (SR) can be configured as either set or reset. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a Global Set/Reset pulse during normal operation, and the effect of a pulse on the SR pin of the CLB. All three set/reset functions for any single flip-flop are controlled by the same configuration data bit.

The set/reset state can be independently specified for each flip-flop. This input can also be independently disabled for either flip-flop.

The set/reset state is specified by using the INIT attribute, or by placing the appropriate set or reset flip-flop library symbol.

SR is active High. It is not invertible within the CLB.

### Global Set/Reset

A separate Global Set/Reset line (not shown in Figure 1) sets or clears each storage element during power-up, re-configuration, or when a dedicated Reset net is driven active. This global net (GSR) does not compete with other routing resources; it uses a dedicated distribution network.

Each flip-flop is configured as either globally set or reset in the same way that the local set/reset (SR) is specified. Therefore, if a flip-flop is set by SR, it is also set by GSR. Similarly, a reset flip-flop is reset by both SR and GSR.

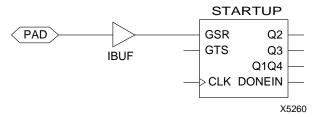

Figure 2: Schematic Symbols for Global Set/Reset

GSR can be driven from any user-programmable pin as a global reset input. To use this global net, place an input pad and input buffer in the schematic or HDL code, driving the GSR pin of the STARTUP symbol. (See Figure 2.) A specific pin location can be assigned to this input using a LOC attribute or property, just as with any other user-programmable pad. An inverter can optionally be inserted after the input buffer to invert the sense of the Global Set/Reset signal.

Alternatively, GSR can be driven from any internal node.

### Data Inputs and Outputs

The source of a storage element data input is programmable. It is driven by any of the functions F', G', and H', or by the Direct In (DIN) block input. The flip-flops or latches drive the XQ and YQ CLB outputs.

Two fast feed-through paths are available, as shown in Figure 1. A two-to-one multiplexer on each of the XQ and YQ outputs selects between a storage element output and any of the control inputs. This bypass is sometimes used by the automated router to repower internal signals.

### **Control Signals**

Multiplexers in the CLB map the four control inputs (C1 - C4 in Figure 1) into the four internal control signals (H1, DIN/H2, SR/H0, and EC). Any of these inputs can drive any of the four internal control signals.

When the logic function is enabled, the four inputs are:

- EC Enable Clock

- SR/H0 Asynchronous Set/Reset or H function generator Input 0

- DIN/H2 Direct In or H function generator Input 2

- H1 H function generator Input 1.

When the memory function is enabled, the four inputs are:

- EC Enable Clock

- WE Write Enable

- D0 Data Input to F and/or G function generator

- D1 Data input to G function generator (16x1 and 16x2 modes) or 5th Address bit (32x1 mode).

### Using FPGA Flip-Flops and Latches

The abundance of flip-flops in the XC4000 Series invites pipelined designs. This is a powerful way of increasing performance by breaking the function into smaller subfunctions and executing them in parallel, passing on the results through pipeline flip-flops. This method should be seriously considered wherever throughput is more important than latency.

To include a CLB flip-flop, place the appropriate library symbol. For example, FDCE is a D-type flip-flop with clock enable and asynchronous clear. The corresponding latch symbol (for the XC4000X only) is called LDCE.

In XC4000 Series devices, the flip flops can be used as registers or shift registers without blocking the function generators from performing a different, perhaps unrelated task. This ability increases the functional capacity of the devices.

The CLB setup time is specified between the function generator inputs and the clock input K. Therefore, the specified CLB flip-flop setup time includes the delay through the function generator.

### Using Function Generators as RAM

Optional modes for each CLB make the memory look-up tables in the F' and G' function generators usable as an array of Read/Write memory cells. Available modes are level-sensitive (similar to the XC4000/A/H families), edge-triggered, and dual-port edge-triggered. Depending on the selected mode, a single CLB can be configured as either a 16x2, 32x1, or 16x1 bit array.

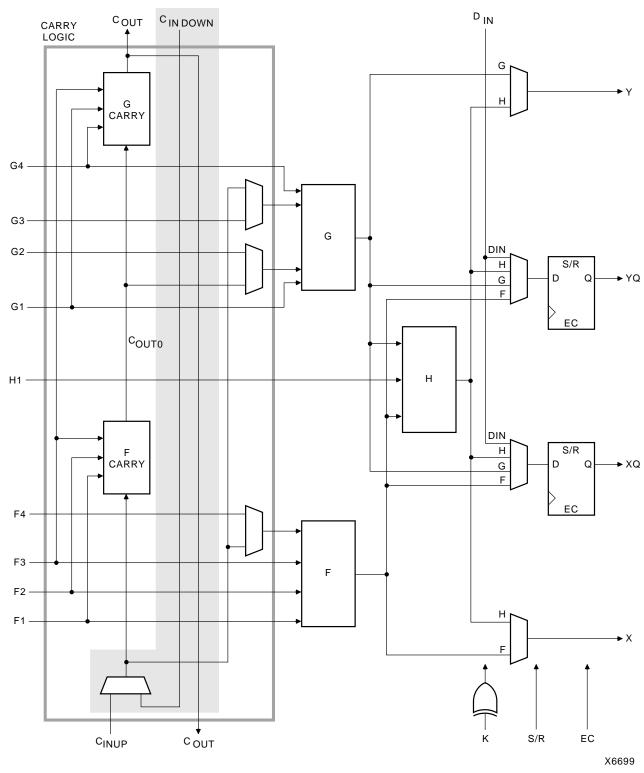

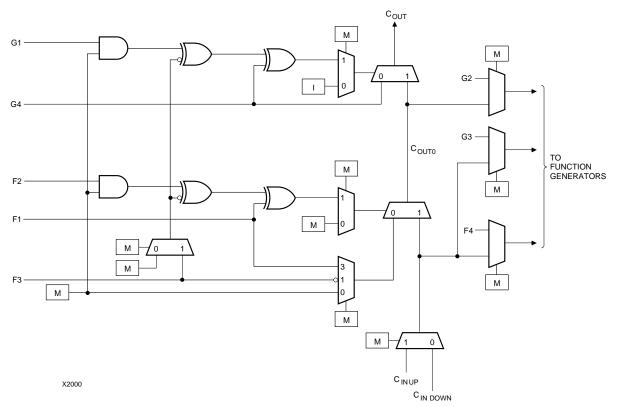

Figure 13: Fast Carry Logic in XC4000E CLB (shaded area not present in XC4000X)

Figure 14: Detail of XC4000E Dedicated Carry Logic

# Input/Output Blocks (IOBs)

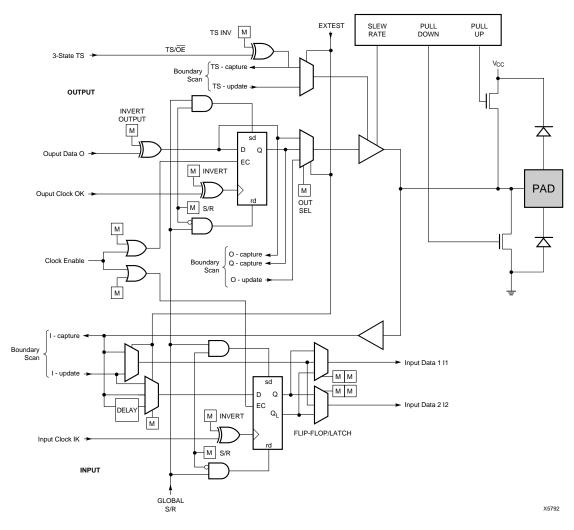

User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be configured for input, output, or bidirectional signals.

Figure 15 shows a simplified block diagram of the XC4000E IOB. A more complete diagram which includes the boundary scan logic of the XC4000E IOB can be found in Figure 40 on page 43, in the "Boundary Scan" section.

The XC4000X IOB contains some special features not included in the XC4000E IOB. These features are highlighted in a simplified block diagram found in Figure 16, and discussed throughout this section. When XC4000X special features are discussed, they are clearly identified in the text. Any feature not so identified is present in both XC4000E and XC4000X devices.

### IOB Input Signals

Two paths, labeled I1 and I2 in Figure 15 and Figure 16, bring input signals into the array. Inputs also connect to an input register that can be programmed as either an edge-triggered flip-flop or a level-sensitive latch.

The choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are available, and some combinations of latches and flip-flops can be implemented in a single IOB, as described in the *XACT Libraries Guide*.

The XC4000E inputs can be globally configured for either TTL (1.2V) or 5.0 volt CMOS thresholds, using an option in the bitstream generation software. There is a slight input hysteresis of about 300mV. The XC4000E output levels are also configurable; the two global adjustments of input threshold and output level are independent.

Inputs on the XC4000XL are TTL compatible and 3.3V CMOS compatible. Outputs on the XC4000XL are pulled to the 3.3V positive supply.

The inputs of XC4000 Series 5-Volt devices can be driven by the outputs of any 3.3-Volt device, if the 5-Volt inputs are in TTL mode.

Supported sources for XC4000 Series device inputs are shown in Table 8.

Table 8: Supported Sources for XC4000 Series Device Inputs

|                                                                         |             | 00E/EX<br>Inputs | XC4000XL<br>Series Inputs |

|-------------------------------------------------------------------------|-------------|------------------|---------------------------|

| Source                                                                  | 5 V,<br>TTL | 5 V,<br>CMOS     | 3.3 V<br>CMOS             |

| Any device, Vcc = 3.3 V,<br>CMOS outputs                                | V           | Unreli           | V                         |

| XC4000 Series, Vcc = 5 V, TTL outputs                                   | V           | -able<br>Data    | √                         |

| Any device, $Vcc = 5 \text{ V}$ , TTL outputs $(Voh \le 3.7 \text{ V})$ | V           | Data             | √                         |

| Any device, Vcc = 5 V,<br>CMOS outputs                                  | V           | √                | √                         |

### XC4000XL 5-Volt Tolerant I/Os

The I/Os on the XC4000XL are fully 5-volt tolerant even though the  $V_{\rm CC}$  is 3.3 volts. This allows 5 V signals to directly connect to the XC4000XL inputs without damage, as shown in Table 8. In addition, the 3.3 volt  $V_{\rm CC}$  can be applied before or after 5 volt signals are applied to the I/Os. This makes the XC4000XL immune to power supply sequencing problems.

### **Registered Inputs**

The I1 and I2 signals that exit the block can each carry either the direct or registered input signal.

The input and output storage elements in each IOB have a common clock enable input, which, through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC pin on the XC4000 Series CLB. It cannot be inverted within the IOB.

The storage element behavior is shown in Table 9.

Table 9: Input Register Functionality (active rising edge is shown)

| Mode            | Clock | Clock<br>Enable | D | Q  |

|-----------------|-------|-----------------|---|----|

| Power-Up or GSR | X     | X               | Х | SR |

| Flip-Flop       |       | 1*              | D | D  |

|                 | 0     | Х               | Х | Q  |

| Latch           | 1     | 1*              | Х | Q  |

|                 | 0     | 1*              | D | D  |

| Both            | Χ     | 0               | Х | Q  |

Legend:

X Don't care

Rising edge

SR Set or Reset value. Reset is default.

0\* Input is Low or unconnected (default value)

1\* Input is High or unconnected (default value)

### **Optional Delay Guarantees Zero Hold Time**

The data input to the register can optionally be delayed by several nanoseconds. With the delay enabled, the setup time of the input flip-flop is increased so that normal clock routing does not result in a positive hold-time requirement. A positive hold time requirement can lead to unreliable, temperature- or processing-dependent operation.

The input flip-flop setup time is defined between the data measured at the device I/O pin and the clock input at the IOB (not at the clock pin). Any routing delay from the device clock pin to the clock input of the IOB must, therefore, be subtracted from this setup time to arrive at the real setup time requirement relative to the device pins. A short specified setup time might, therefore, result in a negative setup time at the device pins, i.e., a positive hold-time requirement.

When a delay is inserted on the data line, more clock delay can be tolerated without causing a positive hold-time requirement. Sufficient delay eliminates the possibility of a data hold-time requirement at the external pin. The maximum delay is therefore inserted as the default.

The XC4000E IOB has a one-tap delay element: either the delay is inserted (default), or it is not. The delay guarantees a zero hold time with respect to clocks routed through any of the XC4000E global clock buffers. (See "Global Nets and Buffers (XC4000E only)" on page 35 for a description of the global clock buffers in the XC4000E.) For a shorter input register setup time, with non-zero hold, attach a NODELAY attribute or property to the flip-flop.

The XC4000X IOB has a two-tap delay element, with choices of a full delay, a partial delay, or no delay. The attributes or properties used to select the desired delay are shown in Table 10. The choices are no added attribute, MEDDELAY, and NODELAY. The default setting, with no added attribute, ensures no hold time with respect to any of the XC4000X clock buffers, including the Global Low-Skew buffers. MEDDELAY ensures no hold time with respect to the Global Early buffers. Inputs with NODELAY may have a positive hold time with respect to all clock buffers. For a description of each of these buffers, see "Global Nets and Buffers (XC4000X only)" on page 37.

Table 10: XC4000X IOB Input Delay Element

| Value            | When to Use                            |

|------------------|----------------------------------------|

| full delay       | Zero Hold with respect to Global       |

| (default, no     | Low-Skew Buffer, Global Early Buffer   |

| attribute added) |                                        |

| MEDDELAY         | Zero Hold with respect to Global Early |

|                  | Buffer                                 |

| NODELAY          | Short Setup, positive Hold time        |

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

or clear on reset and after configuration. Other than the global GSR net, no user-controlled set/reset signal is available to the I/O flip-flops. The choice of set or clear applies to both the initial state of the flip-flop and the response to the Global Set/Reset pulse. See "Global Set/Reset" on page 11 for a description of how to use GSR.

### **JTAG Support**

Embedded logic attached to the IOBs contains test structures compatible with IEEE Standard 1149.1 for boundary scan testing, permitting easy chip and board-level testing. More information is provided in "Boundary Scan" on page 42.

### **Three-State Buffers**

A pair of 3-state buffers is associated with each CLB in the array. (See Figure 27 on page 30.) These 3-state buffers can be used to drive signals onto the nearest horizontal longlines above and below the CLB. They can therefore be used to implement multiplexed or bidirectional buses on the horizontal longlines, saving logic resources. Programmable pull-up resistors attached to these longlines help to implement a wide wired-AND function.

The buffer enable is an active-High 3-state (i.e. an active-Low enable), as shown in Table 13.

Another 3-state buffer with similar access is located near each I/O block along the right and left edges of the array. (See Figure 33 on page 34.)

The horizontal longlines driven by the 3-state buffers have a weak keeper at each end. This circuit prevents undefined floating levels. However, it is overridden by any driver, even a pull-up resistor.

Special longlines running along the perimeter of the array can be used to wire-AND signals coming from nearby IOBs or from internal longlines. These longlines form the wide edge decoders discussed in "Wide Edge Decoders" on page 27.

### Three-State Buffer Modes

The 3-state buffers can be configured in three modes:

- · Standard 3-state buffer

- Wired-AND with input on the I pin

- Wired OR-AND

#### Standard 3-State Buffer

All three pins are used. Place the library element BUFT. Connect the input to the I pin and the output to the O pin. The T pin is an active-High 3-state (i.e. an active-Low enable). Tie the T pin to Ground to implement a standard buffer.

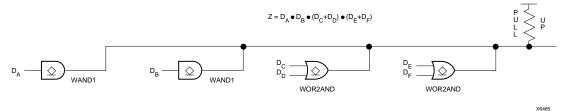

### Wired-AND with Input on the I Pin

The buffer can be used as a Wired-AND. Use the WAND1 library symbol, which is essentially an open-drain buffer. WAND4, WAND8, and WAND16 are also available. See the *XACT Libraries Guide* for further information.

The T pin is internally tied to the I pin. Connect the input to the I pin and the output to the O pin. Connect the outputs of all the WAND1s together and attach a PULLUP symbol.

### **Wired OR-AND**

The buffer can be configured as a Wired OR-AND. A High level on either input turns off the output. Use the WOR2AND library symbol, which is essentially an open-drain 2-input OR gate. The two input pins are functionally equivalent. Attach the two inputs to the I0 and I1 pins and tie the output to the O pin. Tie the outputs of all the WOR2ANDs together and attach a PULLUP symbol.

### Three-State Buffer Examples

Figure 21 shows how to use the 3-state buffers to implement a wired-AND function. When all the buffer inputs are High, the pull-up resistor(s) provide the High output.

Figure 22 shows how to use the 3-state buffers to implement a multiplexer. The selection is accomplished by the buffer 3-state signal.

Pay particular attention to the polarity of the T pin when using these buffers in a design. Active-High 3-state (T) is identical to an active-Low output enable, as shown in Table 13.

**Table 13: Three-State Buffer Functionality**

| IN | Т | OUT |

|----|---|-----|

| X  | 1 | Z   |

| IN | 0 | IN  |

Figure 21: Open-Drain Buffers Implement a Wired-AND Function

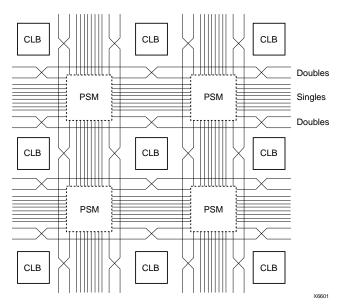

Figure 28: Single- and Double-Length Lines, with Programmable Switch Matrices (PSMs)

### **Double-Length Lines**

The double-length lines consist of a grid of metal segments, each twice as long as the single-length lines: they run past two CLBs before entering a switch matrix. Double-length lines are grouped in pairs with the switch matrices staggered, so that each line goes through a switch matrix at every other row or column of CLBs (see Figure 28).

There are four vertical and four horizontal double-length lines associated with each CLB. These lines provide faster signal routing over intermediate distances, while retaining routing flexibility. Double-length lines are connected by way of the programmable switch matrices. Routing connectivity is shown in Figure 27.

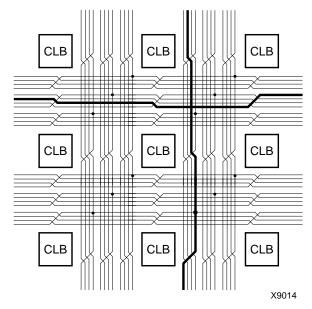

### Quad Lines (XC4000X only)

XC4000X devices also include twelve vertical and twelve horizontal quad lines per CLB row and column. Quad lines are four times as long as the single-length lines. They are interconnected via buffered switch matrices (shown as diamonds in Figure 27 on page 30). Quad lines run past four CLBs before entering a buffered switch matrix. They are grouped in fours, with the buffered switch matrices staggered, so that each line goes through a buffered switch matrix at every fourth CLB location in that row or column. (See Figure 29.)

The buffered switch matrixes have four pins, one on each edge. All of the pins are bidirectional. Any pin can drive any or all of the other pins.

Each buffered switch matrix contains one buffer and six pass transistors. It resembles the programmable switch matrix shown in Figure 26, with the addition of a programmable buffer. There can be up to two independent inputs

Figure 29: Quad Lines (XC4000X only)

and up to two independent outputs. Only one of the independent inputs can be buffered.

The place and route software automatically uses the timing requirements of the design to determine whether or not a quad line signal should be buffered. A heavily loaded signal is typically buffered, while a lightly loaded one is not. One scenario is to alternate buffers and pass transistors. This allows both vertical and horizontal quad lines to be buffered at alternating buffered switch matrices.

Due to the buffered switch matrices, quad lines are very fast. They provide the fastest available method of routing heavily loaded signals for long distances across the device.

### Longlines

Longlines form a grid of metal interconnect segments that run the entire length or width of the array. Longlines are intended for high fan-out, time-critical signal nets, or nets that are distributed over long distances. In XC4000X devices, quad lines are preferred for critical nets, because the buffered switch matrices make them faster for high fan-out nets.

Two horizontal longlines per CLB can be driven by 3-state or open-drain drivers (TBUFs). They can therefore implement unidirectional or bidirectional buses, wide multiplexers, or wired-AND functions. (See "Three-State Buffers" on page 26 for more details.)

Each horizontal longline driven by TBUFs has either two (XC4000E) or eight (XC4000X) pull-up resistors. To activate these resistors, attach a PULLUP symbol to the long-line net. The software automatically activates the appropriate number of pull-ups. There is also a weak keeper at each end of these two horizontal longlines. This

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

IOB inputs and outputs interface with the octal lines via the single-length interconnect lines. Single-length lines are also used for communication between the octals and double-length lines, quads, and longlines within the CLB array.

Segmentation into buffered octals was found to be optimal for distributing signals over long distances around the device.

### **Global Nets and Buffers**

Both the XC4000E and the XC4000X have dedicated global networks. These networks are designed to distribute clocks and other high fanout control signals throughout the devices with minimal skew. The global buffers are described in detail in the following sections. The text descriptions and diagrams are summarized in Table 15. The table shows which CLB and IOB clock pins can be sourced by which global buffers.

In both XC4000E and XC4000X devices, placement of a library symbol called BUFG results in the software choosing the appropriate clock buffer, based on the timing requirements of the design. The detailed information in these sections is included only for reference.

### Global Nets and Buffers (XC4000E only)

Four vertical longlines in each CLB column are driven exclusively by special global buffers. These longlines are in addition to the vertical longlines used for standard interconnect. The four global lines can be driven by either of two types of global buffers. The clock pins of every CLB and IOB can also be sourced from local interconnect.

Two different types of clock buffers are available in the XC4000E:

- Primary Global Buffers (BUFGP)

- Secondary Global Buffers (BUFGS)

Four Primary Global buffers offer the shortest delay and negligible skew. Four Secondary Global buffers have slightly longer delay and slightly more skew due to potentially heavier loading, but offer greater flexibility when used to drive non-clock CLB inputs.

The Primary Global buffers must be driven by the semi-dedicated pads. The Secondary Global buffers can be sourced by either semi-dedicated pads or internal nets.

Each CLB column has four dedicated vertical Global lines. Each of these lines can be accessed by one particular Primary Global buffer, or by any of the Secondary Global buffers, as shown in Figure 34. Each corner of the device has one Primary buffer and one Secondary buffer.

IOBs along the left and right edges have four vertical global longlines. Top and bottom IOBs can be clocked from the global lines in the adjacent CLB column.

A global buffer should be specified for all timing-sensitive global signal distribution. To use a global buffer, place a BUFGP (primary buffer), BUFGS (secondary buffer), or BUFG (either primary or secondary buffer) element in a schematic or in HDL code. If desired, attach a LOC attribute or property to direct placement to the designated location. For example, attach a LOC=L attribute or property to a BUFGS symbol to direct that a buffer be placed in one of the two Secondary Global buffers on the left edge of the device, or a LOC=BL to indicate the Secondary Global buffer on the bottom edge of the device, on the left.

**Table 15: Clock Pin Access**

|                                                                | XC4   | 000E  |        | XC4000X        |                |                   |  |

|----------------------------------------------------------------|-------|-------|--------|----------------|----------------|-------------------|--|

|                                                                | BUFGP | BUFGS | BUFGLS | L & R<br>BUFGE | T & B<br>BUFGE | Inter-<br>connect |  |

| All CLBs in Quadrant                                           | √     | √     | V      | V              | V              | V                 |  |

| All CLBs in Device                                             | V     | √     | V      |                |                | V                 |  |

| IOBs on Adjacent Vertical<br>Half Edge                         | √     | V     | V      | V              | √              | V                 |  |

| IOBs on Adjacent Vertical<br>Full Edge                         | V     | V     | V      | <b>V</b>       |                | V                 |  |

| IOBs on Adjacent Horizontal<br>Half Edge (Direct)              |       |       |        | <b>V</b>       |                | V                 |  |

| IOBs on Adjacent Horizontal<br>Half Edge (through CLB globals) | V     | V     | V      | 1              | V              | V                 |  |

| IOBs on Adjacent Horizontal<br>Full Edge (through CLB globals) | V     | V     | V      |                |                | V                 |  |

L = Left, R = Right, T = Top, B = Bottom

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

**Table 16: Pin Descriptions**

|               | 1/0            | I/O                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name      | During Config. | After Config.                | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Permanently [ | _              |                              | 1 2000pus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VCC           | I              | I                            | Eight or more (depending on package) connections to the nominal +5 V supply voltage (+3.3 V for low-voltage devices). All must be connected, and each must be decoupled with a $0.01 - 0.1 \mu\text{F}$ capacitor to Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND           | I              | I                            | Eight or more (depending on package type) connections to Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CCLK          | I or O         | I                            | During configuration, Configuration Clock (CCLK) is an output in Master modes or Asynchronous Peripheral mode, but is an input in Slave mode and Synchronous Peripheral mode. After configuration, CCLK has a weak pull-up resistor and can be selected as the Readback Clock. There is no CCLK High or Low time restriction on XC4000 Series devices, except during Readback. See "Violating the Maximum High and Low Time Specification for the Readback Clock" on page 56 for an explanation of this exception.                                                                                                                                                                                                                                                                                                                                                                      |

| DONE          | I/O            | 0                            | DONE is a bidirectional signal with an optional internal pull-up resistor. As an output, it indicates the completion of the configuration process. As an input, a Low level on DONE can be configured to delay the global logic initialization and the enabling of outputs. The optional pull-up resistor is selected as an option in the XACT step program that creates the configuration bitstream. The resistor is included by default.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PROGRAM       | ı              | I                            | PROGRAM is an active Low input that forces the FPGA to clear its configuration memory. It is used to initiate a configuration cycle. When PROGRAM goes High, the FPGA finishes the current clear cycle and executes another complete clear cycle, before it goes into a WAIT state and releases INIT.  The PROGRAM pin has a permanent weak pull-up, so it need not be externally pulled up to Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| User I/O Pins | That Can       | Have Spe                     | ecial Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RDY/BUSY      | 0              | I/O                          | During Peripheral mode configuration, this pin indicates when it is appropriate to write another byte of data into the FPGA. The same status is also available on D7 in Asynchronous Peripheral mode, if a read operation is performed when the device is selected. After configuration, RDY/BUSY is a user-programmable I/O pin. RDY/BUSY is pulled High with a high-impedance pull-up prior to INIT going High.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RCLK          | 0              | I/O                          | During Master Parallel configuration, each change on the A0-A17 outputs (A0 - A21 for XC4000X) is preceded by a rising edge on $\overline{RCLK}$ , a redundant output signal. $\overline{RCLK}$ is useful for clocked PROMs. It is rarely used during configuration. After configuration, $\overline{RCLK}$ is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| M0, M1, M2    | I              | I (M0),<br>O (M1),<br>I (M2) | As Mode inputs, these pins are sampled after $\overline{\text{INIT}}$ goes High to determine the configuration mode to be used. After configuration, M0 and M2 can be used as inputs, and M1 can be used as a 3-state output. These three pins have no associated input or output registers. During configuration, these pins have weak pull-up resistors. For the most popular configuration mode, Slave Serial, the mode pins can thus be left unconnected. The three mode inputs can be individually configured with or without weak pull-up or pull-down resistors. A pull-down resistor value of 4.7 k $\Omega$ is recommended. These pins can only be used as inputs or outputs when called out by special schematic definitions. To use these pins, place the library components MD0, MD1, and MD2 instead of the usual pad symbols. Input or output buffers must still be used. |

| TDO           | 0              | 0                            | If boundary scan is used, this pin is the Test Data Output. If boundary scan is not used, this pin is a 3-state output without a register, after configuration is completed. This pin can be user output only when called out by special schematic definitions. To use this pin, place the library component TDO instead of the usual pad symbol. An output buffer must still be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **Table 16: Pin Descriptions (Continued)**

|                                                            | I/O<br>During   | I/O<br>After          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                   | Config.         | Config.               | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

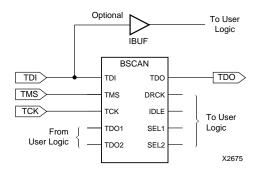

| TDI, TCK,<br>TMS                                           | I               | I/O<br>or I<br>(JTAG) | If boundary scan is used, these pins are Test Data In, Test Clock, and Test Mode Select inputs respectively. They come directly from the pads, bypassing the IOBs. These pins can also be used as inputs to the CLB logic after configuration is completed. If the BSCAN symbol is not placed in the design, all boundary scan functions are inhibited once configuration is completed, and these pins become user-programmable I/O. The pins can be used automatically or user-constrained. To use them, use "LOC=" or place the library components TDI, TCK, and TMS instead of the usual pad symbols. Input or output buffers must still be used.                                                                                                       |

| HDC                                                        | 0               | I/O                   | High During Configuration (HDC) is driven High until the I/O go active. It is available as a control output indicating that configuration is not yet completed. After configuration, HDC is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDC                                                        | 0               | I/O                   | Low During Configuration (LDC) is driven Low until the I/O go active. It is available as a control output indicating that configuration is not yet completed. After configuration, LDC is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ĪNĪT                                                       | I/O             | I/O                   | Before and during configuration, $\overline{\text{INIT}}$ is a bidirectional signal. A 1 k $\Omega$ - 10 k $\Omega$ external pull-up resistor is recommended. As an active-Low open-drain output, $\overline{\text{INIT}}$ is held Low during the power stabilization and internal clearing of the configuration memory. As an active-Low input, it can be used to hold the FPGA in the internal WAIT state before the start of configuration. Master mode devices stay in a WAIT state an additional 30 to 300 $\mu$ s after $\overline{\text{INIT}}$ has gone High. During configuration, a Low on this output indicates that a configuration data error has occurred. After the I/O go active, $\overline{\text{INIT}}$ is a user-programmable I/O pin. |

| PGCK1 -<br>PGCK4<br>(XC4000E<br>only)                      | Weak<br>Pull-up | I or I/O              | Four Primary Global inputs each drive a dedicated internal global net with short delay and minimal skew. If not used to drive a global buffer, any of these pins is a user-programmable I/O.  The PGCK1-PGCK4 pins drive the four Primary Global Buffers. Any input pad symbol connected directly to the input of a BUFGP symbol is automatically placed on one of these pins.                                                                                                                                                                                                                                                                                                                                                                             |

| SGCK1 -<br>SGCK4<br>(XC4000E<br>only)                      | Weak<br>Pull-up | I or I/O              | Four Secondary Global inputs each drive a dedicated internal global net with short delay and minimal skew. These internal global nets can also be driven from internal logic. If not used to drive a global net, any of these pins is a user-programmable I/O pin. The SGCK1-SGCK4 pins provide the shortest path to the four Secondary Global Buffers. Any input pad symbol connected directly to the input of a BUFGS symbol is automatically placed on one of these pins.                                                                                                                                                                                                                                                                               |

| GCK1 -<br>GCK8<br>(XC4000X<br>only)                        | Weak<br>Pull-up | I or I/O              | Eight inputs can each drive a Global Low-Skew buffer. In addition, each can drive a Global Early buffer. Each pair of global buffers can also be driven from internal logic, but must share an input signal. If not used to drive a global buffer, any of these pins is a user-programmable I/O.  Any input pad symbol connected directly to the input of a BUFGLS or BUFGE symbol is automatically placed on one of these pins.                                                                                                                                                                                                                                                                                                                           |

| FCLK1 -<br>FCLK4<br>(XC4000XLA<br>and<br>XC4000XV<br>only) | Weak<br>Pull-up | I or I/O              | Four inputs can each drive a Fast Clock (FCLK) buffer which can deliver a clock signal to any IOB clock input in the octant of the die served by the Fast Clock buffer. Two Fast Clock buffers serve the two IOB octants on the left side of the die and the other two Fast Clock buffers serve the two IOB octants on the right side of the die. On each side of the die, one Fast Clock buffer serves the upper octant and the other serves the lower octant. If not used to drive a Fast Clock buffer, any of these pins is a user-programmable I/O.                                                                                                                                                                                                    |

Figure 41 on page 44 is a diagram of the XC4000 Series boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

XC4000 Series devices can also be configured through the boundary scan logic. See "Readback" on page 55.

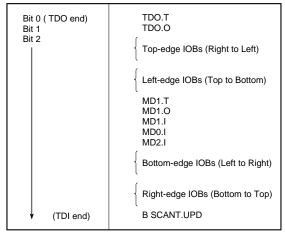

### **Data Registers**

The primary data register is the boundary scan register. For each IOB pin in the FPGA, bonded or not, it includes three bits for In, Out and 3-State Control. Non-IOB pins have appropriate partial bit population for In or Out only. PROGRAM, CCLK and DONE are not included in the boundary scan register. Each EXTEST CAPTURE-DR state captures all In, Out, and 3-state pins.

The data register also includes the following non-pin bits: TDO.T, and TDO.O, which are always bits 0 and 1 of the

data register, respectively, and BSCANT.UPD, which is always the last bit of the data register. These three boundary scan bits are special-purpose Xilinx test signals.

The other standard data register is the single flip-flop BYPASS register. It synchronizes data being passed through the FPGA to the next downstream boundary scan device.

The FPGA provides two additional data registers that can be specified using the BSCAN macro. The FPGA provides two user pins (BSCAN.SEL1 and BSCAN.SEL2) which are the decodes of two user instructions. For these instructions, two corresponding pins (BSCAN.TDO1 and BSCAN.TDO2) allow user scan data to be shifted out on TDO. The data register clock (BSCAN.DRCK) is available for control of test logic which the user may wish to implement with CLBs. The NAND of TCK and RUN-TEST-IDLE is also provided (BSCAN.IDLE).

Figure 40: Block Diagram of XC4000E IOB with Boundary Scan (some details not shown). XC4000X Boundary Scan Logic is Identical.

**Table 17: Boundary Scan Instructions**

|   | uction |   | Test<br>Selected   | TDO Source         | I/O Data<br>Source |

|---|--------|---|--------------------|--------------------|--------------------|

| 0 | 0      | 0 | EXTEST             | DR                 | DR                 |

| 0 | 0      | 1 | SAMPLE/PR<br>ELOAD | DR                 | Pin/Logic          |

| 0 | 1      | 0 | USER 1             | BSCAN.<br>TDO1     | User Logic         |

| 0 | 1      | 1 | USER 2             | BSCAN.<br>TDO2     | User Logic         |

| 1 | 0      | 0 | READBACK           | Readback<br>Data   | Pin/Logic          |

| 1 | 0      | 1 | CONFIGURE          | DOUT               | Disabled           |

| 1 | 1      | 0 | Reserved           |                    |                    |

| 1 | 1      | 1 | BYPASS             | Bypass<br>Register | _                  |

X6075

Figure 42: Boundary Scan Bit Sequence

# **Avoiding Inadvertent Boundary Scan**

If TMS or TCK is used as user I/O, care must be taken to ensure that at least one of these pins is held constant during configuration. In some applications, a situation may occur where TMS or TCK is driven during configuration. This may cause the device to go into boundary scan mode and disrupt the configuration process.

To prevent activation of boundary scan during configuration, do either of the following:

- TMS: Tie High to put the Test Access Port controller in a benign RESET state

- TCK: Tie High or Low—don't toggle this clock input.

For more information regarding boundary scan, refer to the Xilinx Application Note XAPP 017.001, "Boundary Scan in XC4000E Devices."

Figure 43: Boundary Scan Schematic Example

# Configuration

Configuration is the process of loading design-specific programming data into one or more FPGAs to define the functional operation of the internal blocks and their interconnections. This is somewhat like loading the command registers of a programmable peripheral chip. XC4000 Series devices use several hundred bits of configuration data per CLB and its associated interconnects. Each configuration bit defines the state of a static memory cell that controls either a function look-up table bit, a multiplexer input, or an interconnect pass transistor. The XACT step development system translates the design into a netlist file. It automatically partitions, places and routes the logic and generates the configuration data in PROM format.

# **Special Purpose Pins**

Three configuration mode pins (M2, M1, M0) are sampled prior to configuration to determine the configuration mode. After configuration, these pins can be used as auxiliary connections. M2 and M0 can be used as inputs, and M1 can be used as an output. The XACT step development system does not use these resources unless they are explicitly specified in the design entry. This is done by placing a special pad symbol called MD2, MD1, or MD0 instead of the input or output pad symbol.

In XC4000 Series devices, the mode pins have weak pull-up resistors during configuration. With all three mode pins High, Slave Serial mode is selected, which is the most popular configuration mode. Therefore, for the most common configuration mode, the mode pins can be left unconnected. (Note, however, that the internal pull-up resistor value can be as high as 100 k $\Omega$ .) After configuration, these pins can individually have weak pull-up or pull-down resistors, as specified in the design. A pull-down resistor value of 4.7 k $\Omega$  is recommended.

These pins are located in the lower left chip corner and are near the readback nets. This location allows convenient routing if compatibility with the XC2000 and XC3000 family conventions of M0/RT, M1/RD is desired.

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

is passed through and is captured by each FPGA when it recognizes the 0010 preamble. Following the length-count data, each FPGA outputs a High on DOUT until it has received its required number of data frames.

After an FPGA has received its configuration data, it passes on any additional frame start bits and configuration data on DOUT. When the total number of configuration clocks applied after memory initialization equals the value of the 24-bit length count, the FPGAs begin the start-up sequence and become operational together. FPGA I/O are normally released two CCLK cycles after the last configuration bit is received. Figure 47 on page 53 shows the start-up timing for an XC4000 Series device.

The daisy-chained bitstream is not simply a concatenation of the individual bitstreams. The PROM file formatter must be used to combine the bitstreams for a daisy-chained configuration.

### **Multi-Family Daisy Chain**

All Xilinx FPGAs of the XC2000, XC3000, and XC4000 Series use a compatible bitstream format and can, therefore, be connected in a daisy chain in an arbitrary sequence. There is, however, one limitation. The lead device must belong to the highest family in the chain. If the chain contains XC4000 Series devices, the master normally cannot be an XC2000 or XC3000 device.

The reason for this rule is shown in Figure 47 on page 53. Since all devices in the chain store the same length count value and generate or receive one common sequence of CCLK pulses, they all recognize length-count match on the same CCLK edge, as indicated on the left edge of Figure 47. The master device then generates additional CCLK pulses until it reaches its finish point F. The different families generate or require different numbers of additional CCLK pulses until they reach F. Not reaching F means that the device does not really finish its configuration, although DONE may have gone High, the outputs became active, and the internal reset was released. For the XC4000 Series device, not reaching F means that readback cannot be ini-

tiated and most boundary scan instructions cannot be used.

The user has some control over the relative timing of these events and can, therefore, make sure that they occur at the proper time and the finish point F is reached. Timing is controlled using options in the bitstream generation software.

### XC3000 Master with an XC4000 Series Slave

Some designers want to use an inexpensive lead device in peripheral mode and have the more precious I/O pins of the XC4000 Series devices all available for user I/O. Figure 44 provides a solution for that case.

This solution requires one CLB, one IOB and pin, and an internal oscillator with a frequency of up to 5 MHz as a clock source. The XC3000 master device must be configured with late Internal Reset, which is the default option.

One CLB and one IOB in the lead XC3000-family device are used to generate the additional CCLK pulse required by the XC4000 Series devices. When the lead device removes the internal RESET signal, the 2-bit shift register responds to its clock input and generates an active Low output signal for the duration of the subsequent clock period. An external connection between this output and CCLK thus creates the extra CCLK pulse.

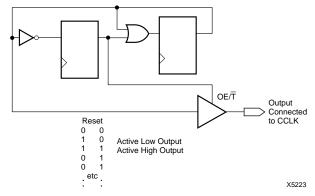

Figure 44: CCLK Generation for XC3000 Master Driving an XC4000 Series Slave

# **Setting CCLK Frequency**

For Master modes, CCLK can be generated in either of two frequencies. In the default slow mode, the frequency ranges from 0.5 MHz to 1.25 MHz for XC4000E and XC4000EX devices and from 0.6 MHz to 1.8 MHz for XC4000XL devices. In fast CCLK mode, the frequency ranges from 4 MHz to 10 MHz for XC4000E/EX devices and from 5 MHz to 15 MHz for XC4000XL devices. The frequency is selected by an option when running the bitstream generation software. If an XC4000 Series Master is driving an XC3000- or XC2000-family slave, slow CCLK mode must be used. In addition, an XC4000XL device driving a XC4000E or XC4000EX should use slow mode. Slow mode is the default

Table 19: XC4000 Series Data Stream Formats

| Data Type          | All Other<br>Modes (D0) |

|--------------------|-------------------------|

| Fill Byte          | 11111111b               |

| Preamble Code      | 0010b                   |

| Length Count       | COUNT(23:0)             |

| Fill Bits          | 1111b                   |

| Start Field        | Ob                      |

| Data Frame         | DATA(n-1:0)             |

| CRC or Constant    | xxxx (CRC)              |

| Field Check        | or 0110b                |

| Extend Write Cycle | _                       |

| Postamble          | 01111111b               |

| Start-Up Bytes     | xxh                     |

| Legend:            |                         |

| Not shaded         | Once per bitstream      |

| Light              | Once per data frame     |

| Dark               | Once per device         |

### **Data Stream Format**

The data stream ("bitstream") format is identical for all configuration modes.

The data stream formats are shown in Table 19. Bit-serial data is read from left to right, and byte-parallel data is effectively assembled from this serial bitstream, with the first bit in each byte assigned to D0.

The configuration data stream begins with a string of eight ones, a preamble code, followed by a 24-bit length count and a separator field of ones. This header is followed by the actual configuration data in frames. The length and number of frames depends on the device type (see Table 20 and Table 21). Each frame begins with a start field and ends with an error check. A postamble code is required to signal the end of data for a single device. In all cases, additional start-up bytes of data are required to provide four clocks for the startup sequence at the end of configuration. Long daisy chains require additional startup bytes to shift the last data through the chain. All startup bytes are don't-cares; these bytes are not included in bitstreams created by the Xilinx software.

A selection of CRC or non-CRC error checking is allowed by the bitstream generation software. The non-CRC error checking tests for a designated end-of-frame field for each frame. For CRC error checking, the software calculates a running CRC and inserts a unique four-bit partial check at the end of each frame. The 11-bit CRC check of the last frame of an FPGA includes the last seven data bits.

Detection of an error results in the suspension of data loading and the pulling down of the  $\overline{\text{INIT}}$  pin. In Master modes, CCLK and address signals continue to operate externally. The user must detect  $\overline{\text{INIT}}$  and initialize a new configuration by pulsing the  $\overline{\text{PROGRAM}}$  pin Low or cycling Vcc.

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

Low. During this time delay, or as long as the PROGRAM input is asserted, the configuration logic is held in a Configuration Memory Clear state. The configuration-memory frames are consecutively initialized, using the internal oscillator.

At the end of each complete pass through the frame addressing, the power-on time-out delay circuitry and the level of the PROGRAM pin are tested. If neither is asserted, the logic initiates one additional clearing of the configuration frames and then tests the NIT input.

### Initialization

During initialization and configuration, user pins HDC,  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE provide status outputs for the system interface. The outputs  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE are held Low and HDC is held High starting at the initial application of power.

The open drain  $\overline{INIT}$  pin is released after the final initialization pass through the frame addresses. There is a deliberate delay of 50 to 250  $\mu s$  (up to 10% longer for low-voltage devices) before a Master-mode device recognizes an inactive  $\overline{INIT}$ . Two internal clocks after the  $\overline{INIT}$  pin is recognized as High, the FPGA samples the three mode lines to determine the configuration mode. The appropriate interface lines become active and the configuration preamble and data can be loaded.Configuration

The 0010 preamble code indicates that the following 24 bits represent the length count. The length count is the total number of configuration clocks needed to load the complete configuration data. (Four additional configuration clocks are required to complete the configuration process, as discussed below.) After the preamble and the length count have been passed through to all devices in the daisy chain, DOUT is held High to prevent frame start bits from reaching any daisy-chained devices.

A specific configuration bit, early in the first frame of a master device, controls the configuration-clock rate and can increase it by a factor of eight. Therefore, if a fast configuration clock is selected by the bitstream, the slower clock rate is used until this configuration bit is detected.

Each frame has a start field followed by the frame-configuration data bits and a frame error field. If a frame data error is detected, the FPGA halts loading, and signals the error by pulling the open-drain  $\overline{\text{INIT}}$  pin Low. After all configuration frames have been loaded into an FPGA, DOUT again follows the input data so that the remaining data is passed on to the next device.

## **Delaying Configuration After Power-Up**

There are two methods of delaying configuration after power-up: put a logic Low on the PROGRAM input, or pull the bidirectional INIT pin Low, using an open-collector (open-drain) driver. (See Figure 46 on page 50.)

A Low on the PROGRAM input is the more radical approach, and is recommended when the power-supply

rise time is excessive or poorly defined. As long as \$\overline{PRO}\$ GRAM is Low, the FPGA keeps clearing its configuration memory. When \$\overline{PROGRAM}\$ goes High, the configuration memory is cleared one more time, followed by the beginning of configuration, provided the \$\overline{INIT}\$ input is not externally held Low. Note that a Low on the \$\overline{PROGRAM}\$ input automatically forces a Low on the \$\overline{INIT}\$ output. The XC4000 Series \$\overline{PROGRAM}\$ pin has a permanent weak pull-up.

Using an open-collector or open-drain driver to hold  $\overline{INIT}$  Low before the beginning of configuration causes the FPGA to wait after completing the configuration memory clear operation. When  $\overline{INIT}$  is no longer held Low externally, the device determines its configuration mode by capturing its mode pins, and is ready to start the configuration process. A master device waits up to an additional 250  $\mu s$  to make sure that any slaves in the optional daisy chain have seen that  $\overline{INIT}$  is High.

### Start-Up

Start-up is the transition from the configuration process to the intended user operation. This transition involves a change from one clock source to another, and a change from interfacing parallel or serial configuration data where most outputs are 3-stated, to normal operation with I/O pins active in the user-system. Start-up must make sure that the user-logic 'wakes up' gracefully, that the outputs become active without causing contention with the configuration signals, and that the internal flip-flops are released from the global Reset or Set at the right time.

Figure 47 describes start-up timing for the three Xilinx families in detail. The configuration modes can use any of the four timing sequences.

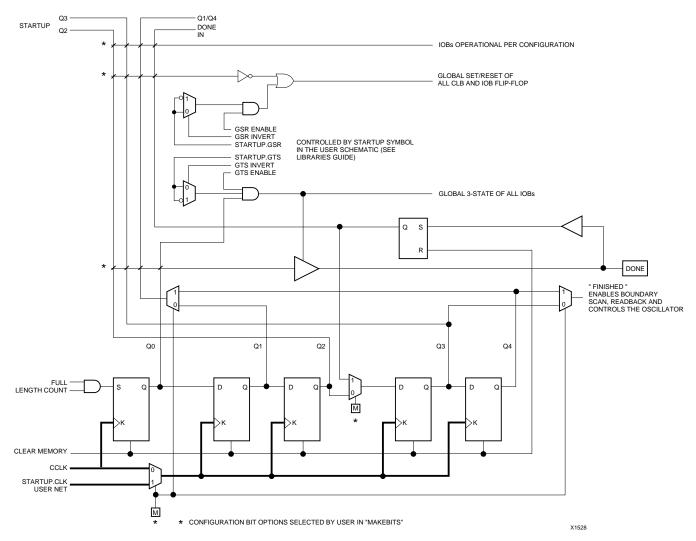

To access the internal start-up signals, place the STARTUP library symbol.

### **Start-up Timing**

Different FPGA families have different start-up sequences.

The XC2000 family goes through a fixed sequence. DONE goes High and the internal global Reset is de-activated one CCLK period after the I/O become active.

The XC3000A family offers some flexibility. DONE can be programmed to go High one CCLK period before or after the I/O become active. Independent of DONE, the internal global Reset is de-activated one CCLK period before or after the I/O become active.

The XC4000 Series offers additional flexibility. The three events — DONE going High, the internal Set/Reset being de-activated, and the user I/O going active — can all occur in any arbitrary sequence. Each of them can occur one CCLK period before or after, or simultaneous with, any of the others. This relative timing is selected by means of software options in the bitstream generation software.

# Product Obsolete or Under Obsolescence XC4000E and XC4000X Series Field Programmable Gate Arrays

The default option, and the most practical one, is for DONE to go High first, disconnecting the configuration data source and avoiding any contention when the I/Os become active one clock later. Reset/Set is then released another clock period later to make sure that user-operation starts from stable internal conditions. This is the most common sequence, shown with heavy lines in Figure 47, but the designer can modify it to meet particular requirements.

Normally, the start-up sequence is controlled by the internal device oscillator output (CCLK), which is asynchronous to the system clock.

XC4000 Series offers another start-up clocking option, UCLK\_NOSYNC. The three events described above need not be triggered by CCLK. They can, as a configuration option, be triggered by a user clock. This means that the device can wake up in synchronism with the user system.

When the UCLK\_SYNC option is enabled, the user can externally hold the open-drain DONE output Low, and thus stall all further progress in the start-up sequence until DONE is released and has gone High. This option can be used to force synchronization of several FPGAs to a common user clock, or to guarantee that all devices are successfully configured before any I/Os go active.

If either of these two options is selected, and no user clock is specified in the design or attached to the device, the chip could reach a point where the configuration of the device is complete and the Done pin is asserted, but the outputs do not become active. The solution is either to recreate the bitstream specifying the start-up clock as CCLK, or to supply the appropriate user clock.

### Start-up Sequence

The Start-up sequence begins when the configuration memory is full, and the total number of configuration clocks

received since  $\overline{\text{INIT}}$  went High equals the loaded value of the length count.

The next rising clock edge sets a flip-flop Q0, shown in Figure 48. Q0 is the leading bit of a 5-bit shift register. The outputs of this register can be programmed to control three events.

- The release of the open-drain DONE output

- The change of configuration-related pins to the user function, activating all IOBs.

- The termination of the global Set/Reset initialization of all CLB and IOB storage elements.

The DONE pin can also be wire-ANDed with DONE pins of other FPGAs or with other external signals, and can then be used as input to bit Q3 of the start-up register. This is called "Start-up Timing Synchronous to Done In" and is selected by either CCLK SYNC or UCLK SYNC.

When DONE is not used as an input, the operation is called "Start-up Timing Not Synchronous to DONE In," and is selected by either CCLK\_NOSYNC or UCLK\_NOSYNC.

As a configuration option, the start-up control register beyond Q0 can be clocked either by subsequent CCLK pulses or from an on-chip user net called STARTUP.CLK. These signals can be accessed by placing the STARTUP library symbol.

### **Start-up from CCLK**

If CCLK is used to drive the start-up, Q0 through Q3 provide the timing. Heavy lines in Figure 47 show the default timing, which is compatible with XC2000 and XC3000 devices using early DONE and late Reset. The thin lines indicate all other possible timing options.

Figure 48: Start-up Logic

### Readback

The user can read back the content of configuration memory and the level of certain internal nodes without interfering with the normal operation of the device.

Readback not only reports the downloaded configuration bits, but can also include the present state of the device, represented by the content of all flip-flops and latches in CLBs and IOBs, as well as the content of function generators used as RAMs.

Note that in XC4000 Series devices, configuration data is *not* inverted with respect to configuration as it is in XC2000 and XC3000 families.

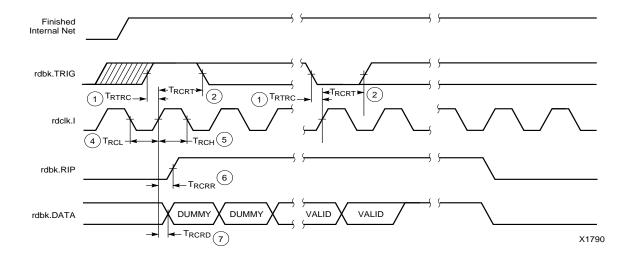

XC4000 Series Readback does not use any dedicated pins, but uses four internal nets (RDBK.TRIG, RDBK.DATA, RDBK.RIP and RDBK.CLK) that can be routed to any IOB. To access the internal Readback signals, place the READ-

BACK library symbol and attach the appropriate pad symbols, as shown in Figure 49.

After Readback has been initiated by a High level on RDBK.TRIG after configuration, the RDBK.RIP (Read In Progress) output goes High on the next rising edge of RDBK.CLK. Subsequent rising edges of this clock shift out Readback data on the RDBK.DATA net.

Readback data does not include the preamble, but starts with five dummy bits (all High) followed by the Start bit (Low) of the first frame. The first two data bits of the first frame are always High.

Each frame ends with four error check bits. They are read back as High. The last seven bits of the last frame are also read back as High. An additional Start bit (Low) and an 11-bit Cyclic Redundancy Check (CRC) signature follow, before RDBK.RIP returns Low.

# XC4000E/EX/XL Program Readback Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are not measured directly. They are derived from benchmark timing patterns that are taken at device introduction, prior to any process improvements.

The following guidelines reflect worst-case values over the recommended operating conditions.

### E/EX

|           | Description                                    | 5 | Symbol            | Min | Max | Units |

|-----------|------------------------------------------------|---|-------------------|-----|-----|-------|

| rdbk.TRIG | rdbk.TRIG setup to initiate and abort Readback | 1 | T <sub>RTRC</sub> | 200 | -   | ns    |

|           | rdbk.TRIG hold to initiate and abort Readback  | 2 | T <sub>RCRT</sub> | 50  | -   | ns    |

| rdclk.1   | rdbk.DATA delay                                | 7 | T <sub>RCRD</sub> | -   | 250 | ns    |

|           | rdbk.RIP delay                                 | 6 | T <sub>RCRR</sub> | -   | 250 | ns    |

|           | High time                                      | 5 | T <sub>RCH</sub>  | 250 | 500 | ns    |

|           | Low time                                       | 4 | T <sub>RCL</sub>  | 250 | 500 | ns    |

Note 1: Timing parameters apply to all speed grades.

Note 2: If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

### XL

|           | Description                                    |   | Symbol            | Min | Max | Units |

|-----------|------------------------------------------------|---|-------------------|-----|-----|-------|

| rdbk.TRIG | rdbk.TRIG setup to initiate and abort Readback | 1 | T <sub>RTRC</sub> | 200 | -   | ns    |

|           | rdbk.TRIG hold to initiate and abort Readback  | 2 | T <sub>RCRT</sub> | 50  | -   | ns    |

| rdclk.1   | rdbk.DATA delay                                | 7 | T <sub>RCRD</sub> | -   | 250 | ns    |

|           | rdbk.RIP delay                                 | 6 | T <sub>RCRR</sub> | -   | 250 | ns    |

|           | High time                                      | 5 | T <sub>RCH</sub>  | 250 | 500 | ns    |

|           | Low time                                       | 4 | T <sub>RCL</sub>  | 250 | 500 | ns    |

Note 1: Timing parameters apply to all speed grades.

Note 2: If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

**Table 23: Pin Functions During Configuration**

| SLAVE<br>SERIAL<br><1:1:1> | MASTER<br>SERIAL<br><0:0:0> | SERIAL PERIPHERAL <0:0:> <0:1:1> |              | MASTER<br>PARALLEL DOWN<br><1:1:0> | MASTER<br>PARALLEL UP<br><1:0:0> | USER<br>OPERATION |  |

|----------------------------|-----------------------------|----------------------------------|--------------|------------------------------------|----------------------------------|-------------------|--|

| M2(HIGH) (I)               | M2(LOW) (I)                 | M2(LOW) (I)                      | M2(HIGH) (I) | M2(HIGH) (I)                       | M2(HIGH) (I)                     | (I)               |  |

| M1(HIGH) (I)               | M1(LOW) (I)                 | M1(HIGH) (I)                     | M1(LOW) (I)  | M1(HIGH) (I)                       | M1(LOW) (I)                      | (O)               |  |

| M0(HIGH) (I)               | M0(LOW) (I)                 | M0(HIGH) (I)                     | M0(HIGH) (I) | M0(LOW) (I)                        | M0(LOW) (I)                      | (I)               |  |

| HDC (HIGH)                 | HDC (HIGH)                  | HDC (HIGH)                       | HDC (HIGH)   | HDC (HIGH)                         | HDC (HIGH)                       | I/O               |  |

| LDC (LOW)                  | LDC (LOW)                   | LDC (LOW)                        | LDC (LOW)    | LDC (LOW)                          | LDC (LOW)                        | I/O               |  |

| ĪNIT                       | ĪNIT                        | ĪNĪT                             | ĪNIT         | ĪNIT                               | ĪNIT                             | I/O               |  |

| DONE                       | DONE                        | DONE                             | DONE         | DONE                               | DONE                             | DONE              |  |

| PROGRAM (I)                | PROGRAM (I)                 | PROGRAM (I)                      | PROGRAM (I)  | PROGRAM (I)                        | PROGRAM (I)                      | PROGRAM           |  |

| CCLK (I)                   | ( )                         |                                  | CCLK (O)     | CCLK (O)                           | CCLK (O)                         | CCLK (I)          |  |

|                            |                             | RDY/BUSY (O)                     | RDY/BUSY (O) | RCLK (O)                           | RCLK (O)                         | I/O               |  |

|                            |                             |                                  | RS (I)       |                                    |                                  | I/O               |  |

|                            |                             |                                  | CSO (I)      |                                    |                                  | I/O               |  |

|                            |                             | DATA 7 (I)                       | DATA 7 (I)   | DATA 7 (I)                         | DATA 7 (I)                       | I/O               |  |

|                            |                             | DATA 6 (I)                       | DATA 6 (I)   | DATA 6 (I)                         | DATA 6 (I)                       | I/O               |  |