Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | Fixed Point                                                           |

| Interface               | CAN, SPI, SSP, TWI, UART                                              |

| Clock Rate              | 400MHz                                                                |

| Non-Volatile Memory     | External                                                              |

| On-Chip RAM             | 148kB                                                                 |

| Voltage - I/O           | 2.50V, 3.30V                                                          |

| Voltage - Core          | 1.20V                                                                 |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                     |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 316-LFBGA, CSPBGA                                                     |

| Supplier Device Package | 316-CSPBGA (17x17)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf538bbcz-4a |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **GENERAL DESCRIPTION**

The ADSP-BF538/ADSP-BF538F processors are members of the Blackfin<sup>fi</sup> family of products, incorporating the Analog Devices, Inc./Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction set architecture.

The ADSP-BF538/ADSP-BF538F processors are completely code compatible with other Blackfin processors, differing only with respect to performance, peripherals, and on-chip memory. Specific performance, peripherals, and memory configurations are shown in Table 1.

#### Ta le 1. Processor Features

| Feature                           | ADSP-BF538            | ADSP-BF538F8          |

|-----------------------------------|-----------------------|-----------------------|

| SPORTs                            | 4                     | 4                     |

| UARTs                             | 3                     | 3                     |

| SPI                               | 3                     | 3                     |

| TWI                               | 2                     | 2                     |

| CAN                               | 1                     | 1                     |

| PPI                               | 1                     | 1                     |

| Internal 8M bit<br>Parallel Flash | _                     | 1                     |

| Instruction<br>SRAM/Cache         | 16K bytes             | 16K bytes             |

| Instruction SRAM                  | 64K bytes             | 64K bytes             |

| Data SRAM/Cache                   | 32K bytes             | 32K bytes             |

| Data SRAM                         | 32K bytes             | 32K bytes             |

| Scratchpad                        | 4K bytes              | 4K bytes              |

| Maximum<br>Frequency              | 533 MHz<br>1066 MMACS | 533 MHz<br>1066 MMACS |

| Package Option                    | BC-316                | BC-316                |

By integrating a rich set of industry-leading system peripherals and memory, Blackfin processors are the platform of choice for next generation applications that require RISC-like programmability, multimedia support, and leading edge signal processing in one integrated package.

#### LOW POWER ARCHITECTURE

Blackfin processors provide world class power management and performance. They are designed using a low power and low voltage methodology and feature dynamic power management, which is the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. Varying the voltage and frequency can result in a substantial reduction in power consumption, compared with just varying the frequency of operation. This translates into longer battery life and lower heat dissipation.

#### SYSTEM INTEGRATION

The ADSP-BF538/ADSP-BF538F processors are highly integrated system-on-a-chip solutions for the next generation of consumer and industrial applications including audio and video signal processing. By combining advanced memory configurations, such as on-chip flash memory, industry-standard interfaces, and a high performance signal processing core, costeffective solutions can be quickly developed, without the need for costly external components. The system peripherals include three UART ports, three SPI ports, four serial ports (SPORTs), one CAN interface, two 2-wire interfaces (TWI), four generalpurpose timers (three with PWM capability), a real-time clock, a watchdog timer, a parallel peripheral interface (PPI), and general-purpose I/O pins.

#### ADSP-BF538/ADSP-BF538F PROCESSOR PERIPHERALS

The ADSP-BF538/ADSP-BF538F processors contain a rich set of peripherals connected to the core via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the block diagram 1). The general-purpose peripherals include functions such as UART, timers with PWM (pulse-width modulation) and pulse measurement capability, general-purpose I/O pins, a real-time clock, and a watchdog timer. This set of functions satisfies a wide variety of typical system support needs and is augmented by the system expansion capabilities of the device. In addition to these general-purpose peripherals, the processors contain high speed serial and parallel ports for interfacing to a variety of audio, video, and modem codec functions. A CAN 2.0B controller is provided for automotive and industrial control networks. An interrupt controller manages interrupts from the on-chip peripherals or from external sources. Power management control functions tailor the performance and power characteristics of the processors and system to many application scenarios.

All of the peripherals, except for general-purpose I/O, CAN, TWI, real-time clock, and timers, are supported by a flexible DMA structure. There are also four separate memory DMA channels dedicated to data transfers between the processor's various memory spaces, including external SDRAM and asynchronous memory. Multiple on-chip buses running at up to 133 MHz provide enough bandwidth to keep the processor core running with activity on all of the on-chip and external peripherals.

The ADSP-BF538/ADSP-BF538F processors include an on-chip voltage regulator in support of the processor's dynamic power management capability. The voltage regulator provides a range of core voltage levels from  $V_{DDEXT}$ . The voltage regulator can be bypassed as needed.

### **SPECIFICATIONS**

Note that component specifications are subject to change without notice.

#### **OPERATING CONDITIONS**

| Param                | eter                                    | Conditions                                                                                      | Min  | Nom  | Max   | Unit |

|----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|------|------|-------|------|

| V <sub>DDINT</sub>   | Internal Supply Voltage                 | 533 MHz Speed Grade Models <sup>1, 2</sup>                                                      | 0.8  | 1.25 | 1.375 | V    |

| V <sub>DDINT</sub>   | Internal Supply Voltage                 | 400 MHz Speed Grade Models <sup>1, 2</sup>                                                      | 0.8  | 1.2  | 1.32  | V    |

| V <sub>DDEXT</sub>   | External Supply Voltage                 | Models with on-chip flash <sup>2</sup>                                                          | 2.7  | 3.3  | 3.6   | V    |

| V <sub>DDEXT</sub>   | External Supply Voltage                 | Models without on-chip flash <sup>2, 3</sup>                                                    | 2.25 | 3.0  | 3.6   | V    |

| V <sub>DDRTC</sub>   | Real-Time Clock Power Supply<br>Voltage |                                                                                                 | 2.25 |      | 3.6   | V    |

| V <sub>IH</sub>      | High Level Input Voltage ${}^4$         | V <sub>DDEXT</sub> = Maximum                                                                    | 2.0  |      |       | V    |

| V <sub>IH5V</sub>    | High Level Input Voltage ${}^5$         | V <sub>DDEXT</sub> = Maximum                                                                    | 2.0  |      |       | V    |

| V <sub>IHCLKIN</sub> | High Level Input Voltage 6              | V <sub>DDEXT</sub> = Maximum                                                                    | 2.2  |      |       | V    |

| $V_{IL}$             | Low Level Input Voltage <sup>4,7</sup>  | V <sub>DDEXT</sub> = Minimum                                                                    |      |      | +0.6  | V    |

| $V_{IL5V}$           | Low Level Input Voltage 5               | V <sub>DDEXT</sub> = Minimum                                                                    |      |      | +0.8  | V    |

| TJ                   | Junction Temperature                    | \$16-Ball Chip Scale Package Ball Grid Array (CSP_BGA)<br>@ T <sub>AMBIENT</sub> =40°C to +85°C | 40   |      | +110  | °C   |

$^{1}$  The regulator can generate  $V_{DDINT}$  at levels of 0.85 V to 1.2 V with -5% to +10% tolerance and 1.25 V with -4% to +10% tolerance

<sup>2</sup> See Ordering Guide on Page 58.

$^3$  When V\_{\rm DDEXT} < 2.70 V, on-chip voltage regulation is not supported.

<sup>4</sup> The 3.3 V tolerant <u>pins are capable of accepting up to 3.6 V maximum V<sub>IH</sub> The following bidirectional pins are 3.3 V tolerant: DATA15-0, SCK2-0, MISO2-0, MOSI2-0, PF15-0, PF13-0, SF1ISS, SF1ISELI, PC9-5, SF12SS, SF12SELI, RX2-1, TX2-1, TSCLK3-0, RSCLK3-0, RFS3-0, DT2PRI, DT2SEC, DR2PRI, DR2SEC, DT3PRI, DT3SEC, DR3PRI, DR3SEC, and TMR2-0. The following input-only pins are 3.3 V tolerant: RESET, RX0, TCK, TDI, TMS, TRST, ARDY, BMODE1-0, BR, DR0PRI, DR0SEC, DR1PRI, DR1SEC, NMI, PPI\_CLK, and RTXI.</u>

<sup>5</sup> The 5 V tolerant pins are capable of accepting up to 5.5 V maximum V<sub>IH</sub>. The following bidirectional pins are 5 V tolerant: SCL0, SCL1, SDA0, SDA1, CANTX, CANRX, and PC4. The following input-only pin is 5 V tolerant: GPW.

<sup>6</sup> Parameter value applies to the CLKIN input pin.

<sup>7</sup> Parameter value applies to all input and bidirectional pins.

The following tables describe the voltage/frequency requirements for the ADSP-BF538/ADSP-BF538F processor clocks. Take care in selecting MSEL, SSEL, and CSEL ratios so as not to exceed the maximum core clock (Table 11 and Table 12) and system clock (Table 14) specifications. Table 13 describes phase-locked loop operating conditions.

#### Ta le 11. Core Clock (CCLK) Re uirements — 400 MHz Models

|                   |                                                      | Internal Regulator |     |      |

|-------------------|------------------------------------------------------|--------------------|-----|------|

| Param             | neter                                                | Setting            | Max | Unit |

| f <sub>CCLK</sub> | CLK Frequency (V <sub>DDINT</sub> = 1.14 V Minimum)  | 1.20 V             | 400 | MHz  |

| f <sub>CCLK</sub> | CLK Frequency (V <sub>DDINT</sub> = 1.045 V Minimum) | 1.10 V             | 364 | MHz  |

| f <sub>CCLK</sub> | CLK Frequency (V <sub>DDINT</sub> = 0.95 V Minimum)  | 1.00 V             | 333 | MHz  |

| f <sub>CCLK</sub> | CLK Frequency (V <sub>DDINT</sub> = 0.85 V Minimum)  | 0.90 V             | 280 | MHz  |

| f <sub>CCLK</sub> | CLK Frequency (V <sub>DDINT</sub> = 0.8 V Minimum)   | 0.85 V             | 250 | MHz  |

#### Ta le 12. Core Clock (CCLK) Re uirements — 533 MHz Models

| Param             | neter                                                       | Internal Regulato | r Setting Max | Unit |

|-------------------|-------------------------------------------------------------|-------------------|---------------|------|

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 1.2 V Minimum)   | 1.25 V            | 533           | MHz  |

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 1.14 V Minimum)  | 1.20 V            | 500           | MHz  |

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 1.045 V Minimum) | 1.10 V            | 444           | MHz  |

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 0.95 V Minimum)  | 1.00 V            | 400           | MHz  |

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 0.85 V Minimum)  | 0.95 V            | 333           | MHz  |

| f <sub>CCLK</sub> | Core Clock Frequency (V <sub>DDINT</sub> = 0.8 V Minimum)   | 0.85 V            | 250           | MHz  |

#### Ta le 13. P ase-Locked Locopperating Conditions

| Parame           |                                               | Min | Max                  | Unit |

|------------------|-----------------------------------------------|-----|----------------------|------|

| f <sub>VCO</sub> | Voltage Controlled Oscillator (VCO) Frequency | 50  | Maxf <sub>CCLK</sub> | MHz  |

#### Ta le 14. System Clock (SCLK) Re uirements

| Param             | neter <sup>1</sup>                                 | Max              | Unit |

|-------------------|----------------------------------------------------|------------------|------|

| f <sub>SCLK</sub> | CLKOUT/SCLK Frequency (V <sub>DDINT</sub> t1.14 V) | 133 <sup>2</sup> | MHz  |

| f <sub>SCLK</sub> | CLKOUT/SCLK Frequency (V <sub>DDINT</sub> 1.14 V)  | 100              | MHz  |

$^{1}$ t<sub>SCLK</sub> (= 1/f<sub>SCLK</sub>) must be greater than or equal to t<sub>CCLK</sub>.

<sup>2</sup> Guaranteed to  $t_{SCLK}$  = 7.5 ns. See Table 27 on page 33.

#### **ELECTRICAL CHARACTERISTICS**

| Parameter <sup>1</sup>                |                                                 | Test Conditions                                                                        | Min | Тур | Max                                           | Unit |

|---------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----------------------------------------------|------|

| V <sub>OH</sub>                       | High Level Output Voltage <sup>2</sup>          | $V_{DDEXT} = +3.0 V, I_{OH} =0.5 mA$                                                   | 2.4 |     |                                               | V    |

| V <sub>OL</sub>                       | Low Level Output Voltage <sup>2</sup>           | $V_{DDEXT} = 3.0 V, I_{OL} = 2.0 mA$                                                   |     |     | 0.4                                           | V    |

| I <sub>IH</sub>                       | High Level Input Current <sup>3</sup>           | $V_{DDEXT} = Maximum, V_{IN} = V_{DD} Maximum$                                         |     |     | 10.0                                          | μΑ   |

| I <sub>IHP</sub>                      | High Level Input Current JTAG $^4$              | $V_{DDEXT} = Maximum, V_{IN} = V_{DD} Maximum$                                         |     |     | 50.0                                          | μA   |

| I <sub>IL</sub>                       | Low Level Input Current <sup>3</sup>            | $V_{DDEXT} = Maximum, V_{IN} = 0 V$                                                    |     |     | 10.0                                          | μA   |

| I <sub>OZH</sub>                      | Three-State Leakage Current ${}^5$              | $V_{DDEXT} = Maximum, V_{IN} = V_{DD} Maximum$                                         |     |     | 10.0                                          | μA   |

| I <sub>OZL</sub>                      | Three-State Leakage Current ${}^5$              | $V_{DDEXT} = Maximum, V_{IN} = 0 V$                                                    |     |     | 10.0                                          | μA   |

| C <sub>IN</sub>                       | Input Capacitance <sup>6,7</sup>                | $f_{CCLK} = 1 MHz, T_{AMBIENT} = 25 °C, V_N = 2.5 V$                                   |     | 4   | 8                                             | рF   |

| I <sub>DDDEEPSLEEP</sub> <sup>8</sup> | V <sub>DDINT</sub> Current in Deep Sleep Mode V | $D_{DDINT} = 1.0 V, f_{CCLK} = 0 MHz, T_J = 25 °C, ASF = 0.00$                         |     | 7.5 |                                               | mА   |

| <b>I</b> <sub>DDSLEEP</sub>           | V <sub>DDINT</sub> Current in Sleep Mode        | $D_{DINT} = 0.8 V, T_J = 25 °C, SCLK = 25 MHz$                                         |     |     | 10                                            | тA   |

| I <sub>DD-TYP</sub>                   | V <sub>DDINT</sub> Current                      | $V_{DDINT} = 1.14 V, f_{CCLK} = 400 MHz, T_J = 25 °C$                                  |     | 130 |                                               | тA   |

| I <sub>DD-TYP</sub>                   | V <sub>DDINT</sub> Current                      | $V_{DDINT} = 1.2 V, f_{CCLK} = 500 MHz, T_J = 25 °C$                                   |     | 168 |                                               | тA   |

| I <sub>DD-TYP</sub>                   | V <sub>DDINT</sub> Current                      | $V_{DDINT} = 1.2 V, f_{CCLK} = 533 MHz, T_J = 25 °C$                                   |     | 180 |                                               | тA   |

| I <sub>DDHIBERNATE</sub> <sup>8</sup> | V <sub>DDEXT</sub> Current in Hibernate State   | $V_{DDEXT} = 3.6 V, CLKIN = 0 MHz, T_J = Max, voltage regulator off (V_{DDINT} = 0 V)$ |     | 50  | 100                                           | P4   |

| I <sub>DDRTC</sub>                    | V <sub>DDRTC</sub> Current                      | $V_{DDRTC} = 3.3 V, T_J = 25 $ c $f$                                                   |     | 20  |                                               | PA   |

| I <sub>DDDEEPSLEEP</sub> <sup>8</sup> | V <sub>DDINT</sub> Current in Deep Sleep Mode f | $_{CCLK} = 0 MHz$                                                                      |     | 6   | Table 15                                      | тA   |

| I <sub>DDINT</sub> 9                  | V <sub>DDINT</sub> Current                      | f <sub>CCLK</sub> > 0 MHz                                                              |     |     | I <sub>DDDEEPSLEEP</sub> +<br>(Table 17 uASF) | тA   |

<sup>1</sup>Specifications subject to change without notice.

<sup>2</sup> Applies to output and bidirectional pins.

<sup>3</sup> Applies to input pins except JTAG inputs.

$^4$  Applies to JTAG input pins (TCK, TDI, TMS,  $\overline{\text{TRST}}$ ).

<sup>5</sup> Applies to three-statable pins.

<sup>6</sup> Applies to all signal pins.

<sup>7</sup> Guaranteed, but not tested.

<sup>8</sup> See the ADSP-BF538/538F Blackfin Processor Hardware Refiewed to the steep, deep sleep, and hibernate operating modes.

<sup>9</sup> See Table 16 for the list of I<sub>DDINT</sub> power vectors covered by various Activity Scaling Factors (ASF).

System designers should refer to Estimating Power for the ADSP-BF538/BF539 Blackfin Processors (EEv298) provides detailed information for optimizing designs for lowest power. All topics discussed in this section are described in detail in EE-298. Total power dissipation has two components:

1. Static, including leakage current

2. Dynamic, due to transistor switching characteristics

Many operating conditions can also affect power dissipation, including temperature, voltage, operating frequency, and processor activity. Electrical Characteristics on Page 25 shows the current dissipation for internal circuitry ( $V_{DDINT}$ ). I<sub>DDDEEPSLEEP</sub> specifies static power dissipation as a function of voltage ( $V_{DDINT}$ ) and temperature (see Table 15), and I<sub>DDINT</sub> specifies the total power specification for the listed test conditions, including the dynamic component as a function of voltage ( $V_{DDINT}$ ) and frequency (Table 17).

The dynamic component is also subject to an Activity Scaling Factor (ASF) which represents application code running on the processor (Table 16).

#### Ta le 15. Static Current (mÅ)

|                     | V <sub>DDINT</sub> (\ | V <sub>DDINT</sub> (V) |        |        |        |        |        |        |        |        |        |        |         |  |  |

|---------------------|-----------------------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--|--|

| Т <sub>Ј</sub> (°С) | 0.80 V                | 0.85 V                 | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.32 V | 1.375 V |  |  |

| 40                  | 6.4                   | 7.7                    | 8.8    | 10.4   | 12.0   | 14.0   | 16.1   | 18.9   | 21.9   | 25.2   | 28.7   | 30.6   | 35.9    |  |  |

| 25                  | 9.2                   | 10.9                   | 12.5   | 14.5   | 16.7   | 19.3   | 22.1   | 25.6   | 29.5   | 33.7   | 38.1   | 40.5   | 47.2    |  |  |

| 0                   | 16.8                  | 18.9                   | 21.5   | 24.4   | 27.7   | 31.7   | 35.8   | 40.5   | 45.8   | 51.6   | 58.2   | 61.0   | 69.8    |  |  |

| 25                  | 32.9                  | 37.2                   | 41.4   | 46.2   | 51.8   | 57.4   | 64.2   | 72.3   | 80.0   | 89.3   | 98.9   | 103.3  | 116.4   |  |  |

| 40                  | 48.4                  | 54.8                   | 60.5   | 67.1   | 74.7   | 82.9   | 91.6   | 101.5  | 112.4  | 123.2  | 136.2  | 142.0  | 158.7   |  |  |

| 55                  | 71.2                  | 78.6                   | 86.5   | 95.8   | 104.9  | 115.7  | 127.1  | 139.8  | 153.6  | 168.0  | 183.7  | 191.0  | 211.8   |  |  |

| 70                  | 102.3                 | 112.2                  | 122.1  | 133.5  | 146.1  | 159.2  | 173.9  | 189.8  | 206.7  | 225.5  | 245.6  | 254.1  | 279.6   |  |  |

| 85                  | 140.7                 | 153.0                  | 167.0  | 182.5  | 198.0  | 216.0  | 234.3  | 254.0  | 276.0  | 299.1  | 324.3  | 334.8  | 366.6   |  |  |

| 100                 | 190.6                 | 207.1                  | 224.6  | 244.0  | 265.6  | 285.7  | 309.0  | 333.7  | 360.0  | 387.8  | 417.3  | 431.1  | 469.3   |  |  |

| 105                 | 210.2                 | 228.1                  | 245.1  | 265.6  | 285.8  | 309.2  | 334.0  | 360.1  | 385.6  | 417.2  | 448.0  | 461.5  | 501.1   |  |  |

$^1\,\textsc{Values}$  are guaranteed maximum  $I_{\textsc{DDDEEPSLEEP}}$  specifications.

#### Ta le 16. Activity Scaling Factors

| IDDINT Power Vector <sup>1</sup> | Activity Scaling Factor (ASF) <sup>2</sup> |

|----------------------------------|--------------------------------------------|

| I <sub>DD-PEAK</sub>             | 1.30                                       |

| I <sub>DD-HIGH</sub>             | 1.28                                       |

| I <sub>DD-TYP</sub>              | 1.00                                       |

| I <sub>DD-APP</sub>              | 0.88                                       |

| I <sub>DD-NOP</sub>              | 0.74                                       |

| I <sub>DD-IDLE</sub>             | 0.48                                       |

<sup>1</sup> See EE-298 for power vector definitions.

<sup>2</sup> All ASF values determined using a 10:1 CCLK:SCLK ratio.

#### Ta le 17. Dynamic Current (mA, wit $ASF = 1^{1.0}$ )

| Frequency | Voltage (V <sub>DDINT</sub> ) |        |        |        |        |        |        |        |        |        |        |        |         |

|-----------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|

| (MHz)     | 0.80 V                        | 0.85 V | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.32 V | 1.375 V |

| 50        | 13.6                          | 14.9   | 16.4   | 17.5   | 19.1   | 20.5   | 22.0   | 23.5   | 25.4   | 27.1   | 29.1   | 29.7   | 31.6    |

| 100       | 23.6                          | 26.0   | 27.9   | 30.1   | 32.3   | 34.4   | 37.0   | 39.2   | 41.7   | 44.3   | 46.4   | 47.6   | 50.3    |

| 200       | 44.1                          | 47.5   | 51.0   | 54.8   | 58.4   | 61.8   | 65.6   | 69.7   | 74.3   | 76.2   | 82.2   | 83.4   | 87.8    |

| 250       | 54.6                          | 58.7   | 62.8   | 66.8   | 71.2   | 75.7   | 79.9   | 84.5   | 89.8   | 94.2   | 99.4   | 101.2  | 106.5   |

| 300       | N/A                           | 69.8   | 74.1   | 79.3   | 84.5   | 89.0   | 94.7   | 100.0  | 105.5  | 111.6  | 116.8  | 119.3  | 125.5   |

| 375       | N/A                           | N/A    | 91.9   | 97.9   | 103.9  | 109.9  | 116.5  | 122.2  | 129.7  | 136.0  | 142.9  | 145.9  | 153.6   |

| 400       | N/A                           | N/A    | N/A    | 103.8  | 110.3  | 116.9  | 123.7  | 130.0  | 137.5  | 144.2  | 151.2  | 154.5  | 162.4   |

| 425       | N/A                           | N/A    | N/A    | N/A    | 116.6  | 123.7  | 130.9  | 137.2  | 144.7  | 152.7  | 159.9  | 163.3  | 171.8   |

| 475       | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | 145.0  | 151.8  | 161.4  | 169.4  | 177.8  | 181.1  | 190.4   |

| 500       | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | 159.9  | 168.9  | 177.8  | 186.3  | 190.0  | 199.6   |

| 533       | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | 179.8  | 188.9  | 198.8  | 202.2  | 212.5   |

<sup>1</sup>The values are not guaranteed as standalone maximum specifications, they must be combined with static current per the equations of Electrical Characteristics on Page 25.

#### TIMING SPECIFICATIONS

Component specifications are subject to change with PCN notice.

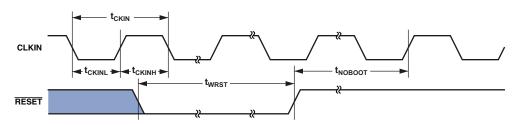

Clock and Reset Timing

Table 21 and Figure 10 describe clock and reset operations. Per Absolute Maximum Ratings on Page 27, combinations of CLKIN and clock multipliers must not select core/peripheral clocks that exceed maximum operating conditions.

#### Ta le 21. Clock and Reset Timing

| Parameter           |                                                                    | Min                    | Max                 | Unit |

|---------------------|--------------------------------------------------------------------|------------------------|---------------------|------|

| Timing Req          | uirement                                                           |                        |                     |      |

| f <sub>CKIN</sub>   | CLKIN Frequency (Commercial/Industrial Models) <sup>1, 2,3,4</sup> | 10                     | 50                  | MHz  |

| t <sub>CKINL</sub>  | CLKIN Low Pulse <sup>1</sup>                                       | 8                      |                     | ns   |

| t <sub>CKINH</sub>  | CLKIN High Pulse <sup>1</sup>                                      | 8                      |                     | ns   |

| t <sub>WRST</sub>   | RESET Asserted Pulse Width Low <sup>5</sup>                        | 11 × t <sub>СКIN</sub> |                     | ns   |

| t <sub>NOBOOT</sub> | RESET Deassertion to First External Access Delay <sup>6</sup>      | $3 \times t_{CKIN}$    | $5 \times t_{CKIN}$ | ns   |

<sup>1</sup> Applies to PLL bypass mode and PLL nonbypass mode.

<sup>2</sup> Combinations of the CLKIN frequency and the PLL clock multiplier must not exceed the allowed f<sub>VCO</sub>, f<sub>CCLK</sub>, and f<sub>SCLK</sub> settings discussed in Table 11 on Page 24 through Table 16 on Page 26.

$^3$  The  $t_{CKIN}$  period (see Figure 10) equals  $1/f_{CKIN}.$

$^{4}$  If the DF bit in the PLL\_CTL register is set, the minimum f<sub>CKIN</sub> specification is 24 MHz for commercial/industrial models.

<sup>5</sup> Applies after power-up sequence is complete. See Table 22 and Figure 11 for power-up reset timing.

<sup>6</sup> Applies when processor is configured in No Boot Mode (BMODE2-0 = b#000).

Figure 10. Clock and Reset Timing

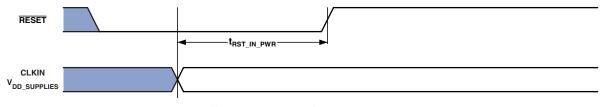

#### Ta le 22. Power-Up Reset Timing

| Parameter                             |                                                                                                                                                              | Min                      | Max | Unit |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|

| Timing Red<br>t <sub>RST_IN_PWR</sub> | quirement<br>RESET Deasserted after the V <sub>DDINT</sub> , V <sub>DDEXT</sub> , V <sub>DDRTC</sub> , and CLKIN Pins are Stable and Within<br>Specification | 3500 × t <sub>скіл</sub> |     | ns   |

In Figure 11, Vod\_supplies is V DDINT, Vodext, Vodext, Vodext,

Figure 11. Powed PReset Timing

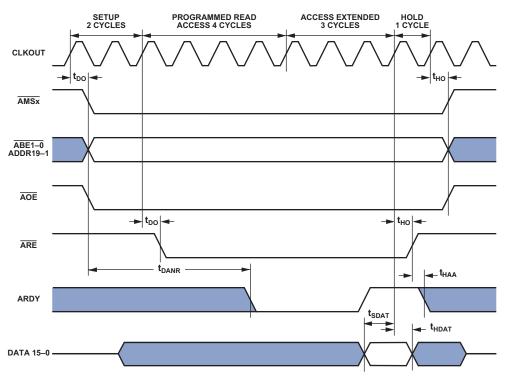

#### Ta le 24. Async ronous Memory Readcory Timing wit Async ronous ARDY

| Paramete          | r                                                  | Min | Max                           | Unit |

|-------------------|----------------------------------------------------|-----|-------------------------------|------|

| Timing R          | equirements                                        |     |                               |      |

| t <sub>SDAT</sub> | DATA150 Setup Before CLKOUT                        | 2.1 |                               | ns   |

| t <sub>HDAT</sub> | DATA150 Hold After CLKOUT                          | 0.8 |                               | ns   |

| t <sub>DANR</sub> | ARDY Negated Delay from AMSx Asserted <sup>1</sup> |     | (S + RA 2) ut <sub>SCLK</sub> | ns   |

| t <sub>HAA</sub>  | ARDY Asserted Hold After ARE Negated               | 0.0 |                               | ns   |

| Switching         | Characteristics                                    |     |                               |      |

| t <sub>DO</sub>   | Output Delay After CLKOUT <sup>2</sup>             |     | 6.0                           | ns   |

| t <sub>HO</sub>   | Output Hold After CLKOUT <sup>2</sup>              | 0.8 |                               | ns   |

$^{1}$ S = number of programmed setup cycles, RA = number of programmed read access cycles.

<sup>2</sup> Output pins include  $\overline{AMS3-0}$ ,  $\overline{ABE1-0}$ , ADDR19-1,  $\overline{AOE}$ ,  $\overline{ARE}$ .

Figure 13. Asynchronous Memory Regarde Timing with Asynchronous ARDY

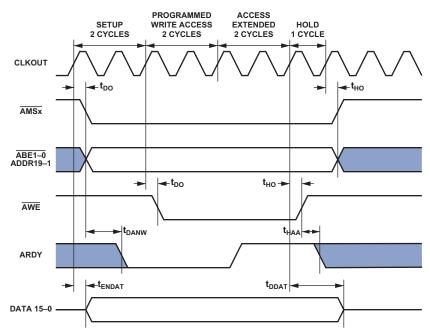

#### Ta le 26. Async ronous Memory Write Cly Timing wit Async ronous ARDY

| Parameter          | ſ                                                  | Min | Max                               | Unit |

|--------------------|----------------------------------------------------|-----|-----------------------------------|------|

| Timing Re          | quirements                                         |     |                                   |      |

| t <sub>DANW</sub>  | ARDY Negated Delay from AMSx Asserted <sup>1</sup> |     | $(S + WA \dots 2) \times t_{SCL}$ | , ns |

| t <sub>HAA</sub>   | ARDY Asserted Hold After ARE Negated               | 0.0 |                                   | ns   |

| Switching          | Characteristics                                    |     |                                   |      |

| t <sub>DDAT</sub>  | DATA150 Disable After CLKOUT                       |     | 6.0                               | ns   |

| t <sub>ENDAT</sub> | DATA150 Enable After CLKOUT                        | 1.0 |                                   | ns   |

| t <sub>DO</sub>    | Output Delay After CLKOUT <sup>2</sup>             |     | 6.0                               | ns   |

| t <sub>HO</sub>    | Output Hold After CLKOUT <sup>2</sup>              | 0.8 |                                   | ns   |

<sup>1</sup>S = number of programmed setup cycles, WA = number of programmed write access cycles. <sup>2</sup>Output pipe in clude  $\overline{AMS_{-0}}$   $\overline{APE_{-0}}$  ADDP10 1 DATA15 0  $\overline{AOE}$   $\overline{AWE}$

<sup>2</sup> Output pins include AMS3-0, ABE1-0, ADDR19-1, DATA15-0, AOE, AWE.

Figure 15. Asynchronous Memory Write Cycle Timing with Asynchronous ARDY

#### SDRAM Interface Timing

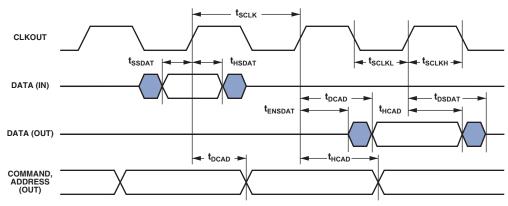

#### Ta le 27. SDRAM Interface Timing

| Parameter           |                                                     | Min | Мах | Unit |

|---------------------|-----------------------------------------------------|-----|-----|------|

| Timing F            | Requirement                                         |     |     |      |

| t <sub>SSDAT</sub>  | DATA Setup Before CLKOUT                            | 2.1 |     | ns   |

| t <sub>HSDAT</sub>  | DATA Hold After CLKOUT                              | 0.8 |     | ns   |

| Switchir            | g Characteristics                                   |     |     |      |

| t <sub>SCLK</sub>   | CLKOUT Period                                       | 7.5 |     | ns   |

| t <sub>SCLKH</sub>  | CLKOUT Width High                                   | 2.5 |     | ns   |

| t <sub>SCLKL</sub>  | CLKOUT Width Low                                    | 2.5 |     | ns   |

| t <sub>DCAD</sub>   | Command, ADDR, Data Delay After CLKOUT <sup>1</sup> |     | 6.0 | ns   |

| t <sub>HCAD</sub>   | Command, ADDR, Data Hold After CLKOUT <sup>1</sup>  | 0.8 |     | ns   |

| t <sub>DSDAT</sub>  | Data Disable After CLKOUT                           |     | 6.0 | ns   |

| t <sub>ENSDAT</sub> | Data Enable After CLKOUT                            | 1.0 |     | ns   |

<sup>1</sup>Command pins include: SRAS, SCAS, SWE, SDQM, SMS, SA10, SCKE.

NOTE: COMMAND = SRAS, SCAS, SWE, SDQM, SMS, SA10, SCKE.

Figure 16. SDRAM Interface Timing

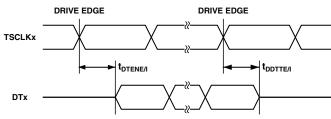

#### Table 33. Serial Ports—Enable and Three-State

| Parameter          |                                                            | Min | Max | Unit |

|--------------------|------------------------------------------------------------|-----|-----|------|

| Switching          | Characteristics                                            |     |     |      |

| t <sub>DTENE</sub> | Data Enable Delay from External TSCLKx <sup>1</sup>        | 0   |     | ns   |

| t <sub>DDTTE</sub> | Data Disable Delay from External TSCLKx <sup>1, 2, 3</sup> |     | 10  | ns   |

| t <sub>DTENI</sub> | Data Enable Delay from Internal TSCLKx <sup>1</sup>        | 2   |     | ns   |

| t <sub>DDTTI</sub> | Data Disable Delay from Internal TSCLKx <sup>1, 2, 3</sup> |     | 3   | ns   |

<sup>1</sup>Referenced to drive edge.

<sup>2</sup>Applicable to multichannel mode only. <sup>3</sup>TSCLKx is tied to RSCLKx.

Figure 25. Serial Ports, Enable and Three-State

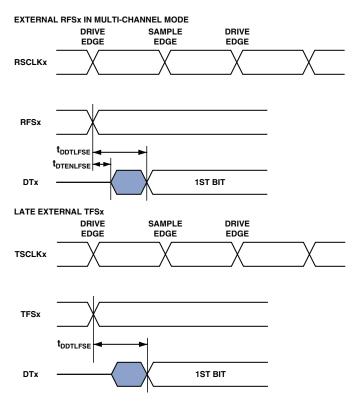

#### Ta le 34. External Late Frame Sync

| Parameter            |                                                                                             | Min | Max  | Unit |

|----------------------|---------------------------------------------------------------------------------------------|-----|------|------|

| Switching Ch         | naracteristics                                                                              |     |      |      |

| t <sub>DDTLFSE</sub> | Data Delay from Late External TFSx or External RFSx in multichannel mode, $MFD = 0^{-1, 2}$ |     | 10.0 | ns   |

| t <sub>DTENLFS</sub> | Data Enable from Late FS or multichannel mode, $MFD = 0^{-1, 2}$                            | 0   |      | ns   |

$^1$  In multichannel mode, TFSx enable and TFSx valid follow  $t_{\mbox{\scriptsize DTENLFS}}$  and  $t_{\mbox{\scriptsize DDTLFSE}}$

$^{2}$  If external RFSx/TFSx setup to RSCLKx/TSCLKx > t<sub>SCLKE</sub>/2, then t<sub>DDTTE/I</sub> and t<sub>DTENE/I</sub> apply; otherwise t<sub>DDTLFSE</sub> and t<sub>DTENLFS</sub> apply.

Figure 26. External Late Frame Sync

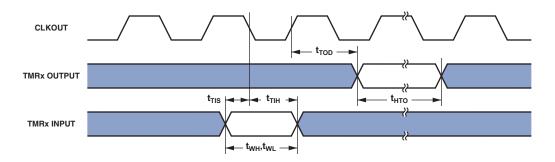

#### Timer Cycle Timing

Table 39 and Figure 31 describe timer expired operations. The input signal is asynchronous in "width capture mode" and "external clock mode" and has an absolute maximum input frequency of ( $f_{SCLK}/2$ ) MHz.

#### Table 39. Timer Cycle Timing

| Parameter        |                                                       | Min                  | Max                                     | Unit |

|------------------|-------------------------------------------------------|----------------------|-----------------------------------------|------|

| Timing Ch        | aracteristics                                         |                      |                                         |      |

| t <sub>WL</sub>  | Timer Pulse Width Input Low <sup>1</sup>              | 1× t <sub>SCLK</sub> |                                         | ns   |

| t <sub>WH</sub>  | Timer Pulse Width Input High <sup>1</sup>             | 1× t <sub>SCLK</sub> |                                         | ns   |

| t <sub>TIS</sub> | Timer Input Setup Time Before CLKOUT Low <sup>2</sup> | 6.5                  |                                         | ns   |

| t <sub>TIH</sub> | Timer Input Hold Time After CLKOUT Low <sup>2</sup>   | 1                    |                                         | ns   |

| Switching        | Characteristics                                       |                      |                                         |      |

| t <sub>HTO</sub> | Timer Pulse Width Output                              | 1×t <sub>sclk</sub>  | (2 <sup>32</sup> 1) × t <sub>SCLK</sub> | ns   |

| t <sub>TOD</sub> | Timer Output Delay After CLKOUT High                  |                      | 6                                       | ns   |

<sup>1</sup>The minimum pulse widths apply for TMRx signals in width capture and external clock modes.

<sup>2</sup>Either a valid setup and hold time or a valid pulse width is sufficient. There is no need to resynchronize timer flag inputs.

Figure 31. Timer Cycle Timing

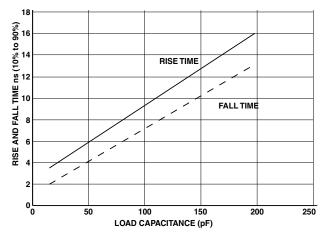

Figure 52. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver D at  $\frac{1}{MET} = 2.7 V$  (Min)

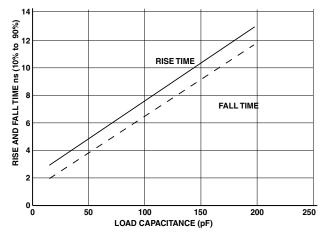

Figure 53. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver D at  $\frac{1}{MEXT}$  = 3.6 V (Max)

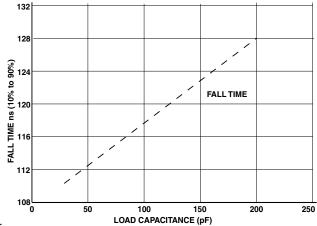

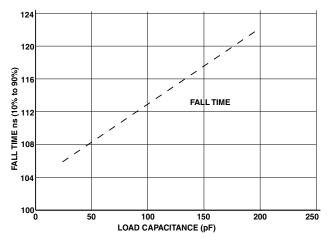

Figure 54. Typical Fall Time (10% to 90%) vs. Load Capacitance for Driver E at  $V_{\text{DDEXT}}{=}2.7$  V (Min)

Figure 55. Typical Fall Time (10% to 90%) vs. Load Capacitance for Driver E at V\_{DDEXT}= 3.6 V (Max)

#### THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board use

$$T_J = T_{CASE} + <_{JT} uP_D$$

where:

$T_J$  = junction temperature (°C)

$T_{CASE}$  = case temperature (°C) measured by customer at top center of package.

<\_JT = from Table 41 or Table 42</pre>

$P_D$  = power dissipation (see Electrical Characteristics on Page 25 for the method to calculate  $P_D$ )

Values of  $T_A$  are provided for package comparison and printed circuit board design considerations.  $T_A$  can be used for a first order approximation of  $T_I$  by the equation

$$T_J = T_A + T_{JA} uP_D$$

where:

$T_A$  = ambient temperature (°C)

Values of  $\mathcal{T}_C$  are provided for package comparison and printed circuit board design considerations when an external heatsink is required.

Values of  $T_{B}$  are provided for package comparison and printed circuit board design considerations.

In Table 41 and Table 42, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6, and the junction-toboard measurement complies with JESD51-8. The junction-tocase measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

Ta le 41. T ermal C aracteristics BC-316-2 wit out Flas

| Parameter        | Condition            | Typical | Unit |

|------------------|----------------------|---------|------|

| Ţ <sub>A</sub>   | 0 Linear m/s Airflow | 25.4    | °C/W |

| T <sub>IMA</sub> | 1 Linear m/s Airflow | 22.8    | °C/W |

| T <sub>IMA</sub> | 2 Linear m/s Airflow | 22.0    | °C/W |

| $T_{C}$          |                      | 6.7     | °C/W |

| < <sub>JT</sub>  | 0 Linear m/s Airflow | 0.18    | °C/W |

| < <sub>JT</sub>  | 1 Linear m/s Airflow | 0.38    | °C/W |

| < <sub>JT</sub>  | 2 Linear m/s Airflow | 0.40    | °C/W |

Ta le 42. T ermal C aracteristics BC-316-2 wit Flas

| Parameter              | Condition            | Typical | Unit |

|------------------------|----------------------|---------|------|

| Ţ <sub>A</sub>         | 0 Linear m/s Airflow | 24.3    | °C/W |

| <b>T</b> <sub>MA</sub> | 1 Linear m/s Airflow | 21.8    | °C/W |

| <b>T</b> <sub>MA</sub> | 2 Linear m/s Airflow | 21.0    | °C/W |

| $T_{C}$                |                      | 6.3     | °C/W |

| < <sub>JT</sub>        | 0 Linear m/s Airflow | 0.17    | °C/W |

| < <sub>JT</sub>        | 1 Linear m/s Airflow | 0.36    | °C/W |

| < <sub>JT</sub>        | 2 Linear m/s Airflow | 0.38    | °C/W |