Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 20                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                      |

| Data Converters            | A/D 20x12b; D/A 2x12b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f411-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

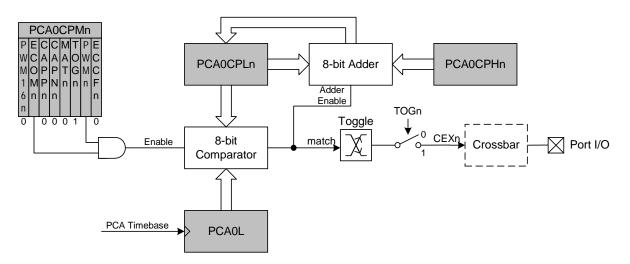

| 25.2.Capture/Compare Modules             | 251 |

|------------------------------------------|-----|

| 25.2.1.Edge-triggered Capture Mode       |     |

|                                          |     |

| 25.2.2.Software Timer (Compare) Mode     |     |

| 25.2.3.High Speed Output Mode            |     |

| 25.2.4.Frequency Output Mode             | 255 |

| 25.2.5.8-Bit Pulse Width Modulator Mode  | 256 |

| 25.2.6.16-Bit Pulse Width Modulator Mode | 257 |

| 25.3.Watchdog Timer Mode                 | 257 |

| 25.3.1.Watchdog Timer Operation          | 258 |

| 25.3.2.Watchdog Timer Usage              |     |

| 25.4.Register Descriptions for PCA       |     |

| 26.C2 Interface                          |     |

| 26.1.C2 Interface Registers              |     |

| 26.2.C2 Pin Sharing                      |     |

| 2012.02.                                 | 201 |

| Figure 9.3. Comparator Hysteresis Plot                           | 85  |

|------------------------------------------------------------------|-----|

| 10. CIP-51 Microcontroller                                       |     |

| Figure 10.1. CIP-51 Block Diagram                                | 93  |

| 11. Memory Organization and SFRs                                 |     |

| Figure 11.1. Memory Map                                          | 103 |

| 12. Interrupt Handler                                            |     |

| 13. Prefetch Engine                                              |     |

| 14. Cyclic Redundancy Check Unit (CRC0)                          |     |

| Figure 14.1. CRC0 Block Diagram                                  |     |

| Figure 14.2. Bit Reverse Register                                | 124 |

| 15. Reset Sources                                                |     |

| Figure 15.1. Reset Sources                                       |     |

| Figure 15.2. Power-On and VDD Monitor Reset Timing               | 128 |

| 16. Flash Memory                                                 |     |

| Figure 16.1. Flash Program Memory Map                            | 137 |

| 17. External RAM                                                 |     |

| 18. Port Input/Output                                            |     |

| Figure 18.1. Port I/O Functional Block Diagram                   | 147 |

| Figure 18.2. Port I/O Cell Block Diagram                         | 148 |

| Figure 18.3. Crossbar Priority Decoder with No Pins Skipped      |     |

| Figure 18.4. Crossbar Priority Decoder with Crystal Pins Skipped |     |

| Figure 18.5. Port 0 Input Overdrive Current Range                | 152 |

| 19. Oscillators                                                  |     |

| Figure 19.1. Oscillator Diagram                                  | 165 |

| Figure 19.2. 32.768 kHz External Crystal Example                 | 169 |

| Figure 19.3. Example Clock Multiplier Output                     | 172 |

| 20. smaRTClock (Real Time Clock)                                 |     |

| Figure 20.1. smaRTClock Block Diagram                            | 177 |

| 21.SMBus                                                         |     |

| Figure 21.1. SMBus Block Diagram                                 | 191 |

| Figure 21.2. Typical SMBus Configuration                         | 192 |

| Figure 21.3. SMBus Transaction                                   | 193 |

| Figure 21.4. Typical SMBus SCL Generation                        | 196 |

| Figure 21.5. Typical Master Transmitter Sequence                 | 202 |

| Figure 21.6. Typical Master Receiver Sequence                    | 202 |

| Figure 21.7. Typical Slave Receiver Sequence                     |     |

| Figure 21.8. Typical Slave Transmitter Sequence                  |     |

| 22. UART0                                                        |     |

| Figure 22.1. UART0 Block Diagram                                 | 207 |

| Figure 22.2. UART0 Baud Rate Logic                               |     |

| Figure 22.3. UART Interconnect Diagram                           |     |

| Figure 22.4. 8-Bit UART Timing Diagram                           |     |

| Figure 22.5. 9-Bit UART Timing Diagram                           |     |

| Figure 22.6. UART Multi-Processor Mode Interconnect Diagram      |     |

NOTES:

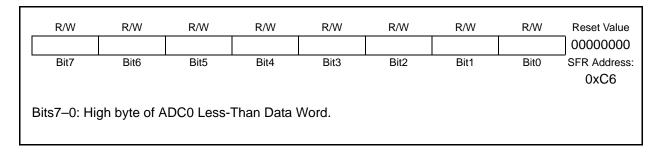

### SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

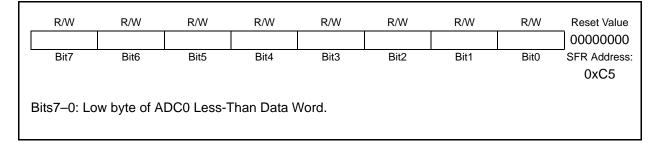

## SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

## SFR Definition 9.2. CPT0MX: Comparator0 MUX Selection

| R/W    | R/W                                                                                                                       | R/W                                                                                                                                                                                 | R/W                                                                                                                                                                                                                | R/W                                                                                                                                            | R/W                                                                                                                                                 | R/W          | R/W      | Reset Value         |

|--------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|---------------------|

| CMX0N3 |                                                                                                                           |                                                                                                                                                                                     |                                                                                                                                                                                                                    |                                                                                                                                                |                                                                                                                                                     | CMX0P1       | CMX0P0   | 11111111            |

| Bit7   | Bit6                                                                                                                      | Bit5                                                                                                                                                                                | Bit4                                                                                                                                                                                                               | Bit3                                                                                                                                           | Bit2                                                                                                                                                | Bit1         | Bit0     | SFR Address<br>0x9F |

|        |                                                                                                                           |                                                                                                                                                                                     |                                                                                                                                                                                                                    |                                                                                                                                                | e Input MUX Se<br>the Comparato                                                                                                                     |              | e input. |                     |

| [      | CMX0N3                                                                                                                    | CMX0N2                                                                                                                                                                              | CMX0N1                                                                                                                                                                                                             | CMX0N0                                                                                                                                         | Negative Inp                                                                                                                                        | out          |          |                     |

|        | 0                                                                                                                         | 0                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 0                                                                                                                                              | P0.1                                                                                                                                                |              |          |                     |

|        | 0                                                                                                                         | 0                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 1                                                                                                                                              | P0.3                                                                                                                                                |              |          |                     |

|        | 0                                                                                                                         | 0                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 0                                                                                                                                              | P0.5                                                                                                                                                |              |          |                     |

| -      | 0                                                                                                                         | 0                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 1                                                                                                                                              | P0.7                                                                                                                                                |              |          |                     |

| _      | 0                                                                                                                         | 1                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 0                                                                                                                                              | P1.1                                                                                                                                                |              |          |                     |

|        | 0                                                                                                                         | 1                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 1                                                                                                                                              | P1.3                                                                                                                                                |              |          |                     |

|        | 0                                                                                                                         | 1                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 0                                                                                                                                              | P1.5                                                                                                                                                |              |          |                     |

|        | 0                                                                                                                         | 1                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 1                                                                                                                                              | P1.7                                                                                                                                                |              |          |                     |

| -      | 1                                                                                                                         | 0                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 0                                                                                                                                              | P2.1                                                                                                                                                |              |          |                     |

| _      | 1                                                                                                                         | 0                                                                                                                                                                                   | 0                                                                                                                                                                                                                  | 1                                                                                                                                              | P2.3*                                                                                                                                               |              |          |                     |

|        |                                                                                                                           | 0                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 0                                                                                                                                              | P2.5*                                                                                                                                               |              |          |                     |

| -      | 1                                                                                                                         |                                                                                                                                                                                     | 4                                                                                                                                                                                                                  | 4                                                                                                                                              | <b>D</b> O <b>7</b>                                                                                                                                 |              |          |                     |

| -      | 1                                                                                                                         | 0                                                                                                                                                                                   | 1                                                                                                                                                                                                                  | 1                                                                                                                                              | P2.7                                                                                                                                                |              |          |                     |

| -      | 1<br>1                                                                                                                    | 0<br>1                                                                                                                                                                              | 1<br>x<br>on the C805                                                                                                                                                                                              | х                                                                                                                                              | P2.7<br>Reserved                                                                                                                                    |              |          |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits                                                                            | 0<br>1<br>nilable only o<br>CMX0P0: 0<br>select whice                                                                                                                               | x<br>on the C805<br>Comparator<br>ch Port pin                                                                                                                                                                      | x<br>1F410/2.<br>r0 Positive<br>is used as                                                                                                     | Reserved<br>Input MUX Sel<br>the Comparato                                                                                                          | or0 positive | input.   |                     |

|        | 1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3                                                                       | 0<br>1<br>iilable only o<br>CMX0P0: 0<br>select whio<br>CMX0P2                                                                                                                      | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1                                                                                                                                                            | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0                                                                                           | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp                                                                                          | or0 positive | input.   |                     |

|        | 1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0                                                                  | 0<br>1<br>iilable only o<br>CMX0P0: 0<br>select whio<br><b>CMX0P2</b><br>0                                                                                                          | x<br>on the C805<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0                                                                                                                                                | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0                                                                                      | Reserved<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0                                                                           | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0                                                   | 0<br>1<br>nilable only of<br>CMX0P0: 0<br>select whice<br>CMX0P2<br>0<br>0                                                                                                          | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0                                                                                                                                                  | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1                                                                                 | Reserved<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2                                                                   | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0                                              | 0<br>1<br>hilable only of<br>CMX0P0: C<br>select which<br>CMX0P2<br>0<br>0<br>0                                                                                                     | x<br>on the C805<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1                                                                                                                                      | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0                                                                            | Reserved<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4                                                           | or0 positive | input.   |                     |

|        | 1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                    | 0<br>1<br>iilable only o<br>CMX0P0: C<br>select whic<br>CMX0P2<br>0<br>0<br>0<br>0<br>0                                                                                             | x<br>on the C805<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1<br>1                                                                                                                                 | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>1                                                                  | Reserved<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6                                                   | or0 positive | input.   |                     |

|        | 1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0      | 0<br>1<br>iilable only o<br>CMX0P0: C<br>select whic<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1                                                                                        | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>1<br>0                                                                                                                              | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0                                                        | Reserved<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0                                           | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>nilable only of<br>CMX0P0: C<br>select whice<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1                                                                            | x<br>on the C805<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1<br>1<br>1<br>0<br>0                                                                                                                  | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                                                   | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp<br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2                                          | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only o<br>CMX0P0: C<br>select whic<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1                                                                              | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1                                                                                                | x<br>1F410/2.<br>r0 Positive<br>is used as<br><b>CMX0P0</b><br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0                             | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp<br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2<br>P1.4                                  | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only of<br>CMX0P0: C<br>select white<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1                                                             | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1                                                                                      | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                               | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp<br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2<br>P1.4<br>P1.6                          | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ave<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only o<br>CMX0P0: C<br>select whic<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>0                                                          | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0                                                                  | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0      | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp<br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.0<br>P1.2<br>P1.4<br>P1.6<br>P2.0          | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ava<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only of<br>CMX0P0: C<br>select which<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0                                                        | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1           | Reserved<br>Input MUX Sel<br>the Comparato<br>Po.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2<br>P1.4<br>P1.6<br>P2.0<br>P2.2                          | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ave<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only o<br>CMX0P0: C<br>select whic<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                       | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1 | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | Reserved<br>Input MUX Sel<br>the Comparato<br>Positive Inp<br>P0.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2<br>P1.4<br>P1.6<br>P2.0<br>P2.2<br>P2.4* | or0 positive | input.   |                     |

|        | 1<br>1<br>*Note: Ave<br>CMX0P3–0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>iilable only of<br>CMX0P0: C<br>select which<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | x<br>on the C805<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0                                                        | x<br>1F410/2.<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1           | Reserved<br>Input MUX Sel<br>the Comparato<br>Po.0<br>P0.2<br>P0.4<br>P0.6<br>P1.0<br>P1.2<br>P1.4<br>P1.6<br>P2.0<br>P2.2                          | or0 positive | input.   |                     |

| Table 10.1. CIP-51 Instruction Set Summary <sup>1</sup> | (Continued) |

|---------------------------------------------------------|-------------|

|---------------------------------------------------------|-------------|

| Mnemonic           | Description                              | Bytes | Clock<br>Cycles     |  |  |

|--------------------|------------------------------------------|-------|---------------------|--|--|

| ORL A, @Ri         | OR indirect RAM to A                     | 1     | 2                   |  |  |

| ORL A, #data       | OR immediate to A                        | 2     | 2                   |  |  |

| ORL direct, A      | OR A to direct byte                      | 2     | 2                   |  |  |

| ORL direct, #data  | OR immediate to direct byte              | 3     | 3                   |  |  |

| XRL A, Rn          | Exclusive-OR Register to A               | 1     | 1                   |  |  |

| XRL A, direct      | Exclusive-OR direct byte to A            | 2     | 2                   |  |  |

| XRL A, @Ri         | Exclusive-OR indirect RAM to A           | 1     | 2                   |  |  |

| XRL A, #data       | Exclusive-OR immediate to A              | 2     | 2                   |  |  |

| XRL direct, A      | Exclusive-OR A to direct byte            | 2     | 2                   |  |  |

| XRL direct, #data  | Exclusive-OR immediate to direct byte    | 3     | 3                   |  |  |

| CLR A              | Clear A                                  | 1     | 1                   |  |  |

| CPL A              | Complement A                             | 1     | 1                   |  |  |

| RL A               | Rotate A left                            | 1     | 1                   |  |  |

| RLC A              | Rotate A left through Carry              | 1     | 1                   |  |  |

| RR A               | Rotate A right                           | 1     | 1                   |  |  |

| RRC A              | Rotate A right through Carry             | 1     | 1                   |  |  |

| SWAP A             | Swap nibbles of A                        | 1     | 1                   |  |  |

|                    | Data Transfer                            |       |                     |  |  |

| MOV A, Rn          | Move Register to A                       | 1     | 1                   |  |  |

| MOV A, direct      | Move direct byte to A                    | 2     | 2                   |  |  |

| MOV A, @Ri         | Move indirect RAM to A                   | 1     | 2                   |  |  |

| MOV A, #data       | Move immediate to A                      | 2     | 2                   |  |  |

| MOV Rn, A          | Move A to Register                       | 1     | 1                   |  |  |

| MOV Rn, direct     | Move direct byte to Register             | 2     | 2                   |  |  |

| MOV Rn, #data      | Move immediate to Register               | 2     | 2                   |  |  |

| MOV direct, A      | Move A to direct byte                    | 2     | 2                   |  |  |

| MOV direct, Rn     | Move Register to direct byte             | 2     | 2                   |  |  |

| MOV direct, direct | Move direct byte to direct byte          | 3     | 3                   |  |  |

| MOV direct, @Ri    | Move indirect RAM to direct byte         | 2     | 2                   |  |  |

| MOV direct, #data  | Move immediate to direct byte            | 3     | 3                   |  |  |

| MOV @Ri, A         | Move A to indirect RAM                   | 1     | 2                   |  |  |

| MOV @Ri, direct    | Move direct byte to indirect RAM         | 2     | 2                   |  |  |

| MOV @Ri, #data     | Move immediate to indirect RAM           | 2     | 2                   |  |  |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant           | 3     | 3                   |  |  |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A        | 1     | 4 to 7 <sup>2</sup> |  |  |

| MOVC A, @A+PC      | Move code byte relative PC to A          | 1     | 4 to 7 <sup>2</sup> |  |  |

| MOVX A, @Ri        | Move external data (8-bit address) to A  | 1     | 3                   |  |  |

| MOVX @Ri, A        | Move A to external data (8-bit address)  | 1     | 3                   |  |  |

| MOVX A, @DPTR      | Move external data (16-bit address) to A | 1     | 3                   |  |  |

| MOVX @DPTR, A      | Move A to external data (16-bit address) |       |                     |  |  |

| PUSH direct        | Push direct byte onto stack              | 2     | 2                   |  |  |

| Notes:             |                                          | I     |                     |  |  |

#### Notes:

Assumes PFEN = 1 for all instruction timing.

MOVC instructions take 4 to 7 clock cycles depending on instruction alignment and the FLRT setting (SFR Definition 16.3. FLSCL: Flash Scale).

| SFR Definition 12.3. EIE1: Extended Interrupt Enable 1 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| R/W                  | R/W                                             | R/W  | R/W   | R/W           | R/W         | R/W           | R/W   | Reset Value |  |  |  |

|----------------------|-------------------------------------------------|------|-------|---------------|-------------|---------------|-------|-------------|--|--|--|

| ET3                  | ECP1                                            | ECP0 | EPCA0 | EADC0         | EWADC0      | ERTC0         | ESMB0 | 00000000    |  |  |  |

| Bit7                 | Bit6                                            | Bit5 | Bit4  | Bit3          | Bit2        | Bit1          | Bit0  |             |  |  |  |

|                      | SFR Address: 0x                                 |      |       |               |             |               |       | : 0xE6      |  |  |  |

|                      |                                                 |      |       |               |             |               |       |             |  |  |  |

| Bit 7:               | ET3: Enable Timer 3 Interrupt.                  |      |       |               |             |               |       |             |  |  |  |

|                      | This bit sets                                   |      | •     | ner 3 interru | ipt.        |               |       |             |  |  |  |

|                      | 0: Disable Ti                                   |      | •     |               |             |               |       |             |  |  |  |

|                      | 1: Enable int                                   |      | •     |               | TF3L or TF3 | BH flags.     |       |             |  |  |  |

| Bit 6:               | ECP1: Enab                                      |      |       |               |             |               |       |             |  |  |  |

|                      | This bit sets                                   |      |       | 1 interrupt.  |             |               |       |             |  |  |  |

|                      | 0: Disable C                                    |      |       |               |             |               |       |             |  |  |  |

| <b>D</b> '' <b>-</b> | 1: Enable int                                   |      | •     |               | CP1RIF or C | CP1FIF flag   | js.   |             |  |  |  |

| Bit 5:               | ECP0: Enab                                      |      | · · · |               |             |               |       |             |  |  |  |

|                      | This bit sets                                   |      |       | 0 interrupt.  |             |               |       |             |  |  |  |

|                      | 0: Disable C                                    |      |       |               |             |               |       |             |  |  |  |

| D:4 4.               | 1: Enable int                                   |      | •     |               |             |               | js.   |             |  |  |  |

| Bit 4:               | EPCA0: Ena                                      | •    |       |               | ` '         | errupt.       |       |             |  |  |  |

|                      | This bit sets<br>0: Disable al                  |      | •     | Au menup      | IS.         |               |       |             |  |  |  |

|                      | 1: Enable inf                                   |      | •     | atod by PC    | 0           |               |       |             |  |  |  |

| Bit 3:               | EADC0: Ena                                      |      |       |               |             |               |       |             |  |  |  |

| Dit 5.               | This bit sets                                   |      |       |               | •           | te interrun   | ŀ     |             |  |  |  |

|                      | 0: Disable A                                    |      | •     |               |             |               |       |             |  |  |  |

|                      | 1: Enable int                                   |      |       |               |             |               |       |             |  |  |  |

| Bit 2:               | EWADC0: E                                       |      |       |               |             | •             |       |             |  |  |  |

| DR Z.                | This bit sets                                   |      |       | •             |             | n interrupt.  |       |             |  |  |  |

|                      | 0: Disable A                                    |      |       |               |             | in interrupti |       |             |  |  |  |

|                      | 1: Enable int                                   |      |       |               |             | ad.           |       |             |  |  |  |

| Bit 1:               | ERTC0: Ena                                      |      |       |               |             | 9-            |       |             |  |  |  |

|                      | This bit sets                                   |      |       |               | nterrupt.   |               |       |             |  |  |  |

|                      | 0: Disable sr                                   |      | -     |               |             |               |       |             |  |  |  |

|                      | 1: Enable int                                   |      | •     | ated by the   | ALRM and C  | DSCFAIL fl    | ag.   |             |  |  |  |

| Bit 0:               | ESMB0: Ena                                      |      | •     |               |             |               | 5     |             |  |  |  |

|                      | This bit sets                                   |      |       |               | t.          |               |       |             |  |  |  |

|                      | 0: Disable al                                   |      |       |               |             |               |       |             |  |  |  |

|                      | 1: Enable interrupt requests generated by SMB0. |      |       |               |             |               |       |             |  |  |  |

|                      |                                                 |      |       |               |             |               |       |             |  |  |  |

| R/W         | R/W                              | R/W        | R/W           | R/W            | R/W             | R/W            | R/W              | Reset Value   |  |  |  |

|-------------|----------------------------------|------------|---------------|----------------|-----------------|----------------|------------------|---------------|--|--|--|

| IN1PL       | IN1SL2                           | IN1SL1     | IN1SL0        | INOPL          | IN0SL2          | IN0SL1         | INOSLO           | 0000000       |  |  |  |

| Bit7        | Bit6                             | Bit5       | Bit4          | Bit3           | Bit2            | Bit1           | Bit0             |               |  |  |  |

|             |                                  |            |               |                |                 |                | SFR Address      | : 0xE4        |  |  |  |

| lote: Refer | to SFR Definition                | 24.1. "TCO | N: Timer Cont | rol" on page 2 | 35 for INT0/1 e | dge- or level- | sensitive interr | upt selection |  |  |  |

|             |                                  |            |               |                |                 | 0              |                  |               |  |  |  |

| Bit 7:      | IN1PL: /INT1                     | Polarity   |               |                |                 |                |                  |               |  |  |  |

|             | 0: /INT1 input is active low.    |            |               |                |                 |                |                  |               |  |  |  |

|             | 1: /INT1 input                   |            | •             |                |                 |                |                  |               |  |  |  |

| 8its 6–4:   | IN1SL2-0: /IN                    |            |               |                |                 |                |                  |               |  |  |  |

|             | These bits sel                   |            |               |                |                 |                |                  |               |  |  |  |

|             | pendent of the                   |            |               |                |                 |                |                  |               |  |  |  |

|             | peripheral tha                   |            |               |                |                 |                |                  |               |  |  |  |

|             | assign the Po                    |            |               |                |                 | the selected   | a pin (accor     | npiisned b    |  |  |  |

|             | setting to '1' th                | he corresp | onding bit i  | in register F  | 05KIP).         |                |                  |               |  |  |  |

|             | IN1SL2-0                         | /INT       | 1 Port Pin    |                |                 |                |                  |               |  |  |  |

|             | 000                              |            | P0.0          |                |                 |                |                  |               |  |  |  |

|             | 001                              |            | P0.1          |                |                 |                |                  |               |  |  |  |

|             | 010                              |            | P0.2          |                |                 |                |                  |               |  |  |  |

|             | 011                              |            | P0.3          |                |                 |                |                  |               |  |  |  |

|             | 100                              |            | P0.4          |                |                 |                |                  |               |  |  |  |

|             | 101                              |            | P0.5          |                |                 |                |                  |               |  |  |  |

|             | 110                              |            | P0.6          |                |                 |                |                  |               |  |  |  |

|             | 111                              |            | P0.7          |                |                 |                |                  |               |  |  |  |

|             |                                  |            |               |                |                 |                |                  |               |  |  |  |

| Bit 3:      | IN0PL: /INT0                     |            |               |                |                 |                |                  |               |  |  |  |

|             | 0: /INT0 interr                  | •          |               |                |                 |                |                  |               |  |  |  |

|             | 1: /INT0 interr                  | •          | •             |                |                 |                |                  |               |  |  |  |

| 3its 2–0:   | INT0SL2-0: /                     |            |               |                |                 |                |                  |               |  |  |  |

|             | These bits sel<br>pendent of the |            |               |                |                 |                |                  |               |  |  |  |

|             | peripheral tha                   |            |               |                |                 |                |                  |               |  |  |  |

|             | assign the Po                    |            |               |                |                 |                |                  |               |  |  |  |

|             | setting to '1' the               |            | •             | •              |                 |                |                  |               |  |  |  |

|             | eeting te i t                    |            | on an ig sit  |                |                 |                |                  |               |  |  |  |

|             | IN0SL2-0                         | /INT       | 0 Port Pin    |                |                 |                |                  |               |  |  |  |

|             | 000                              |            | P0.0          |                |                 |                |                  |               |  |  |  |

|             | 001                              |            | P0.1          |                |                 |                |                  |               |  |  |  |

|             | 010                              |            | P0.2          |                |                 |                |                  |               |  |  |  |

|             | 011                              |            | P0.3          |                |                 |                |                  |               |  |  |  |

|             | 100                              |            | P0.4          |                |                 |                |                  |               |  |  |  |

|             | 101                              |            | P0.5          |                |                 |                |                  |               |  |  |  |

|             | 110                              | 1          | P0.6          |                |                 |                |                  |               |  |  |  |

|             | 111                              |            | P0.7          |                |                 |                |                  |               |  |  |  |

#### For example, the 16-bit 'F41x CRC algorithm can be described by the following code:

```

unsigned short UpdateCRC (unsigned short CRC_acc, unsigned char CRC_input)

ł

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

11

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;</pre>

}

}

// Return the final remainder (CRC value)

return CRC_acc;

}

```

The following table lists several input values and the associated outputs using the 16-bit 'F41x CRC algorithm (an initial value of 0xFFFF is used):

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0x8C                         | 0xB1F4 |

| 0x7D                         | 0x4ECA |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

## 16. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 16.2 for complete Flash memory electrical characteristics.

### 16.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "26. C2 Interface" on page 265. For detailed guidelines on writing or erasing Flash from firmware, please see Section "16.4. Flash Write and Erase Guidelines" on page 139.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled to the higher setting (VDMLVL = '1') in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor disabled will cause a Flash Error device reset.

#### 16.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 16.2.

#### 16.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. **A byte location to be programmed should be erased before a new value is written.** The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- Step 1. Disable interrupts (recommended).

- Step 2. Write the first key code to FLKEY: 0xA5.

- Step 3. Write the second key code to FLKEY: 0xF1.

- Step 4. Set the PSEE bit (register PSCTL).

- Step 5. Set the PSWE bit (register PSCTL).

- Step 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- Step 7. Clear the PSWE and PSEE bits.

- Step 8. Re-enable interrupts.

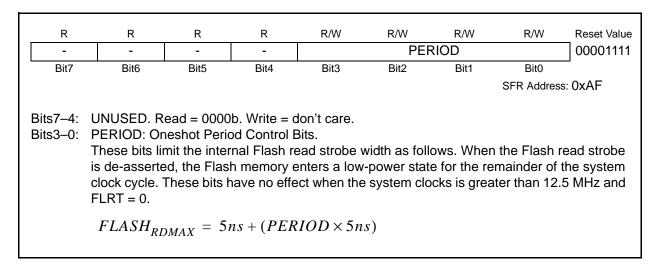

### SFR Definition 16.4. ONESHOT: Flash Oneshot Period

#### **Table 16.2. Flash Electrical Characteristics**

V<sub>DD</sub> = 2.0 to 2.75 V; -40 to +85 °C unless otherwise specified. Typical values are given at 25 °C.

| Parameter                | Conditions                          | Min    | Тур  | Max | Units       |

|--------------------------|-------------------------------------|--------|------|-----|-------------|

| Flash Size               | C8051F410/1                         | 32768* |      |     | butoo       |

| FIASIT SIZE              | C8051F412/3                         | 16384  | —    | _   | bytes       |

| Endurance                | V <sub>DD</sub> is 2.2 V or greater | 20 k   | 90 k | —   | Erase/Write |

| Erase Cycle Time         | FLSCL.3-0 written to '0000'         | 16     | 20   | 24  | ms          |

| Write Cycle Time         | FLSCL.3-0 written to '0000'         | 38     | 46   | 57  | μs          |

| Read Cycle Time          |                                     | 40     | _    | _   | ns          |

| V <sub>DD</sub>          | Write/Erase Operations              | 2.25   | _    | —   | V           |

| *Note: 512 bytes at addr | esses 0x7E00 to 0x7FFF are reserved |        |      |     |             |

(P1MATCH & P1MASK). This allows Software to be notified if a certain change or pattern occurs on P0 or P1 input pins regardless of the XBRn settings. A port match event can cause an interrupt if EMAT (EIE2.1) is set to '1' or cause the internal oscillator to awaken from SUSPEND mode. See Section "19.1.1. Internal Oscillator Suspend Mode" on page 166 for more information.

| R/W      | R/W                                                                                                                            | R/W                                                                | R/W                                         | R/W                          | R/W         | R/W      | R/W         | Reset Value        |

|----------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|------------------------------|-------------|----------|-------------|--------------------|

| P0.7     | P0.6                                                                                                                           | P0.5                                                               | P0.4                                        | P0.3                         | P0.2        | P0.1     | P0.0        | 11111111           |

| Bit7     | Bit6                                                                                                                           | Bit5                                                               | Bit4                                        | Bit3                         | Bit2        | Bit1     | Bit0        | Bit<br>Addressable |

|          |                                                                                                                                |                                                                    |                                             |                              |             |          | SFR Address | s: 0x80            |

| Bits7–0: | P0.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alway<br>pin when cor<br>0: P0.n pin is<br>1: P0.n pin is | Output.<br>Output (h<br>ys reads '0<br>nfigured as<br>s logic low. | igh impedar<br>if selected<br>digital input | nce if corres<br>as analog i | sponding PC | )MDOUT.n | ,           | reads Port         |

## SFR Definition 18.3. P0: Port0

## SFR Definition 18.4. POMDIN: Port0 Input Mode

| R/W      | R/W                           | R/W                                 | R/W                          | R/W                        | R/W                         | R/W                               | R/W         | Reset Value |

|----------|-------------------------------|-------------------------------------|------------------------------|----------------------------|-----------------------------|-----------------------------------|-------------|-------------|

| Bit7     | Bit6                          | Bit5                                | Bit4                         | Bit3                       | Bit2                        | Bit1                              | Bit0        |             |

|          |                               |                                     |                              |                            |                             |                                   | SFR Addres  | s: 0xF1     |

| Bits7–0: | Analog Input<br>Port pins cor | nfigured as                         |                              |                            | · ·                         | • /                               | driver, and | digital     |

| Bits7–0: | • •                           | nfigured as<br>Ibled.<br>Iding P0.n | analog inpu<br>pin is config | its have the<br>ured as an | ir weak pull<br>analog inpu | up, digital<br>t. <b>In order</b> | for the P0. | n pin to be |

| R/W       | R/W                                                                                                                                                 | R               | R/W       | R/W                  | R/W          | R/W          | R/W          | Reset Value   |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|----------------------|--------------|--------------|--------------|---------------|--|--|

| MULEN     | MULINIT                                                                                                                                             | MULRDY          |           | MULDIV               |              | MU           | LSEL         | 0000000       |  |  |

| Bit7      | Bit6                                                                                                                                                | Bit5            | Bit4      | Bit3                 | Bit2         | Bit1         | Bit0         |               |  |  |

|           |                                                                                                                                                     |                 |           |                      |              |              | SFR Addres   | ss: 0xAB      |  |  |

| Note:     | The maximu                                                                                                                                          | m SYSCLK        | is 50 MH  | z, so the Cloc       | k Multiplie  | r output sho | ould be sca  | aled accord-  |  |  |

|           | ingly.                                                                                                                                              |                 |           |                      | ·            | ·            |              |               |  |  |

| Bit7:     | MULEN: Clo<br>0: Clock Mul<br>1: Clock Mul                                                                                                          | tiplier disable | ed.       |                      |              |              |              |               |  |  |

| Bit6:     | MULINIT: CI                                                                                                                                         |                 |           | <b>`</b>             |              |              |              |               |  |  |

| DILO.     |                                                                                                                                                     |                 |           | -<br>Clock Multiplie | r is onable  | od Onco or   | abled writ   | ting a '1' to |  |  |

|           |                                                                                                                                                     |                 |           | iplier. The ML       |              |              |              |               |  |  |

|           | is stabilized.                                                                                                                                      |                 |           |                      |              |              |              |               |  |  |

| Bit5:     | MULRDY: C                                                                                                                                           | lock Multiplie  | r Ready   |                      |              |              |              |               |  |  |

| Dito.     |                                                                                                                                                     |                 |           | atus of the Clo      | ock Multinli | ier          |              |               |  |  |

|           | 0: Clock Mul                                                                                                                                        |                 |           |                      |              |              |              |               |  |  |

|           | 1: Clock Mul                                                                                                                                        |                 |           |                      |              |              |              |               |  |  |

| Bits4–2:  |                                                                                                                                                     |                 |           | Scaling Facto        | r            |              |              |               |  |  |

| Dit34 2.  | These bits s                                                                                                                                        |                 |           |                      |              |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           | d by a factor        | nf 1         |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           | d by a factor        |              |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           | d by a factor        |              |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           | d by a factor        |              |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           |                      |              | (2)          |              |               |  |  |

|           | 100: Clock Multiplier Output scaled by a factor of 2/4 (or 1/2).                                                                                    |                 |           |                      |              |              |              |               |  |  |

|           | 101: Clock Multiplier Output scaled by a factor of 2/5*.                                                                                            |                 |           |                      |              |              |              |               |  |  |

|           | <ul><li>110: Clock Multiplier Output scaled by a factor of 2/6 (or 1/3).</li><li>111: Clock Multiplier Output scaled by a factor of 2/7*.</li></ul> |                 |           |                      |              |              |              |               |  |  |

|           |                                                                                                                                                     |                 |           | ity cycle is not     |              | so sottings  |              |               |  |  |

| Bits1–0:  | MULSEL: CI                                                                                                                                          |                 |           |                      |              | se settings. |              |               |  |  |

| Dita 1=0. |                                                                                                                                                     |                 |           | ed to the Cloc       | k Multinlie  | r            |              |               |  |  |

|           |                                                                                                                                                     |                 | SK Suppli |                      | R Multiplie  |              |              |               |  |  |

|           | MU                                                                                                                                                  | LSEL            | Se        | lected Input         | Clock        | Clock M      | ultiplier O  | utput         |  |  |

|           |                                                                                                                                                     |                 |           |                      |              |              | JLDIV = 00   |               |  |  |

|           |                                                                                                                                                     | 00              | Int       | ternal Oscillat      | or / 2       |              | I Oscillator |               |  |  |

|           |                                                                                                                                                     | ))<br>))        |           | External Oscill      |              |              | al Oscillato |               |  |  |

|           |                                                                                                                                                     | 10              |           | ternal Oscilla       |              |              | al Oscillato |               |  |  |

|           |                                                                                                                                                     | 10              |           | nternal Oscilla      |              |              | I Oscillator |               |  |  |

|           |                                                                                                                                                     | 11              |           | memai Oscilla        | 3101         | interna      | u Oscillator | х 4           |  |  |

#### 20.1. smaRTClock Interface

The smaRTClock Interface consists of three registers: RTC0KEY, RTC0ADR, and RTC0DAT. These interface registers are located on the CIP-51's SFR map and provide access to the smaRTClock internal registers listed in Table 20.1. The smaRTClock internal registers can only be accessed indirectly through the smaRTClock Interface.

#### 20.1.1. smaRTClock Lock and Key Functions