Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 20                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                      |

| Data Converters            | A/D 20x12b; D/A 2x12b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f413-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

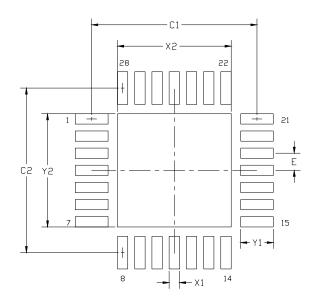

### Figure 4.6. QFN-28 Recommended PCB Land Pattern

| Table 4.5. QFN-28 PCB Land Pattern Dimensions | S |

|-----------------------------------------------|---|

|-----------------------------------------------|---|

| Dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                     | Max  |  | Dimension | Min  | Max  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|-----------|------|------|--|--|--|--|--|--|

| C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.80                                                                                                                                                                                                                    |      |  | X2        | 3.20 | 3.30 |  |  |  |  |  |  |

| C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.3                                                                                                                                                                                                                     | 80   |  | Y1        | 0.85 | 0.95 |  |  |  |  |  |  |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.                                                                                                                                                                                                                      | 50   |  | Y2        | 3.20 | 3.30 |  |  |  |  |  |  |

| X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.20                                                                                                                                                                                                                    | 0.30 |  |           |      |      |  |  |  |  |  |  |

| <ul> <li>Notes:<br/>General</li> <li>1. All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.</li> <li>3. This Land Pattern Design is based on the IPC-7351 guidelines.</li> <li>Solder Mask Design</li> <li>4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad.</li> </ul>            |                                                                                                                                                                                                                         |      |  |           |      |      |  |  |  |  |  |  |

| <ul> <li>Stencil Design</li> <li>5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.</li> <li>6. The stencil thickness should be 0.125mm (5 mils).</li> <li>7. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.</li> <li>8. A 3x3 array of 0.90mm openings on a 1.1mm pitch should be used for the center pad to assure the proper paste volume (67% Paste Coverage).</li> </ul> |                                                                                                                                                                                                                         |      |  |           |      |      |  |  |  |  |  |  |

| <ol> <li>9. A No-C</li> <li>10. The rec</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>Card Assembly</li> <li>9. A No-Clean, Type-3 solder paste is recommended.</li> <li>10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.</li> </ul> |      |  |           |      |      |  |  |  |  |  |  |

### 5.3.5. Output Conversion Code

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from '0' to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to '0'. Example codes are shown in Table 5.1 for both right-justified and left-justified data.

| Input Voltage                | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------------------|----------------------------------------------|---------------------------------------------|

| V <sub>REF</sub> x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| V <sub>REF</sub> x 2048/4096 | 0x0800                                       | 0x8000                                      |

| V <sub>REF</sub> x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                            | 0x0000                                       | 0x0000                                      |

Table 5.1. ADC0 Examples of Right- and Left-Justified Samples

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = "0"), and unused bits in the ADC0H and ADC0L registers are set to '0'. The example in Table 5.2 shows the right-justified result for various input voltages and repeat counts. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Table 5.2. ADC0 | <b>Repeat Count</b> | Examples at | Various | Input V | Voltages |

|-----------------|---------------------|-------------|---------|---------|----------|

|                 |                     |             |         |         | <b>U</b> |

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

### SFR Definition 5.1. ADC0MX: ADC0 Channel Select

| R         | R         | R         | R/W          | R/W                          | R/W    | R/W  | R/W  | Reset Value         |

|-----------|-----------|-----------|--------------|------------------------------|--------|------|------|---------------------|

| -         | -         | -         |              |                              | AD0MX  |      |      | 00011111            |

| Bit7      | Bit6      | Bit5      | Bit4         | Bit3                         | Bit2   | Bit1 | Bit0 | SFR Address<br>0xBB |

| its7–5: I | UNUSED. R | ead = 000 | o: Write = c | on't care.                   |        |      |      |                     |

|           | AD0MX4–0: |           |              |                              |        |      |      |                     |

| ſ         | AD0MX     | 4–0       | AD           | C0 Input C                   | hannel |      |      |                     |

| ŀ         | 0000      | 0         |              | P0.0                         |        |      |      |                     |

| Ī         | 0000      | 1         |              | P0.1                         |        |      |      |                     |

| Ī         | 0001      | 0         |              | P0.2                         |        |      |      |                     |

| -         | 0001      | 1         |              | P0.3                         |        |      |      |                     |

|           | 0010      | 0         |              | P0.4                         |        |      |      |                     |

| ſ         | 0010      | 1         |              |                              |        |      |      |                     |

|           | 0011      |           |              |                              |        |      |      |                     |

|           | 0011      |           |              |                              |        |      |      |                     |

|           | 0100      |           |              |                              |        |      |      |                     |

|           | 0100      |           |              | P1.1                         |        |      |      |                     |

|           | 0101      |           |              | P1.2                         |        |      |      |                     |

|           | 0101      |           |              | P1.3                         |        |      |      |                     |

|           | 0110      |           |              | P1.4                         |        |      |      |                     |

|           | 0110      |           |              | P1.5                         |        |      |      |                     |

|           | 0111      |           |              | P1.6                         |        |      |      |                     |

| _         | 0111      |           |              | P1.7                         |        |      |      |                     |

|           | 1000      |           |              | P2.0                         |        |      |      |                     |

|           | 1000      |           |              | P2.1                         |        |      |      |                     |

| F         | 1001      |           |              | P2.2                         |        |      |      |                     |

|           | 1001      |           |              | P2.3*                        |        |      |      |                     |

|           | 1010      |           |              | P2.4*                        |        |      |      |                     |

| F         | 1010      |           |              | P2.5*                        |        |      |      |                     |

| F         | 1011      |           |              | P2.6*                        |        |      |      |                     |

| F         | 10111     |           |              | P2.7                         |        |      |      |                     |

| ļ         | 1100      |           |              | Temp Sens<br>V <sub>DD</sub> |        |      |      |                     |

|           | 1100      |           |              |                              |        |      |      |                     |

|           | 11010 - 1 | 11111     |              | GND                          |        |      |      |                     |

**Important Note About the V<sub>REF</sub> Pin:** Port pin P1.2 is used as the external V<sub>REF</sub> input and as an output for the internal V<sub>REF</sub>. When using either an external voltage reference or the internal reference circuitry, P1.2 should be configured as an analog pin, and skipped by the Digital Crossbar. To configure P1.2 as an analog pin, clear Bit 2 in register P1MDIN to '0' and set Bit 2 in register P1 to '1'. To configure the Crossbar to skip P1.2, set Bit 2 in register P1SKIP to '1'. Refer to Section "18. Port Input/Output" on page 147 for complete Port I/O configuration details. The TEMPE bit in register REFOCN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADCO measurements performed on the sensor result in meaningless data.

| R/W          | R/W                                | R/W           | R/W         | R/W           | R/W          | R/W          | R/W        | Reset Value |  |

|--------------|------------------------------------|---------------|-------------|---------------|--------------|--------------|------------|-------------|--|

| IDAMR        | G GF                               | ZTCEN         | REFLV       | REFSL         | TEMPE        | BIASE        | REFBE      | 00000000    |  |

| Bit7         | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |               |             |               |              |              |            |             |  |

|              |                                    |               |             |               |              |              |            | 0xD1        |  |

| Bit7:        | IDAMRG: ID<br>0: IDA1 Out          |               | Merge Sele  | ect.          |              |              |            |             |  |

|              | 1: IDA1 Out                        |               | Merged wi   | th IDA0 Out   | out)         |              |            |             |  |

| Bit6:        | GF. General                        |               |             |               | putj.        |              |            |             |  |

| Bito.        | This bit is a                      |               | •           | or use under  | software c   | ontrol       |            |             |  |

| Bit5:        | ZTCEN: Zer                         | • •           |             |               | oonnaro o    | ontroll      |            |             |  |

| 2.101        | 0: ZeroTC B                        | •             |             |               | ed when ne   | eded.        |            |             |  |

|              | 1: ZeroTC B                        |               |             |               |              |              |            |             |  |

| Bit4:        | REFLV: Volt                        | age Refere    | nce Output  | Level Selec   | t.           |              |            |             |  |

|              | This bit sele                      | cts the outp  | ut voltage  | evel for the  | internal vol | tage referer | nce.       |             |  |

|              | 0: Internal v                      | oltage refere | ence set to | 1.5 V.        |              |              |            |             |  |

|              | 1: Internal v                      | •             |             |               |              |              |            |             |  |

| Bit3:        | REFSL: Volt                        | •             |             |               |              |              |            |             |  |

|              | This bit sele                      |               |             |               | ge referenc  | ce.          |            |             |  |

|              | 0: V <sub>REF</sub> pin            |               | -           | nce.          |              |              |            |             |  |

|              | 1: V <sub>DD</sub> used            | as voltage    | reference.  |               |              |              |            |             |  |

| Bit2:        | TEMPE: Ter                         | •             |             |               |              |              |            |             |  |

|              | 0: Internal T                      | •             |             |               |              |              |            |             |  |

|              | 1: Internal T                      |               |             |               |              |              |            |             |  |

| Bit1:        | BIASE: Inter                       |               |             |               |              |              |            |             |  |

|              | 0: Internal A                      | •             |             |               | y enabled v  | vhen neede   | ed.        |             |  |

| <b>D</b> '(0 | 1: Internal A                      | •             |             |               |              |              |            |             |  |

| Bit0:        | REFBE: Inte                        |               |             |               |              |              |            |             |  |

|              | 0: Internal R                      |               |             |               | oltogo rofo  | rongo drivo  | n on tha V | nin         |  |

|              | 1: Internal R                      |               |             | eu. mitemal v | ionage rele  | rence unve   |            | REF PILL    |  |

|              |                                    |               |             |               |              |              |            |             |  |

|              |                                    |               |             |               |              |              |            |             |  |

### SFR Definition 7.1. REF0CN: Reference Control

# 9. Comparators

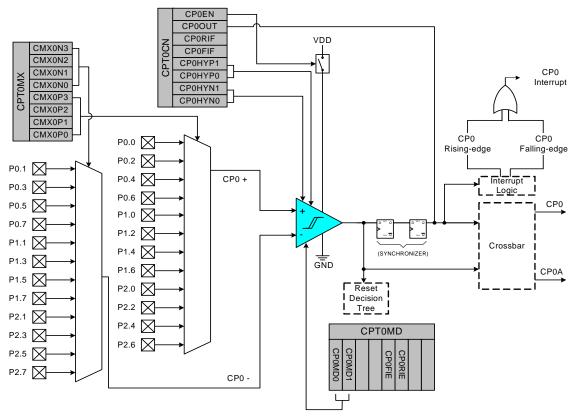

C8051F41x devices include two on-chip programmable voltage comparators: Comparator0 is shown in Figure 9.1; Comparator1 is shown in Figure 9.2. The two comparators operate identically, but only Comparator0 can be used as a reset source.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP or SUSPEND mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "18.2. Port I/O Initialization" on page 151). Comparator0 may also be used as a reset source (see Section "15.5. Comparator0 Reset" on page 130).

The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 9.2). The CMX0P3-CMX0P0 bits select the Comparator0 positive input; the CMX0N3-CMX0N0 bits select the Comparator0 negative input. The Comparator1 inputs are selected in the CPT1MX register (SFR Definition 9.4). The CMX1P3-CMX1P0 bits select the Comparator1 positive input; the CMX1N3-CMX1N0 bits select the Comparator1 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs in their associated Port configuration register (with a '1' written to the corresponding Port Latch register), and configured to be skipped by the Crossbar (for details on Port configuration, see **Section "18.3. General Purpose Port I/O" on page 154**)

Figure 9.1. Comparator0 Functional Block Diagram

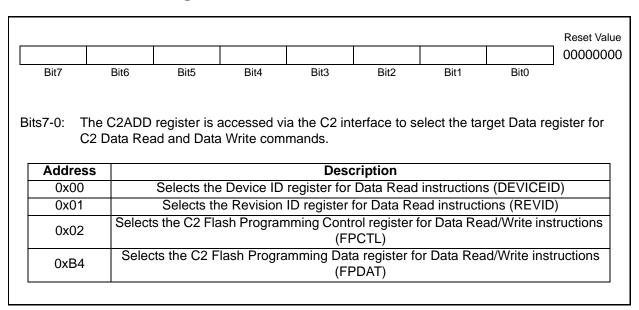

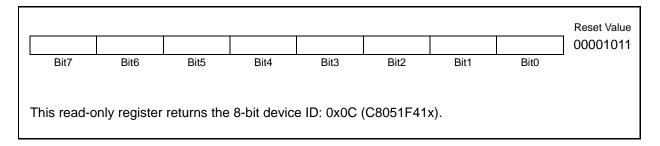

# 16. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 16.2 for complete Flash memory electrical characteristics.

### 16.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "26. C2 Interface" on page 265. For detailed guidelines on writing or erasing Flash from firmware, please see Section "16.4. Flash Write and Erase Guidelines" on page 139.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled to the higher setting (VDMLVL = '1') in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor disabled will cause a Flash Error device reset.

### 16.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 16.2.

### 16.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. **A byte location to be programmed should be erased before a new value is written.** The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- Step 1. Disable interrupts (recommended).

- Step 2. Write the first key code to FLKEY: 0xA5.

- Step 3. Write the second key code to FLKEY: 0xF1.

- Step 4. Set the PSEE bit (register PSCTL).

- Step 5. Set the PSWE bit (register PSCTL).

- Step 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- Step 7. Clear the PSWE and PSEE bits.

- Step 8. Re-enable interrupts.

NOTES:

|            | PO          |     |   |   |   |   |     | P1 |    |     |      |   |   |   | P2 |   |      |      |      |       |      |   |   |   |

|------------|-------------|-----|---|---|---|---|-----|----|----|-----|------|---|---|---|----|---|------|------|------|-------|------|---|---|---|

| SF Signals | i0          | ·i1 |   |   |   | C | nvs | tr | x1 | x2  | vref |   |   |   |    |   |      |      |      |       |      |   |   |   |

| PIN I/O    | 0           | 1   | 2 | 3 | 4 | 5 | 6   | 7  | 0  | 1   | 2    | 3 | 4 | 5 | 6  | 7 | 0    | 1    | 2    | 3     | 4    | 5 | 6 | 7 |

| ТХО        |             |     |   |   |   |   | _   |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| RX0        |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| SCK        |             |     |   |   |   |   | -   |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| MISO       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| MOSI       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| NSS*       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   | (*4- | Wire | e SP | 'l Or | nly) |   |   |   |

| SDA        |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| SCL        |             |     |   |   |   |   | 1   |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CP0        |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CP0A       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CP1        |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CP1A       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| /SYSCLK    |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CEX0       |             |     |   |   |   |   |     |    |    |     |      |   |   |   | 1  |   |      |      |      |       |      |   |   |   |

| CEX1       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    | I |      |      |      |       |      |   |   |   |

| CEX2       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CEX3       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| CEX4       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      | 1    |       |      |   |   |   |

| CEX5       |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| ECI        |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| ТО         |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

| T1         |             |     |   |   |   |   |     |    |    |     |      |   |   |   |    |   |      |      |      |       |      |   |   |   |

|            | 0           | 0   | 0 | 0 | 0 | 0 | 0   | 0  | 1  | 1   | 0    | 0 | 0 | 0 | 0  | 0 | 0    | 0    | 0    | 0     | 0    | 0 | 0 | ( |

|            | P0SKIP[0:7] |     |   |   |   |   |     |    |    | ISK |      |   | - | - |    |   |      |      |      | P[0:  |      |   |   |   |

SF Signals Special Function Signals are not assigned by the crossbar. When these signals are enabled, the CrossBar must be manually configured to skip their corresponding port pins.

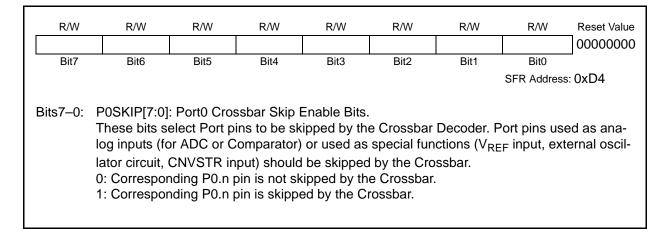

## Figure 18.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously starting at P0.0 after prioritized functions and skipped pins are assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

| SFR Definition 18.5. P0MDOUT: Port0 Output | Mode |

|--------------------------------------------|------|

|--------------------------------------------|------|

| R/W      | R/W                                                                                       | R/W                                                         | R/W                                        | R/W                     | R/W  | R/W  | R/W  | Reset Value<br>00000000 |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------|-------------------------|------|------|------|-------------------------|--|--|--|--|--|

| Bit7     | Bit6                                                                                      | Bit5                                                        | Bit4                                       | Bit3                    | Bit2 | Bit1 | Bit0 |                         |  |  |  |  |  |

|          | SFR Address: 0xA4                                                                         |                                                             |                                            |                         |      |      |      |                         |  |  |  |  |  |

| Bits7–0: | Output Confi<br>ter P0MDIN<br>0: Correspor<br>1: Correspor<br>(Note: When<br>of the value | is logic 0.<br>Inding P0.n (<br>Inding P0.n (<br>ISDA and S | Output is op<br>Output is pu<br>SCL appear | ben-drain.<br>ush-pull. | ., . |      |      | Ū.                      |  |  |  |  |  |

### SFR Definition 18.6. P0SKIP: Port0 Skip

| R/W<br>P1.7 | R/W<br>P1.6                                                                                                                    | R/W<br>P1.5                                                            | R/W<br>P1.4                                | R/W<br>P1.3                  | R/W<br>P1.2 | R/W<br>P1.1 | R/W<br>P1.0      | Reset Value |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------|------------------------------|-------------|-------------|------------------|-------------|--|--|--|--|--|

| Bit7        | Bit6                                                                                                                           | Bit5                                                                   | Bit4                                       | Bit3                         | Bit2        | Bit1        | Bit0 Addressable |             |  |  |  |  |  |

|             | SFR Address: 0x90                                                                                                              |                                                                        |                                            |                              |             |             |                  |             |  |  |  |  |  |

| Bits7–0:    | P1.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alway<br>pin when cor<br>0: P1.n pin is<br>1: P1.n pin is | Output.<br>n Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital input | nce if corres<br>as analog i | ponding P1  | IMDOUT.n    | ,                | eads Port   |  |  |  |  |  |

SFR Definition 18.10. P1: Port1

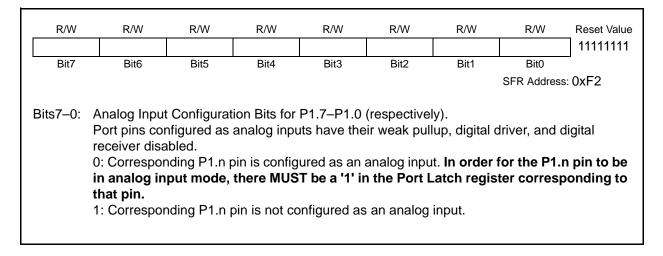

### SFR Definition 18.11. P1MDIN: Port1 Input Mode

NOTES:

ning of each series of consecutive reads. Software must check if the smaRTClock Interface is busy prior to reading RTC0DAT. Autoread is enabled by setting AUTORD (RTC0ADR.6) to logic 1.

### 20.1.4. RTC0ADR Autoincrement Feature

For ease of reading and writing the 48-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current smaRTClock timer value.

| smaRTClock<br>Address | smaRTClock<br>Register | Register Name                                      | Description                                                                                                                     |

|-----------------------|------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0x00 - 0x05           | CAPTUREn               | smaRTClock Capture<br>Registers                    | Six Registers used for setting the 47-bit<br>smaRTClock timer or reading its current<br>value. The LSB of CAPTURE0 is not used. |

| 0x06                  | RTC0CN                 | smaRTClock Control<br>Register                     | Controls the operation of the smaRTClock State Machine.                                                                         |

| 0x07                  | RTC0XCN                | smaRTClock Oscillator<br>Control Register          | Controls the operation of the smaRTClock Oscillator.                                                                            |

| 0x08–0x0D             | ALARMn                 | smaRTClock Alarm<br>Registers                      | Six registers used to set or read the 47-bit<br>smaRTClock alarm value. The LSB of<br>ALARM0 is not used.                       |

| 0x0E                  | RAMADDR                | smaRTClock Backup RAM<br>Indirect Address Register | Used as an index to the 64 byte smaRTClock backup RAM.                                                                          |

| 0x0F                  | RAMDATA                | smaRTClock Backup RAM<br>Indirect Data Register    | Used to read or write the byte pointed to by RAMADDR.                                                                           |

### Table 20.1. smaRTClock Internal Registers

```

; Enable the smaRTClock

mov RTCOADR, #06h ; address the RTCOCN register

mov RTC0DAT, #080h ; enable the smaRTClock

; poll on the BUSY bit

L0:mov A, RTCOADR

jb ACC.7, L0

; Write to the smaRTClock RAM

mov RTCOADR, #OEh; address the RAMADDR register

mov RTC0DAT, #20h; write the address of 0x20 to RAMADDR

L1: mov A, RTCOADR

; poll on the BUSY bit

jb ACC.7, L1

mov RTCOADR, #0Fh; address the RAMDATA register

mov RTC0DAT, #0A5h; write 0xA5 to RAM address 0x20

L2: mov A, RTCOADR

; poll on the BUSY bit

jb ACC.7, L2

; Read from the smaRTClock RAM

mov RTCOADR, #0Eh; address the RAMADDR register

mov RTC0DAT, #20h; write the address of 0x20 to RAMADDR

L3: mov A, RTCOADR ; poll on the BUSY bit

jb ACC.7, L3

mov RTCOADR, #OFh ; address the RAMDATA register

orl RTCOADR, #80h ; initiate a read of the RAMDATA register

L4: mov A, RTCOADR ; poll on the BUSY bit

jb ACC.7, L4

movR0, #80h

mov@R0, RTC0DAT

; read the value of RAM address 0x20 into

; the 128-byte internal RAM

```

```

To reduce the number of instructions necessary to read and write sections of the 64-byte RAM, the RAMADDR register automatically increments after each write or read. The following C example initializes the entire 64-byte RAM to 0xA5 and copies this value from the RAM to an array using the auto-increment feature:

```

```

// in 'C':

unsigned char RAM_data[64] = 0x00;

unsigned char addr;

// Unlock smaRTClock, enable smaRTClock

// Write to the entire smaRTClock RAM

RTC0ADR = 0x0E;// address the RAMADDR register

RTC0DAT = 0x00;// write the address of 0x00 to RAMADDR

while ((RTC0ADR & 0x80) == 0x80); // poll on the BUSY bit

RTC0ADR = 0x0F;// address the RAMDATA register

for (addr = 0; addr < 64; addr++)

{

RTC0DAT = 0xA5; // write 0xA5 to every RAM address

while ((RTC0ADR & 0x80) == 0x80);// poll on the BUSY bit

}

// Read from the entire smaRTClock RAM

RTC0ADR = 0x0E;// address the RAMADDR register

```

### SFR Definition 22.2. SBUF0: Serial (UART0) Port Data Buffer

| R/W      | R/W                                                                             | R/W                                      | R/W                                          | R/W                        | R/W                             | R/W          | R/W           | Reset Value      |

|----------|---------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------|----------------------------|---------------------------------|--------------|---------------|------------------|

| Bit7     | Bit6                                                                            | Bit5                                     | Bit4                                         | Bit3                       | Bit2                            | Bit1         | Bit0          |                  |

|          |                                                                                 |                                          |                                              |                            |                                 |              | SFR Addres    | s: 0 <b>x9</b> 9 |

| Bits7–0: | SBUF0[7:0]:<br>This SFR ac<br>data is writte<br>sion. Writing<br>tents of the r | cesses two<br>en to SBUF(<br>a byte to S | registers; a<br>0, it goes to<br>BUF0 initia | transmit sh<br>the transmi | ift register a<br>t shift regis | ter and is h | eld for seria | al transmis-     |

| R/W            | R/W                                                                                                                                   | R/W                                                                                                                                                                                        | R/W                                                                                                                           | R/W                                                                                                                | R/W                                                                    | R/W                                                                                                                 | R/W                      | Reset Value       |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|--|--|--|--|

| GATE1          | C/T1                                                                                                                                  | T1M1                                                                                                                                                                                       | T1M0                                                                                                                          | GATE0                                                                                                              | C/T0                                                                   | T0M1                                                                                                                | T0M0                     | 00000000          |  |  |  |  |

| Bit7           | Bit6                                                                                                                                  | Bit5                                                                                                                                                                                       | Bit4                                                                                                                          | Bit3                                                                                                               | Bit2                                                                   | Bit1                                                                                                                | Bit0                     | 1                 |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          | SFR Address: 0x89 |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

| Bit7:          | GATE1: Timer 1 Gate Control.                                                                                                          |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       | <ul> <li>0: Timer 1 enabled when TR1 = 1 irrespective of /INT1 logic level.</li> <li>1: Timer 1 enabled only when TR1 = 1 AND /INT1 is active as defined by bit IN1PL in regis-</li> </ul> |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

| D:40           |                                                                                                                                       |                                                                                                                                                                                            | Definition 12.                                                                                                                | 7. "IT01CF                                                                                                         | : IN I 0/IN I '                                                        | Configurat                                                                                                          | tion" on pag             | ge 118).          |  |  |  |  |

| Bit6:          |                                                                                                                                       | nter/Timer 1                                                                                                                                                                               |                                                                                                                               |                                                                                                                    | اد مام المعمم ا                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            | ner 1 increme                                                                                                                 |                                                                                                                    |                                                                        |                                                                                                                     | · · · ·                  |                   |  |  |  |  |

|                | (T1).                                                                                                                                 | Function.                                                                                                                                                                                  | Timer 1 increr                                                                                                                | nented by n                                                                                                        | Ign-to-low                                                             | transitions (                                                                                                       | on external              | input pin         |  |  |  |  |

| Rite5_1.       |                                                                                                                                       | 10. Timor 1                                                                                                                                                                                | Mode Select                                                                                                                   |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

| Dit30-4.       |                                                                                                                                       |                                                                                                                                                                                            | Timer 1 opera                                                                                                                 |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                | T1M1                                                                                                                                  | T1M0                                                                                                                                                                                       |                                                                                                                               | Mode                                                                                                               |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                | 0                                                                                                                                     | 0                                                                                                                                                                                          | Mode 0: 13-bit counter/timer                                                                                                  |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                | 0                                                                                                                                     | 1                                                                                                                                                                                          | Mode                                                                                                                          | e 1: 16-bit c                                                                                                      |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                | 1                                                                                                                                     | 0                                                                                                                                                                                          | Mode 2: 8-bi                                                                                                                  | t counter/tin                                                                                                      |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                | 1                                                                                                                                     | 1                                                                                                                                                                                          | Мо                                                                                                                            | de 3: Timer                                                                                                        |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            |                                                                                                                               |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

|                |                                                                                                                                       |                                                                                                                                                                                            | •                                                                                                                             |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

| Bit3:          |                                                                                                                                       | mer 0 Gate                                                                                                                                                                                 | · ·                                                                                                                           |                                                                                                                    |                                                                        |                                                                                                                     |                          |                   |  |  |  |  |

| Bit3:          | 0: Timer 0                                                                                                                            | enabled wh                                                                                                                                                                                 | nen TR0 = 1 i                                                                                                                 |                                                                                                                    | of /INT0 log                                                           |                                                                                                                     |                          |                   |  |  |  |  |

| Bit3:          | 0: Timer 0<br>1: Timer 0                                                                                                              | enabled wh<br>enabled on                                                                                                                                                                   | nen TR0 = 1 i<br>ly when TR0                                                                                                  | = 1 AND /IN                                                                                                        | of /INT0 log                                                           | e as define                                                                                                         |                          |                   |  |  |  |  |

|                | 0: Timer 0<br>1: Timer 0<br>ter IT01CF                                                                                                | enabled wh<br>enabled on<br>(see SFR                                                                                                                                                       | nen TR0 = 1 i<br>ly when TR0<br>Definition 12.                                                                                | = 1 AND /IN                                                                                                        | of /INT0 log                                                           | e as define                                                                                                         |                          |                   |  |  |  |  |

| Bit3:<br>Bit2: | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour                                                                                  | enabled wh<br>enabled on<br>(see SFR<br>nter/Timer S                                                                                                                                       | nen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.                                                                     | = 1 AND /IN<br>7. "IT01CF                                                                                          | of /INT0 log<br>IT0 is activ<br>: INT0/INT                             | e as define<br>1 Configurat                                                                                         | tion" on pag             | ge 118).          |  |  |  |  |

|                | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour<br>0: Timer Fr                                                                   | enabled wh<br>enabled on<br>(see SFR<br>nter/Timer S<br>unction: Tim                                                                                                                       | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme                                                    | = 1 AND /IN<br>7. "IT01CF<br>ented by cloo                                                                         | of /INT0 log<br>IT0 is activ<br>INT0/INT <sup>2</sup><br>ck defined l  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

|                | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Coun<br>0: Timer Fu<br>1: Counter                                                     | enabled wh<br>enabled on<br>(see SFR<br>nter/Timer S<br>unction: Tim                                                                                                                       | nen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.                                                                     | = 1 AND /IN<br>7. "IT01CF<br>ented by cloo                                                                         | of /INT0 log<br>IT0 is activ<br>INT0/INT <sup>2</sup><br>ck defined l  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour<br>0: Timer Fo<br>1: Counter<br>(T0).                                            | enabled wh<br>enabled on<br>(see SFR<br>hter/Timer S<br>unction: Tim<br>Function: 1                                                                                                        | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increm                                  | = 1 AND /IN<br>7. "IT01CF<br>Inted by cloo<br>mented by h                                                          | of /INT0 log<br>IT0 is activ<br>INT0/INT <sup>2</sup><br>ck defined l  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

|                | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour<br>0: Timer Fu<br>1: Counter<br>(T0).<br>T0M1-T0M                                | enabled wh<br>enabled on<br>(see SFR)<br>nter/Timer S<br>unction: Tim<br>Function: 1<br>10: Timer 0                                                                                        | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increme<br>Mode Select                  | = 1 AND /IN<br>7. "IT01CF<br>Inted by cloo<br>mented by h                                                          | of /INT0 log<br>IT0 is activ<br>INT0/INT <sup>2</sup><br>ck defined l  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour<br>0: Timer Fu<br>1: Counter<br>(T0).<br>T0M1-T0M                                | enabled wh<br>enabled on<br>(see SFR)<br>nter/Timer S<br>unction: Tim<br>Function: 1<br>10: Timer 0                                                                                        | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increm                                  | = 1 AND /IN<br>7. "IT01CF<br>Inted by cloo<br>mented by h                                                          | of /INT0 log<br>IT0 is activ<br>INT0/INT <sup>2</sup><br>ck defined l  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Cour<br>0: Timer Fu<br>1: Counter<br>(T0).<br>T0M1-T0M                                | enabled wh<br>enabled on<br>(see SFR)<br>nter/Timer S<br>unction: Tim<br>Function: 1<br>10: Timer 0                                                                                        | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increme<br>Mode Select                  | = 1 AND /IN<br>7. "IT01CF<br>Inted by cloo<br>mented by h                                                          | of /INT0 log<br>IT0 is activ<br>INT0/INT<br>k defined l<br>igh-to-low  | e as define<br>1 Configurat                                                                                         | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Court<br>0: Timer Fu<br>1: Counter<br>(T0).<br>T0M1–T0M<br>These bits                 | enabled wh<br>enabled on<br>(see SFR)<br>Inter/Timer S<br>unction: Tim<br>Function: T<br>10: Timer 0<br>select the                                                                         | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increme<br>Mode Select<br>Timer 0 opera | = 1 AND /IN<br>7. "IT01CF<br>ented by cloo<br>mented by h<br>ation mode.<br>Mode<br>e 0: 13-bit c                  | of /INT0 log<br>IT0 is activ<br>INT0/INT<br>ck defined l<br>igh-to-low | e as define<br>I Configurat<br>by TOM bit (<br>transitions o                                                        | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Count<br>0: Timer For<br>1: Counter<br>(T0).<br>T0M1–T0M<br>These bits<br><b>T0M1</b> | enabled wh<br>enabled on<br>(see SFR  <br>inter/Timer S<br>unction: Tim<br>Function: T<br>40: Timer 0<br>select the<br>TOM0                                                                | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increme<br>Mode Select<br>Timer 0 opera | = 1 AND /IN<br>7. "IT01CF<br>ented by cloo<br>mented by h<br>ation mode.<br>Mode                                   | of /INT0 log<br>IT0 is activ<br>INT0/INT<br>ck defined l<br>igh-to-low | e as define<br>I Configurat<br>by TOM bit (<br>transitions o                                                        | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

| Bit2:          | 0: Timer 0<br>1: Timer 0<br>ter IT01CF<br>C/T0: Courd<br>0: Timer Fu<br>1: Counter<br>(T0).<br>T0M1–T0M<br>These bits<br>T0M1<br>0    | enabled wh<br>enabled on<br>(see SFR)<br>inter/Timer S<br>unction: Tim<br>Function: T<br>M0: Timer 0<br>select the<br>TOM0<br>0                                                            | hen TR0 = 1 i<br>ly when TR0<br>Definition 12.<br>Select.<br>her 0 increme<br>Fimer 0 increme<br>Mode Select<br>Timer 0 opera | = 1 AND /IN<br>7. "IT01CF<br>Inted by cloo<br>mented by h<br>ation mode.<br>Mode<br>e 0: 13-bit c<br>e 1: 16-bit c | of /INT0 log<br>IT0 is activ<br>INT0/INT<br>k defined l<br>igh-to-low  | e as define<br>1 Configurat<br>by TOM bit (<br>transitions of<br>transitions of<br>transitions of<br>transitions of | tion" on pag<br>CKCON.3) | ge 118).          |  |  |  |  |

## SFR Definition 24.2. TMOD: Timer Mode

# 25. Programmable Counter Array (PCA0)

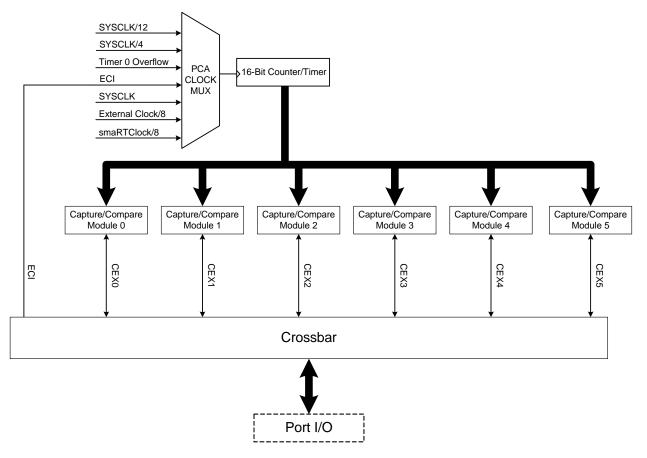

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "18.1. Priority Crossbar Decoder" on page 149 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, smaRTClock Clock divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "25.2. Capture/Compare Modules" on page 251). The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 25.1

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 25.3 for details.

Figure 25.1. PCA Block Diagram

### 25.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

| R/W   | R/W                                                                                                                                                                                     | R/W           | R/W             | R/W           | R/W           | R/W            | R/W           | Reset Valu        |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|---------------|---------------|----------------|---------------|-------------------|--|--|--|--|

| CF    | CR                                                                                                                                                                                      | CCF5          | CCF4            | CCF3          | CCF2          | CCF1           | CCF0          | 000000            |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                    | Bit5          | Bit4            | Bit3          | Bit2          | Bit1           | Bit0          | Bit<br>Addressabl |  |  |  |  |

|       |                                                                                                                                                                                         |               |                 |               |               |                | SFR Addres    | s: 0xD8           |  |  |  |  |