Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 41.667MHz                                                                   |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 39                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3808 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67j60t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.3.6 STATUS REGISTER

The STATUS register, shown in Register 6-3, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled.

These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will set the Z bit but leave the other bits unchanged. The STATUS

register then reads back as '000u uluu'. It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions not affecting any Status bits, see the instruction set summaries in Table 26-2 and Table 26-3.

Note: The C and DC bits operate as a Borrow and Digit Borrow bit respectively, in subtraction.

#### REGISTER 6-3: STATUS REGISTER

| U-0       | U-0                                                          | U-0                                                        | R/W-x             | R/W-x                                   | R/W-x           | R/W-x             | R/W-x            |

|-----------|--------------------------------------------------------------|------------------------------------------------------------|-------------------|-----------------------------------------|-----------------|-------------------|------------------|

|           | —                                                            | _                                                          | N                 | OV                                      | Z               | DC <sup>(1)</sup> | C <sup>(2)</sup> |

| oit 7     |                                                              |                                                            |                   |                                         |                 |                   | bit              |

| Legend:   |                                                              |                                                            |                   |                                         |                 |                   |                  |

| R = Read  | dable bit                                                    | W = Writable                                               | e bit             | U = Unimplen                            | nented bit, rea | ıd as '0'         |                  |

| -n = Valu | e at POR                                                     | '1' = Bit is se                                            | t                 | '0' = Bit is cle                        |                 | x = Bit is unkr   | nown             |

| bit 7-5   | Unimpleme                                                    | nted: Read as                                              | <b>'</b> ∩'       |                                         |                 |                   |                  |

| oit 4     | N: Negative                                                  |                                                            | 0                 |                                         |                 |                   |                  |

| 511 4     | 0                                                            | ed for signed a                                            | rithmetic (2's    | complement). It                         | indicates whe   | ther the result w | vas negative     |

|           | 1 = Result w<br>0 = Result w                                 | •                                                          |                   |                                         |                 |                   |                  |

| bit 3     | which cause                                                  | ed for signed a<br>s the sign bit (b                       | oit 7 of the resu | ult) to change s                        | tate.           | verflow of the 7- | bit magnitude    |

|           | 1 = Overflow<br>0 = No overf                                 |                                                            | igned arithme     | tic (in this arithn                     | netic operatior | ו)                |                  |

| bit 2     | Z: Zero bit                                                  |                                                            |                   |                                         |                 |                   |                  |

|           |                                                              | It of an arithme<br>It of an arithme                       |                   | eration is zero<br>eration is non-z     | ero             |                   |                  |

| bit 1     | 0                                                            | rry/ <mark>Borrow</mark> bit <sup>(1</sup><br>ADDLW, SUBLW |                   | structions:                             |                 |                   |                  |

|           |                                                              | out from the 4th<br>-out from the 4                        |                   | of the result oc<br>t of the result     | curred          |                   |                  |

| bit 0     | C: Carry/Bor                                                 |                                                            |                   |                                         |                 |                   |                  |

|           |                                                              | DDLW, SUBLW                                                | and SUBWF ins     | structions:                             |                 |                   |                  |

|           |                                                              |                                                            |                   | bit of the result<br>t bit of the resul |                 |                   |                  |

| Note 1:   | For Borrow, the po<br>operand. For rotat                     |                                                            |                   |                                         |                 |                   |                  |

| 2:        | For Borrow, the po<br>operand. For rotal<br>source register. | plarity is revers                                          | ed. A subtracti   | on is executed                          | by adding the   | 2's complement    | of the second    |

#### 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing) or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 6-10.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 26.2.1** "Extended Instruction Syntax".

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2 (TMR4), concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 (TMR4) prescaler, the CCPx pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by Equation 17-3:

#### EQUATION 17-3:

PWM Resolution (max) =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCPx pin will not be cleared.

#### 17.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCPx module for PWM operation:

- 1. Set the PWM period by writing to the PR2 (PR4) register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- 3. Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 (TMR4) prescale value, then enable Timer2 (Timer4) by writing to T2CON (T4CON).

- 5. Configure the CCPx module for PWM operation.

#### TABLE 17-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### REGISTER 19-12: PHSTAT2: PHYSICAL LAYER STATUS REGISTER 2

| U-0              | U-0                                                                  | R-0                                                                                               | R-0                  | R-0               | R-0            | R-x             | U-0   |  |  |  |  |  |

|------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|-------------------|----------------|-----------------|-------|--|--|--|--|--|

|                  | —                                                                    | TXSTAT                                                                                            | RXSTAT               | COLSTAT           | LSTAT          | r               |       |  |  |  |  |  |

| oit 15           |                                                                      |                                                                                                   |                      |                   |                | -               | bit   |  |  |  |  |  |

|                  |                                                                      |                                                                                                   |                      |                   |                |                 |       |  |  |  |  |  |

| U-0              | U-0                                                                  | R-0                                                                                               | U-0                  | U-0 U-0 U-0       |                |                 |       |  |  |  |  |  |

| —                |                                                                      | r                                                                                                 | —                    | _                 | _              |                 | _     |  |  |  |  |  |

| bit 7            |                                                                      |                                                                                                   |                      |                   |                |                 | bit ( |  |  |  |  |  |

|                  |                                                                      |                                                                                                   |                      |                   |                |                 |       |  |  |  |  |  |

| Legend:          |                                                                      | r = Reserved                                                                                      | bit                  |                   |                |                 |       |  |  |  |  |  |

| R = Readab       | ole bit                                                              | W = Writable                                                                                      | bit                  | U = Unimplem      | ented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a     | it POR                                                               | '1' = Bit is set                                                                                  |                      | '0' = Bit is clea | ired           | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 12           | 0 = PHY is<br><b>RXSTAT:</b> PH<br>1 = PHY is<br>0 = PHY is          | transmitting data<br>not transmitting<br>HY Receive Statu<br>receiving data<br>not receiving data | data<br>ıs bit<br>a  |                   |                |                 |       |  |  |  |  |  |

| bit 11<br>bit 10 | 1 = A collisi<br>0 = A collisi<br><b>LSTAT:</b> PHY<br>1 = Link is u |                                                                                                   | PHY is both tra<br>g | insmitting and re | eceiving while | in Half-Duplex  | mode) |  |  |  |  |  |

| bit 9            |                                                                      | 0 = Link is down Reserved: Ignore on read                                                         |                      |                   |                |                 |       |  |  |  |  |  |

|                  | Unimplomo                                                            | nted: Read as '                                                                                   | ı'                   |                   |                |                 |       |  |  |  |  |  |

| bit 8-6          | Ommpleme                                                             | meu. Reau as                                                                                      | 5                    |                   |                |                 |       |  |  |  |  |  |

| bit 8-6<br>bit 5 | -                                                                    | gnore on read                                                                                     |                      |                   |                |                 |       |  |  |  |  |  |

### REGISTER 19-15: EIR: ETHERNET INTERRUPT REQUEST (FLAG) REGISTER

| U-0   | R-0   | R/C-0 | R-0    | R/C-0 | U-0 | R/C-0  | R/C-0  |

|-------|-------|-------|--------|-------|-----|--------|--------|

| —     | PKTIF | DMAIF | LINKIF | TXIF  | —   | TXERIF | RXERIF |

| bit 7 |       |       |        |       |     |        | bit 0  |

| Legend:    |                   |                                                                                   |                                    |                                    |  |  |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|--|

| R = Reada  | able bit          | C = Clearable bit                                                                 | U = Unimplemented bit, read as '0' |                                    |  |  |  |  |

| -n = Value | at POR            | '1' = Bit is set                                                                  | '0' = Bit is cleared               | x = Bit is unknown                 |  |  |  |  |

| bit 7      | Unimple           | mented: Read as '0'                                                               |                                    |                                    |  |  |  |  |

| bit 6      | PKTIF: R          | eceive Packet Pending Inter                                                       | rupt Flag bit                      |                                    |  |  |  |  |

|            | 1 = Rece<br>decre | •                                                                                 | more unprocessed packets;          | cleared only when EPKTCNT i        |  |  |  |  |

| bit 5      | DMAIF:            | DMA Interrupt Flag bit                                                            |                                    |                                    |  |  |  |  |

|            |                   | copy or checksum calculation<br>MA interrupt is pending                           | on has completed                   |                                    |  |  |  |  |

| bit 4      | LINKIF: L         | ink Change Interrupt Flag b                                                       | it                                 |                                    |  |  |  |  |

|            |                   | reports that the link status h<br>status has not changed                          | as changed; read PHIR regis        | ter to clear                       |  |  |  |  |

| bit 3      | 1 = Tran          | nsmit Interrupt Flag bit<br>smit request has ended<br>ansmit interrupt is pending |                                    |                                    |  |  |  |  |

| bit 2      | Unimple           | mented: Read as '0'                                                               |                                    |                                    |  |  |  |  |

| bit 1      | TXERIF:           | Transmit Error Interrupt Flag                                                     | ı bit                              |                                    |  |  |  |  |

|            |                   | nsmit error has occurred                                                          |                                    |                                    |  |  |  |  |

|            | 0 = No tr         | ansmit error has occurred                                                         |                                    |                                    |  |  |  |  |

| bit 0      | RXERIF:           | Receive Error Interrupt Flag                                                      | bit                                |                                    |  |  |  |  |

|            | •                 | cket was aborted because the ceive error interrupt is pend                        | •                                  | e, or a buffer overrun has occurre |  |  |  |  |

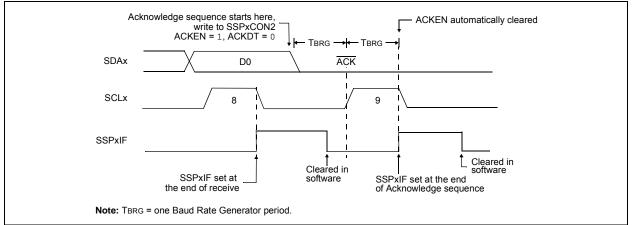

#### 20.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPxCON2<4>). When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 20-25).

#### 20.4.12.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

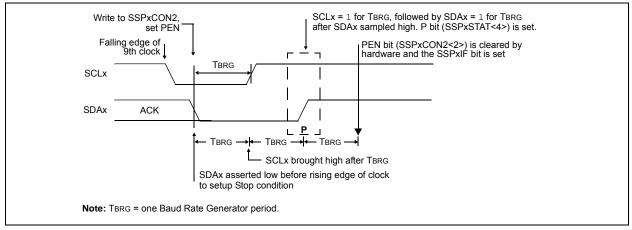

#### 20.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPxCON2<2>). At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit (SSPxSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 20-26).

#### 20.4.13.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 20-25: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 20-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

### 21.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These features make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The 64-pin devices of the PIC18F97J60 family are equipped with one EUSART module, referred to as EUSART1. The 80-pin and 100-pin devices each have two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-Wake-up on Character Reception

- Auto-Baud Calibration

- 12-Bit Break Character Transmission

- Synchronous Master (half-duplex) with Selectable Clock Polarity

- Synchronous Slave (half-duplex) with Selectable Clock Polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1) and PORTG (RG1/TX2/CK2 and RG2/RX2/DT2), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- SPEN bit (RCSTA1<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISG<1> bit must be set (= 1) for Synchronous Slave mode

Note: The EUSARTx control will automatically reconfigure the pin from input to output as needed.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed on the following pages in Register 21-1, Register 21-2 and Register 21-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

|             |                        |            |                             |                    | SYNC  | = 0, BRG1         | 6 = 0, BRG         | 6 <b>H</b> = 0 |                             |                    |            |                             |

|-------------|------------------------|------------|-----------------------------|--------------------|-------|-------------------|--------------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD        | BAUD Fosc = 41.667 MHz |            | Fosc = 31.25 MHz            |                    |       | Fosc = 25.000 MHz |                    |                | Fosc                        | Fosc = 20.833 MHz  |            |                             |

| RATE<br>(K) | Actual<br>Rate (K)     | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | Value |                   | Actual<br>Rate (K) | %<br>Error     | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 0.3         | —                      | _          | _                           | —                  |       |                   | _                  | _              | _                           | _                  |            | _                           |

| 1.2         | _                      | _          | _                           | _                  | _     | _                 | —                  | _              | _                           | 1.271              | 5.96       | 255                         |

| 2.4         | 2.543                  | 5.96       | 255                         | 2.405              | 0.22  | 202               | 2.396              | -0.15          | 162                         | 2.393              | -0.27      | 135                         |

| 9.6         | 9.574                  | -0.27      | 67                          | 9.574              | -0.27 | 50                | 9.527              | -0.76          | 40                          | 9.574              | -0.27      | 33                          |

| 19.2        | 19.148                 | -0.27      | 33                          | 19.531             | 1.73  | 24                | 19.531             | 1.73           | 19                          | 19.147             | -0.27      | 16                          |

| 57.6        | 59.186                 | 2.75       | 10                          | 61.035             | 5.96  | 7                 | 55.804             | -3.12          | 6                           | 54.253             | -5.81      | 5                           |

| 115.2       | 108.508                | -5.81      | 5                           | 122.070            | 5.96  | 3                 | 130.208            | 13.03          | 2                           | 108.505            | -5.81      | 2                           |

|             |                    | SYNC = 0, BRG16 = 0, BRGH = 0 |                             |                    |            |                             |                    |            |                             |  |  |  |  |  |  |

|-------------|--------------------|-------------------------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|--|--|--|--|

| BAUD        | Fosc               | = 13.88                       | 9 MHz                       | Fos                | c = 6.250  | MHz                         | Fos                | c = 4.167  | ' MHz                       |  |  |  |  |  |  |

| RATE<br>(K) | Actual<br>Rate (K) | %<br>Error                    | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |  |  |  |  |

| 0.3         | _                  |                               |                             |                    | _          | _                           | 0.300              | 0.01       | 216                         |  |  |  |  |  |  |

| 1.2         | 1.198              | -0.08                         | 180                         | 1.206              | 0.47       | 80                          | 1.206              | 0.48       | 53                          |  |  |  |  |  |  |

| 2.4         | 2.411              | 0.47                          | 89                          | 2.382              | -0.76      | 40                          | 2.411              | 0.48       | 26                          |  |  |  |  |  |  |

| 9.6         | 9.435              | -1.71                         | 22                          | 9.766              | 1.73       | 9                           | 9.301              | -3.11      | 6                           |  |  |  |  |  |  |

| 19.2        | 19.279             | 2.75                          | 10                          | 19.531             | 1.73       | 4                           | 21.703             | 13.04      | 2                           |  |  |  |  |  |  |

| 57.6        | 54.254             | -5.81                         | 3                           | 48.828             | -15.23     | 1                           | 65.109             | 13.04      | 0                           |  |  |  |  |  |  |

| 115.2       | 108.508            | -5.81                         | 1                           | 97.656             | -15.23     | 0                           | 65.109             | -43.48     | 0                           |  |  |  |  |  |  |

|             |                    |                   |     |                    | SYNC             | = 0, BRG1                   | 6 = 0, BRG         | <b>H</b> = 1      |                             |         |                   |     |  |

|-------------|--------------------|-------------------|-----|--------------------|------------------|-----------------------------|--------------------|-------------------|-----------------------------|---------|-------------------|-----|--|

| BAUD        | Fosc               | Fosc = 41.667 MHz |     |                    | Fosc = 31.25 MHz |                             |                    | Fosc = 25.000 MHz |                             |         | Fosc = 20.833 MHz |     |  |

| RATE<br>(K) | Actual<br>Rate (K) | Value Value       |     | Actual<br>Rate (K) | %<br>Error       | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | %<br>Error        | SPBRG<br>Value<br>(decimal) |         |                   |     |  |

| 0.3         | _                  | _                 |     | _                  |                  |                             |                    | _                 |                             | _       | _                 | _   |  |

| 1.2         | —                  | —                 | —   | —                  | —                | —                           | —                  | —                 | —                           | —       | —                 | —   |  |

| 2.4         | —                  | _                 | _   | _                  | _                | _                           | —                  | _                 | _                           | —       | _                 | _   |  |

| 9.6         | 10.172             | 5.96              | 255 | 9.621              | 0.22             | 202                         | 9.586              | -0.15             | 162                         | 9.573   | -0.27             | 135 |  |

| 19.2        | 19.148             | -0.27             | 135 | 19.148             | -0.27            | 101                         | 19.290             | 0.47              | 80                          | 19.147  | -0.27             | 67  |  |

| 57.6        | 57.871             | 0.47              | 44  | 57.445             | -0.27            | 33                          | 57.870             | 0.47              | 26                          | 56.611  | -1.72             | 22  |  |

| 115.2       | 113.226            | -1.71             | 22  | 114.890            | -0.27            | 16                          | 111.607            | -3.12             | 13                          | 118.369 | 2.75              | 10  |  |

|             |                    | SYNC = 0, BRG16 = 0, BRGH = 1 |                             |                    |           |       |                    |            |                             |  |  |  |  |  |

|-------------|--------------------|-------------------------------|-----------------------------|--------------------|-----------|-------|--------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD        | Fosc               | = 13.88                       | 9 MHz                       | Fos                | c = 6.250 | ) MHz | Foso               | c = 4.167  | ' MHz                       |  |  |  |  |  |

| RATE<br>(K) | Actual<br>Rate (K) | %<br>Error                    | SPBRG<br>Value<br>(decimal) | Actual<br>Rate (K) | Value     |       | Actual<br>Rate (K) | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |  |  |  |

| 0.3         |                    | _                             | _                           | _                  |           | _     |                    | _          | _                           |  |  |  |  |  |

| 1.2         | —                  | —                             | —                           | —                  |           | —     | 1.200              | 0.01       | 216                         |  |  |  |  |  |

| 2.4         | —                  | —                             | —                           | 2.396              | -0.15     | 162   | 2.389              | -0.44      | 108                         |  |  |  |  |  |

| 9.6         | 9.645              | 0.47                          | 89                          | 9.527              | -0.76     | 40    | 9.645              | 0.48       | 26                          |  |  |  |  |  |

| 19.2        | 19.290             | 0.47                          | 44                          | 19.531             | 1.73      | 19    | 18.603             | -3.11      | 13                          |  |  |  |  |  |

| 57.6        | 57.871             | 0.47                          | 14                          | 55.804             | -3.12     | 6     | 52.088             | -9.57      | 4                           |  |  |  |  |  |

| 115.2       | 108.508            | -5.81                         | 7                           | 130.208.           | 13.03     | 2     | 130.219            | 13.04      | 1                           |  |  |  |  |  |

© 2011 Microchip Technology Inc.

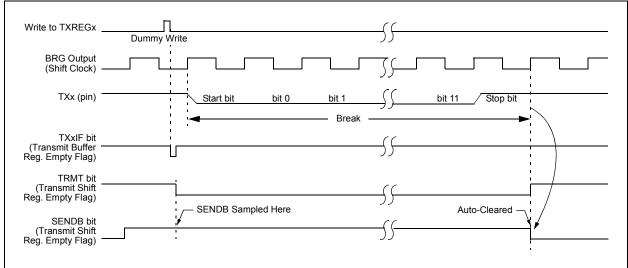

#### 21.2.5 BREAK CHARACTER SEQUENCE

The EUSARTx module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTAx<3> and TXSTAx<5>) are set while the Transmit Shift Register (TSR) is loaded with data. Note that the value of data written to TXREGx will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 support specification).

Note that the data value written to the TXREGx for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 21-10 for the timing of the Break character sequence.

#### 21.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSARTx for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREGx with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREGx to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREGx becomes empty, as indicated by the TXxIF, the next data byte can be written to TXREGx.

#### 21.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USARTx module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit, and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 21.2.4** "**Auto-Wake-up on Sync Break Character**". By enabling this feature, the EUSARTx will sample the next two transitions on RXx/DTx, cause an RCxIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABDEN bit once the TXxIF interrupt is observed.

#### FIGURE 21-10: SEND BREAK CHARACTER SEQUENCE

| R/W-0         | U-0                                                                                                                                                    | R/W-0                                             | R/W-0        | R/W-0                     | R/W-0            | R/W-0           | R/W-0 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------|---------------------------|------------------|-----------------|-------|

| ADFM          |                                                                                                                                                        | ACQT2                                             | ACQT1        | ACQT0                     | ADCS2            | ADCS1           | ADCS0 |

| bit 7         |                                                                                                                                                        |                                                   |              |                           |                  |                 | bit ( |

| Legend:       |                                                                                                                                                        |                                                   |              |                           |                  |                 |       |

| R = Readabl   | e bit                                                                                                                                                  | W = Writable                                      | bit          | U = Unimpler              | nented bit, read | d as '0'        |       |

| -n = Value at | POR                                                                                                                                                    | '1' = Bit is set                                  |              | '0' = Bit is cle          | ared             | x = Bit is unkr | nown  |

| bit 7         | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifie                                                                                             | fied                                              | Select bit   |                           |                  |                 |       |

| bit 6         | Unimplement                                                                                                                                            | t <b>ed:</b> Read as '                            | 0'           |                           |                  |                 |       |

| bit 5-3       | ACQT<2:0>: .<br>111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD<br>000 = 0 TAD <sup>(1)</sup> |                                                   |              |                           |                  |                 |       |

| bit 2-0       | ADCS<2:0>: /<br>111 = FRC (cl<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4<br>011 = FRC (cl<br>010 = Fosc/3<br>001 = Fosc/8<br>000 = Fosc/2         | ock derived fro<br>4<br>6<br>ock derived fro<br>2 | om A/D RC os | scillator) <sup>(1)</sup> |                  |                 |       |

#### REGISTER 22-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

#### TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit:                                                                                                                             |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                 |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                         |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                              |

| d               | Destination select bit:                                                                                                                     |

|                 | d = 0: store result in WREG                                                                                                                 |

| -               | d = 1: store result in file register f                                                                                                      |

| dest            | Destination: either the WREG register or the specified register file location.                                                              |

| f               | 8-bit Register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                               |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                    |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                               |

| GIE             | Global Interrupt Enable bit.                                                                                                                |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                   |

| label           | Label name.                                                                                                                                 |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions: |

| *               | No Change to register (such as TBLPTR with table reads and writes)                                                                          |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                        |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                        |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                         |

|                 | The relative address (2's complement number) for relative branch instructions or the direct address for                                     |

| n               | Call/Branch and Return instructions.                                                                                                        |

| PC              | Program Counter.                                                                                                                            |

| PCL             | Program Counter Low Byte.                                                                                                                   |

| PCH             | Program Counter High Byte.                                                                                                                  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                            |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                           |

| PD              | Power-Down bit.                                                                                                                             |

| PRODH           | Product of Multiply High Byte.                                                                                                              |

| PRODL           | Product of Multiply Low Byte.                                                                                                               |

| s               | Fast Call/Return mode select bit:                                                                                                           |

| 5               | s = 0: do not update into/from shadow registers                                                                                             |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                      |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                 |

| TABLAT          | 8-bit Table Latch.                                                                                                                          |

| TO              | Time-out bit.                                                                                                                               |

| TOS             | Top-of-Stack.                                                                                                                               |

| u               | Unused or Unchanged.                                                                                                                        |

| WDT             | Watchdog Timer.                                                                                                                             |

| WREG            | Working register (accumulator).                                                                                                             |

| х               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                              |

|                 | compatibility with all Microchip software tools.                                                                                            |

| Zs              | 7-bit offset value for indirect addressing of register files (source).                                                                      |

| zd              | 7-bit offset value for indirect addressing of register files (destination).                                                                 |

| { }             | Optional argument.                                                                                                                          |

| [text]          | Indicates an indexed address.                                                                                                               |

| (text)          | The contents of text.                                                                                                                       |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                              |

| $\rightarrow$   | Assigned to.                                                                                                                                |

| < >             | Register bit field.                                                                                                                         |

| E               | In the set of.                                                                                                                              |

| italics         | User-defined term (font is Courier New).                                                                                                    |

| BNC                                                 | Branch if N                               | lot Carry                                             |                                       | BNN                     | Branch                                        | if Not Negati                                                                                         | ve                              |                        |

|-----------------------------------------------------|-------------------------------------------|-------------------------------------------------------|---------------------------------------|-------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|

| Syntax:                                             | BNC n                                     |                                                       |                                       | Syntax:                 | BNN n                                         |                                                                                                       |                                 |                        |

| Operands:                                           | -128 ≤ n ≤ ′                              | 127                                                   |                                       | Operands:               | -128 ≤ n                                      | ≤ 127                                                                                                 |                                 |                        |

| Operation:                                          | if Carry bit i<br>(PC) + 2 + 2            | ,                                                     |                                       | Operation:              | 0                                             | ve bit is '0',<br>+ 2n $\rightarrow$ PC                                                               |                                 |                        |

| Status Affected:                                    | None                                      |                                                       |                                       | Status Affecte          | ed: None                                      |                                                                                                       |                                 |                        |

| Encoding:                                           | 1110                                      | 0011 nn                                               | nn nnnn                               | Encoding:               | 1110                                          | 0111                                                                                                  | nnnn                            | nnnn                   |

| Description:                                        | If the Carry will branch.                 | bit is '0', then                                      | the program                           | Description:            |                                               | gative bit is 'o<br>will branch.                                                                      | )', then t                      | the                    |

|                                                     | added to th<br>incremente<br>instruction, | d to fetch the i<br>the new addre<br>n. This instruct | e PC will have<br>next<br>ess will be |                         | added to<br>increme<br>instructio<br>PC + 2 + | complement r<br>the PC. Sinc<br>nted to fetch f<br>on, the new a<br>- 2n. This inst<br>e instruction. | e the PC<br>he next<br>ddress v | C will have<br>will be |

| Words:                                              | 1                                         |                                                       |                                       | Words:                  | 1                                             |                                                                                                       |                                 |                        |

| Cycles:                                             | 1(2)                                      |                                                       |                                       | Cycles:                 | 1(2)                                          |                                                                                                       |                                 |                        |

| Q Cycle Activity:<br>If Jump:                       |                                           |                                                       |                                       | Q Cycle Act<br>If Jump: | vity:                                         |                                                                                                       |                                 |                        |

| Q1                                                  | Q2                                        | Q3                                                    | Q4                                    | Q^                      | Q2                                            | Q3                                                                                                    |                                 | Q4                     |

| Decode                                              | Read literal<br>'n'                       | Process<br>Data                                       | Write to<br>PC                        | Deco                    | de Read liter<br>'n'                          | al Process<br>Data                                                                                    | s V                             | Vrite to<br>PC         |

| No                                                  | No                                        | No                                                    | No                                    | No                      | No                                            | No                                                                                                    |                                 | No                     |

| operation                                           | operation                                 | operation                                             | operation                             | opera                   | ion operation                                 | operatio                                                                                              | n o                             | peration               |

| If No Jump:                                         |                                           |                                                       | <b>.</b>                              | If No Jump:             |                                               |                                                                                                       |                                 |                        |

| Q1                                                  | Q2                                        | Q3                                                    | Q4                                    | Q'                      |                                               | Q3                                                                                                    |                                 | Q4<br>No               |

| Decode                                              | Read literal<br>'n'                       | Process<br>Data                                       | No<br>operation                       | Deco                    | de Read liter<br>'n'                          | al Process<br>Data                                                                                    | -                               | peration               |

| Example:                                            | HERE                                      | BNC Jump                                              |                                       | Example:                | HERE                                          | BNN J1                                                                                                | ump                             |                        |

| Before Instruc<br>PC<br>After Instructi<br>If Carry | = ad<br>on<br>= 0;                        | dress (HERE                                           |                                       | PC<br>After Ins         | truction<br>legative =                        | address (HE                                                                                           |                                 |                        |

| PC<br>If Carry<br>PC                                | = 1;                                      | dress (Jump<br>dress (HERE                            |                                       | lf N                    | PC =<br>legative =<br>PC =                    | address (Ju<br>1;<br>address (HI                                                                      | -                               | 2)                     |

Move W to f MOVWF f {,a}

MOVWF

Syntax:

| MOV          | LW             | Move Literal to W   |                                             |      |               |  |  |

|--------------|----------------|---------------------|---------------------------------------------|------|---------------|--|--|

| Synta        | ax:            | MOVLW               | k                                           |      |               |  |  |

| Oper         | ands:          | $0 \le k \le 25$    | 5                                           |      |               |  |  |

| Oper         | ation:         | $k\toW$             |                                             |      |               |  |  |

| Statu        | s Affected:    | None                |                                             |      |               |  |  |

| Enco         | ding:          | 0000                | 1110                                        | kkkk | kkkk          |  |  |

| Description: |                | The eight-          | The eight-bit literal 'k' is loaded into W. |      |               |  |  |

| Word         | ls:            | 1                   |                                             |      |               |  |  |

| Cycle        | es:            | 1                   |                                             |      |               |  |  |

| QC           | ycle Activity: |                     |                                             |      |               |  |  |

|              | Q1             | Q2                  | Q3                                          | 5    | Q4            |  |  |

|              | Decode         | Read<br>literal 'k' | Proce<br>Data                               |      | Write to<br>W |  |  |

|              |                |                     |                                             |      |               |  |  |

| Exan         | nple:          | MOVLW               | 5Ah                                         |      |               |  |  |

After Instruction W

=

5Ah

| Operands:         | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                             | 5     |      |            |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------------|--|

| Operation:        | $(W) \to f$                                                                                                                                                                                                                                                                          |       |      |            |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                 |       |      |            |  |

| Encoding:         | 0110                                                                                                                                                                                                                                                                                 | 111a  | ffff | ffff       |  |

| Description:      | Move data from W to register 'f'.<br>Location 'f' can be anywhere in the<br>256-byte bank.                                                                                                                                                                                           |       |      |            |  |

|                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                                                                                                                                   |       |      |            |  |

|                   | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |       |      |            |  |

| Words:            | 1                                                                                                                                                                                                                                                                                    |       |      |            |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                    |       |      |            |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                      |       |      |            |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                   | Q3    |      | Q4         |  |

| Decode            | Read                                                                                                                                                                                                                                                                                 | Proce |      | Write      |  |

|                   | register 'f'                                                                                                                                                                                                                                                                         | Data  | a re | gister 'f' |  |

| Example:          | Example: MOVWF REG, 0                                                                                                                                                                                                                                                                |       |      |            |  |

| Before Instruct   |                                                                                                                                                                                                                                                                                      |       |      |            |  |

| W<br>REG          | = 4Fh<br>= FFh                                                                                                                                                                                                                                                                       |       |      |            |  |

| NEO I             |                                                                                                                                                                                                                                                                                      |       |      |            |  |

4Fh 4Fh

= =

After Instruction W REG

TBLRD \*+ ;

Table Read (Continued)

| TBL   | RD                                                                                                                                                                                                                                                                                                  | Table Read                                                                                                                                                                                                                                                                                                                                                                        |        |            |       |                                               |                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-------|-----------------------------------------------|-------------------------------------------|

| Synta | ax:                                                                                                                                                                                                                                                                                                 | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                      | '+; *· | -; +*)     |       |                                               |                                           |

| Oper  | ands:                                                                                                                                                                                                                                                                                               | None                                                                                                                                                                                                                                                                                                                                                                              |        |            |       |                                               |                                           |

| Oper  | ation:                                                                                                                                                                                                                                                                                              | if TBLRD*,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>TBLPTR – No Change<br>if TBLRD*+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR<br>if TBLRD*-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT |        |            |       |                                               |                                           |

| Statu | s Affected:                                                                                                                                                                                                                                                                                         | None                                                                                                                                                                                                                                                                                                                                                                              |        |            |       |                                               |                                           |

| Enco  | ding:                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                              | 00     | 000        | 000   | 00                                            | 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |