Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 41.667MHz                                                                  |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 55                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3808 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 15x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j60-i-pt |

### 64/80/100-Pin High-Performance, 1-Mbit Flash Microcontrollers with Ethernet

#### **Ethernet Features:**

- IEEE 802.3™ Compatible Ethernet Controller

- Fully Compatible with 10/100/1000Base-T Networks

- · Integrated MAC and 10Base-T PHY

- · 8-Kbyte Transmit/Receive Packet Buffer SRAM

- · Supports One 10Base-T Port

- · Programmable Automatic Retransmit on Collision

- · Programmable Padding and CRC Generation

- Programmable Automatic Rejection of Erroneous Packets

- · Activity Outputs for 2 LED Indicators

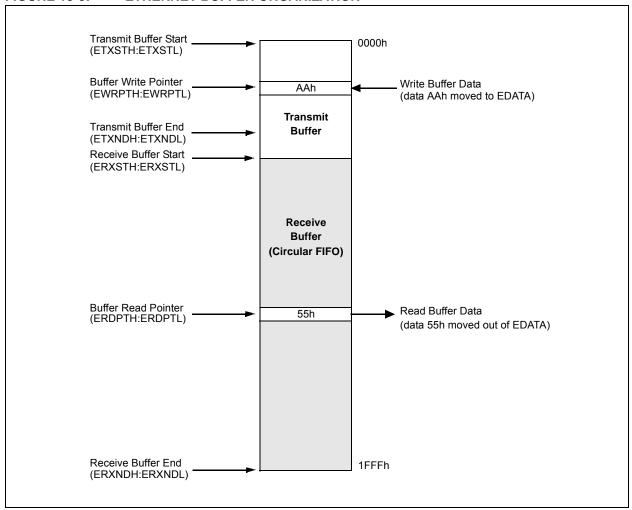

- Buffer:

- Configurable transmit/receive buffer size

- Hardware-managed circular receive FIFO

- Byte-wide random and sequential access

- Internal DMA for fast memory copying

- Hardware assisted checksum calculation for various protocols

- MAC:

- Support for Unicast, Multicast and Broadcast packets

- Programmable Pattern Match of up to 64 bytes within packet at user-defined offset

- Programmable wake-up on multiple packet formats

- PHY:

- Wave shaping output filter

#### Flexible Oscillator Structure:

- Selectable System Clock derived from Single 25 MHz External Source:

- 2.778 to 41.667 MHz

- Internal 31 kHz Oscillator

- Secondary Oscillator using Timer1 @ 32 kHz

- · Fail-Safe Clock Monitor:

- Allows for safe shutdown if oscillator stops

- · Two-Speed Oscillator Start-up

# External Memory Bus (100-pin devices only):

- · Address Capability of up to 2 Mbytes

- · 8-Bit or 16-Bit Interface

- · 12-Bit, 16-Bit and 20-Bit Addressing modes

#### **Peripheral Highlights:**

- High-Current Sink/Source: 25 mA/25 mA on PORTB and PORTC

- Five Timer modules (Timer0 to Timer4)

- · Four External Interrupt pins

- · Two Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Up to Two Master Synchronous Serial Port (MSSP) modules supporting SPI (all 4 modes) and I<sup>2</sup>C™ Master and Slave modes

- · Up to Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect (ABD)

- 10-Bit, Up to 16-Channel Analog-to-Digital Converter module (A/D):

- Auto-acquisition capability

- Conversion available during Sleep

- · Dual Analog Comparators with Input Multiplexing

- Parallel Slave Port (PSP) module (100-pin devices only)

#### **Special Microcontroller Features:**

- 5.5V Tolerant Inputs (digital-only pins)

- Low-Power, High-Speed CMOS Flash Technology:

- Self-reprogrammable under software control

- · C compiler Optimized Architecture for Reentrant Code

- Power Management Features:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 134s

- Single-Supply 3.3V In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) with 3 Breakpoints via Two Pins

- Operating Voltage Range of 2.35V to 3.6V (3.1V to 3.6V using Ethernet module)

- · On-Chip 2.5V Regulator

TABLE 1-4: PIC18F66J60/66J65/67J60 PINOUT I/O DESCRIPTIONS (CONTINUED)

| D' Maria      | Pin Number | Pin  | Buffer | B                                                                                                             |

|---------------|------------|------|--------|---------------------------------------------------------------------------------------------------------------|

| Pin Name      | TQFP       | Type | Type   | Description                                                                                                   |

|               |            |      |        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0/FLT0 | 3          |      |        |                                                                                                               |

| RB0           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| INTO          |            | I    | ST     | External Interrupt 0.                                                                                         |

| FLT0          |            | I    | ST     | Enhanced PWM Fault input (ECCP modules); enabled in software.                                                 |

| RB1/INT1      | 4          |      |        |                                                                                                               |

| RB1           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| INT1          |            | I    | ST     | External Interrupt 1.                                                                                         |

| RB2/INT2      | 5          |      |        |                                                                                                               |

| RB2           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| INT2          |            | - 1  | ST     | External Interrupt 2.                                                                                         |

| RB3/INT3      | 6          |      |        |                                                                                                               |

| RB3           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| INT3          |            | - 1  | ST     | External Interrupt 3.                                                                                         |

| RB4/KBI0      | 44         |      |        |                                                                                                               |

| RB4           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| KBI0          |            | - 1  | TTL    | Interrupt-on-change pin.                                                                                      |

| RB5/KBI1      | 43         |      |        |                                                                                                               |

| RB5           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| KBI1          |            | - 1  | TTL    | Interrupt-on-change pin.                                                                                      |

| RB6/KBI2/PGC  | 42         |      |        |                                                                                                               |

| RB6           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| KBI2          |            | I    | TTL    | Interrupt-on-change pin.                                                                                      |

| PGC           |            | I/O  | ST     | In-Circuit Debugger and ICSP™ programming clock pin.                                                          |

| RB7/KBI3/PGD  | 37         |      |        |                                                                                                               |

| RB7           |            | I/O  | TTL    | Digital I/O.                                                                                                  |

| KBI3          |            | I    | TTL    | Interrupt-on-change pin.                                                                                      |

| PGD           |            | I/O  | ST     | In-Circuit Debugger and ICSP programming data pin.                                                            |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

OD = Open-Drain (no P diode to VDD)

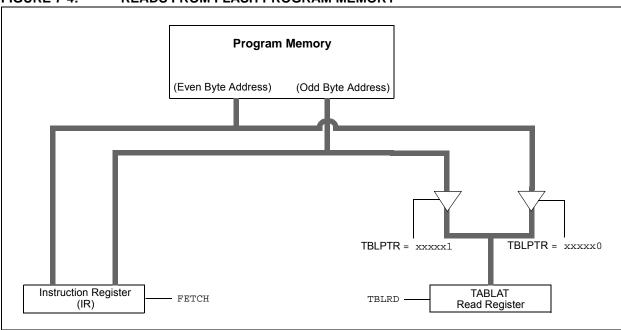

# 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

```

MOVLW

CODE_ADDR_UPPER

; Load TBLPTR with the base

; address of the word

MOVWF

TBLPTRU

MOVLW CODE_ADDR_HIGH

MOVWF

TBLPTRH

MOVLW CODE_ADDR_LOW

MOVWF TBLPTRL

READ_WORD

; read into TABLAT and increment

TBLRD*+

MOVF

TABLAT, W

; get data

MOVWF

WORD_EVEN

TBLRD*+

; read into TABLAT and increment

MOVFW TABLAT, W

; get data

MOVF

WORD_ODD

```

#### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 10-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PSPIP <sup>(1)</sup> | ADIP  | RC1IP | TX1IP | SSP1IP | CCP1IP | TMR2IP | TMR1IP |

| bit 7                |       |       |       |        |        |        | bit 0  |

| Legend:           |                                  |                               |                                          |                    |

|-------------------|----------------------------------|-------------------------------|------------------------------------------|--------------------|

| R = Readable bit  |                                  | W = Writable bit              | U = Unimplemented bit,                   | read as '0'        |

| -n = Value at POR |                                  | '1' = Bit is set              | '0' = Bit is cleared                     | x = Bit is unknown |

| bit 7             | <b>PSPIP:</b> F 1 = High 0 = Low |                               | te Interrupt Priority bit <sup>(1)</sup> |                    |

| bit 6             | ADIP: A/                         | D Converter Interrupt Priorit | y bit                                    |                    |

bit 5 RC1IP: EUSART1 Receive Interrupt Priority bit

1 = High priority0 = Low priority

1 = High priority0 = Low priority

bit 4 **TX1IP:** EUSART1 Transmit Interrupt Priority bit

1 = High priority0 = Low priority

bit 3 SSP1IP: MSSP1 Interrupt Priority bit

1 = High priority0 = Low priority

bit 2 CCP1IP: ECCP1 Interrupt Priority bit

1 = High priority0 = Low priority

bit 1 TMR2IP: TMR2 to PR2 Match Interrupt Priority bit

1 = High priority0 = Low priority

bit 0 TMR1IP: TMR1 Overflow Interrupt Priority bit

1 = High priority0 = Low priority

Note 1: Implemented in 100-pin devices in Microcontroller mode only.

TABLE 11-7: PORTC FUNCTIONS

| Pin Name    | Function             | TRIS<br>Setting | I/O | I/O<br>Type    | Description                                                                                                                               |

|-------------|----------------------|-----------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/  | RC0                  | 0               | 0   | DIG            | LATC<0> data output.                                                                                                                      |

| T13CKI      |                      | 1               | I   | ST             | PORTC<0> data input.                                                                                                                      |

|             | T10S0                | х               | 0   | ANA            | Timer1 oscillator output; enabled when Timer1 oscillator is enabled. Disables digital I/O.                                                |

|             | T13CKI               | 1               | I   | ST             | Timer1/Timer3 counter input.                                                                                                              |

| RC1/T1OSI/  | RC1                  | 0               | 0   | DIG            | LATC<1> data output.                                                                                                                      |

| ECCP2/P2A   |                      | 1               |     | ST             | PORTC<1> data input.                                                                                                                      |

|             | T10SI                | х               | -   | ANA            | Timer1 oscillator input; enabled when Timer1 oscillator is enabled. Disables digital I/O.                                                 |

|             | ECCP2 <sup>(1)</sup> | 0               | 0   | DIG            | ECCP2 compare output and PWM output; takes priority over port data.                                                                       |

|             |                      | 1               | ı   | ST             | ECCP2 capture input.                                                                                                                      |

|             | P2A <sup>(1)</sup>   | 0               | 0   | DIG            | ECCP2 Enhanced PWM output, Channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RC2/ECCP1/  | RC2                  | 0               | 0   | DIG            | LATC<2> data output.                                                                                                                      |

| P1A         |                      | 1               | I   | ST             | PORTC<2> data input.                                                                                                                      |

|             | ECCP1                | 0               | 0   | DIG            | ECCP1 compare output and PWM output; takes priority over port data.                                                                       |

|             |                      | 1               | I   | ST             | ECCP1 capture input.                                                                                                                      |

|             | P1A                  | 0               | 0   | DIG            | ECCP1 Enhanced PWM output, Channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RC3/SCK1/   | RC3                  | 0               | 0   | DIG            | LATC<3> data output.                                                                                                                      |

| SCL1        |                      | 1               |     | ST             | PORTC<3> data input.                                                                                                                      |

|             | SCK1                 | 0               | 0   | DIG            | SPI clock output (MSSP1 module); takes priority over port data.                                                                           |

|             |                      | 1               |     | ST             | SPI clock input (MSSP1 module).                                                                                                           |

|             | SCL1                 | <u> </u>        |     | DIG            | I <sup>2</sup> C™ clock output (MSSP1 module); takes priority over port data.                                                             |

|             |                      | 1               | I   | ST             | I <sup>2</sup> C clock input (MSSP1 module); input type depends on module setting.                                                        |

| RC4/SDI1/   | RC4                  | 0               | 0   | DIG            | LATC<4> data output.                                                                                                                      |

| SDA1        |                      | 1               |     | ST             | PORTC<4> data input.                                                                                                                      |

|             | SDI1                 | 1               | I   | ST             | SPI data input (MSSP1 module).                                                                                                            |

|             | SDA1                 | 1               | 0   | DIG            | I <sup>2</sup> C data output (MSSP1 module); takes priority over port data.                                                               |

|             |                      | 1               |     | ST             | I <sup>2</sup> C data input (MSSP1 module); input type depends on module setting.                                                         |

| RC5/SDO1    | RC5                  | 0               | 0   | DIG            | LATC<5> data output.                                                                                                                      |

|             |                      | 1               | I   | ST             | PORTC<5> data input.                                                                                                                      |

|             | SDO1                 | 0               | 0   | DIG            | SPI data output (MSSP1 module); takes priority over port data.                                                                            |

| RC6/TX1/CK1 | RC6                  | 0               | 0   | DIG            | LATC<6> data output.                                                                                                                      |

|             |                      | 1               | I   | ST             | PORTC<6> data input.                                                                                                                      |

|             | TX1                  | 1               | 0   | DIG            | Synchronous serial data output (EUSART1 module); takes priority over port data.                                                           |

|             | CK1                  | 1               | 0   | DIG            | Synchronous serial data input (EUSART1 module). User must configure as an input.                                                          |

|             |                      | 1               |     | ST             | Synchronous serial clock input (EUSART1 module).                                                                                          |

| RC7/RX1/DT1 | RC7                  | 0               | 0   | DIG            | LATC<7> data output.                                                                                                                      |

|             |                      | 1               | I   | ST             | PORTC<7> data input.                                                                                                                      |

|             | RX1                  | 1               | I   | ST             | Asynchronous serial receive data input (EUSART1 module).                                                                                  |

|             | DT1                  | 1               | 0   | DIG            | Synchronous serial data output (EUSART1 module); takes priority over port data.                                                           |

|             |                      | 1               | I   | ST<br>log Sign | Synchronous serial data input (EUSART1 module). User must configure as an input.                                                          |

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input,

$\mathbf{x}$  = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for ECCP2/P2A when CCP2MX Configuration bit is set.

**TABLE 11-19: PORTJ FUNCTIONS**

| Pin Name                         | Function           | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                     |

|----------------------------------|--------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------|

| RJ0/ALE <sup>(1)</sup>           | RJ0 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<0> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<0> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | ALE <sup>(1)</sup> | х               | 0   | DIG         | External memory interface address latch enable control output; takes priority over digital I/O. |

| RJ1/ <del>OE<sup>(1)</sup></del> | RJ1 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<1> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<1> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | OE <sup>(1)</sup>  | х               | 0   | DIG         | External memory interface output enable control output; takes priority over digital I/O.        |

| RJ2/WRL <sup>(1)</sup>           | RJ2 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<2> data output.                                                                            |

|                                  | 1                  |                 | I   | ST          | PORTJ<2> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | WRL <sup>(1)</sup> | х               | 0   | DIG         | External memory bus write low byte control; takes priority over digital I/O.                    |

| RJ3/WRH <sup>(1)</sup>           | RJ3 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<3> data output.                                                                            |

|                                  |                    | 1               | ı   | ST          | PORTJ<3> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | WRH <sup>(1)</sup> | х               | 0   | DIG         | External memory interface write high byte control output; takes priority over digital I/O.      |

| RJ4/BA0                          | RJ4                | 0               | 0   | DIG         | LATJ<4> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<4> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | BA0 <sup>(2)</sup> | х               | 0   | DIG         | External Memory Interface Byte Address 0 control output; takes priority over digital I/O.       |

| RJ5/CE                           | RJ5                | 0               | 0   | DIG         | LATJ<5> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<5> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | CE <sup>(2)</sup>  | х               | 0   | DIG         | External memory interface chip enable control output; takes priority over digital I/O.          |

| RJ6/LB <sup>(1)</sup>            | RJ6 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<6> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<6> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | LB <sup>(1)</sup>  | х               | 0   | DIG         | External memory interface lower byte enable control output; takes priority over digital I/O.    |

| RJ7/ <del>UB<sup>(1)</sup></del> | RJ7 <sup>(1)</sup> | 0               | 0   | DIG         | LATJ<7> data output.                                                                            |

|                                  |                    | 1               | I   | ST          | PORTJ<7> data input; weak pull-up when RJPU bit is set.                                         |

|                                  | UB <sup>(1)</sup>  | х               | 0   | DIG         | External memory interface upper byte enable control output; takes priority over digital I/O.    |

**Legend:** O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Implemented on 100-pin devices only.

2: EMB functions are implemented on 100-pin devices only.

#### TABLE 11-20: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | Reset<br>Values<br>on Page: |

|-------|-----------------------|-----------------------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------------|

| PORTJ | RJ7 <sup>(1)</sup>    | RJ6 <sup>(1)</sup>    | RJ5    | RJ4    | RJ3 <sup>(1)</sup>    | RJ2 <sup>(1)</sup>    | RJ1 <sup>(1)</sup>    | RJ0 <sup>(1)</sup>    | 72                          |

| LATJ  | LATJ7 <sup>(1)</sup>  | LATJ6 <sup>(1)</sup>  | LATJ5  | LATJ4  | LATJ3 <sup>(1)</sup>  | LATJ2 <sup>(1)</sup>  | LATJ1 <sup>(1)</sup>  | LATJ0 <sup>(1)</sup>  | 71                          |

| TRISJ | TRISJ7 <sup>(1)</sup> | TRISJ6 <sup>(1)</sup> | TRISJ5 | TRISJ4 | TRISJ3 <sup>(1)</sup> | TRISJ2 <sup>(1)</sup> | TRISJ1 <sup>(1)</sup> | TRISJ0 <sup>(1)</sup> | 71                          |

| PORTA | RJPU                  | _                     | RA5    | RA4    | RA3                   | RA2                   | RA1                   | RA0                   | 72                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTJ.

Note 1: Implemented on 100-pin devices only.

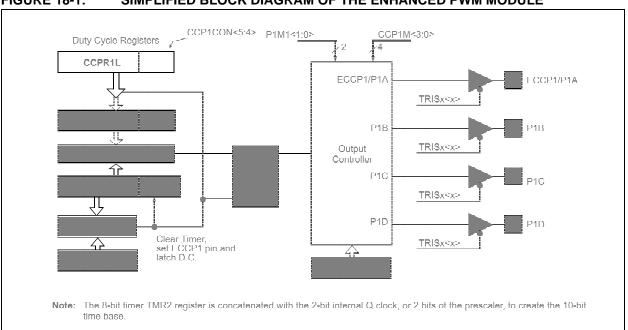

#### 18.4 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is a backward compatible version of the standard CCPx modules and offers up to four outputs, designated PxA through PxD. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the PxM<1:0> and CCPxM<3:0> bits of the CCPxCON register (CCPxCON<7:6> and <3:0>, respectively).

For the sake of clarity, Enhanced PWM mode operation is described generically throughout this section with respect to ECCP1 and TMR2 modules. Control register names are presented in terms of ECCP1. All three Enhanced modules, as well as the two timer resources, can be used interchangeably and function identically. TMR2 or TMR4 can be selected for PWM operation by selecting the proper bits in T3CON.

Figure 18-1 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the ECCP1 Dead-Band Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the boundary period (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that

Enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead, offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRIS bits for output.

#### 18.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation:

#### **EQUATION 18-1:**

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The ECCP1 pin is set (if PWM duty cycle = 0%, the ECCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

Note:

The Timer2 postscaler (see Section 14.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

FIGURE 18-1: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

FIGURE 19-5: ETHERNET BUFFER ORGANIZATION

#### REGISTER 20-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C™ MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       | •     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7 WCOL: Write Collision Detect bit

#### In Master Transmit mode:

- 1 = A write to the SSPxBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

#### In Slave Transmit mode:

- 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

#### In Receive mode (Master or Slave modes):

This is a "don't care" bit.

#### bit 6 SSPOV: Receive Overflow Indicator bit

#### In Receive mode:

- 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

#### In Transmit mode:

This is a "don't care" bit in Transmit mode.

- bit 5 SSPEN: Master Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins<sup>(1)</sup>

- 0 = Disables serial port and configures these pins as I/O port pins (1)

- bit 4 **CKP:** SCKx Release Control bit

#### In Slave mode:

- 1 = Releases clock

- 0 = Holds clock low (clock stretch); used to ensure data setup time

#### In Master mode:

Unused in this mode.

- bit 3-0 SSPM<3:0>: Master Synchronous Serial Port Mode Select bits

- 1111 = I<sup>2</sup>C Slave mode, 10-bit addressing with Start and Stop bit interrupts enabled<sup>(2)</sup>

- 1110 = I<sup>2</sup>C Slave mode, 7-bit addressing with Start and Stop bit interrupts enabled<sup>(2)</sup>

- 1011 =  $I^2C$  Firmware Controlled Master mode (slave Idle)<sup>(2)</sup>

- 1000 =  $I^2$ C Master mode, Clock = Fosc/ $(4 * (SSPADD + 1))^{(2)}$

- $0111 = I^2C$  Slave mode, 10-bit addressing<sup>(2)</sup>

- $0110 = I^2C$  Slave mode, 7-bit addressing<sup>(2)</sup>

- Note 1: When enabled, the SDAx and SCLx pins must be configured as inputs.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

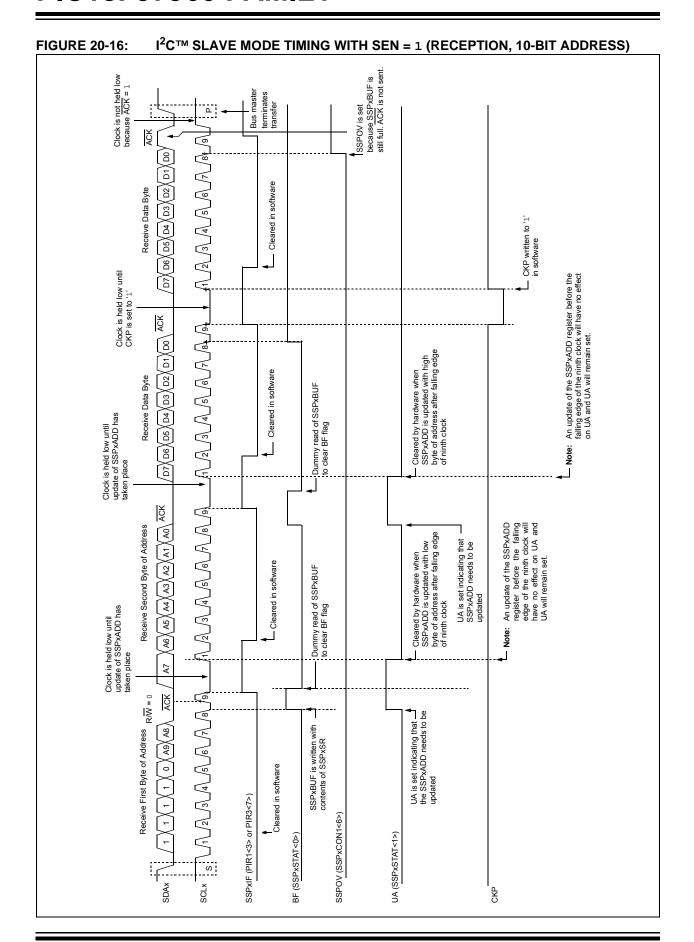

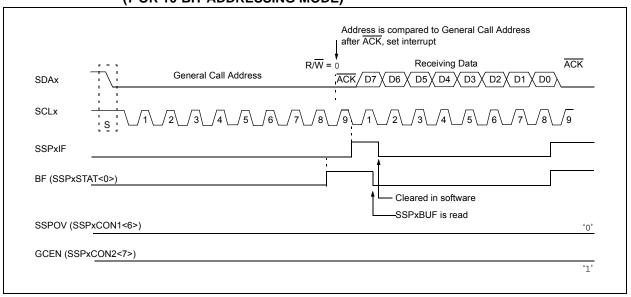

### 20.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPxCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPxSR and the address is compared against the SSPxADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPxSR is transferred to the SSPxBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPxIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPxBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-Bit Addressing mode, the SSPxADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPxSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 20-17).

FIGURE 20-17: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT ADDRESSING MODE)

#### REGISTER 21-1: TXSTAX: TRANSMIT STATUS AND CONTROL REGISTER X

| R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|---------------------|-------|-------|-------|------|-------|

| CSRC  | TX9   | TXEN <sup>(1)</sup> | SYNC  | SENDB | BRGH  | TRMT | TX9D  |

| bit 7 |       |                     |       |       |       |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care.

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 **TX9:** 9-Bit Transmit Enable bit

1 = Selects 9-bit transmission0 = Selects 8-bit transmission

bit 5 **TXEN:** Transmit Enable bit<sup>(1)</sup>

1 = Transmit is enabled0 = Transmit is disabled

bit 4 SYNC: EUSARTx Mode Select bit

1 = Synchronous mode0 = Asynchronous mode

bit 3 **SENDB:** Send Break Character bit

Asynchronous mode:

1 = Send Sync Break on next transmission (cleared by hardware upon completion)

0 = Sync Break transmission is completed

Synchronous mode:

Don't care.

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode.

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR is empty 0 = TSR is full

bit 0 **TX9D:** 9th bit of Transmit Data

Can be address/data bit or a parity bit.

Note 1: SREN/CREN overrides TXEN in Sync mode.

## 21.4 EUSARTx Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 21.4.1 EUSARTX SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If the signal from the CKx pin is to be inverted, set the TXCKP bit. If the signal from the DTx pin is to be inverted, set the RXDTP bit.

- 4. If interrupts are desired, set enable bit, TXxIE.

- 5. If 9-bit transmission is desired, set bit, TX9.

- Enable the transmission by setting enable bit, TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 8. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

TABLE 21-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4                | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------|-------------|-------------|----------------------|--------|--------|--------|--------|-----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE               | RBIE   | TMR0IF | INT0IF | RBIF   | 69                          |

| PIR1     | PSPIF    | ADIF        | RC1IF       | TX1IF                | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 71                          |

| PIE1     | PSPIE    | ADIE        | RC1IE       | TX1IE                | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 71                          |

| IPR1     | PSPIP    | ADIP        | RC1IP       | TX1IP                | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 71                          |

| PIR3     | SSP2IF   | BCL2IF      | RC2IF       | TX2IF <sup>(1)</sup> | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 71                          |

| PIE3     | SSP2IE   | BCL2IE      | RC2IE       | TX2IE <sup>(1)</sup> | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 71                          |

| IPR3     | SSP2IP   | BCL2IP      | RC2IP       | TX2IP <sup>(1)</sup> | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 71                          |

| RCSTAx   | SPEN     | RX9         | SREN        | CREN                 | ADDEN  | FERR   | OERR   | RX9D   | 71                          |

| TXREGx   | EUSARTx  | Transmit Re | gister      |                      |        |        |        |        | 71                          |

| TXSTAx   | CSRC     | TX9         | TXEN        | SYNC                 | SENDB  | BRGH   | TRMT   | TX9D   | 71                          |

| BAUDCONx | ABDOVF   | RCIDL       | RXDTP       | TXCKP                | BRG16  | _      | WUE    | ABDEN  | 72                          |

| SPBRGHx  | EUSARTx  | Baud Rate G | Senerator R | egister High         | n Byte |        |        |        | 72                          |

| SPBRGx   | EUSARTx  | Baud Rate G | Senerator R | egister Low          | Byte   |        |        |        | 72                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These bits are only available in 80-pin and 100-pin devices; otherwise, they are unimplemented and read as '0'.

#### REGISTER 25-7: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F97J60 FAMILY DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Read-only bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-5 **DEV<2:0>:** Device ID bits

See Register 25-8 for a complete listing.

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to indicate the device revision.

#### REGISTER 25-8: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F97J60 FAMILY DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Read-only bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

#### bit 7-0 **DEV<10:3>:** Device ID bits:

| DEV<10:3><br>(DEVID2<7:0>) | DEV<2:0><br>(DEVID1<7:5>) | Device      |

|----------------------------|---------------------------|-------------|

| 0001 1000                  | 000                       | PIC18F66J60 |

| 0001 1111                  | 000                       | PIC18F66J65 |

| 0001 1111                  | 001                       | PIC18F67J60 |

| 0001 1000                  | 001                       | PIC18F86J60 |

| 0001 1111                  | 010                       | PIC18F86J65 |

| 0001 1111                  | 011                       | PIC18F87J60 |

| 0001 1000                  | 010                       | PIC18F96J60 |

| 0001 1111                  | 100                       | PIC18F96J65 |

| 0001 1111                  | 101                       | PIC18F97J60 |

BRA Unconditional Branch

Syntax: BRA n

Operands:  $-1024 \le n \le 1023$ Operation:  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 Onnn nnnn nnnn

Description: Add the 2's complement number '2n' to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a

two-cycle instruction.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

Example: HERE BRA Jump

Before Instruction

PC = address (HERE)

After Instruction

PC = address (Jump)

| BSF              | Bit Set f                                             |  |  |

|------------------|-------------------------------------------------------|--|--|

| Syntax:          | BSF f, b {,a}                                         |  |  |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |  |  |

| Operation:       | $1 \rightarrow f < b >$                               |  |  |

| Status Affected: | None                                                  |  |  |

| Encoding:        | 1000 bbba ffff ffff                                   |  |  |

| Description:     | Bit 'b' in register 'f' is set.                       |  |  |

|                  | If 'a' is '0' the Access Bank is selected             |  |  |

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BSF FLAG\_REG, 7, 1

Before Instruction

FLAG\_REG = 0Ah

After Instruction

$FLAG_REG = 8Ah$

#### 27.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM™ Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 27.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

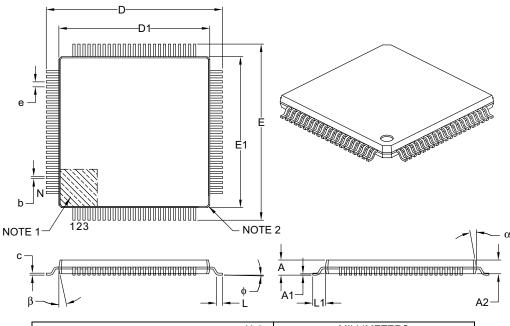

#### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |                  | MILLIMETERS |      |      |

|--------------------------|------------------|-------------|------|------|

|                          | Dimension Limits | MIN         | NOM  | MAX  |

| Number of Leads          | N                | 100         |      |      |

| Lead Pitch               | е                | 0.40 BSC    |      |      |

| Overall Height           | Α                | -           | _    | 1.20 |

| Molded Package Thickness | A2               | 0.95        | 1.00 | 1.05 |

| Standoff                 | A1               | 0.05        | _    | 0.15 |

| Foot Length              | L                | 0.45        | 0.60 | 0.75 |

| Footprint                | L1               | 1.00 REF    |      |      |

| Foot Angle               | ф                | 0°          | 3.5° | 7°   |

| Overall Width            | Е                | 14.00 BSC   |      |      |

| Overall Length           | D                | 14.00 BSC   |      |      |

| Molded Package Width     | E1               | 12.00 BSC   |      |      |

| Molded Package Length    | D1               | 12.00 BSC   |      |      |

| Lead Thickness           | С                | 0.09        | _    | 0.20 |

| Lead Width               | b                | 0.13        | 0.18 | 0.23 |

| Mold Draft Angle Top     | α                | 11°         | 12°  | 13°  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°  | 13°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

| RD2/CCP4/P3D           | 21         | VDD24                                         | ١, 42, 32 |

|------------------------|------------|-----------------------------------------------|-----------|

| RD3/AD3/PSP3           | 36         | VDDCORE/VCAP42                                | 2, 24, 32 |

| RD4/AD4/PSP4/SDO2      | 36         | VDDPLL                                        | 2, 42, 24 |

| RD5/AD5/PSP5/SDI2/SDA2 | 36         | VDDRX                                         | 2, 42, 24 |

| RD6/AD6/PSP6/SCK2/SCL2 |            | VDDTX24                                       |           |

| RD7/AD7/PSP7/SS2       |            | Vss42                                         |           |

| RE0/AD8/RD/P2D         |            | VSSPLL                                        |           |

| RE0/P2D                |            | VSSRX                                         |           |

| RE1/AD9/WR/P2C         |            |                                               |           |

|                        |            | VSSTX                                         | 1, 42, 24 |

| RE1/P2C                |            | Pinout I/O Descriptions                       | 4.0       |

| RE2/AD10/CS/P2B        |            | PIC18F66J60/66J65/67J60                       |           |

| RE2/P2B                | , -        | PIC18F86J60/86J65/87J60                       |           |

| RE3/AD11/P3C           | 37         | PIC18F96J60/96J65/97J60                       | 33        |

| RE3/P3C                | 22, 28     | PIR Registers                                 | 134       |

| RE4/AD12/P3B           | 37         | PLL Block                                     | 51        |

| RE4/P3B                | 22, 28     | Clock Speeds for Various Configurations       | 52        |

| RE5/AD13/P1C           | 37         | POP                                           |           |

| RE5/P1C                |            | POR. See Power-on Reset.                      |           |

| RE6/AD14/P1B           | •          | PORTA                                         |           |

| RE6/P1B                |            |                                               | 117       |

|                        |            | Associated Registers                          |           |

| RE7/AD15/ECCP2/P2A     |            | LATA Register                                 |           |

| RE7/ECCP2/P2A          |            | PORTA Register                                |           |

| RF0/AN5                | 38         | TRISA Register                                | 146       |

| RF1/AN6/C2OUT          | 23, 29, 38 | PORTB                                         |           |

| RF2/AN7/C1OUT          | 23, 29, 38 | Associated Registers                          | 150       |

| RF3/AN8                | 23, 29, 38 | LATB Register                                 | 148       |

| RF4/AN9                |            | PORTB Register                                |           |

| RF5/AN10/CVREF         | , ,        | RB7:RB4 Interrupt-on-Change Flag (RBIF Bit) . |           |

| RF6/AN11               | , ,        | TRISB Register                                |           |

| RF7/SS1                |            | PORTC                                         | 140       |

|                        |            |                                               | 450       |

| RG0/ECCP3/P3A          | ·          | Associated Registers                          |           |

| RG1/TX2/CK2            | ·          | LATC Register                                 |           |

| RG2/RX2/DT2            |            | PORTC Register                                |           |

| RG3/CCP4/P3D           | 30, 39     | RC3/SCK1/SCL1 Pin                             | 286       |

| RG4/CCP5/P1D           | 24, 30, 39 | TRISC Register                                | 151       |

| RG5                    | 39         | PORTD                                         |           |

| RG6                    | 39         | Associated Registers                          | 156       |

| RG7                    | 39         | LATD Register                                 | 154       |

| RH0                    |            | PORTD Register                                |           |

| RH0/A16                |            | TRISD Register                                |           |

| RH1                    |            | PORTE                                         |           |

|                        |            | Associated Registers                          | 150       |

| RH1/A17                |            |                                               |           |

| RH2                    |            | LATE Register                                 |           |

| RH2/A18                |            | PORTE Register                                |           |

| RH3                    |            | PSP Mode Select (PSPMODE Bit)                 |           |

| RH3/A19                | 40         | RE0/AD8/RD/P2D Pin                            | 168       |

| RH4/AN12/P3C           | 31, 40     | RE1/AD9/WR/P2C Pin                            | 168       |

| RH5/AN13/P3B           | 31, 40     | RE2/AD10/CS/P2B Pin                           | 168       |

| RH6/AN14/P1C           | 31, 40     | TRISE Register                                | 157       |

| RH7/AN15/P1B           | 31. 40     | PORTF                                         |           |

| RJ0/ALE                | •          | Associated Registers                          | 161       |

| RJ1/OE                 |            | LATF Register                                 |           |

| RJ2/WRL                |            | PORTF Register                                |           |

|                        |            | · · · · · · · · · · · · · · · · · · ·         |           |

| RJ3/WRH                |            | TRISF Register                                | 160       |

| RJ4                    |            | PORTG                                         |           |

| RJ4/BA0                |            | Associated Registers                          |           |

| RJ5                    | 32         | LATG Register                                 | 162       |

| RJ5/CE                 | 41         | PORTG Register                                | 162       |

| RJ6/LB                 | 41         | TRISG Register                                | 162       |

| RJ7/UB                 |            | PORTH                                         |           |

| TPIN                   |            | Associated Registers                          | 165       |

| TPIN+                  |            | LATH Register                                 |           |

| TPOUT-                 |            | PORTH Register                                |           |

|                        |            |                                               |           |

| TPOUT+                 | 24, 32, 42 | TRISH Register                                | 104       |

| Serial Clock269                                 | Timer3                                                              |

|-------------------------------------------------|---------------------------------------------------------------------|

| Serial Data In                                  | 16-Bit Read/Write Mode                                              |

| Serial Data Out269                              | Associated Registers                                                |

| Slave Mode275                                   | Operation                                                           |

| Slave Select                                    | Oscillator 183, 185                                                 |

| Slave Select Synchronization275                 | Overflow Interrupt                                                  |

| SPI Clock274                                    | Resetting Using the ECCPx Special                                   |

| Typical Connection273                           | Event Trigger185                                                    |

| SSPOV                                           | TMR3H Register183                                                   |

| SSPOV Status Flag304                            | TMR3L Register183                                                   |

| SSPSTAT Register                                | Timer4                                                              |

| R/W Bit286                                      | Associated Registers188                                             |

| SSPxSTAT Register                               | Operation 187                                                       |

| R/W Bit284                                      | Output, PWM Time Base188                                            |

| 269                                             | Postscaler. See Postscaler, Timer4.                                 |

| SUBFSR421                                       | PR4 Register 187, 194                                               |

| SUBFWB410                                       | Prescaler. See Prescaler, Timer4.                                   |

| SUBLW411                                        | TMR4 Register187                                                    |

| SUBULNK421                                      | TMR4 to PR4 Match Interrupt187, 188                                 |

| SUBWF411                                        | Timing Diagrams                                                     |

| SUBWFB412                                       | A/D Conversion462                                                   |

| SWAPF412                                        | Asynchronous Reception, RXDTP = 0                                   |

| <b>T</b>                                        | (RXx Not Inverted)329                                               |

| Т                                               | Asynchronous Transmission (Back-to-Back),                           |

| Table Pointer Operations (table)108             | TXCKP = 0 (TXx Not Inverted)                                        |

| Table Reads/Table Writes83                      | Asynchronous Transmission, TXCKP = 0                                |

| TBLRD413                                        | (TXx Not Inverted)326                                               |

| TBLWT414                                        | Automatic Baud Rate Calculation 324                                 |

| Timer0171                                       | Auto-Wake-up Bit (WUE) During Normal                                |

| Associated Registers173                         | Operation33                                                         |

| Clock Source Select (T0CS Bit)172               | Auto-Wake-up Bit (WUE) During Sleep33                               |

| Operation172                                    | Baud Rate Generator with Clock Arbitration 30                       |

| Overflow Interrupt173                           | BRG Overflow Sequence324                                            |

| Prescaler173                                    | BRG Reset Due to SDAx Arbitration During                            |

| Prescaler Assignment (PSA Bit)173               | Start Condition310                                                  |

| Prescaler Select (T0PS2:T0PS0 Bits)173          | Capture/Compare/PWM (Including                                      |

| Prescaler, Switching Assignment                 | ECCPx Modules)452                                                   |

| Prescaler. See Prescaler, Timer0.               | CLKO and I/O447                                                     |

| Reads and Writes in 16-Bit Mode                 | Clock Synchronization294                                            |

| Source Edge Select (T0SE Bit)                   | Clock/Instruction Cycle84                                           |

| Timer1                                          | EUSARTx Synchronous Receive                                         |

| 16-Bit Read/Write Mode                          | (Master/Slave)46                                                    |

| Associated Registers                            | EUSARTx Synchronous Transmission                                    |

| Considerations in Asynchronous Counter Mode 178 | (Master/Slave)46                                                    |

| Interrupt                                       | Example SPI Master Mode (CKE = 0)                                   |

| Operation                                       | Example SPI Master Mode (CKE = 1)                                   |

| Oscillator                                      | Example SPI Slave Mode (CKE = 0)                                    |

| Layout Considerations                           | Example SPI Slave Mode (CKE = 1)                                    |

| Overflow Interrupt                              | External Clock (All Modes Except PLL) 445                           |

| Resetting, Using the ECCPx Special              | External Memory Bus for Sleep (Extended                             |

| Event Trigger                                   | Microcontroller Mode)                                               |

| Special Event Trigger (ECCP)                    | External Memory Bus for TBLRD (Extended                             |

| TMR1H Register                                  | Microcontroller Mode)                                               |

| TMR1L Register                                  | Fail-Safe Clock Monitor                                             |

| Use as a Clock Source                           | First Start Bit                                                     |

| Use as a Real-Time Clock                        | Full-Bridge PWM Output                                              |

| Timer2                                          | Half-Bridge PWM Output                                              |

| Associated Registers                            | I <sup>2</sup> C Acknowledge Sequence                               |

| Interrupt                                       | I <sup>2</sup> C Bus Collision During a Repeated                    |

| Operation                                       | Start Condition (Case 1)                                            |

| Output                                          | I <sup>2</sup> C Bus Collision During a Repeated                    |

| PR2 Register                                    | Start Condition (Case 2)                                            |

| TMR2 to PR2 Match Interrupt203                  | I <sup>2</sup> C Bus Collision During a Stop Condition (Case 1) 312 |

| I <sup>2</sup> C Bus Collision During a Stop                    | Transition From RC_RUN Mode to                      |

|-----------------------------------------------------------------|-----------------------------------------------------|

| Condition (Case 2)312                                           | PRI_RUN Mode 58                                     |

| I <sup>2</sup> C Bus Collision During Start                     | Transition From SEC RUN Mode to                     |

| Condition (SCLx = 0)310                                         | PRI_RUN Mode (HSPLL) 57                             |

| I <sup>2</sup> C Bus Collision During Start                     | Transition to RC_RUN Mode58                         |

| Condition (SDAx Only)309                                        | Timing Diagrams and Specifications                  |

| I <sup>2</sup> C Bus Collision for Transmit and Acknowledge 308 | AC Characteristics                                  |

| I <sup>2</sup> C Bus Data457                                    | Internal RC Accuracy446                             |

| I <sup>2</sup> C Bus Start/Stop Bits457                         | Capture/Compare/PWM Requirements                    |

| I <sup>2</sup> C Master Mode (7 or 10-Bit Transmission) 305     | (Including ECCPx Modules)452                        |

| I <sup>2</sup> C Master Mode (7-Bit Reception)306               | CLKO and I/O Requirements 447, 448                  |

| I <sup>2</sup> C Slave Mode (10-Bit Reception, SEN = 0,         | EUSARTx Synchronous Receive Requirements 461        |

| ADMSK = 01001)291                                               | EUSARTx Synchronous Transmission                    |

| $1^{2}$ C Slave Mode (10-Bit Reception, SEN = 0) 290            | Requirements461                                     |

| I <sup>2</sup> C Slave Mode (10-Bit Reception, SEN = 1)         | Example SPI Mode Requirements                       |

| I <sup>2</sup> C Slave Mode (10-Bit Transmission)               | (Master Mode, CKE = 0) 453                          |

| I <sup>2</sup> C Slave Mode (7-Bit Reception, SEN = 0,          | Example SPI Mode Requirements                       |

| ADMSK = 01011)                                                  | (Master Mode, CKE = 1)                              |

| I <sup>2</sup> C Slave Mode (7-Bit Reception, SEN = 0)          | Example SPI Mode Requirements                       |

| I <sup>2</sup> C Slave Mode (7-Bit Reception, SEN = 1)          | (Slave Mode, CKE = 0)                               |

| I <sup>2</sup> C Slave Mode (7-Bit Transmission)                | Example SPI Slave Mode Requirements (CKE = 1) 456   |

| I <sup>2</sup> C Slave Mode General Call Address                | External Clock Requirements                         |

| Sequence (7 or 10-Bit Addressing Mode) 297                      | I <sup>2</sup> C Bus Data Requirements (Slave Mode) |

| I <sup>2</sup> C Stop Condition Receive or Transmit Mode 307    | I <sup>2</sup> C Bus Start/Stop Bits Requirements   |

| Master SSP I <sup>2</sup> C Bus Data                            | (Slave Mode)                                        |

| Master SSP I <sup>2</sup> C Bus Start/Stop Bits                 | Master SSP I <sup>2</sup> C Bus Data Requirements   |

| Parallel Slave Port (PSP) Read                                  | Master SSP I <sup>2</sup> C Bus Start/Stop Bits     |

| Parallel Slave Port (PSP) Write                                 | Requirements                                        |

| Program Memory Read                                             | Parallel Slave Port Requirements                    |

| Program Memory Write                                            | PLL Clock                                           |

| PWM Auto-Shutdown (P1RSEN = 0,                                  | Program Memory Write Requirements                   |

| Auto-Restart Disabled)                                          | Reset, Watchdog Timer, Oscillator Start-up          |

| PWM Auto-Shutdown (P1RSEN = 1,                                  | Timer, Power-up Timer and Brown-out                 |

| Auto-Restart Enabled)                                           | Reset Requirements                                  |

| PWM Direction Change                                            | Timer0 and Timer1 External Clock                    |

| PWM Direction Change at Near                                    | Requirements                                        |

| 100% Duty Cycle                                                 | Top-of-Stack Access                                 |

| PWM Output                                                      | TRISE Register PSPMODE Bit168                       |

| Repeated Start Condition                                        |                                                     |

| Reset, Watchdog Timer (WDT), Oscillator Start-up                | TSTFSZ                                              |

| Timer (OST) and Power-up Timer (PWRT) 450                       | Two-Speed Start-up                                  |

| Send Break Character Sequence                                   | Example Cases85                                     |

| Slow Rise Time (MCLR Tied to VDD,                               | TXSTAx Register                                     |

| VDD Rise > TPWRT)67                                             | BRGH Bit                                            |

| SPI Mode (Master Mode)274                                       | DIVOTI DIL                                          |

| SPI Mode (Slave Mode, CKE = 0)                                  | V                                                   |

| SPI Mode (Slave Mode, CKE = 1)                                  | VDDCORE/VCAP Pin                                    |

| Synchronous Reception (Master Mode, SREN) 335                   |                                                     |

| Synchronous Transmission                                        | W                                                   |

| Synchronous Transmission (Through TXEN)                         | Watchdog Timer (WDT)                                |

| Time-out Sequence on Power-up (MCLR                             | Associated Registers                                |

| Not Tied to VDD), Case 166                                      | Control Register                                    |

| Time-out Sequence on Power-up (MCLR                             | Programming Considerations                          |

| Not Tied to VDD), Case 267                                      | WCOL 302, 303, 304, 307                             |

| Time-out Sequence on Power-up (MCLR Tied                        | WCOL Status Flag                                    |

| to VDD, VDD Rise < TPWRT)                                       | WWW Address                                         |

| Timer0 and Timer1 External Clock451                             | WWW, On-Line Support9                               |

| Transition for Entry to Idle Mode                               | V                                                   |

| Transition for Entry to SEC_RUN Mode57                          | X                                                   |

| Transition for Entry to Sleep Mode59                            | XORLW415                                            |

| Transition for Two-Speed Start-up                               | XORWF416                                            |

| (INTRC to HSPLL)370                                             |                                                     |

| Transition for Wake From Idle to Run Mode 60                    |                                                     |

| Transition for Wake From Sleep Mode (HSPLL) 59                  |                                                     |